Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 2KB (2K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 768 × 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 16x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f334-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

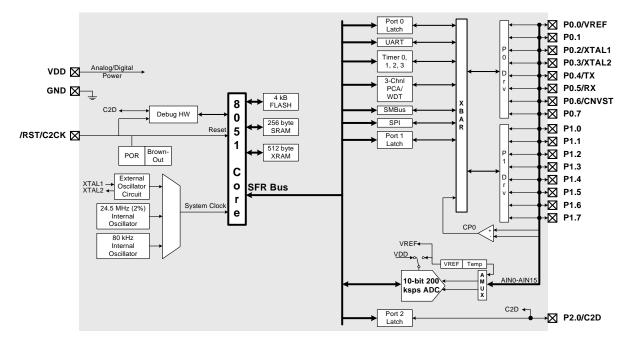

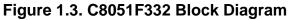

# C8051F330/1/2/3/4/5

Г

| Ordering Part Number | MIPS (Peak) | Flash Memory (kB) | RAM (bytes) | Calibrated Internal 24.5 MHz Oscillator | Internal 80 kHz Oscillator | SMBus/I <sup>2</sup> C | Enhanced SPI | UART         | Timers (16-bit) | Programmable Counter Array | Digital Port I/Os | 10-bit 200ksps ADC | 10-bit Current Output DAC | Internal Voltage Reference | Temperature Sensor | Analog Comparator | Lead-free (RoHS Compliant) | Package |

|----------------------|-------------|-------------------|-------------|-----------------------------------------|----------------------------|------------------------|--------------|--------------|-----------------|----------------------------|-------------------|--------------------|---------------------------|----------------------------|--------------------|-------------------|----------------------------|---------|

| C8051F330-GM         | 25          | 8                 | 768         | $\checkmark$                            | $\checkmark$               | $\checkmark$           | $\checkmark$ | $\checkmark$ | 4               | V                          | 17                | $\checkmark$       | $\checkmark$              | $\checkmark$               | $\checkmark$       | $\checkmark$      | $\checkmark$               | QFN-20  |

| C8051F331-GM         | 25          | 8                 | 768         | $\checkmark$                            | ~                          | $\checkmark$           | $\checkmark$ | $\checkmark$ | 4               | $\checkmark$               | 17                | —                  | —                         |                            |                    | $\checkmark$      | $\checkmark$               | QFN-20  |

| C8051F332-GM         | 25          | 4                 | 768         | $\checkmark$                            | ~                          | $\checkmark$           | ~            | $\checkmark$ | 4               | ~                          | 17                | ~                  | —                         | $\checkmark$               | $\checkmark$       | ~                 | $\checkmark$               | QFN-20  |

| C8051F333-GM         | 25          | 4                 | 768         | ~                                       | ~                          | ~                      | ~            | ~            | 4               | ~                          | 17                | —                  | —                         | _                          | _                  | ~                 | $\checkmark$               | QFN-20  |

| C8051F334-GM         | 25          | 2                 | 768         | $\checkmark$                            | $\checkmark$               | $\checkmark$           | $\checkmark$ | $\checkmark$ | 4               | ~                          | 17                | $\checkmark$       |                           | $\checkmark$               | $\checkmark$       | $\checkmark$      | $\checkmark$               | QFN-20  |

| C8051F335-GM         | 25          | 2                 | 768         | $\checkmark$                            | $\checkmark$               | $\checkmark$           | $\checkmark$ | $\checkmark$ | 4               | $\checkmark$               | 17                |                    |                           |                            |                    | $\checkmark$      | $\checkmark$               | QFN-20  |

Table 1.1. Product Selection Guide

٦

# C8051F330/1/2/3/4/5

Figure 1.4. C8051F333 Block Diagram

# C8051F330/1/2/3/4/5

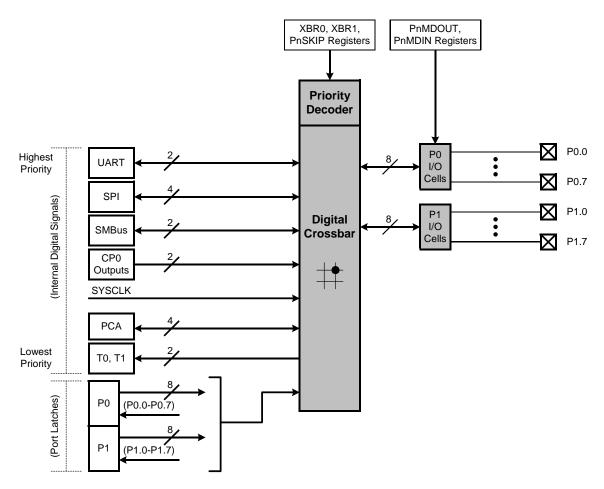

# 1.4. Programmable Digital I/O and Crossbar

C8051F330/1/2/3/4/5 devices include 17 I/O pins (two byte-wide Ports and one 1-bit-wide Port). The C8051F330/1/2/3/4/5 Ports behave like typical 8051 Ports with a few enhancements. Each Port pin may be configured as an analog input or a digital I/O pin. Pins selected as digital I/Os may additionally be configured for push-pull or open-drain output. The "weak pullups" that are fixed on typical 8051 devices may be globally disabled, providing power savings capabilities.

The Digital Crossbar allows mapping of internal digital system resources to Port I/O pins. (See Figure 1.11.) On-chip counter/timers, serial buses, HW interrupts, comparator output, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the particular application.

# 1.5. Serial Ports

The C8051F330/1/2/3/4/5 Family includes an SMBus/I<sup>2</sup>C interface, a full-duplex UART with enhanced baud rate configuration, and an Enhanced SPI interface. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

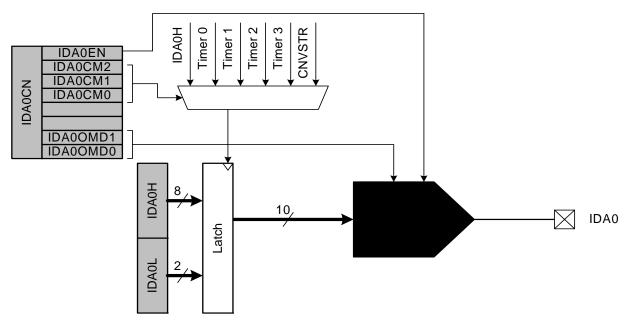

# 1.9. 10-bit Current Output DAC

The C8051F330 device includes a 10-bit current-mode Digital-to-Analog Converter (IDA0). The maximum current output of the IDA0 can be adjusted for three different current settings; 0.5 mA, 1 mA, and 2 mA. IDA0 features a flexible output update mechanism which allows for seamless full-scale changes and supports jitter-free updates for waveform generation. Three update modes are provided, allowing IDA0 output updates on a write to IDA0H, on a Timer overflow, or on an external pin edge.

Figure 1.16. IDA0 Functional Block Diagram

# 3. Global Electrical Characteristics

## **Table 3.1. Global Electrical Characteristics**

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                    | Conditions                                                                        | Min           | Тур    | Max   | Units  |

|----------------------------------------------|-----------------------------------------------------------------------------------|---------------|--------|-------|--------|

| Digital Supply Voltage                       |                                                                                   | $V_{RST}^{1}$ | 3.0    | 3.6   | V      |

| Digital Supply RAM Data<br>Retention Voltage |                                                                                   | _             | 1.5    | _     | V      |

| SYSCLK (System Clock)<br>(Note 2)            |                                                                                   | 0             |        | 25    | MHz    |

| T <sub>SYSH</sub> (SYSCLK High Time)         |                                                                                   | 18            | _      |       | ns     |

| T <sub>SYSL</sub> (SYSCLK Low Time)          |                                                                                   | 18            | _      | _     | ns     |

| Specified Operating<br>Temperature Range     |                                                                                   | -40           |        | +85   | °C     |

| Digital Supply Current—CPU                   | Active (Normal Mode, fetching instr                                               | uctions       | from F | lash) |        |

| I <sub>DD</sub> (Note 3)                     | V <sub>DD</sub> = 3.6 V, F = 25 MHz                                               | —             | 10.7   | 11.7  | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 25 MHz                                               | —             | 7.8    | 8.3   | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 1 MHz                                                | —             | 0.38   | —     | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 80 kHz                                               | _             | 31     | _     | μA     |

| I <sub>DD</sub> Supply Sensitivity (Note 3)  | F = 25 MHz                                                                        | _             | 65     |       | %/V    |

|                                              | F = 1 MHz                                                                         |               | 61     |       | %/V    |

| I <sub>DD</sub> Frequency Sensitivity        | $V_{DD}$ = 3.0 V, F $\leq$ 15 MHz, T = 25 °C                                      | _             | 0.38   | _     | mA/MHz |

| (Note 3, Note 4)                             | V <sub>DD</sub> = 3.0 V, F > 15 MHz, T = 25 °C                                    | —             | 0.21   | —     | mA/MHz |

|                                              | $V_{DD} = 3.6 \text{ V}, \text{ F} \le 15 \text{ MHz}, \text{ T} = 25 \text{ °C}$ | —             | 0.53   | —     | mA/MHz |

|                                              | V <sub>DD</sub> = 3.6 V, F > 15 MHz, T = 25 °C                                    | _             | 0.27   | _     | mA/MHz |

## Table 3.1. Global Electrical Characteristics

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                       | Conditions                                                  | Min      | Тур     | Max    | Units  |

|-------------------------------------------------|-------------------------------------------------------------|----------|---------|--------|--------|

| Digital Supply Current—CPU                      | Inactive (Idle Mode, not fetching ins                       | tructior | ns from | Flash) |        |

| I <sub>DD</sub> (Note 3)                        | V <sub>DD</sub> = 3.6 V, F = 25 MHz                         | _        | 4.8     | 5.2    | mA     |

|                                                 | V <sub>DD</sub> = 3.0 V, F = 25 MHz                         | —        | 3.8     | 4.1    | mA     |

|                                                 | V <sub>DD</sub> = 3.0 V, F = 1 MHz                          | _        | 0.20    | —      | mA     |

|                                                 | V <sub>DD</sub> = 3.0 V, F = 80 kHz                         | _        | 16      | —      | μA     |

| I <sub>DD</sub> Supply Sensitivity (Note 3)     | F = 25 MHz                                                  | _        | 43      | _      | %/V    |

|                                                 | F = 1 MHz                                                   | —        | 55      | —      | %/V    |

| I <sub>DD</sub> Frequency Sensitivity           | V <sub>DD</sub> = 3.0 V, F <u>&lt;</u> 1 MHz, T = 25 °C     | _        | 0.20    | —      | mA/MHz |

| (Note 3, Note 5)                                | V <sub>DD</sub> = 3.0 V, F > 1 MHz, T = 25 °C               | —        | 0.15    | —      | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F <u>&lt;</u> 1 MHz, T = 25 °C     | _        | 0.24    | —      | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F > 1 MHz, T = 25 °C               | _        | 0.19    | _      | mA/MHz |

| Digital Supply Current<br>(Stop Mode, shutdown) | Oscillator not running,<br>V <sub>DD</sub> Monitor Disabled | —        | < 0.1   | —      | μA     |

#### Notes:

- 1. Given in Table 10.1 on page 102.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- 3. Based on device characterization data; Not production tested.

- 4. IDD can be estimated for frequencies <= 15 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> for >15 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 20 MHz, I<sub>DD</sub> = 7.8 mA (25 MHz 20 MHz) \* 0.21 mA/MHz = 6.75 mA.

- 5. Idle IDD can be estimated for frequencies <= 1 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate Idle I<sub>DD</sub> for >1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 4.8 mA (25 MHz 5 MHz) \* 0.15 mA/MHz = 1.8 mA.

Other electrical characteristics tables are found in the data sheet section corresponding to the associated peripherals. For more information on electrical characteristics for a specific peripheral, refer to the page indicated in Table 3.2.

| R/W      | R/W                                                                                                                                                                                                                      | R/W           | R/W           | R/W          | R/W            | R/W           | R/W           | Reset Value  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|--------------|----------------|---------------|---------------|--------------|--|--|--|--|--|

| AD0EN    | AD0TM                                                                                                                                                                                                                    | AD0INT        | AD0BUSY       | AD0WINT      | AD0CM2         | AD0CM1        | AD0CM0        | 00000000     |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                     | Bit5          | Bit4          | Bit3         | Bit2           | Bit1          | Bit0          | SFR Address: |  |  |  |  |  |

|          |                                                                                                                                                                                                                          |               |               |              |                | (bit addr     | essable)      | 0xE8         |  |  |  |  |  |

| Bit7:    | AD0EN: AD<br>0: ADC0 Dis                                                                                                                                                                                                 |               |               | power shutc  | lown.          |               |               |              |  |  |  |  |  |

| Bit6:    | <ol> <li>1: ADC0 Enabled. ADC0 is active and ready for data conversions.</li> <li>AD0TM: ADC0 Track Mode Bit.</li> <li>0: Normal Track Mode: When ADC0 is enabled, tracking is continuous unless a conversion</li> </ol> |               |               |              |                |               |               |              |  |  |  |  |  |

| Bit5:    | is in progress.<br>1: Low-power Track Mode: Tracking Defined by AD0CM2–0 bits (see below).                                                                                                                               |               |               |              |                |               |               |              |  |  |  |  |  |

|          | AD0INT: ADC0 Conversion Complete Interrupt Flag.<br>0: ADC0 has not completed a data conversion since the last time AD0INT was cleared.<br>1: ADC0 has completed a data conversion.                                      |               |               |              |                |               |               |              |  |  |  |  |  |

| Bit4:    | AD0BUSY: /<br>Read:                                                                                                                                                                                                      |               |               |              |                |               |               |              |  |  |  |  |  |

|          | 0: ADC0 cor<br>to logic 1 on                                                                                                                                                                                             | the falling   | edge of AD    | 0BUSY.       | on is not cu   | rrently in pr | ogress. AD    | 0INT is set  |  |  |  |  |  |

|          | 1: ADC0 cor<br>Write:                                                                                                                                                                                                    | nversion is   | in progress   |              |                |               |               |              |  |  |  |  |  |

|          | 0: No Effect.                                                                                                                                                                                                            |               |               |              |                |               |               |              |  |  |  |  |  |

|          | 1: Initiates A                                                                                                                                                                                                           |               |               |              |                |               |               |              |  |  |  |  |  |

| Bit3:    | ADOWINT: A                                                                                                                                                                                                               |               | •             | •            | -              |               | . ()          |              |  |  |  |  |  |

|          | 0: ADC0 Win<br>1: ADC0 Win                                                                                                                                                                                               |               |               |              |                | ed since this | s flag was la | ast cleared. |  |  |  |  |  |

| Bits2–0: | AD0CM2-0:                                                                                                                                                                                                                |               |               |              |                |               |               |              |  |  |  |  |  |

|          | When AD0T                                                                                                                                                                                                                |               |               |              |                |               |               |              |  |  |  |  |  |

|          | 000: ADC0 (                                                                                                                                                                                                              |               |               |              |                | 0BUSY.        |               |              |  |  |  |  |  |

|          | 001: ADC0 0<br>010: ADC0 0                                                                                                                                                                                               |               |               |              |                |               |               |              |  |  |  |  |  |

|          | 010: ADC0 0                                                                                                                                                                                                              |               |               |              |                |               |               |              |  |  |  |  |  |

|          | 100: ADC0 0                                                                                                                                                                                                              |               |               |              |                | CNVSTR.       |               |              |  |  |  |  |  |

|          | 101: ADC0 o                                                                                                                                                                                                              | conversion    | initiated on  | overflow of  | Timer 3.       |               |               |              |  |  |  |  |  |

|          | 11x: Reserve                                                                                                                                                                                                             |               |               |              |                |               |               |              |  |  |  |  |  |

|          | When AD0T<br>000: Trackin<br>version.                                                                                                                                                                                    |               | on write of ' | 1' to AD0BU  | SY and las     | ts 3 SAR cl   | ocks, follow  | ved by con-  |  |  |  |  |  |

|          | 001: Trackin sion.                                                                                                                                                                                                       | g initiated   | on overflow   | of Timer 0 a | ind lasts 3 \$ | SAR clocks    | , followed b  | y conver-    |  |  |  |  |  |

|          | 010: Trackin sion.                                                                                                                                                                                                       | g initiated   | on overflow   | of Timer 2 a | ind lasts 3 \$ | SAR clocks    | , followed b  | y conver-    |  |  |  |  |  |

|          | 011: Trackin sion.                                                                                                                                                                                                       | g initiated o | on overflow   | of Timer 1 a | nd lasts 3 S   | SAR clocks    | , followed b  | y conver-    |  |  |  |  |  |

|          | 100: ADC0 t<br>CNVSTR ed                                                                                                                                                                                                 | •             | when CNV      | STR input is | logic low; c   | conversion s  | starts on ris | ing          |  |  |  |  |  |

|          | 101: Trackin sion.                                                                                                                                                                                                       |               | on overflow   | of Timer 3 a | ind lasts 3 \$ | SAR clocks    | , followed b  | y conver-    |  |  |  |  |  |

|          | 11x: Reserve                                                                                                                                                                                                             | ed.           |               |              |                |               |               |              |  |  |  |  |  |

# SFR Definition 5.6. ADC0CN: ADC0 Control

# 6. 10-Bit Current Mode DAC (IDA0, C8051F330 only)

The C8051F330 device includes a 10-bit current-mode Digital-to-Analog Converter (IDAC). The maximum current output of the IDAC can be adjusted for three different current settings; 0.5 mA, 1 mA, and 2 mA. The IDAC is enabled or disabled with the IDA0EN bit in the IDA0 Control Register (see SFR Definition 6.1). When IDA0EN is set to '0', the IDAC port pin (P0.1) behaves as a normal GPIO pin. When IDA0EN is set to '1', the digital output drivers and weak pullup for the IDAC pin are automatically disabled, and the pin is connected to the IDAC output. An internal bandgap bias generator is used to generate a reference current for the IDAC whenever it is enabled. When using the IDAC, bit 1 in the POSKIP register should be set to '1', to force the Crossbar to skip the IDAC pin.

# 6.1. IDA0 Output Scheduling

IDA0 features a flexible output update mechanism which allows for seamless full-scale changes and supports jitter-free updates for waveform generation. Three update modes are provided, allowing IDAC output updates on a write to IDA0H, on a Timer overflow, or on an external pin edge.

## 6.1.1. Update Output On-Demand

In its default mode (IDA0CN.[6:4] = '111') the IDA0 output is updated "on-demand" on a write to the highbyte of the IDA0 data register (IDA0H). It is important to note that writes to IDA0L are held in this mode, and have no effect on the IDA0 output until a write to IDA0H takes place. If writing a full 10-bit word to the IDAC data registers, the 10-bit data word is written to the low byte (IDA0L) and high byte (IDA0H) data registers. Data is latched into IDA0 after a write to the IDA0H register, **so the write sequence should be IDA0L followed by IDA0H** if the full 10-bit resolution is required. The IDAC can be used in 8-bit mode by initializing IDA0L to the desired value (typically 0x00), and writing data to only IDA0H (see **Section 6.2** for information on the format of the 10-bit IDAC data word within the 16-bit SFR space).

Figure 6.1. IDA0 Functional Block Diagram

### 9.2.2. Data Memory

The CIP-51 includes 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory organization of the CIP-51.

#### 9.2.3. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 9.4). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 9.2.4. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

#### MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 9.2.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

# Table 9.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Description                       | Page |

|----------|---------|-----------------------------------|------|

| OSCXCN   | 0xB1    | External Oscillator Control       | 117  |

| P0       | 0x80    | Port 0 Latch                      | 130  |

| POMDIN   | 0xF1    | Port 0 Input Mode Configuration   | 130  |

| POMDOUT  | 0xA4    | Port 0 Output Mode Configuration  | 131  |

| POSKIP   | 0xD4    | Port 0 Skip                       | 131  |

| P1       | 0x90    | Port 1 Latch                      | 131  |

| P1MDIN   | 0xF2    | Port 1 Input Mode Configuration   | 132  |

| P1MDOUT  | 0xA5    | Port 1 Output Mode Configuration  | 132  |

| P1SKIP   | 0xD5    | Port 1 Skip                       | 132  |

| P2       | 0xA0    | Port 2 Latch                      | 133  |

| P2MDOUT  | 0xA6    | Port 2 Output Mode Configuration  | 133  |

| PCA0CN   | 0xD8    | PCA Control                       | 205  |

| PCA0CPH0 | 0xFC    | PCA Capture 0 High                | 208  |

| PCA0CPH1 | 0xEA    | PCA Capture 1 High                | 208  |

| PCA0CPH2 | 0xEC    | PCA Capture 2 High                | 208  |

| PCA0CPL0 | 0xFB    | PCA Capture 0 Low                 | 208  |

| PCA0CPL1 | 0xE9    | PCA Capture 1 Low                 | 208  |

| PCA0CPL2 | 0xEB    | PCA Capture 2 Low                 | 208  |

| PCA0CPM0 | 0xDA    | PCA Module 0 Mode Register        | 207  |

| PCA0CPM1 | 0xDB    | PCA Module 1 Mode Register        | 207  |

| PCA0CPM2 | 0xDC    | PCA Module 2 Mode Register        | 207  |

| PCA0H    | 0xFA    | PCA Counter High                  | 208  |

| PCA0L    | 0xF9    | PCA Counter Low                   | 208  |

| PCA0MD   | 0xD9    | PCA Mode                          | 206  |

| PCON     | 0x87    | Power Control                     | 95   |

| PSCTL    | 0x8F    | Program Store R/W Control         | 108  |

| PSW      | 0xD0    | Program Status Word               | 84   |

| REF0CN   | 0xD1    | Voltage Reference Control         | 62   |

| RSTSRC   | 0xEF    | Reset Source Configuration/Status | 101  |

| SBUF0    | 0x99    | UART0 Data Buffer                 | 159  |

| SCON0    | 0x98    | UART0 Control                     | 158  |

| SMB0CF   | 0xC1    | SMBus Configuration               | 142  |

| SMB0CN   | 0xC0    | SMBus Control                     | 144  |

| SMB0DAT  | 0xC2    | SMBus Data                        | 146  |

# SFR Definition 9.9. EIE1: Extended Interrupt Enable 1

| R/W   | R/W                                                                                                                        | R/W                                                 | R/W         | R/W          | R/W        | R/W           | R/W       | Reset Value  |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|--------------|------------|---------------|-----------|--------------|--|--|--|--|--|--|

| ET3   | Reserved                                                                                                                   | ECP0                                                | EPCA0       | EADC0        | EWADC0     | Reserved      | ESMB0     | 00000000     |  |  |  |  |  |  |

| Bit7  | Bit6                                                                                                                       | Bit5                                                | Bit4        | Bit3         | Bit2       | Bit1          | Bit0      | SFR Address: |  |  |  |  |  |  |

|       |                                                                                                                            |                                                     |             |              |            |               |           | 0xE6         |  |  |  |  |  |  |

|       |                                                                                                                            |                                                     |             |              |            |               |           |              |  |  |  |  |  |  |

| Bit7: | ET3: Enable                                                                                                                |                                                     |             | <b>.</b>     |            |               |           |              |  |  |  |  |  |  |

|       |                                                                                                                            | This bit sets the masking of the Timer 3 interrupt. |             |              |            |               |           |              |  |  |  |  |  |  |

|       | <ul><li>0: Disable Timer 3 interrupts.</li><li>1: Enable interrupt requests generated by the TF3L or TF3H flags.</li></ul> |                                                     |             |              |            |               |           |              |  |  |  |  |  |  |

| D:+C. |                                                                                                                            |                                                     | •           |              | IF3L OF IF | 3H flags.     |           |              |  |  |  |  |  |  |

| Bit6: | RESERVED.                                                                                                                  |                                                     |             | -            |            |               |           |              |  |  |  |  |  |  |

| Bit5: | ECP0: Enabl                                                                                                                |                                                     | ```         |              |            |               |           |              |  |  |  |  |  |  |

|       | This bit sets                                                                                                              |                                                     | •           | o interrupt. |            |               |           |              |  |  |  |  |  |  |

|       | 0: Disable Cl<br>1: Enable int                                                                                             |                                                     |             | atod by the  |            |               | •         |              |  |  |  |  |  |  |

| Bit4: | EPCA0: Ena                                                                                                                 |                                                     |             |              |            |               | 5.        |              |  |  |  |  |  |  |

| DIL4. | This bit sets                                                                                                              | •                                                   |             | •            | · · ·      | enupt.        |           |              |  |  |  |  |  |  |

|       | 0: Disable all                                                                                                             |                                                     | •           | Ao interiup  |            |               |           |              |  |  |  |  |  |  |

|       | 1: Enable int                                                                                                              |                                                     |             | ated by PC4  | 20         |               |           |              |  |  |  |  |  |  |

| Bit3: | EADC0: Ena                                                                                                                 |                                                     | •           |              |            |               |           |              |  |  |  |  |  |  |

| Dito. | This bit sets                                                                                                              |                                                     |             |              | •          | ete interrupt |           |              |  |  |  |  |  |  |

|       | 0: Disable Al                                                                                                              |                                                     | •           |              |            |               | •         |              |  |  |  |  |  |  |

|       | 1: Enable int                                                                                                              |                                                     |             |              | •          | <b>a</b> .    |           |              |  |  |  |  |  |  |

| Bit2: | EWADC0: Er                                                                                                                 |                                                     |             |              |            | 5             |           |              |  |  |  |  |  |  |

|       | This bit sets                                                                                                              |                                                     |             |              |            | terrupt.      |           |              |  |  |  |  |  |  |

|       | 0: Disable Al                                                                                                              | DC0 Windo                                           | w Compari   | son interrup | ot.        | ·             |           |              |  |  |  |  |  |  |

|       | 1: Enable int                                                                                                              | errupt requ                                         | ests genera | ated by AD   | C0 Window  | Compare fla   | ag (AD0WI | NT).         |  |  |  |  |  |  |

| Bit1: | RESERVED.                                                                                                                  | . Read = 0.                                         | Must Write  | e 0.         |            |               |           |              |  |  |  |  |  |  |

| Bit0: | ESMB0: Ena                                                                                                                 | ble SMBus                                           | s (SMB0) In | terrupt.     |            |               |           |              |  |  |  |  |  |  |

|       | This bit sets                                                                                                              | the maskin                                          | g of the SM | 1B0 interrup | t.         |               |           |              |  |  |  |  |  |  |

|       | 0: Disable all SMB0 interrupts.                                                                                            |                                                     |             |              |            |               |           |              |  |  |  |  |  |  |

|       | 1: Enable interrupt requests generated by SMB0.                                                                            |                                                     |             |              |            |               |           |              |  |  |  |  |  |  |

|       |                                                                                                                            |                                                     |             |              |            |               |           |              |  |  |  |  |  |  |

|       |                                                                                                                            |                                                     |             |              |            |               |           |              |  |  |  |  |  |  |

# SFR Definition 9.11. IT01CF: INT0/INT1 Configuration

| R/W       | R/W                                | R/W          | R/W          | R/W           | R/W            | R/W            | R/W          | Reset Value  |

|-----------|------------------------------------|--------------|--------------|---------------|----------------|----------------|--------------|--------------|

| IN1PL     | IN1SL2                             | IN1SL1       | IN1SL0       | IN0PL         | IN0SL2         | IN0SL1         | IN0SL0       | 00000001     |

| Bit7      | Bit6                               | Bit5         | Bit4         | Bit3          | Bit2           | Bit1           | Bit0         | SFR Address: |

|           |                                    |              |              |               |                |                |              | 0xE4         |

| *Note: Re | efer to SFR Defin                  | ition 18.1 f | or INT0/1 ed | ae- or level- | sensitive inte | rrupt selectio | n.           |              |

|           |                                    |              |              | 9             |                |                |              |              |

| Bit7:     | IN1PL: /INT1 F                     | Polarity     |              |               |                |                |              |              |

|           | 0: /INT1 input                     |              | ow.          |               |                |                |              |              |

|           | 1: /INT1 input                     | is active h  | nigh.        |               |                |                |              |              |

| Bits6–4:  | IN1SL2-0: /IN                      |              |              |               |                |                |              |              |

|           | These bits sel                     |              |              |               |                |                |              |              |

|           | pendent of the                     |              |              |               |                |                |              |              |

|           | peripheral that                    |              |              |               |                |                |              |              |

|           | assign the Por                     |              |              |               |                | the selected   | a pin (accor | npiisned by  |

|           | setting to '1' th                  | le corresp   | onaing bit i | n register r  | -USKIP).       |                |              |              |

|           | IN1SL2-0                           | /INT         | 1 Port Pin   |               |                |                |              |              |

|           | 000                                |              | P0.0         |               |                |                |              |              |

|           | 001                                |              | P0.1         |               |                |                |              |              |

|           | 010                                |              | P0.2         |               |                |                |              |              |

|           | 011                                |              | P0.3         |               |                |                |              |              |

|           | 100                                |              | P0.4         |               |                |                |              |              |

|           | 101                                |              | P0.5         |               |                |                |              |              |

|           | 110                                |              | P0.6         |               |                |                |              |              |

|           | 111                                |              | P0.7         |               |                |                |              |              |

| D:40.     |                                    |              |              |               |                |                |              |              |

| Bit3:     | INOPL: /INTO I<br>0: /INTO interro |              |              |               |                |                |              |              |

|           | 1: /INT0 interro                   | •            |              |               |                |                |              |              |

| Bits2–0:  | INT0SL2-0: /I                      | •            | •            | on Bits       |                |                |              |              |

| B102 01   | These bits sel                     |              |              |               | /INT0. Note    | e that this p  | in assionm   | ent is inde- |

|           | pendent of the                     |              |              |               |                |                |              |              |

|           | peripheral that                    |              |              |               |                |                |              |              |

|           | assign the Por                     | • •          | •            | -             | •              | the selected   | d pin (accor | mplished by  |

|           | setting to '1' th                  | ne corresp   | onding bit i | n register F  | POSKIP).       |                |              |              |

|           |                                    | /////        |              |               |                |                |              |              |

|           | <b>IN0SL2–0</b><br>000             | /IN I        | P0.0         |               |                |                |              |              |

|           | 000                                | _            | P0.0<br>P0.1 |               |                |                |              |              |

|           | 010                                | _            | P0.1         |               |                |                |              |              |

|           | 010                                |              | P0.2<br>P0.3 |               |                |                |              |              |

|           | 100                                |              | P0.3<br>P0.4 |               |                |                |              |              |

|           | 100                                |              | P0.4         |               |                |                |              |              |

|           | 110                                |              | P0.5         |               |                |                |              |              |

|           | 110                                |              | P0.0         |               |                |                |              |              |

|           |                                    |              | . 0.1        |               |                |                |              |              |

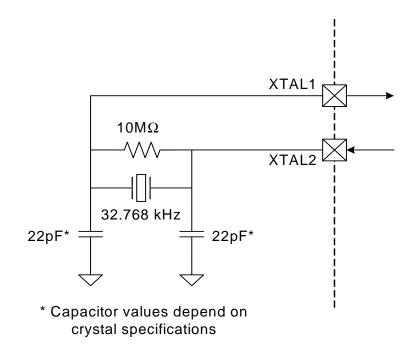

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

**Note:** The desired load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 13.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 13.2.

## Figure 13.2. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram

### 13.3.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 13.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$f = 1.23(10^3) / RC = 1.23(10^3) / [246 \times 50] = 0.1 MHz = 100 kHz$

Referring to the table in SFR Definition 13.4, the required XFCN setting is 010b.

#### 13.3.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 13.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation from the equations below. Assume  $V_{DD} = 3.0$  V and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 13.4 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

| R/W      | R/W                                                         | R            | R/W         | R/W           | R/W          | R/W           | R/W          | Reset Value  |  |  |  |  |  |

|----------|-------------------------------------------------------------|--------------|-------------|---------------|--------------|---------------|--------------|--------------|--|--|--|--|--|

| ENSMB    | INH                                                         | BUSY         | EXTHOLD     | SMBTOE        | SMBFTE       | SMBCS1        | SMBCS0       | 0000000      |  |  |  |  |  |

| Bit7     | Bit6                                                        | Bit5         | Bit4        | Bit3          | Bit2         | Bit1          | Bit0         |              |  |  |  |  |  |

|          |                                                             |              |             |               |              |               | SFR Address  | s: 0xC1      |  |  |  |  |  |

|          |                                                             |              |             |               |              |               |              |              |  |  |  |  |  |

| Bit7:    | ENSMB: SM                                                   |              |             |               |              |               |              |              |  |  |  |  |  |

|          | This bit enab                                               |              |             | is interface. | When enal    | oled, the int | erface cons  | tantly mon-  |  |  |  |  |  |

|          | itors the SD                                                |              |             |               |              |               |              |              |  |  |  |  |  |

|          | 0: SMBus interface disabled.<br>1: SMBus interface enabled. |              |             |               |              |               |              |              |  |  |  |  |  |

| Bit6:    | INH: SMBus Slave Inhibit.                                   |              |             |               |              |               |              |              |  |  |  |  |  |

| Dito:    | When this bi                                                |              |             | MBus does     | not genera   | te an interr  | upt when sla | ave events   |  |  |  |  |  |

|          | occur. This e                                               |              |             |               |              |               |              |              |  |  |  |  |  |

|          | not affected.                                               | •            |             |               |              |               |              | ·            |  |  |  |  |  |

|          | 0: SMBus S                                                  | lave Mode e  | enabled.    |               |              |               |              |              |  |  |  |  |  |

|          | 1: SMBus S                                                  |              |             |               |              |               |              |              |  |  |  |  |  |

| Bit5:    | BUSY: SMB                                                   | •            |             |               |              |               |              |              |  |  |  |  |  |

|          | This bit is se                                              | -            | •           |               | ansfer is in | progress. It  | is cleared t | o logic 0    |  |  |  |  |  |

| Bit4:    | when a STC<br>EXTHOLD:                                      |              |             |               | ncion Engh   |               |              |              |  |  |  |  |  |

| DIL4.    | This bit cont                                               |              |             |               |              |               |              |              |  |  |  |  |  |

|          | 0: SDA Exte                                                 |              |             |               | •            |               |              |              |  |  |  |  |  |

|          | 1: SDA Exte                                                 |              |             |               |              |               |              |              |  |  |  |  |  |

| Bit3:    | SMBTOE: S                                                   |              |             |               |              |               |              |              |  |  |  |  |  |

|          | This bit enal                                               | oles SCL lo  | w timeout d | etection. If  | set to logic | 1, the SMB    | us forces Ti | mer 3 to     |  |  |  |  |  |

|          | reload while                                                |              |             |               |              |               |              |              |  |  |  |  |  |

|          | figured to Sp                                               |              | • •         | •             |              |               |              | -            |  |  |  |  |  |

|          | Timer 3 sho                                                 |              |             |               |              | 25 ms, and f  | the Timer 3  | interrupt    |  |  |  |  |  |

| Dit0     | service routi                                               |              |             |               |              |               |              |              |  |  |  |  |  |

| Bit2:    | SMBFTE: S<br>When this bi                                   |              |             |               |              | o if SCL on   |              | ain high for |  |  |  |  |  |

|          | more than 1                                                 |              | -           |               |              |               |              | annightor    |  |  |  |  |  |

| Bits1–0: | SMBCS1-S                                                    |              |             |               | ection.      |               |              |              |  |  |  |  |  |

|          | These two b                                                 |              |             |               |              | sed to gene   | rate the SM  | lBus bit     |  |  |  |  |  |

|          | rate. The se                                                | lected devid | e should be | e configured  | d according  | to Equation   | n 15.1.      |              |  |  |  |  |  |

|          |                                                             |              |             |               | _            |               |              |              |  |  |  |  |  |

|          | SMBCS1                                                      | SMBCS0       |             | Bus Clock     |              |               |              |              |  |  |  |  |  |

|          | 0                                                           | 0            |             | Fimer 0 Ove   |              |               |              |              |  |  |  |  |  |

|          | 0                                                           | 1            |             | Fimer 1 Ove   | -            |               |              |              |  |  |  |  |  |

|          | 1                                                           | 0            |             | 2 High Byte   |              |               |              |              |  |  |  |  |  |

|          | 1                                                           | 1            | limer       | 2 Low Byte    | Overflow     |               |              |              |  |  |  |  |  |

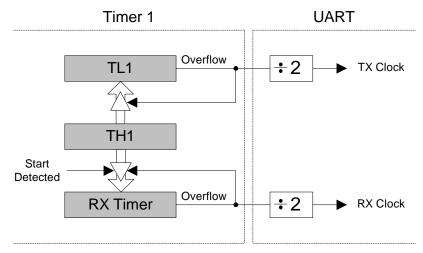

# 16.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 16.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see **Section "18.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 179**). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 16.1-A and Equation 16.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

# Equation 16.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in **Section "18. Timers" on page 177.** A quick reference for typical baud rates and system clock frequencies is given in Table 16.1 through Table 16.6. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

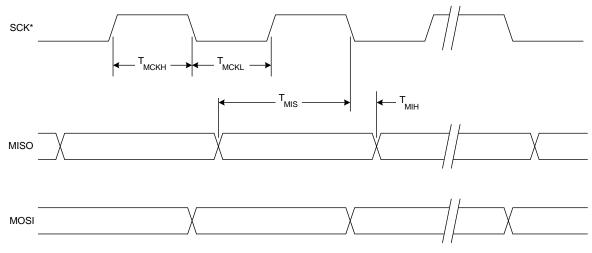

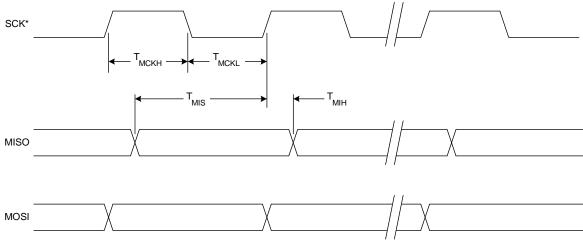

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

# Figure 17.9. SPI Master Timing (CKPHA = 1)

# SFR Definition 18.1. TCON: Timer Control

| R/W   | R/W                          | R/W          | R/W         | R/W           | R/W            | R/W           | R/W          | Reset Value   |

|-------|------------------------------|--------------|-------------|---------------|----------------|---------------|--------------|---------------|

| TF1   | TR1                          | TF0          | TR0         | IE1           | IT1            | IE0           | IT0          | 00000000      |

| Bit7  | Bit6                         | Bit5         | Bit4        | Bit3          | Bit2           | Bit1          | Bit0         | SFR Address   |

|       |                              |              |             |               |                | (bit addr     | essable)     | 0x88          |

|       |                              |              |             |               |                |               |              |               |

| Bit7: | TF1: Timer 1                 |              | -           |               |                |               |              |               |

|       | Set by hardw                 |              |             |               | -              | •             |              |               |

|       | matically clea               |              |             | ectors to the | Timer 1 int    | errupt servi  | ce routine   | •             |

|       | 0: No Timer                  |              |             |               |                |               |              |               |

| D'10  | 1: Timer 1 ha                |              |             |               |                |               |              |               |

| Bit6: | TR1: Timer 1                 |              | rol.        |               |                |               |              |               |

|       | 0: Timer 1 di                |              |             |               |                |               |              |               |

| Bit5: | 1: Timer 1 er                |              | Eloa        |               |                |               |              |               |

| DIIO. | TF0: Timer 0<br>Set by hardw |              | -           | offowe This   | flag can be    | cleared by    | coftware     | but is auto-  |

|       | matically clea               |              |             |               |                |               |              |               |

|       | 0: No Timer (                |              |             |               |                | chupt och h   |              | •             |

|       | 1: Timer 0 ha                |              |             |               |                |               |              |               |

| Bit4: | TR0: Timer 0                 |              |             |               |                |               |              |               |

|       | 0: Timer 0 di                | sabled.      |             |               |                |               |              |               |

|       | 1: Timer 0 er                | nabled.      |             |               |                |               |              |               |

| Bit3: | IE1: External                |              |             |               |                |               |              |               |

|       | This flag is s               |              |             |               |                |               |              |               |

|       | cleared by so                |              |             |               |                |               |              |               |

|       | Interrupt 1 se               |              |             |               |                | -             | ' when /IN   | IT1 is active |

| DVA   | as defined by                |              | -           | IT01CF (se    | e SFR Defir    | nition 9.11). |              |               |

| Bit2: | IT1: Interrupt               |              |             |               |                |               |              |               |

|       | This bit select              |              |             |               |                |               |              |               |

|       | is configured 9.11).         | active low   | or high by  |               | bit in the ITU | TCF registe   | er (see SF   | R Definition  |

|       | 9.11).<br>0: /INT1 is le     | vel triggere | d           |               |                |               |              |               |

|       | 1: /INT1 is e                |              |             |               |                |               |              |               |

| Bit1: | IE0: External                |              |             |               |                |               |              |               |

| Ditt. | This flag is s               | •            |             | n edae/leve   | el of type de  | fined by IT(  | ) is detecte | ed. It can be |

|       | cleared by so                |              |             |               |                |               |              |               |

|       | Interrupt 0 se               |              |             |               |                |               |              |               |

|       | as defined by                | y bit IN0PL  | in register | IT01CF (se    | e SFR Defir    | nition 9.11). |              |               |

| Bit0: | IT0: Interrupt               | t 0 Type Se  | elect.      |               |                |               |              |               |

|       | This bit seled               |              | •           |               |                | •             |              |               |

|       | is configured                | l active low | or high by  | the IN0PL b   | oit in registe | r IT01CF (s   | ee SFR D     | efinition     |

|       | 9.11).                       |              |             |               |                |               |              |               |

|       | 0: /INT0 is le               |              |             |               |                |               |              |               |

|       | 1: /INT0 is ed               | dge triggere | ed.         |               |                |               |              |               |

|       |                              |              |             |               |                |               |              |               |

# SFR Definition 18.13. TMR3CN: Timer 3 Control

| R/W   | R/W                                                                                                                                                                            | R/W          | R/W           | R/W          | R/W            | R             | R/W          | Reset Value  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|--------------|----------------|---------------|--------------|--------------|--|--|--|--|--|

| TF3H  | TF3L                                                                                                                                                                           | TF3LEN       | TF3CEN        | T3SPLIT      | TR3            |               | T3XCLK       | 00000000     |  |  |  |  |  |

| Bit7  | Bit6                                                                                                                                                                           | Bit5         | Bit4          | Bit3         | Bit2           | Bit1          | Bit0         | SFR Address: |  |  |  |  |  |

|       |                                                                                                                                                                                |              |               |              |                |               |              | 0x91         |  |  |  |  |  |

|       |                                                                                                                                                                                |              |               |              |                |               |              |              |  |  |  |  |  |

| Bit7: | TF3H: Time                                                                                                                                                                     |              |               |              |                |               |              |              |  |  |  |  |  |

|       | Set by hard                                                                                                                                                                    |              |               |              |                |               |              |              |  |  |  |  |  |

|       | this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is                                                                                    |              |               |              |                |               |              |              |  |  |  |  |  |

|       | enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine.<br>TE3H is not automatically cleared by hardware and must be cleared by software. |              |               |              |                |               |              |              |  |  |  |  |  |

| Bit6: | TF3H is not automatically cleared by hardware and must be cleared by software.<br>TF3L: Timer 3 Low Byte Overflow Flag.                                                        |              |               |              |                |               |              |              |  |  |  |  |  |

| Dito. | Set by hard                                                                                                                                                                    |              |               | •            | erflows fror   | n 0xFF to 0   | x00 When     | this bit is  |  |  |  |  |  |

|       | set, an interi                                                                                                                                                                 |              |               |              |                |               |              |              |  |  |  |  |  |

|       | will set wher                                                                                                                                                                  |              |               |              |                |               |              |              |  |  |  |  |  |

|       | ically cleared                                                                                                                                                                 |              |               | 0            |                |               |              |              |  |  |  |  |  |

| Bit5: | TF3LEN: Tir                                                                                                                                                                    |              |               |              |                |               |              |              |  |  |  |  |  |

|       | This bit enal                                                                                                                                                                  |              |               |              |                |               |              |              |  |  |  |  |  |

|       | rupts are en                                                                                                                                                                   |              |               | •            | d when the     | e low byte o  | f Timer 3 ov | /erflows.    |  |  |  |  |  |

|       | 0: Timer 3 L                                                                                                                                                                   | •            | •             |              |                |               |              |              |  |  |  |  |  |

| Bit4: | 1: Timer 3 L<br>TF3CEN: Ti                                                                                                                                                     | •            | •             |              | antura Engl    | hlo           |              |              |  |  |  |  |  |

| Dit4. | This bit enab                                                                                                                                                                  |              |               |              |                |               | Node If TE:  | RCEN is set  |  |  |  |  |  |

|       | and Timer 3                                                                                                                                                                    |              |               | •            | •              | •             |              |              |  |  |  |  |  |

|       | low-frequence                                                                                                                                                                  | •            |               | •            | -              |               |              |              |  |  |  |  |  |

|       | copied to TM                                                                                                                                                                   |              |               |              |                |               |              |              |  |  |  |  |  |

|       | details.                                                                                                                                                                       |              |               |              |                |               |              |              |  |  |  |  |  |