# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SCI, UART/USART                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                             |

| Number of I/O              | 29                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b SAR                                                                  |

| Oscillator Type            | External, Internal                                                             |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-LQFP                                                                        |

| Supplier Device Package    | 64-LFQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3694fpjv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

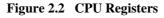

## 2.2 Register Configuration

The H8/300H CPU has the internal registers shown in figure 2.2. There are two types of registers; general registers and control registers. The control registers are a 24-bit program counter (PC), and an 8-bit condition code register (CCR).

|                                         | 15                            |          | 07   |                                         | 0 7                          | 0         |

|-----------------------------------------|-------------------------------|----------|------|-----------------------------------------|------------------------------|-----------|

| ER0                                     |                               | E0       |      | R0H                                     |                              | R0L       |

| ER1                                     |                               | E1       |      | R1H                                     |                              | R1L       |

| ER2                                     |                               | E2       |      | R2H                                     |                              | R2L       |

| ER3                                     |                               | E3       |      | R3H                                     |                              | R3L       |

| ER4                                     |                               | E4       |      | R4H                                     |                              | R4L       |

| ER5                                     |                               | E5       |      | R5H                                     |                              | R5L       |

| ER6                                     |                               | E6       |      | R6H                                     |                              | R6L       |

| ER7                                     |                               | E7       | (SP) | R7H                                     |                              | R7L       |

| Control F                               | Registers (CR)                | 23       | ·    |                                         |                              | C         |

| Control F                               |                               | 23<br>PC |      |                                         | 765                          | 4 3 2 1 0 |

| Control F                               |                               |          |      |                                         | 7 6 5<br>CCR 1 UIH           | 43210     |

| Control F                               |                               |          |      |                                         |                              | 43210     |

| [Legend]                                |                               |          | н    |                                         | CCR I UIH                    | 43210     |

| [Legend]<br>SP: St<br>PC: Pr            | ack pointer<br>rogram counter | PC       | U    | : Half-carr<br>: User bit               | CCR I UI H                   | 43210     |

| [Legend]<br>SP: St<br>PC: Pr<br>CCR: Co | ack pointer                   | PC       |      | : Half-carr<br>: User bit<br>: Negative | CCR I UI H<br>y flag<br>flag | 43210     |

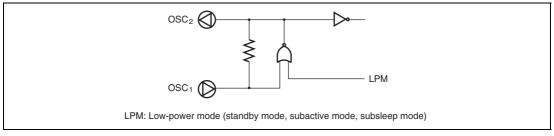

## 5.1 System Clock Generator

Clock pulses can be supplied to the system clock divider either by connecting a crystal or ceramic resonator, or by providing external clock input. Figure 5.2 shows a block diagram of the system clock generator.

Figure 5.2 Block Diagram of System Clock Generator

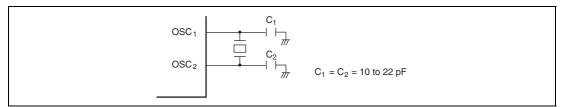

#### 5.1.1 Connecting Crystal Resonator

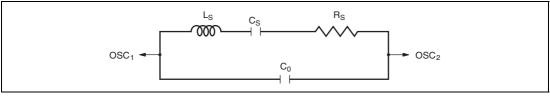

Figure 5.3 shows a typical method of connecting a crystal resonator. An AT-cut parallel-resonance crystal resonator should be used. Figure 5.4 shows the equivalent circuit of a crystal resonator. A resonator having the characteristics given in table 5.1 should be used.

Figure 5.4 Equivalent Circuit of Crystal Resonator

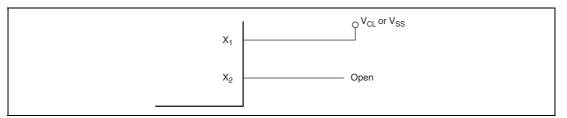

#### 5.2.2 Pin Connection when Not Using Subclock

When the subclock is not used, connect pin  $X_1$  to  $V_{cL}$  or  $V_{ss}$  and leave pin  $X_2$  open, as shown in figure 5.10.

#### 5.3 Prescalers

#### 5.3.1 Prescaler S

Prescaler S is a 13-bit counter using the system clock ( $\phi$ ) as its input clock. It is incremented once per clock period. Prescaler S is initialized to H'0000 by a reset, and starts counting on exit from the reset state. In standby mode, subactive mode, and subsleep mode, the system clock pulse generator stops. Prescaler S also stops and is initialized to H'0000. The CPU cannot read or write prescaler S. The output from prescaler S is shared by the on-chip peripheral modules. The divider ratio can be set separately for each on-chip peripheral function. In active mode and sleep mode, the clock input to prescaler S is determined by the division factor designated by MA2 to MA0 in SYSCR2.

#### 5.3.2 Prescaler W

Prescaler W is a 5-bit counter using a 32.768 kHz signal divided by 4 ( $\phi_w/4$ ) as its input clock. The divided output is used for clock time base operation of timer A. Prescaler W is initialized to H'00 by a reset, and starts counting on exit from the reset state. Even in standby mode, subactive mode, or subsleep mode, prescaler W continues functioning so long as clock signals are supplied to pins  $X_1$  and  $X_2$ . Prescaler W can be reset by setting 1s in bits TMA3 and TMA2 of timer mode register A (TMA).

#### 6.2.1 Sleep Mode

In sleep mode, CPU operation is halted but the on-chip peripheral modules function at the clock frequency set by the MA2, MA1, and MA0 bits in SYSCR2. CPU register contents are retained. When an interrupt is requested, sleep mode is cleared and interrupt exception handling starts. Sleep mode is not cleared if the I bit of the condition code register (CCR) is set to 1 or the requested interrupt is disabled in the interrupt enable register. After sleep mode is cleared, a transition is made to active mode when the LSON bit in SYSCR2 is 0, and a transition is made to subactive mode when the bit is 1.

When the  $\overline{\text{RES}}$  pin goes low, the CPU goes into the reset state and sleep mode is cleared.

#### 6.2.2 Standby Mode

In standby mode, the clock pulse generator stops, so the CPU and on-chip peripheral modules stop functioning. However, as long as the rated voltage is supplied, the contents of CPU registers, on-chip RAM, and some on-chip peripheral module registers are retained. On-chip RAM contents will be retained as long as the voltage set by the RAM data retention voltage is provided. The I/O ports go to the high-impedance state.

Standby mode is cleared by an interrupt. When an interrupt is requested, the system clock pulse generator starts. After the time set in bits STS2–STS0 in SYSCR1 has elapsed, and interrupt exception handling starts. Standby mode is not cleared if the I bit of CCR is set to 1 or the requested interrupt is disabled in the interrupt enable register.

When the  $\overline{\text{RES}}$  pin goes low, the system clock pulse generator starts. Since system clock signals are supplied to the entire chip as soon as the system clock pulse generator starts functioning, the  $\overline{\text{RES}}$  pin must be kept low until the pulse generator output stabilizes. After the pulse generator output has stabilized, the CPU starts reset exception handling if the  $\overline{\text{RES}}$  pin is driven high.

#### 6.2.3 Subsleep Mode

In subsleep mode, operation of the CPU and on-chip peripheral modules other than timer A is halted. As long as a required voltage is applied, the contents of CPU registers, the on-chip RAM, and some registers of the on-chip peripheral modules are retained. I/O ports keep the same states as before the transition.

Subsleep mode is cleared by an interrupt. When an interrupt is requested, subsleep mode is cleared and interrupt exception handling starts. Subsleep mode is not cleared if the I bit of CCR is set to 1 or the requested interrupt is disabled in the interrupt enable register. After subsleep mode is

# Section 7 ROM

The features of the 32-kbyte flash memory built into the flash memory version are summarized below.

- Programming/erase methods

- The flash memory is programmed 128 bytes at a time. Erase is performed in single-block units. The flash memory is configured as follows: 1 kbyte × 4 blocks and 28 kbytes × 1 block. To erase the entire flash memory, each block must be erased in turn.

- Reprogramming capability

- The flash memory can be reprogrammed up to 1,000 times.

- On-board programming

- On-board programming/erasing can be done in boot mode, in which the boot program built into the chip is started to erase or program of the entire flash memory. In normal user program mode, individual blocks can be erased or programmed.

- Programmer mode

- Flash memory can be programmed/erased in programmer mode using a PROM programmer, as well as in on-board programming mode.

- Automatic bit rate adjustment

- For data transfer in boot mode, this LSI's bit rate can be automatically adjusted to match the transfer bit rate of the host.

- Programming/erasing protection

- Sets software protection against flash memory programming/erasing.

- Power-down mode

- Operation of the power supply circuit can be partly halted in subactive mode. As a result, flash memory can be read with low power consumption.

## 7.1 Block Configuration

Figure 7.1 shows the block configuration of 32-kbyte flash memory. The thick lines indicate erasing units, the narrow lines indicate programming units, and the values are addresses. The flash memory is divided into 1 kbyte  $\times$  4 blocks and 28 kbytes  $\times$  1 block. Erasing is performed in these units. Programming is performed in 128-byte units starting from an address with lower eight bits H'00 or H'80.

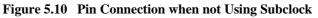

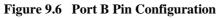

## 9.6 Port B

Port B is an input port also functioning as an A/D converter analog input pin. Each pin of the port B is shown in figure 9.6.

Port B has the following register.

• Port data register B (PDRB)

#### 9.6.1 Port Data Register B (PDRB)

PDRB is a general input-only port data register of port B.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                               |

|-----|----------|------------------|-----|-----------------------------------------------------------|

| 7   | PB7      | _                | R   | The input value of each pin is read by reading this       |

| 6   | PB6      | _                | R   | register.                                                 |

| 5   | PB5      |                  | R   | However, if a port B pin is designated as an analog input |

| 4   | PB4      | _                | R   | channel by ADCSR in A/D converter, 0 is read.             |

| 3   | PB3      | _                | R   |                                                           |

| 2   | PB2      | _                | R   |                                                           |

| 1   | PB1      | _                | R   |                                                           |

| 0   | PB0      | —                | R   |                                                           |

# 12.5 Operation Timing

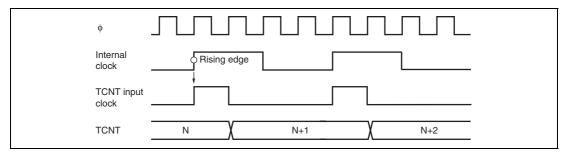

#### 12.5.1 TCNT Count Timing

Figure 12.14 shows the TCNT count timing when the internal clock source is selected. Figure 12.15 shows the timing when the external clock source is selected. The pulse width of the external clock signal must be at least two system clock ( $\phi$ ) cycles; shorter pulses will not be counted correctly.

Figure 12.14 Count Timing for Internal Clock Source

Figure 12.15 Count Timing for External Clock Source

#### 12.5.2 Output Compare Output Timing

The compare match signal is generated in the last state in which TCNT and GR match (when TCNT changes from the matching value to the next value). When the compare match signal is generated, the output value selected in TIOR is output at the compare match output pin (FTIOA, FTIOB, FTIOC, or FTIOD).

When TCNT matches GR, the compare match signal is generated only after the next counter clock pulse is input.

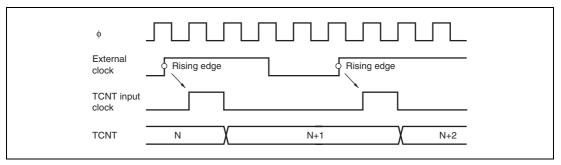

## 13.3 Operation

The watchdog timer is provided with an 8-bit counter. If 1 is written to WDON while writing 0 to B2WI when the TCSRWE bit in TCSRWD is set to 1, TCWD begins counting up. (To operate the watchdog timer, two write accesses to TCSRWD are required.) When a clock pulse is input after the TCWD count value has reached H'FF, the watchdog timer overflows and an internal reset signal is generated. The internal reset signal is output for a period of 256  $\phi_{osc}$  clock cycles. TCWD is a writable counter, and when a value is set in TCWD, the count-up starts from that value. An overflow period in the range of 1 to 256 input clock cycles can therefore be set, according to the TCWD set value.

Figure 13.2 shows an example of watchdog timer operation.

Figure 13.2 Watchdog Timer Operation Example

#### 14.3.8 Bit Rate Register (BRR)

BRR is an 8-bit register that adjusts the bit rate. The initial value of BRR is H'FF. Table 14.2 shows the relationship between the N setting in BRR and the n setting in bits CKS1 and CKS0 of SMR in asynchronous mode. Table 14.3 shows the maximum bit rate for each frequency in asynchronous mode. The values shown in both tables 14.2 and 14.3 are values in active (high-speed) mode. Table 14.4 shows the relationship between the N setting in BRR and the n setting in bits CKS1 and CKS0 in SMR in clocked synchronous mode. The values shown in table 14.4 are values in active (high-speed) mode. The N setting in BRR and error for other operating frequencies and bit rates can be obtained by the following formulas:

#### [Asynchronous Mode]

$$N = \frac{\phi}{64 \times 2^{2n-1} \times B} \times 10^6 - 1$$

Error (%) =

$$\left\{ \frac{\phi \times 10^6}{(N+1) \times B \times 64 \times 2^{2n-1}} - 1 \right\} \times 100$$

[Clocked Synchronous Mode]

$$N = \frac{\varphi}{8 \times 2^{2n-1} \times B} \times 10^6 - 1$$

Note: B: Bit rate (bit/s)

- N: BRR setting for baud rate generator ( $0 \le N \le 255$ )

- φ: Operating frequency (MHz)

- n: CKS1 and CKS0 setting for SMR ( $0 \le N \le 3$ )

## 14.4 Operation in Asynchronous Mode

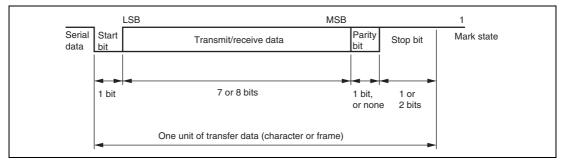

Figure 14.2 shows the general format for asynchronous serial communication. One frame consists of a start bit (low level), followed by data (in LSB-first order), a parity bit (high or low level), and finally stop bits (high level). Inside the SCI3, the transmitter and receiver are independent units, enabling full duplex. Both the transmitter and the receiver also have a double-buffered structure, so data can be read or written during transmission or reception, enabling continuous data transfer.

Figure 14.2 Data Format in Asynchronous Communication

#### 14.4.1 Clock

Either an internal clock generated by the on-chip baud rate generator or an external clock input at the SCK3 pin can be selected as the SCI3's serial clock source, according to the setting of the COM bit in SMR and the CKE0 and CKE1 bits in SCR3. When an external clock is input at the SCK3 pin, the clock frequency should be 16 times the bit rate used.

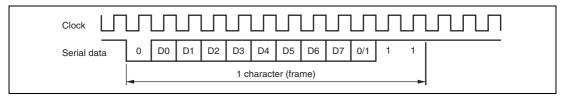

When the SCI3 is operated on an internal clock, the clock can be output from the SCK3 pin. The frequency of the clock output in this case is equal to the bit rate, and the phase is such that the rising edge of the clock is in the middle of the transmit data, as shown in figure 14.3.

Figure 14.3 Relationship between Output Clock and Transfer Data Phase (Asynchronous Mode) (Example with 8-Bit Data, Parity, Two Stop Bits)

RENESAS

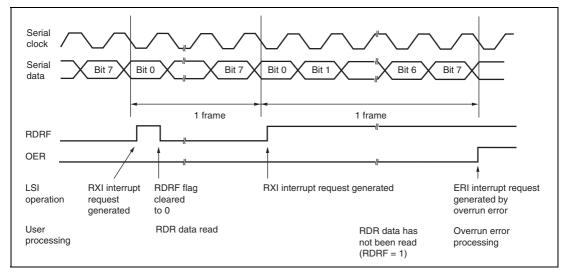

#### 14.5.4 Serial Data Reception (Clocked Synchronous Mode)

Figure 14.12 shows an example of SCI3 operation for reception in clocked synchronous mode. In serial reception, the SCI3 operates as described below.

- 1. The SCI3 performs internal initialization synchronous with a synchronous clock input or output, starts receiving data.

- 2. The SCI3 stores the received data in RSR.

- 3. If an overrun error occurs (when reception of the next data is completed while the RDRF flag in SSR is still set to 1), the OER bit in SSR is set to 1. If the RIE bit in SCR3 is set to 1 at this time, an ERI interrupt request is generated, receive data is not transferred to RDR, and the RDRF flag remains to be set to 1.

- 4. If reception is completed successfully, the RDRF bit in SSR is set to 1, and receive data is transferred to RDR. If the RIE bit in SCR3 is set to 1 at this time, an RXI interrupt request is generated.

Figure 14.12 Example of SCI3 Reception Operation in Clocked Synchronous Mode

Reception cannot be resumed while a receive error flag is set to 1. Accordingly, clear the OER, FER, PER, and RDRF bits to 0 before resuming reception. Figure 14.13 shows a sample flowchart for serial data reception.

#### 14.6.2 Multiprocessor Serial Data Reception

Figure 14.17 shows a sample flowchart for multiprocessor serial data reception. If the MPIE bit in SCR3 is set to 1, data is skipped until data with a 1 multiprocessor bit is received. On receiving data with a 1 multiprocessor bit, the receive data is transferred to RDR. An RXI interrupt request is generated at this time. All other SCI3 operations are the same as in asynchronous mode. Figure 14.18 shows an example of SCI3 operation for multiprocessor format reception.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5, 4 | _        | All 1            |     | Reserved                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|      |          |                  |     | These bits are always read as 1, and cannot be r                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 3    | BCWP     | 1                | R/W | BC Write Protect                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|      |          |                  |     | This bit controls the BC2 to BC0 modifications.<br>modifying BC2 to BC0, this bit should be cleare<br>use the MOV instruction. In clock synchronous<br>mode, BC should not be modified. |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|      |          |                  |     | 0: When writing, val                                                                                                                                                                    | ues of BC2 to BC0 are set.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|      |          |                  |     | 1: When reading, 1                                                                                                                                                                      | is always read.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|      |          |                  |     | When writing, set                                                                                                                                                                       | tings of BC2 to BC0 are invalid.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 2    | BC2      | 0                | R/W | Bit Counter 2 to 0                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 1    | BC1      | 0                | R/W |                                                                                                                                                                                         | ne number of bits to be transferred                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 0    | BC0      | 0                | R/W | indicated. With the I<br>with one addition ac<br>settings should be n<br>transfer frames. If bi<br>other than 000, the<br>SCL pin is low. The<br>data transfer, includ                  | e remaining number of transfer bits is ${}^{2}$ C bus format, the data is transferred knowledge bit. Bit BC2 to BC0 nade during an interval between its BC2 to BC0 are set to a value setting should be made while the value returns to 000 at the end of a ing the acknowledge bit. With the serial format, these bits should not be |  |  |  |  |

|      |          |                  |     | I <sup>2</sup> C Bus Format                                                                                                                                                             | Clock Synchronous Serial Format                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|      |          |                  |     | 000: 9 bits                                                                                                                                                                             | 000: 8 bits                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|      |          |                  |     | 001: 2 bits                                                                                                                                                                             | 001: 1 bits                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|      |          |                  |     | 010: 3 bits                                                                                                                                                                             | 010: 2 bits                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|      |          |                  |     | 011: 4 bits                                                                                                                                                                             | 011: 3 bits                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|      |          |                  |     | 100: 5 bits                                                                                                                                                                             | 100: 4 bits                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|      |          |                  |     | 101: 6 bits                                                                                                                                                                             | 101: 5 bits                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|      |          |                  |     | 110: 7 bits                                                                                                                                                                             | 110: 6 bits                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|      |          |                  |     | 111: 8 bits                                                                                                                                                                             | 111: 7 bits                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

# Section 16 A/D Converter

This LSI includes a successive approximation type 10-bit A/D converter that allows up to eight analog input channels to be selected. The block diagram of the A/D converter is shown in figure 16.1.

## 16.1 Features

- 10-bit resolution

- Eight input channels

- Conversion time: at least 3.5 µs per channel (at 20-MHz operation)

- Two operating modes

- Single mode: Single-channel A/D conversion

- Scan mode: Continuous A/D conversion on 1 to 4 channels

- Four data registers

- Conversion results are held in a data register for each channel

- Sample-and-hold function

- Two conversion start methods

- Software

- External trigger signal

- Interrupt request

- An A/D conversion end interrupt request (ADI) can be generated

## **16.3** Register Descriptions

The A/D converter has the following registers.

- A/D data register A (ADDRA)

- A/D data register B (ADDRB)

- A/D data register C (ADDRC)

- A/D data register D (ADDRD)

- A/D control/status register (ADCSR)

- A/D control register (ADCR)

Analog Input Channel

#### 16.3.1 A/D Data Registers A to D (ADDRA to ADDRD)

There are four 16-bit read-only ADDR registers; ADDRA to ADDRD, used to store the results of A/D conversion. The ADDR registers, which store a conversion result for each analog input channel, are shown in table 16.2.

The converted 10-bit data is stored in bits 15 to 6. The lower 6 bits are always read as 0.

The data bus width between the CPU and the A/D converter is 8 bits. The upper byte can be read directly from the CPU, however the lower byte should be read via a temporary register. The temporary register contents are transferred from the ADDR when the upper byte data is read. Therefore byte access to ADDR should be done by reading the upper byte first then the lower one. Word access is also possible. ADDR is initialized to H'0000.

#### Table 16.2 Analog Input Channels and Corresponding ADDR Registers

| Analogi | nput Channel |                                                          |

|---------|--------------|----------------------------------------------------------|

| Group 0 | Group 1      | A/D Data Register to Be Stored Results of A/D Conversion |

| AN0     | AN4          | ADDRA                                                    |

| AN1     | AN5          | ADDRB                                                    |

| AN2     | AN6          | ADDRC                                                    |

| AN3     | AN7          | ADDRD                                                    |

## 2. Arithmetic Instructions

|      |                   |              |     |    |      |           |             |     | le ai<br>i (by |        | ) |                                      |                |     |    |        | No. of<br>States <sup>*1</sup> |    |   |   |

|------|-------------------|--------------|-----|----|------|-----------|-------------|-----|----------------|--------|---|--------------------------------------|----------------|-----|----|--------|--------------------------------|----|---|---|

|      | Mnemonic          | Operand Size | #xx | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC)       | @ @ aa |   | Operation                            | Condition Code |     | с  | Normal | Advanced                       |    |   |   |

| ADD  | ADD.B #xx:8, Rd   | В            | 2   |    |      |           |             |     |                |        | - | $Rd8+#xx:8 \rightarrow Rd8$          | _              | \$  | \$ | 1      | \$                             | \$ |   | 2 |

|      | ADD.B Rs, Rd      | В            |     | 2  |      |           |             |     |                |        |   | $Rd8+Rs8 \rightarrow Rd8$            | -              | \$  | 1  | 1      | \$                             | \$ | 2 | 2 |

|      | ADD.W #xx:16, Rd  | W            | 4   |    |      |           |             |     |                |        |   | Rd16+#xx:16 $\rightarrow$ Rd16       | -              | (1) | 1  | 1      | \$                             | \$ | 4 | 4 |

|      | ADD.W Rs, Rd      | W            |     | 2  |      |           |             |     |                |        |   | Rd16+Rs16 $\rightarrow$ Rd16         | -              | (1) | 1  | \$     | \$                             | \$ | 2 | 2 |

|      | ADD.L #xx:32, ERd | L            | 6   |    |      |           |             |     |                |        |   | ERd32+#xx:32 →<br>ERd32              | -              | (2) | \$ | \$     | \$                             | \$ | e | 6 |

|      | ADD.L ERs, ERd    | L            |     | 2  |      |           |             |     |                |        |   | ERd32+ERs32 →<br>ERd32               | -              | (2) | \$ | \$     | \$                             | \$ | 2 | 2 |

| ADDX | ADDX.B #xx:8, Rd  | В            | 2   |    |      |           |             |     |                |        |   | $Rd8+#xx:8 + C \rightarrow Rd8$      | -              | \$  | 1  | (3)    | \$                             | Ĵ  | 2 | 2 |

|      | ADDX.B Rs, Rd     | В            |     | 2  |      |           |             |     |                |        |   | Rd8+Rs8 +C $\rightarrow$ Rd8         | -              | 1   | 1  | (3)    | 1                              | 1  | 2 | 2 |

| ADDS | ADDS.L #1, ERd    | L            |     | 2  |      |           |             |     |                |        |   | ERd32+1 $\rightarrow$ ERd32          | -              |     | _  | _      | -                              | -  | 2 | 2 |

|      | ADDS.L #2, ERd    | L            |     | 2  |      |           |             |     |                |        |   | $ERd32+2 \rightarrow ERd32$          | _              | -   | -  | -      | _                              | -  | 2 | 2 |

|      | ADDS.L #4, ERd    | L            |     | 2  |      |           |             |     |                |        |   | ERd32+4 $\rightarrow$ ERd32          | -              | -   | -  | —      | _                              | -  | 2 | 2 |

| INC  | INC.B Rd          | В            |     | 2  |      |           |             |     |                |        |   | $Rd8+1 \rightarrow Rd8$              | -              | -   | \$ | \$     | €                              | —  | 2 | 2 |

|      | INC.W #1, Rd      | W            |     | 2  |      |           |             |     |                |        |   | Rd16+1 $\rightarrow$ Rd16            | —              | -   | \$ | \$     | \$                             | —  | 2 | 2 |

|      | INC.W #2, Rd      | W            |     | 2  |      |           |             |     |                |        |   | Rd16+2 $\rightarrow$ Rd16            | —              | -   | \$ | \$     | \$                             | —  | 2 | 2 |

|      | INC.L #1, ERd     | L            |     | 2  |      |           |             |     |                |        |   | ERd32+1 $\rightarrow$ ERd32          | —              | -   | \$ | \$     | \$                             | —  | 2 | 2 |

|      | INC.L #2, ERd     | L            |     | 2  |      |           |             |     |                |        |   | $ERd32+2 \rightarrow ERd32$          | —              | -   | \$ | \$     | \$                             | —  | 2 | 2 |

| DAA  | DAA Rd            | В            |     | 2  |      |           |             |     |                |        |   | Rd8 decimal adjust $\rightarrow$ Rd8 | -              | *   | \$ | \$     | *                              | -  | 2 | 2 |

| SUB  | SUB.B Rs, Rd      | В            |     | 2  |      |           |             |     |                |        |   | $Rd8-Rs8 \rightarrow Rd8$            | —              | \$  | \$ | \$     | \$                             | \$ | 2 | 2 |

|      | SUB.W #xx:16, Rd  | W            | 4   |    |      |           |             |     |                |        |   | Rd16–#xx:16 $\rightarrow$ Rd16       | -              | (1) | \$ | \$     | \$                             | \$ | 4 | 4 |

|      | SUB.W Rs, Rd      | W            |     | 2  |      |           |             |     |                |        |   | Rd16–Rs16 $\rightarrow$ Rd16         | -              | (1) | \$ | \$     | \$                             | \$ | 2 | 2 |

|      | SUB.L #xx:32, ERd | L            | 6   |    |      |           |             |     |                |        |   | ERd32–#xx:32 $\rightarrow$ ERd32     | -              | (2) | \$ | \$     | \$                             | \$ | e | 6 |

|      | SUB.L ERs, ERd    | L            |     | 2  |      |           |             |     |                |        |   | ERd32–ERs32 $\rightarrow$ ERd32      | —              | (2) | \$ | \$     | $\uparrow$                     | \$ | 2 | 2 |

| SUBX | SUBX.B #xx:8, Rd  | В            | 2   |    |      |           |             |     |                |        |   | Rd8–#xx:8–C $\rightarrow$ Rd8        | —              | \$  | \$ | (3)    | \$                             | \$ | 2 | 2 |

|      | SUBX.B Rs, Rd     | В            |     | 2  |      |           |             |     |                |        |   | Rd8–Rs8–C $\rightarrow$ Rd8          | -              | \$  | \$ | (3)    | \$                             | \$ | 2 | 2 |

| SUBS | SUBS.L #1, ERd    | L            |     | 2  |      |           |             |     |                |        |   | ERd32–1 $\rightarrow$ ERd32          | —              | -   | -  | -      | —                              | -  | 2 | 2 |

|      | SUBS.L #2, ERd    | L            |     | 2  |      |           |             |     |                |        |   | ERd32–2 $\rightarrow$ ERd32          | -              | -   | -  | -      | —                              | -  | 2 | 2 |

|      | SUBS.L #4, ERd    | L            |     | 2  |      |           |             |     |                |        |   | ERd32–4 $\rightarrow$ ERd32          | -              | -   | -  | -      | —                              | -  | 2 | 2 |

| DEC  | DEC.B Rd          | В            |     | 2  |      |           |             |     |                |        |   | Rd8–1 $\rightarrow$ Rd8              | -              | -   | \$ | \$     | \$                             | -  | 2 | 2 |

|      | DEC.W #1, Rd      | W            |     | 2  |      |           |             |     |                |        |   | Rd16−1 → Rd16                        | -              | -   | \$ | \$     | $\uparrow$                     | -  | 2 | 2 |

|      | DEC.W #2, Rd      | W            |     | 2  |      |           |             |     |                |        |   | Rd16–2 $\rightarrow$ Rd16            | —              | -   | \$ | \$     | $\uparrow$                     | —  | 2 | 2 |

## 6. Branching Instructions

|     |                     |              |     |    |      |           |             |     | de ai<br>1 (by |     | ) |                                    |              |                |   |   |        |   |   | No<br>Stat | . of<br>es <sup>*1</sup> |

|-----|---------------------|--------------|-----|----|------|-----------|-------------|-----|----------------|-----|---|------------------------------------|--------------|----------------|---|---|--------|---|---|------------|--------------------------|

|     | Mnemonic            | Operand Size |     |    | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC)       | @aa |   | Oper                               | ation        | Condition Code |   |   | Normal |   |   |            |                          |

|     |                     | ď            | XX# | Rn | 0    | 0         | 0           | 0   | 0              | 0   | Ι |                                    | Condition    | Т              | н | N | z      | v | с | Ŷ          | Advanced                 |

| Bcc | BRA d:8 (BT d:8)    |              |     |    |      |           |             |     | 2              |     |   | If condition                       | Always       | _              | _ | _ | _      | _ | - | 4          | 4                        |

|     | BRA d:16 (BT d:16)  |              |     |    |      |           |             |     | 4              |     |   | is true then                       |              | _              | - | - | -      | - | - | (          | 6                        |

|     | BRN d:8 (BF d:8)    | _            |     |    |      |           |             |     | 2              |     |   | $PC \leftarrow PC+d$<br>else next: | Never        | _              | - | - | -      | _ | - | 4          | 4                        |

|     | BRN d:16 (BF d:16)  | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | _              | - | - | _      | _ | - | (          | 6                        |

|     | BHI d:8             | —            |     |    |      |           |             |     | 2              |     |   |                                    | C∨ Z = 0     | _              |   | - | -      | - | - | 4          | 4                        |

|     | BHI d:16            | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | _              | - | - | -      | - | — | 6          | 6                        |

|     | BLS d:8             | —            |     |    |      |           |             |     | 2              |     |   |                                    | C∨ Z = 1     | -              | - | - | -      | - | - | 4          | 4                        |

|     | BLS d:16            | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | -              | - | - | -      | - |   | (          | 6                        |

|     | BCC d:8 (BHS d:8)   | _            |     |    |      |           |             |     | 2              |     |   |                                    | C = 0        | -              | - | - | -      | - | - | 4          | 4                        |

|     | BCC d:16 (BHS d:16) | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | -              | - | - | -      | - | - | (          | 6                        |

|     | BCS d:8 (BLO d:8)   | _            |     |    |      |           |             |     | 2              |     |   |                                    | C = 1        | -              | - | - | -      | - | - | 4          | 4                        |

|     | BCS d:16 (BLO d:16) | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | -              | - | - | -      | - | - | (          | 6                        |

|     | BNE d:8             | _            |     |    |      |           |             |     | 2              |     |   |                                    | Z = 0        | _              | - | - | -      | - | - | 4          | 4                        |

|     | BNE d:16            | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | —              | - | - | -      | - | - | (          | 6                        |

|     | BEQ d:8             | _            |     |    |      |           |             |     | 2              |     |   |                                    | Z = 1        | —              | - | - | -      | — | - | 4          | 4                        |

|     | BEQ d:16            | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | -              | - | - | -      | - | - | (          | 6                        |

|     | BVC d:8             | _            |     |    |      |           |             |     | 2              |     |   |                                    | V = 0        | _              | - | - | -      | - | - | 4          | 4                        |

|     | BVC d:16            | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | -              | - | - | -      | - | - | (          | 6                        |

|     | BVS d:8             | _            |     |    |      |           |             |     | 2              |     |   |                                    | V = 1        | —              | - | - | -      | — | - | 4          | 4                        |

|     | BVS d:16            | _            |     |    |      |           |             |     | 4              |     |   |                                    |              | -              | - | - | -      | - | - | (          | 6                        |

|     | BPL d:8             | -            |     |    |      |           |             |     | 2              |     |   |                                    | N = 0        | -              | - | - | -      | - | - | 4          | 4                        |

|     | BPL d:16            | -            |     |    |      |           |             |     | 4              |     |   | ]                                  |              | —              | - | - | -      | - | - | (          | 6                        |

|     | BMI d:8             | -            |     |    |      |           |             |     | 2              |     |   | ]                                  | N = 1        | -              | - | - | -      | - | - | 4          | 4                        |

|     | BMI d:16            | —            |     |    |      |           |             |     | 4              |     |   | 1                                  |              | —              | - | - | -      | - | - | (          | 6                        |

|     | BGE d:8             | —            |     |    |      |           |             |     | 2              |     |   | 1                                  | N⊕V = 0      | -              | - | - | -      | - | - | 4          | 4                        |

|     | BGE d:16            | -            |     |    |      |           |             |     | 4              |     |   |                                    |              | —              | - | - | -      | - | - | (          | 6                        |

|     | BLT d:8             | -            |     |    |      |           |             |     | 2              |     |   | 1                                  | N⊕V = 1      | -              | - | - | -      | - | - | 4          | 4                        |

|     | BLT d:16            | -            |     |    |      |           |             |     | 4              |     |   | 1                                  |              | -              | - | - | -      | - | - | (          | 6                        |

|     | BGT d:8             | —            |     |    |      |           |             |     | 2              |     |   | 1                                  | Z∨ (N⊕V) = 0 | -              | - | - | -      | - | - | 4          | 4                        |

|     | BGT d:16            | -            |     |    |      |           |             |     | 4              |     |   | 1                                  |              | -              | - | - | -      | - | - | (          | 6                        |

|     | BLE d:8             | -            |     |    |      |           |             |     | 2              |     |   | 1                                  | Z∨ (N⊕V) = 1 | -              | - | - | -      | - | - | 4          | 4                        |

|     | BLE d:16            | _            |     |    |      |           |             |     | 4              |     |   | 1                                  |              | -              | - | _ | _      | - | - | (          | 6                        |

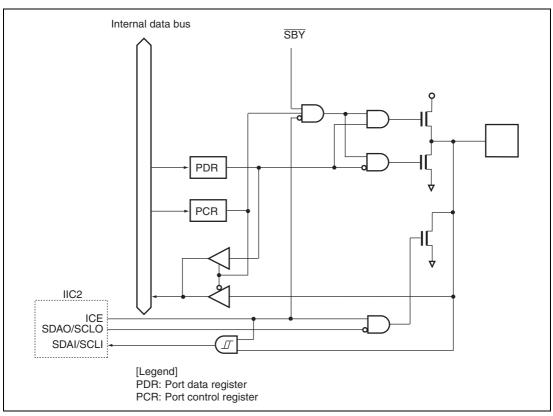

Figure B.8 Port 5 Block Diagram (P57, P56)\*

Note: \* This diagram is applied to the SCL and SDA pins in the H8/3694N.

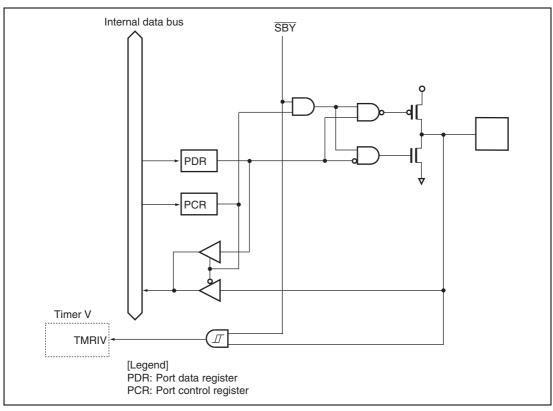

Figure B.13 Port 7 Block Diagram (P74)

| Item                                                                 | Page          | Revision (S           | See Manu        | ual for Detai                   | ls)                                      |                     |

|----------------------------------------------------------------------|---------------|-----------------------|-----------------|---------------------------------|------------------------------------------|---------------------|

| Table 21.2 DC                                                        | 321           | Mode                  |                 | <b>RES</b> Pin                  | Internal Stat                            | e                   |

| Characteristics (1)                                                  |               | Active mod            | e 1             | V <sub>cc</sub>                 | Operates                                 |                     |

|                                                                      |               | Active mod            | e 2             | _                               | Operates<br>(¢OSC/64)                    |                     |

|                                                                      |               | Sleep mode            | ə 1             | V <sub>cc</sub>                 | Only timers of                           | operate             |

|                                                                      |               | Sleep mod             | e 2             | -                               | Only timers o<br>(¢OSC/64)               | operate             |

| Table 21.12 DC                                                       | 337           |                       |                 | Applicable                      |                                          | Values              |

| Characteristics (1)                                                  |               | Item                  | Symbol          |                                 | Test Condition                           | Min                 |

|                                                                      |               | Input high<br>voltage | V <sub>IH</sub> | PB0 to PB7                      | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | $V_{cc} \times 0.7$ |

|                                                                      |               |                       |                 |                                 |                                          | $V_{cc} \times 0.8$ |

|                                                                      |               | Input low<br>voltage  | V <sub>IL</sub> | RXD, SCL,<br>SDA<br>P10 to P12, | $V_{cc} = 4.0$ to 5.5 V                  | -0.3                |

|                                                                      |               |                       |                 | :                               |                                          | -0.3                |

|                                                                      |               |                       |                 | P80 to P87<br>PB0 to PB7        |                                          |                     |

|                                                                      | 340           | Mode                  |                 | RES Pin                         | Internal Stat                            | e                   |

|                                                                      |               | Active mod            | e 1             | V <sub>cc</sub>                 | Operates                                 |                     |

|                                                                      |               | Active mod            | e 2             | _                               | Operates<br>(¢OSC/64)                    |                     |

|                                                                      |               | Sleep mode            | ə 1             | V <sub>cc</sub>                 | Only timers of                           | operate             |

|                                                                      |               | Sleep mode            | ə 2             | -                               | Only timers α<br>(φOSC/64)               | operate             |

| Figure 21.4 I <sup>2</sup> C Bus<br>Interface Input/Output<br>Timing | 352           |                       | SCL             | P* S*                           |                                          |                     |

| Appendix D Package<br>Dimensions                                     | 405 to<br>409 | Swapped w             | ith new o       | nes.                            |                                          |                     |