#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20MHz                                                                         |

| Connectivity               | I²C, SCI                                                                      |

| Peripherals                | PWM, WDT                                                                      |

| Number of I/O              | 29                                                                            |

| Program Memory Size        | 32KB (32K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-VFQFN                                                                      |

| Supplier Device Package    | 48-VQFN (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3694ftv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.4 Pin Functions

## Table 1.1Pin Functions

|                   |                   | Pin                 | No.                        |        |                                                                                                                                       |  |  |  |

|-------------------|-------------------|---------------------|----------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Туре              | Symbol            | FP-64E<br>FP-64A    | FP-48F<br>FP-48B<br>TNP-48 | I/O    | Functions                                                                                                                             |  |  |  |

| Power<br>source   | $V_{cc}$          | 12                  | 10                         | Input  | Power supply pin. Connect this pin to the system power supply.                                                                        |  |  |  |

| pins              | V <sub>ss</sub> 9 |                     | 7                          | Input  | Ground pin. Connect this pin to the system power supply (0V).                                                                         |  |  |  |

|                   | AV <sub>cc</sub>  | 3                   | 1                          | Input  | Analog power supply pin for the A/D converter.<br>When the A/D converter is not used, connect<br>this pin to the system power supply. |  |  |  |

|                   | V <sub>cL</sub>   | 6                   | 4                          | Input  | Internal step-down power supply pin. Connect a capacitor of around 0.1 $\mu F$ between this pin and the Vss pin for stabilization.    |  |  |  |

| Clock             | OSC1              | 11                  | 9                          | Input  | These pins connect with crystal or ceramic                                                                                            |  |  |  |

| pins              | OSC2              | 10                  | 8                          | Output | resonator for the system clock, or can be used<br>to input an external clock.                                                         |  |  |  |

|                   |                   |                     |                            |        | See section 5, Clock Pulse Generators, for a typical connection.                                                                      |  |  |  |

|                   | X1                | 5                   | 3                          | Input  | These pins connect with a 32.768 kHz crystal                                                                                          |  |  |  |

|                   | X2                | 4                   | 2                          | Output | resonator for the subclock. See section 5,<br>Clock Pulse Generators, for a typical<br>connection.                                    |  |  |  |

| System control    | RES               | 7                   | 5                          | Input  | Reset pin. The pull-up resistor (typ. 150 k $\Omega$ ) is incorporated. When driven low, the chip is reset.                           |  |  |  |

|                   | TEST              | 8                   | 6                          | Input  | Test pin. Connect this pin to Vss.                                                                                                    |  |  |  |

| Interrupt<br>pins | NMI               | 35                  | 25                         | Input  | Non-maskable interrupt request input pin. Be sure to pull-up by a pull-up resistor.                                                   |  |  |  |

|                   | IRQ0 to<br>IRQ3   | 51 to 54            | 37 to 40                   | Input  | External interrupt request input pins. Can select the rising or falling edge.                                                         |  |  |  |

|                   | WKP0 to<br>WKP5   | 13, 14,<br>19 to 22 | 11 to 16                   | Input  | External interrupt request input pins. Can select the rising or falling edge.                                                         |  |  |  |

## 2.2 Register Configuration

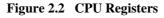

The H8/300H CPU has the internal registers shown in figure 2.2. There are two types of registers; general registers and control registers. The control registers are a 24-bit program counter (PC), and an 8-bit condition code register (CCR).

| ER0         E0           ER1         E1           ER2         E2           ER3         E3           ER4         E4           ER5         E5           ER6         E6 |      | R0H<br>R1H<br>R2H<br>R3H<br>R4H | R0L<br>R1L<br>R2L<br>R3L<br>R4L |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------|---------------------------------|

| ER2         E2           ER3         E3           ER4         E4           ER5         E5                                                                            |      | R2H<br>R3H                      | R2L<br>R3L                      |

| ER3 E3<br>ER4 E4<br>ER5 E5                                                                                                                                           |      | R3H                             | R3L                             |

| ER4 E4<br>ER5 E5                                                                                                                                                     |      | _                               |                                 |

| ER5 E5                                                                                                                                                               |      | R4H                             | B4I                             |

|                                                                                                                                                                      |      |                                 | ⊓4∟                             |

| ER6 E6                                                                                                                                                               |      | R5H                             | R5L                             |

| -                                                                                                                                                                    |      | R6H                             | R6L                             |

| ER7 E7                                                                                                                                                               | (SP) | R7H                             | R7L                             |

| PC                                                                                                                                                                   |      |                                 | 76543210                        |

|                                                                                                                                                                      |      | CC                              | RUUHUNZVC                       |

| 11                                                                                                                                                                   |      |                                 |                                 |

| [Legend]                                                                                                                                                             |      | J. Holf corru fl                | 20                              |

| SP: Stack pointer                                                                                                                                                    | F    | ,                               | ay                              |

| SP: Stack pointer<br>PC: Program counter                                                                                                                             | L    | J: User bit                     | -                               |

| SP: Stack pointer                                                                                                                                                    | L    | ,                               | -                               |

an input pin by the BCLR instruction is shown below. It is assumed that a high-level signal will be input to this input pin.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

• Prior to executing BCLR instruction

#### • BCLR instruction executed

BCLR #0, @PCR5

The BCLR instruction is executed for PCR5.

### • After executing BCLR instruction

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50           |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Input/output | Output       | Output        | Output       | Output       | Output       | Output       | Output       | Input         |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | High<br>level |

| PCR5         | 1            | 1             | 1            | 1            | 1            | 1            | 1            | 0             |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0             |

- Description on operation

- 1. When the BCLR instruction is executed, first the CPU reads PCR5. Since PCR5 is a write-only register, the CPU reads a value of H'FF, even though the PCR5 value is actually H'3F.

- 2. Next, the CPU clears bit 0 in the read data to 0, changing the data to H'FE.

- 3. Finally, H'FE is written to PCR5 and BCLR instruction execution ends.

As a result of this operation, bit 0 in PCR5 becomes 0, making P50 an input port. However, bits 7 and 6 in PCR5 change to 1, so that P57 and P56 change from input pins to output pins. To prevent this problem, store a copy of the PDR5 data in a work area in memory and manipulate data of the bit in the work area, then write this data to PDR5.

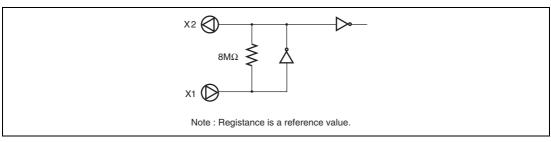

## 5.2 Subclock Generator

Figure 5.7 shows a block diagram of the subclock generator.

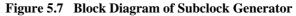

#### 5.2.1 Connecting 32.768-kHz Crystal Resonator

Clock pulses can be supplied to the subclock divider by connecting a 32.768-kHz crystal resonator, as shown in figure 5.8. Figure 5.9 shows the equivalent circuit of the 32.768-kHz crystal resonator.

$$X_{1}$$

$$X_{2}$$

$$X_{2}$$

$$C_{1}$$

$$C_{2}$$

$$C_{1} = C_{2} = 15 \text{ pF (typ.)}$$

Figure 5.8 Typical Connection to 32.768-kHz Crystal Resonator

Figure 5.9 Equivalent Circuit of 32.768-kHz Crystal Resonator

| DTON | SSBY | SMSEL | LSON | Transition Mode after<br>SLEEP Instruction<br>Execution | Transition Mode due to<br>Interrupt |

|------|------|-------|------|---------------------------------------------------------|-------------------------------------|

| 0    | 0    | 0     | 0    | Sleep mode                                              | Active mode                         |

|      |      |       | 1    |                                                         | Subactive mode                      |

|      |      | 1     | 0    | Subsleep mode                                           | Active mode                         |

|      |      |       | 1    | _                                                       | Subactive mode                      |

|      | 1    | Х     | Х    | Standby mode                                            | Active mode                         |

| 1    | Х    | 0*    | 0    | Active mode (direct transition)                         | _                                   |

|      | Х    | Х     | 1    | Subactive mode (direct transition)                      | _                                   |

## Table 6.2 Transition Mode after SLEEP Instruction Execution and Interrupt Handling

Legend: X : Don't care.

\* When a state transition is performed while SMSEL is 1, timer V, SCI3, and the A/D converter are reset, and all registers are set to their initial values. To use these functions after entering active mode, reset the registers.

## 6.4 Direct Transition

The CPU can execute programs in two modes: active and subactive mode. A direct transition is a transition between these two modes without stopping program execution. A direct transition can be made by executing a SLEEP instruction while the DTON bit in SYSCR2 is set to 1. The direct transition also enables operating frequency modification in active or subactive mode. After the mode transition, direct transition interrupt exception handling starts.

If the direct transition interrupt is disabled in interrupt enable register 1, a transition is made instead to sleep or subsleep mode. Note that if a direct transition is attempted while the I bit in CCR is set to 1, sleep or subsleep mode will be entered, and the resulting mode cannot be cleared by means of an interrupt.

## 6.4.1 Direct Transition from Active Mode to Subactive Mode

The time from the start of SLEEP instruction execution to the end of interrupt exception handling (the direct transition time) is calculated by equation (1).

Direct transition time = {(number of SLEEP instruction execution states) + (number of internal processing states)} (tcyc before transition) + (number of interrupt exception handling states) (tsubcyc after transition) (1)

## Example

Direct transition time =  $(2 + 1) \times \text{tosc} + 14 \times 8\text{tw} = 3\text{tosc} + 112\text{tw}$ (when the CPU operating clock of  $\phi_{osc} \rightarrow \phi_w/8$  is selected)

## Legend

tosc: OSC clock cycle time tw: watch clock cycle time tcyc: system clock ( $\phi$ ) cycle time tsubcyc: subclock ( $\phi_{sub}$ ) cycle time

## 6.4.2 Direct Transition from Subactive Mode to Active Mode

The time from the start of SLEEP instruction execution to the end of interrupt exception handling (the direct transition time) is calculated by equation (2).

Direct transition time = {(number of SLEEP instruction execution states) + (number of internal processing states)}  $\times$  (tsubcyc before transition) + {(waiting time set in bits STS2 to STS0) + (number of interrupt exception handling states)}  $\times$  (tcyc after transition) (2)

RENESAS

### 9.1.2 Port Control Register 1 (PCR1)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                    |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------|

| 7   | PCR17    | 0                | W   | When the corresponding pin is designated in PMR1 as a                                                          |

| 6   | PCR16    | 0                | W   | general I/O pin, setting a PCR1 bit to 1 makes the corresponding pin an output port, while clearing the bit to |

| 5   | PCR15    | 0                | W   | 0 makes the pin an input port.                                                                                 |

| 4   | PCR14    | 0                | W   | Bit 3 is a reserved bit.                                                                                       |

| 3   | —        |                  |     |                                                                                                                |

| 2   | PCR12    | 0                | W   |                                                                                                                |

| 1   | PCR11    | 0                | W   |                                                                                                                |

| 0   | PCR10    | 0                | W   |                                                                                                                |

PCR1 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 1.

### 9.1.3 Port Data Register 1 (PDR1)

PDR1 is a general I/O port data register of port 1.

|     |          | Initial |     |                                                                                   |

|-----|----------|---------|-----|-----------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                       |

| 7   | P17      | 0       | R/W | PDR1 stores output data for port 1 pins.                                          |

| 6   | P16      | 0       | R/W | If PDR1 is read while PCR1 bits are set to 1, the value                           |

| 5   | P15      | 0       | R/W | stored in PDR1 are read. If PDR1 is read while PCR1 bits                          |

| 4   | P14      | 0       | R/W | are cleared to 0, the pin states are read regardless of the value stored in PDR1. |

| 3   | —        | 1       |     | Bit 3 is a reserved bit. This bit is always read as 1.                            |

| 2   | P12      | 0       | R/W |                                                                                   |

| 1   | P11      | 0       | R/W |                                                                                   |

| 0   | P10      | 0       | R/W |                                                                                   |

### 9.2.1 Port Control Register 2 (PCR2)

Initial Bit **Bit Name** Value R/W Description 7 to 3 Reserved \_\_\_\_ 2 PCR22 W When each of the port 2 pins P22 to P20 functions as an 0 general I/O port, setting a PCR2 bit to 1 makes the 1 PCR21 0 W corresponding pin an output port, while clearing the bit to 0 PCR20 0 W 0 makes the pin an input port.

PCR2 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 2.

#### 9.2.2 Port Data Register 2 (PDR2)

PDR2 is a general I/O port data register of port 2.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                               |

|--------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3 | —        | All 1            | —   | Reserved                                                                                                                                  |

|        |          |                  |     | These bits are always read as 1.                                                                                                          |

| 2      | P22      | 0                | R/W | PDR2 stores output data for port 2 pins.                                                                                                  |

| 1      | P21      | 0                | R/W | If PDR2 is read while PCR2 bits are set to 1, the value                                                                                   |

| 0      | P20      | 0                | R/W | stored in PDR2 is read. If PDR2 is read while PCR2 bits are cleared to 0, the pin states are read regardless of the value stored in PDR2. |

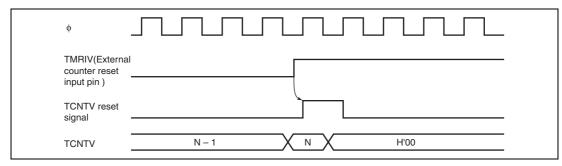

Figure 11.8 Clear Timing by TMRIV Input

|                     |   |     |              |   | Operat | ing Fre      | quene | су ф (МН | z)           |   |     |              |  |

|---------------------|---|-----|--------------|---|--------|--------------|-------|----------|--------------|---|-----|--------------|--|

|                     |   | 6   |              |   | 6.144  |              |       | 7.3728   |              |   | 8   |              |  |

| Bit Rate<br>(bit/s) | n | N   | Error<br>(%) | n | N      | Error<br>(%) | n     | N        | Error<br>(%) | n | N   | Error<br>(%) |  |

| 110                 | 2 | 106 | -0.44        | 2 | 108    | 0.08         | 2     | 130      | -0.07        | 2 | 141 | 0.03         |  |

| 150                 | 2 | 77  | 0.16         | 2 | 79     | 0.00         | 2     | 95       | 0.00         | 2 | 103 | 0.16         |  |

| 300                 | 1 | 155 | 0.16         | 1 | 159    | 0.00         | 1     | 191      | 0.00         | 1 | 207 | 0.16         |  |

| 600                 | 1 | 77  | 0.16         | 1 | 79     | 0.00         | 1     | 95       | 0.00         | 1 | 103 | 0.16         |  |

| 1200                | 0 | 155 | 0.16         | 0 | 159    | 0.00         | 0     | 191      | 0.00         | 0 | 207 | 0.16         |  |

| 2400                | 0 | 77  | 0.16         | 0 | 79     | 0.00         | 0     | 95       | 0.00         | 0 | 103 | 0.16         |  |

| 4800                | 0 | 38  | 0.16         | 0 | 39     | 0.00         | 0     | 47       | 0.00         | 0 | 51  | 0.16         |  |

| 9600                | 0 | 19  | -2.34        | 0 | 19     | 0.00         | 0     | 23       | 0.00         | 0 | 25  | 0.16         |  |

| 19200               | 0 | 9   | -2.34        | 0 | 9      | 0.00         | 0     | 11       | 0.00         | 0 | 12  | 0.16         |  |

| 31250               | 0 | 5   | 0.00         | 0 | 5      | 2.40         | 0     | 6        | 5.33         | 0 | 7   | 0.00         |  |

| 38400               | 0 | 4   | -2.34        | 0 | 4      | 0.00         | 0     | 5        | 0.00         | 0 | 6   | -6.99        |  |

## Table 14.2 Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (2)

### Operating Frequency $\phi$ (MHz)

|                     |   | 9.830 | 4            |   | 10  |              |   | 12  |              |   | 12.88 | 8            |

|---------------------|---|-------|--------------|---|-----|--------------|---|-----|--------------|---|-------|--------------|

| Bit Rate<br>(bit/s) | n | N     | Error<br>(%) | n | Ν   | Error<br>(%) | n | N   | Error<br>(%) | n | N     | Error<br>(%) |

| 110                 | 2 | 174   | -0.26        | 2 | 177 | -0.25        | 2 | 212 | 0.03         | 2 | 217   | 0.08         |

| 150                 | 2 | 127   | 0.00         | 2 | 129 | 0.16         | 2 | 155 | 0.16         | 2 | 159   | 0.00         |

| 300                 | 1 | 255   | 0.00         | 2 | 64  | 0.16         | 2 | 77  | 0.16         | 2 | 79    | 0.00         |

| 600                 | 1 | 127   | 0.00         | 1 | 129 | 0.16         | 1 | 155 | 0.16         | 1 | 159   | 0.00         |

| 1200                | 0 | 255   | 0.00         | 1 | 64  | 0.16         | 1 | 77  | 0.16         | 1 | 79    | 0.00         |

| 2400                | 0 | 127   | 0.00         | 0 | 129 | 0.16         | 0 | 155 | 0.16         | 0 | 159   | 0.00         |

| 4800                | 0 | 63    | 0.00         | 0 | 64  | 0.16         | 0 | 77  | 0.16         | 0 | 79    | 0.00         |

| 9600                | 0 | 31    | 0.00         | 0 | 32  | -1.36        | 0 | 38  | 0.16         | 0 | 39    | 0.00         |

| 19200               | 0 | 15    | 0.00         | 0 | 15  | 1.73         | 0 | 19  | -2.34        | 0 | 19    | 0.00         |

| 31250               | 0 | 9     | -1.70        | 0 | 9   | 0.00         | 0 | 11  | 0.00         | 0 | 11    | 2.40         |

| 38400               | 0 | 7     | 0.00         | 0 | 7   | 1.73         | 0 | 9   | -2.34        | 0 | 9     | 0.00         |

# Section 15 I<sup>2</sup>C Bus Interface 2 (IIC2)

The I<sup>2</sup>C bus interface 2 conforms to and provides a subset of the Philips I<sup>2</sup>C bus (inter-IC bus) interface functions. The register configuration that controls the I<sup>2</sup>C bus differs partly from the Philips configuration, however.

Figure 15.1 shows a block diagram of the I<sup>2</sup>C bus interface 2.

Figure 15.2 shows an example of I/O pin connections to external circuits.

## 15.1 Features

- Selection of I<sup>2</sup>C format or clocked synchronous serial format

- Continuous transmission/reception

Since the shift register, transmit data register, and receive data register are independent from each other, the continuous transmission/reception can be performed.

I<sup>2</sup>C bus format

- Start and stop conditions generated automatically in master mode

- Selection of acknowledge output levels when receiving

- Automatic loading of acknowledge bit when transmitting

- Bit synchronization/wait function

In master mode, the state of SCL is monitored per bit, and the timing is synchronized automatically.

If transmission/reception is not yet possible, set the SCL to low until preparations are completed.

• Six interrupt sources

Transmit data empty (including slave-address match), transmit end, receive data full (including slave-address match), arbitration lost, NACK detection, and stop condition detection

• Direct bus drive

Two pins, SCL and SDA pins, function as NMOS open-drain outputs when the bus drive function is selected.

Clocked synchronous format

• Four interrupt sources

Transmit-data-empty, transmit-end, receive-data-full, and overrun error

## 15.4 Operation

The  $I^2C$  bus interface can communicate either in  $I^2C$  bus mode or clocked synchronous serial mode by setting FS in SAR.

### 15.4.1 I<sup>2</sup>C Bus Format

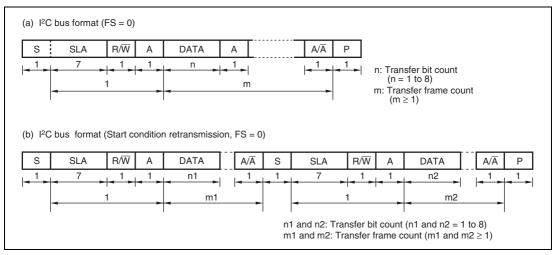

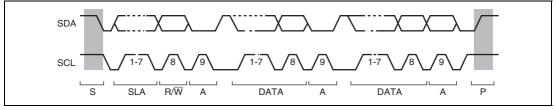

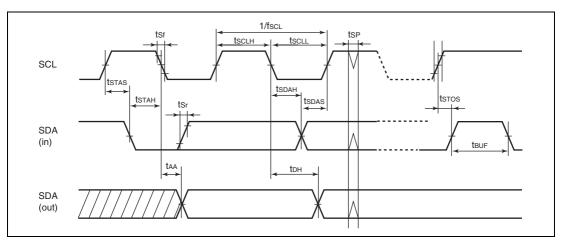

Figure 15.3 shows the  $I^2C$  bus formats. Figure 15.4 shows the  $I^2C$  bus timing. The first frame following a start condition always consists of 8 bits.

Figure 15.3 I<sup>2</sup>C Bus Formats

Figure 15.4 I<sup>2</sup>C Bus Timing

RENESAS

## Legend

S: Start condition. The master device drives SDA from high to low while SCL is high.

SLA: Slave address

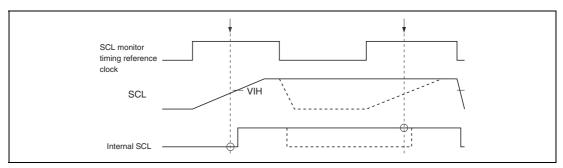

## 15.6 Bit Synchronous Circuit

In master mode, this module has a possibility that high level period may be short in the two states described below.

- When SCL is driven to low by the slave device

- When the rising speed of SCL is lowered by the load of the SCL line (load capacitance or pullup resistance)

Therefore, it monitors SCL and communicates by bit with synchronization.

Figure 15.21 shows the timing of the bit synchronous circuit and table 15.4 shows the time when SCL output changes from low to Hi-Z then SCL is monitored.

Figure 15.21 The Timing of the Bit Synchronous Circuit

| <b>Table 15.4</b> | Time | for | Monitoring | SCL |

|-------------------|------|-----|------------|-----|

|-------------------|------|-----|------------|-----|

| CKS3 | CKS2 | Time for Monitoring SCL |

|------|------|-------------------------|

| 0    | 0    | 7.5 tcyc                |

|      | 1    | 19.5 tcyc               |

| 1    | 0    | 17.5 tcyc               |

|      | 1    | 41.5 tcyc               |

## 17.5 Usage Notes

## 17.5.1 Data Protection at $V_{cc}$ On/Off

When  $V_{cc}$  is turned on or off, the data might be destroyed by malfunction. Be careful of the notices described below to prevent the data to be destroyed.

- 1. SCL and SDA should be fixed to  $V_{cc}$  or  $V_{ss}$  during  $V_{cc}$  on/off.

- 2.  $V_{cc}$  should be turned off after the EEPROM is placed in a standby state.

- 3. When  $V_{cc}$  is turned on from the intermediate level, malfunction is caused, so  $V_{cc}$  should be turned on from the ground level ( $V_{ss}$ ).

- 4.  $V_{cc}$  turn on speed should be longer than 10 us.

## 17.5.2 Write/Erase Endurance

The endurance is  $10^5$  cycles/page (1% cumulative failure rate) in case of page programming and  $10^4$  cycles/byte in case of byte programming. The data retention time is more than 10 years when a device is page-programmed less than  $10^4$  cycles.

## 17.5.3 Noise Suppression Time

This EEPROM has a noise suppression function at SCL and SDA inputs, that cuts noise of width less than 50 ns. Be careful not to allow noise of width more than 50 ns because the noise of with more than 50 ms is recognized as an active pulse.

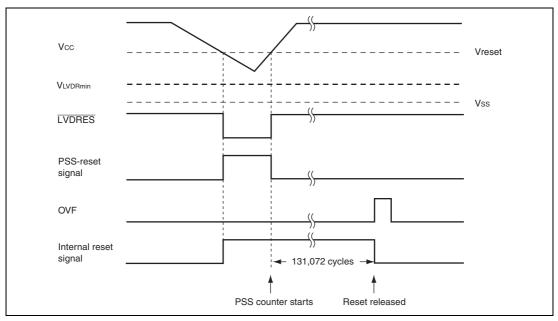

Figure 18.3 Operational Timing of LVDR Circuit

## LVDI (Interrupt by Low Voltage Detect) Circuit:

Figure 18.4 shows the timing of LVDI functions. The LVDI enters the module-standby state after a power-on reset is canceled. To operate the LVDI, set the LVDE bit in LVDCR to 1, wait for 50  $\mu$ s (t<sub>LVDON</sub>) until the reference voltage and the low-voltage-detection power supply have stabilized by a software timer, etc., then set the LVDDE and LVDUE bits in LVDCR to 1. After that, the output settings of ports must be made. To cancel the low-voltage detection circuit, first the LVDDE and LVDUE bits should all be cleared to 0 and then the LVDE bit should be cleared to 0. The LVDE bit must not be cleared to 0 at the same timing as the LVDDE and LVDUE bits because incorrect operation may occur.

When the power-supply voltage falls below Vint (D) (typ. = 3.7 V) voltage, the LVDI clears the  $\overline{\text{LVDINT}}$  signal to 0 and the LVDDF bit in LVDSR is set to 1. If the LVDDE bit is 1 at this time, an IRQ0 interrupt request is simultaneously generated. In this case, the necessary data must be saved in the external EEPROM, etc, and a transition must be made to standby mode or subsleep mode. Until this processing is completed, the power supply voltage must be higher than the lower limit of the guaranteed operating voltage.

When the power-supply voltage does not fall below Vreset1 (typ. = 2.3 V) voltage but rises above Vint (U) (typ. = 4.0 V) voltage, the LVDI sets the  $\overline{\text{LVDINT}}$  signal to 1. If the LVDUE bit is 1 at

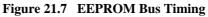

## 21.5 Output Load Condition

Figure 21.8 Output Load Circuit

## Table A.1 Instruction Set

## 1. Data Transfer Instructions

|     |                        |           | Addressing Mode and<br>Instruction Length (bytes) |    |                                                                   |   |   |           |   |     |         |                                                       |        |   |                |        |        |        | No. of<br>States <sup>*1</sup> |    |

|-----|------------------------|-----------|---------------------------------------------------|----|-------------------------------------------------------------------|---|---|-----------|---|-----|---------|-------------------------------------------------------|--------|---|----------------|--------|--------|--------|--------------------------------|----|

|     | Mnemonic               |           | #xx                                               | Rn | Rn<br>@ERn<br>@(d, ERn)<br>@-ERn/@ERn+<br>@aa<br>@(d, PC)<br>@@aa |   |   | Operation |   | Con | Normal  | Advanced                                              |        |   |                |        |        |        |                                |    |

| моу | MOV.B #xx:8, Rd        | B Operand | 2                                                 | -  | -                                                                 | _ | - | -         | - | -   | -<br> - | #xx:8 → Rd8                                           | <br> _ | _ | N<br>Ĵ         | z<br>Ĵ | V<br>0 | с<br>— | - 2                            |    |

|     | MOV.B Rs, Rd           | В         |                                                   | 2  |                                                                   |   |   |           |   |     |         | $Rs8 \rightarrow Rd8$                                 | -      | _ | 1              | 1      | 0      | -      | 2                              | 2  |

|     | MOV.B @ERs, Rd         | В         |                                                   |    | 2                                                                 |   |   |           |   |     |         | @ERs $\rightarrow$ Rd8                                | -      | _ | \$             | \$     | 0      | -      | 4                              | 1  |

|     | MOV.B @(d:16, ERs), Rd | В         |                                                   |    |                                                                   | 4 |   |           |   |     |         | @(d:16, ERs) → Rd8                                    | _      | - | \$             | \$     | 0      | -      | 6                              |    |

|     | MOV.B @(d:24, ERs), Rd | в         |                                                   |    |                                                                   | 8 |   |           |   |     |         | @(d:24, ERs) → Rd8                                    | _      | _ | \$             | \$     | 0      | —      | 10                             |    |

|     | MOV.B @ERs+, Rd        | в         |                                                   |    |                                                                   |   | 2 |           |   |     |         | @ERs → Rd8<br>ERs32+1 → ERs32                         | -      | - | \$             | \$     | 0      | -      | 6                              |    |

|     | MOV.B @aa:8, Rd        | В         |                                                   |    |                                                                   |   |   | 2         |   |     |         | @aa:8 $\rightarrow$ Rd8                               | —      | — | \$             | \$     | 0      | —      | 4                              | ŀ  |

|     | MOV.B @aa:16, Rd       | в         |                                                   |    |                                                                   |   |   | 4         |   |     |         | @aa:16 $\rightarrow$ Rd8                              | _      | _ | \$             | \$     | 0      | —      | 6                              | 3  |

|     | MOV.B @aa:24, Rd       | В         |                                                   |    |                                                                   |   |   | 6         |   |     |         | @aa:24 $\rightarrow$ Rd8                              | —      | — | \$             | \$     | 0      | —      | 8                              | 3  |

|     | MOV.B Rs, @ERd         | В         |                                                   |    | 2                                                                 |   |   |           |   |     |         | $Rs8 \rightarrow @ERd$                                | —      | — | \$             | \$     | 0      | —      | 4                              | 1  |

|     | MOV.B Rs, @(d:16, ERd) | В         |                                                   |    |                                                                   | 4 |   |           |   |     |         | Rs8 $\rightarrow$ @(d:16, ERd)                        | —      | — | \$             | \$     | 0      | —      | 6                              | 3  |

|     | MOV.B Rs, @(d:24, ERd) | В         |                                                   |    |                                                                   | 8 |   |           |   |     |         | $Rs8 \rightarrow @(d:24, ERd)$                        | —      | — | \$             | \$     | 0      | —      | 1                              | 0  |

|     | MOV.B Rs, @-ERd        | В         |                                                   |    |                                                                   |   | 2 |           |   |     |         | $ERd32-1 \rightarrow ERd32$<br>Rs8 $\rightarrow @ERd$ | -      | - | \$             | \$     | 0      | -      | 6                              |    |

|     | MOV.B Rs, @aa:8        | В         |                                                   |    |                                                                   |   |   | 2         |   |     |         | Rs8 $\rightarrow$ @aa:8                               | —      | — | \$             | \$     | 0      | —      | 4                              |    |

|     | MOV.B Rs, @aa:16       | В         |                                                   |    |                                                                   |   |   | 4         |   |     |         | Rs8 $\rightarrow$ @aa:16                              | —      | — | \$             | \$     | 0      | —      | 6                              |    |

|     | MOV.B Rs, @aa:24       | В         |                                                   |    |                                                                   |   |   | 6         |   |     |         | Rs8 $\rightarrow$ @aa:24                              | —      | — | \$             | \$     | 0      | —      | 8                              | 3  |

|     | MOV.W #xx:16, Rd       | w         | 4                                                 |    |                                                                   |   |   |           |   |     |         | #xx:16 → Rd16                                         | —      | — | \$             | \$     | 0      | —      | 4                              |    |

|     | MOV.W Rs, Rd           | W         |                                                   | 2  |                                                                   |   |   |           |   |     |         | $Rs16 \rightarrow Rd16$                               | —      | — | \$             | \$     | 0      | -      | 2                              |    |

|     | MOV.W @ERs, Rd         | w         |                                                   |    | 2                                                                 |   |   |           |   |     |         | @ERs $\rightarrow$ Rd16                               | -      | — | $\updownarrow$ | \$     | 0      | -      | 4                              | ł  |

|     | MOV.W @(d:16, ERs), Rd | W         |                                                   |    |                                                                   | 4 |   |           |   |     |         | @(d:16, ERs) → Rd16                                   | -      | — | $\uparrow$     | \$     | 0      | -      | 6                              | ;  |

|     | MOV.W @(d:24, ERs), Rd | W         |                                                   |    |                                                                   | 8 |   |           |   |     |         | @(d:24, ERs) → Rd16                                   | -      | — | $\uparrow$     | \$     | 0      | -      | 1                              | 0  |

|     | MOV.W @ERs+, Rd        | w         |                                                   |    |                                                                   |   | 2 |           |   |     |         | @ERs → Rd16<br>ERs32+2 → @ERd32                       | -      | - | \$             | \$     | 0      | -      | 6                              | \$ |

|     | MOV.W @aa:16, Rd       | w         |                                                   |    |                                                                   |   |   | 4         |   |     |         | @aa:16 $\rightarrow$ Rd16                             | —      | — | \$             | \$     | 0      | -      | 6                              | ;  |

|     | MOV.W @aa:24, Rd       | w         |                                                   |    |                                                                   |   |   | 6         |   |     |         | @aa:24 → Rd16                                         | -      | — | \$             | \$     | 0      | -      | 8                              |    |

|     | MOV.W Rs, @ERd         | w         |                                                   |    | 2                                                                 |   |   |           |   |     |         | $Rs16 \rightarrow @ERd$                               | —      | — | \$             | \$     | 0      | -      | 4                              |    |

|     | MOV.W Rs, @(d:16, ERd) | w         |                                                   |    |                                                                   | 4 |   |           |   |     |         | $Rs16 \rightarrow @(d:16, ERd)$                       | —      | — | \$             | \$     | 0      | -      | 6                              | ;  |

|     | MOV.W Rs, @(d:24, ERd) | w         |                                                   |    |                                                                   | 8 |   |           |   |     |         | $Rs16 \rightarrow @(d:24, ERd)$                       | _      | — | \$             | \$     | 0      | -      | 1                              | 0  |

## 4. Shift Instructions

| Mnemonic |             |              | Addressing Mode and<br>Instruction Length (bytes) |    |      |           |             |     |          |     |   |             |                |   |                |                |   |                | No.<br>Stat |          |

|----------|-------------|--------------|---------------------------------------------------|----|------|-----------|-------------|-----|----------|-----|---|-------------|----------------|---|----------------|----------------|---|----------------|-------------|----------|

|          |             | Operand Size | ×                                                 |    | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @aa |   | Operation   | Condition Code |   |                |                |   |                | Normal      | Advanced |

|          |             | g            | XX#                                               | Rn | 0    | 0         | ġ           | 0   | 0        | 0   | Ι |             | I              | н | N              | z              | ۷ | с              | ž           | Ă        |

| SHAL     | SHAL.B Rd   | В            |                                                   | 2  |      |           |             |     |          |     |   |             | —              | — | ↕              | ↕              | ↕ | ↕              | 2           | 2        |

|          | SHAL.W Rd   | W            |                                                   | 2  |      |           |             |     |          |     |   |             | _              | — | $\updownarrow$ | $\updownarrow$ | ↕ | $\updownarrow$ | 2           | 2        |

|          | SHAL.L ERd  | L            |                                                   | 2  |      |           |             |     |          |     |   | MSB LSB     | _              | — | $\updownarrow$ | $\updownarrow$ | ↕ | ↕              | 2           | 2        |

| SHAR     | SHAR.B Rd   | В            |                                                   | 2  |      |           |             |     |          |     |   | r►          | _              | — | $\updownarrow$ | $\updownarrow$ | 0 | ↕              | 2           | 2        |

|          | SHAR.W Rd   | W            |                                                   | 2  |      |           |             |     |          |     |   |             |                | — | $\updownarrow$ | $\updownarrow$ | 0 | ¢              | 2           | 2        |

|          | SHAR.L ERd  | L            |                                                   | 2  |      |           |             |     |          |     |   | MSB LSB     | _              | — | $\updownarrow$ | $\updownarrow$ | 0 | ¢              | 2           | 2        |

| SHLL     | SHLL.B Rd   | В            |                                                   | 2  |      |           |             |     |          |     |   |             | _              | — | $\updownarrow$ | $\updownarrow$ | 0 | ¢              | 2           | 2        |

|          | SHLL.W Rd   | W            |                                                   | 2  |      |           |             |     |          |     |   |             | —              | — | $\updownarrow$ | ↕              | 0 | $\updownarrow$ | 2           | 2        |

|          | SHLL.L ERd  | L            |                                                   | 2  |      |           |             |     |          |     |   | MSB LSB     | —              | — | ↕              | $\updownarrow$ | 0 | ↕              | 2           | 2        |

| SHLR     | SHLR.B Rd   | В            |                                                   | 2  |      |           |             |     |          |     |   | 0-> -> C    | —              | — | $\uparrow$     | $\uparrow$     | 0 | €              | 2           | 2        |

|          | SHLR.W Rd   | W            |                                                   | 2  |      |           |             |     |          |     |   |             | —              | — | ↕              | $\updownarrow$ | 0 | ↕              | 2           | 2        |

|          | SHLR.L ERd  | L            |                                                   | 2  |      |           |             |     |          |     |   | MSB LSB     | —              | — | $\updownarrow$ | $\updownarrow$ | 0 | ↕              | 2           | 2        |

| ROTXL    | ROTXL.B Rd  | В            |                                                   | 2  |      |           |             |     |          |     |   |             | —              | — | ↕              | $\updownarrow$ | 0 | ↕              | 2           | 2        |

|          | ROTXL.W Rd  | W            |                                                   | 2  |      |           |             |     |          |     |   |             | —              | — | €              | $\updownarrow$ | 0 | €              | 2           | 2        |

|          | ROTXL.L ERd | L            |                                                   | 2  |      |           |             |     |          |     |   | MSB - LSB   | _              | — | ↕              | \$             | 0 | €              | 2           | 2        |

| ROTXR    | ROTXR.B Rd  | В            |                                                   | 2  |      |           |             |     |          |     |   | · ┌►►C-」    | _              | — | ↕              | $\updownarrow$ | 0 | ↕              | 2           | 2        |

|          | ROTXR.W Rd  | W            |                                                   | 2  |      |           |             |     |          |     |   |             | _              | — | ↕              | $\updownarrow$ | 0 | ↕              | 2           | 2        |

|          | ROTXR.L ERd | L            |                                                   | 2  |      |           |             |     |          |     |   | MSB         | _              | _ | ↕              | ↕              | 0 | ↕              | 2           | 2        |

| ROTL     | ROTL.B Rd   | В            |                                                   | 2  |      |           |             |     |          |     |   |             | —              | - | $\updownarrow$ | $\updownarrow$ | 0 | $\updownarrow$ | 2           | 2        |

|          | ROTL.W Rd   | w            |                                                   | 2  |      |           |             |     |          |     |   |             | —              | - | $\updownarrow$ | $\updownarrow$ | 0 | $\updownarrow$ | 2           | 2        |

|          | ROTL.L ERd  | L            |                                                   | 2  |      |           |             |     |          |     |   | MSB - LSB   | —              | - | $\updownarrow$ | $\updownarrow$ | 0 | $\updownarrow$ | 2           | 2        |

| ROTR     | ROTR.B Rd   | В            |                                                   | 2  |      |           |             |     |          |     |   |             | _              | — | $\updownarrow$ | $\updownarrow$ | 0 | ↕              | 2           | 2        |

|          | ROTR.W Rd   | W            |                                                   | 2  |      |           |             |     |          |     |   |             | —              | — | ↕              | $\updownarrow$ | 0 | ↕              | 2           | 2        |

|          | ROTR.L ERd  | L            |                                                   | 2  |      |           |             |     |          |     |   | MSB ──► LSB | _              | — | $\updownarrow$ | $\updownarrow$ | 0 | $\updownarrow$ | 2           | 2        |

| Item                                                     | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 5 Clock Pulse<br>Generators                      | 70   |                                                                                                                                                                                                                                                                                                                                          |

| Figure 5.3 Typical<br>Connection to Crystal<br>Resonator |      | $OSC_2 \qquad \qquad \qquad C_2 \qquad \qquad C_1 = C_2 = 10 \text{ to } 22 \text{ pF}$                                                                                                                                                                                                                                                  |

| Figure 5.5 Typical<br>Connection to Ceramic<br>Resonator | 71   | $\begin{array}{c} OSC_1 \\ \hline \\ OSC_2 \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $                                                                                                                                                                                                                                |

| Section 6 Power-Down<br>Modes                            | 76   | Bit Bit Name Description                                                                                                                                                                                                                                                                                                                 |

| 6.1.1 System Control<br>Register 1 (SYSCR1)              |      | 3 NESEL Noise Elimination Sampling Frequency<br>Select                                                                                                                                                                                                                                                                                   |

|                                                          |      | The subclock pulse generator generates the watch clock signal ( $\phi_w$ ) and the system clock pulse generator generates the oscillator clock ( $\phi_{osc}$ ). This bit selects the sampling frequency of the oscillator clock when the watch clock signal ( $\phi_w$ ) is sampled. When $\phi_{osc} = 4$ to 20 MHz, clear NESEL to 0. |

| Section 8 RAM                                            | 107  | Note: * When the E7 or E8 is used, area H'F780 to H'FB7F must not be accessed.                                                                                                                                                                                                                                                           |

| Section 13 Watchdog<br>Timer<br>13.2.1 Timer             | 184  | Bit Bit Name Description                                                                                                                                                                                                                                                                                                                 |

| Control/Status Register<br>WD (TCSRWD)                   |      | 4 TCSRWE Timer Control/Status Register WD Write Enable                                                                                                                                                                                                                                                                                   |