Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SCI                                                         |

| Peripherals                | PWM, WDT                                                                      |

| Number of I/O              | 29                                                                            |

| Program Memory Size        | 32KB (32K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-LQFP                                                                       |

| Supplier Device Package    | 48-LFQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3694fyv |

|                            |                                                                               |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

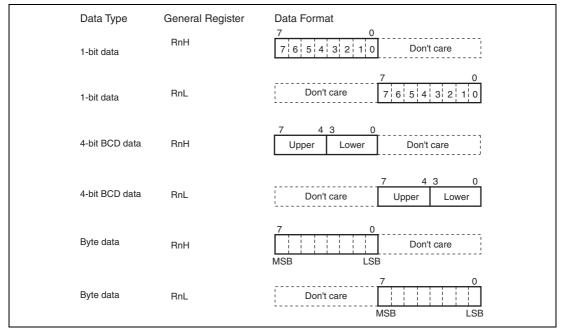

## 2.3 Data Formats

The H8/300H CPU can process 1-bit, 4-bit (BCD), 8-bit (byte), 16-bit (word), and 32-bit (longword) data. Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data. The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

## 2.3.1 General Register Data Formats

Figure 2.5 shows the data formats in general registers.

Figure 2.5 General Register Data Formats (1)

• Prior to executing BCLR instruction

| MOV.B | #3F, | ROL   |

|-------|------|-------|

| MOV.B | ROL, | @RAM0 |

| MOV.B | ROL, | @PCR5 |

The PCR5 value (H'3F) is written to a work area in memory (RAM0) as well as to PCR5.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

| RAM0         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

## • BCLR instruction executed

BCLR #0, @RAMO

The BCLR instructions executed for the PCR5 work area (RAM0).

## • After executing BCLR instruction

| MOV.B | @RAMO, ROI | L  |

|-------|------------|----|

| MOV.B | ROL, @PC   | R5 |

The work area (RAM0) value is written to PCR5.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50           |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output        |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | High<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 0             |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0             |

| RAM0         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 0             |

## 3.5 Usage Notes

#### 3.5.1 Interrupts after Reset

If an interrupt is accepted after a reset and before the stack pointer (SP) is initialized, the PC and CCR will not be saved correctly, leading to a program crash. To prevent this, all interrupt requests, including NMI, are disabled immediately after a reset. Since the first instruction of a program is always executed immediately after the reset state ends, make sure that this instruction initializes the stack pointer (example: MOV.W #xx: 16, SP).

#### 3.5.2 Notes on Stack Area Use

When word data is accessed, the least significant bit of the address is regarded as 0. Access to the stack always takes place in word size, so the stack pointer (SP: R7) should never indicate an odd address. Use PUSH Rn (MOV.W Rn, @–SP) or POP Rn (MOV.W @SP+, Rn) to save or restore register values.

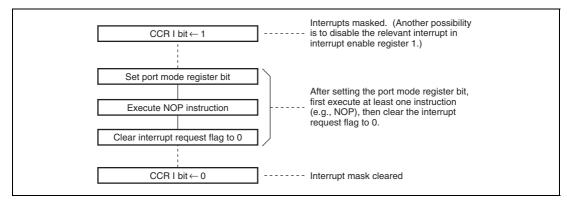

#### 3.5.3 Notes on Rewriting Port Mode Registers

When a port mode register is rewritten to switch the functions of external interrupt pins,  $\overline{IRQ3}$  to  $\overline{IRQ0}$ , and  $\overline{WKP5}$  to  $\overline{WKP0}$ , the interrupt request flag may be set to 1.

When switching a pin function, mask the interrupt before setting the bit in the port mode register. After accessing the port mode register, execute at least one instruction (e.g., NOP), then clear the interrupt request flag from 1 to 0.

Figure 3.4 shows a port mode register setting and interrupt request flag clearing procedure.

Figure 3.4 Port Mode Register Setting and Interrupt Request Flag Clearing Procedure

|                     | Flash Memo                | Flash Memory Operating State |  |  |  |  |

|---------------------|---------------------------|------------------------------|--|--|--|--|

| LSI Operating State | PDWND = 0 (Initial value) | PDWND = 1                    |  |  |  |  |

| Active mode         | Normal operating mode     | Normal operating mode        |  |  |  |  |

| Subactive mode      | Power-down mode           | Normal operating mode        |  |  |  |  |

| Sleep mode          | Normal operating mode     | Normal operating mode        |  |  |  |  |

| Subsleep mode       | Standby mode              | Standby mode                 |  |  |  |  |

| Standby mode        | Standby mode              | Standby mode                 |  |  |  |  |

## Table 7.7 Flash Memory Operating States

## P15/IRQ1 pin

| Register      | PMR1 | PCR1  |                |

|---------------|------|-------|----------------|

| Bit Name      | IRQ1 | PCR15 | Pin Function   |

| Setting value | 9 0  | 0     | P15 input pin  |

|               |      | 1     | P15 output pin |

|               | 1    | Х     | IRQ1 input pin |

Legend: X: Don't care.

## P14/IRQ0 pin

| PMR1 | PCR1  |                                                      |

|------|-------|------------------------------------------------------|

| IRQ0 | PCR14 | Pin Function                                         |

| 0    | 0     | P14 input pin                                        |

|      | 1     | P14 output pin                                       |

| 1    | Х     | IRQ0 input pin                                       |

|      |       | IRQ0         PCR14           0         0           1 |

Legend: X: Don't care.

## P12 pin

| Register      | PCR1  |                |  |

|---------------|-------|----------------|--|

| Bit Name      | PCR12 | Pin Function   |  |

| Setting value | 0     | P12 input pin  |  |

|               | 1     | P12 output pin |  |

## P11 pin

| Register      | PCR1  |                |  |

|---------------|-------|----------------|--|

| Bit Name      | PCR11 | Pin Function   |  |

| Setting value | 0     | P11 input pin  |  |

|               | 1     | P11 output pin |  |

## 11.3.3 Timer Control Register V0 (TCRV0)

TCRV0 selects the input clock signals of TCNTV, specifies the clearing conditions of TCNTV, and controls each interrupt request.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                              |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CMIEB    | 0                | R/W | Compare Match Interrupt Enable B                                                                                                         |

|     |          |                  |     | When this bit is set to 1, interrupt request from the CMFB bit in TCSRV is enabled.                                                      |

| 6   | CMIEA    | 0                | R/W | Compare Match Interrupt Enable A                                                                                                         |

|     |          |                  |     | When this bit is set to 1, interrupt request from the CMFA bit in TCSRV is enabled.                                                      |

| 5   | OVIE     | 0                | R/W | Timer Overflow Interrupt Enable                                                                                                          |

|     |          |                  |     | When this bit is set to 1, interrupt request from the OVF bit in TCSRV is enabled.                                                       |

| 4   | CCLR1    | 0                | R/W | Counter Clear 1 and 0                                                                                                                    |

| 3   | CCLR0    | 0                | R/W | These bits specify the clearing conditions of TCNTV.                                                                                     |

|     |          |                  |     | 00: Clearing is disabled                                                                                                                 |

|     |          |                  |     | 01: Cleared by compare match A                                                                                                           |

|     |          |                  |     | 10: Cleared by compare match B                                                                                                           |

|     |          |                  |     | <ol> <li>Cleared on the rising edge of the TMRIV pin. The<br/>operation of TCNTV after clearing depends on TRGE<br/>in TCRV1.</li> </ol> |

| 2   | CKS2     | 0                | R/W | Clock Select 2 to 0                                                                                                                      |

| 1   | CKS1     | 0                | R/W | These bits select clock signals to input to TCNTV and the                                                                                |

| 0   | CKS0     | 0                | R/W | counting condition in combination with ICKS0 in TCRV1.                                                                                   |

|     |          |                  |     | Refer to table 11.2.                                                                                                                     |

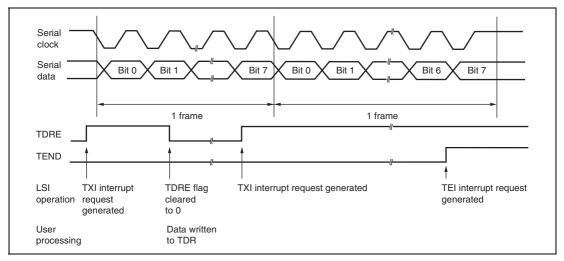

Figure 14.10 Example of SCI3 Operation in Transmission in Clocked Synchronous Mode

|     |          | Initial |     |                                                                                                                                                                                                                                                                                                  |

|-----|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                                                                      |

| 4   | SDAOP    | 1       | R/W | SDAO Write Protect                                                                                                                                                                                                                                                                               |

|     |          |         |     | This bit controls change of output level of the SDA pin by<br>modifying the SDAO bit. To change the output level, clear<br>SDAO and SDAOP to 0 or set SDAO to 1 and clear<br>SDAOP to 0 by the MOV instruction. This bit is always<br>read as 1.                                                 |

| 3   | SCLO     | 1       | R   | This bit monitors SCL output level. When SCLO is 1, SCL pin outputs high. When SCLO is 0, SCL pin outputs low.                                                                                                                                                                                   |

| 2   | —        | 1       |     | Reserved                                                                                                                                                                                                                                                                                         |

|     |          |         |     | This bit is always read as 1, and cannot be modified.                                                                                                                                                                                                                                            |

| 1   | IICRST   | 0       | R/W | IIC Control Part Reset                                                                                                                                                                                                                                                                           |

|     |          |         |     | This bit resets the control part except for I <sup>2</sup> C registers. If<br>this bit is set to 1 when hang-up occurs because of<br>communication failure during I <sup>2</sup> C operation, I <sup>2</sup> C control<br>part can be reset without setting ports and initializing<br>registers. |

| 0   | _        | 1       | _   | Reserved                                                                                                                                                                                                                                                                                         |

|     |          |         |     | This bit is always read as 1, and cannot be modified.                                                                                                                                                                                                                                            |

## 15.3.3 I<sup>2</sup>C Bus Mode Register (ICMR)

ICMR selects whether the MSB or LSB is transferred first, performs master mode wait control, and selects the transfer bit count.

|     |          | Initial |     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                         |

| 7   | MLS      | 0       | R/W | MSB-First/LSB-First Select                                                                                                                                                                                                                                                                                                                                                                          |

|     |          |         |     | 0: MSB-first                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |         |     | 1: LSB-first                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |         |     | Set this bit to 0 when the I <sup>2</sup> C bus format is used.                                                                                                                                                                                                                                                                                                                                     |

| 6   | WAIT     | 0       | R/W | Wait Insertion Bit                                                                                                                                                                                                                                                                                                                                                                                  |

|     |          |         |     | In master mode with the I <sup>2</sup> C bus format, this bit selects<br>whether to insert a wait after data transfer except the<br>acknowledge bit. When WAIT is set to 1, after the fall of<br>the clock for the final data bit, low period is extended for<br>two transfer clocks. If WAIT is cleared to 0, data and<br>acknowledge bits are transferred consecutively with no<br>wait inserted. |

|     |          |         |     | The setting of this bit is invalid in slave mode with the I <sup>2</sup> C bus format or with the clocked synchronous serial format.                                                                                                                                                                                                                                                                |

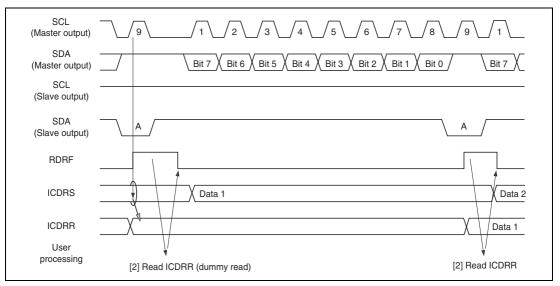

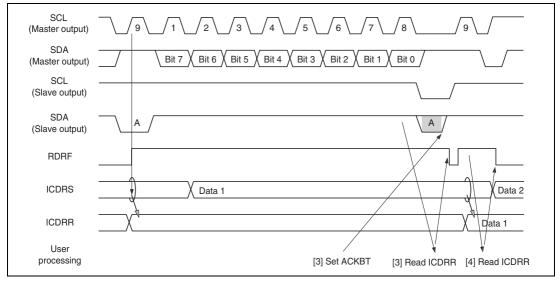

- 3. Read ICDRR every time RDRF is set. If 8th receive clock pulse falls while RDRF is 1, SCL is fixed low until ICDRR is read. The change of the acknowledge before reading ICDRR, to be returned to the master device, is reflected to the next transmit frame.

- 4. The last byte data is read by reading ICDRR.

Figure 15.11 Slave Receive Mode Operation Timing (1)

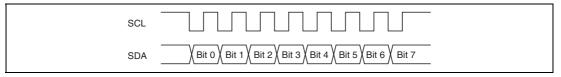

## 15.4.6 Clocked Synchronous Serial Format

This module can be operated with the clocked synchronous serial format, by setting the FS bit in SAR to 1. When the MST bit in ICCR1 is 1, the transfer clock output from SCL is selected. When MST is 0, the external clock input is selected.

#### **Data Transfer Format**

Figure 15.13 shows the clocked synchronous serial transfer format.

The transfer data is output from the rise to the fall of the SCL clock, and the data at the rising edge of the SCL clock is guaranteed. The MLS bit in ICMR sets the order of data transfer, in either the MSB first or LSB first. The output level of SDA can be changed during the transfer wait, by the SDAO bit in ICCR2.

Figure 15.13 Clocked Synchronous Serial Transfer Format

#### **Transmit Operation**

In transmit mode, transmit data is output from SDA, in synchronization with the fall of the transfer clock. The transfer clock is output when MST in ICCR1 is 1, and is input when MST is 0. For transmit mode operation timing, refer to figure 15.14. The transmission procedure and operations in transmit mode are described below.

- 1. Set the ICE bit in ICCR1 to 1. Set the MST and CKS3 to CKS0 bits in ICCR1 to 1. (Initial setting)

- 2. Set the TRS bit in ICCR1 to select the transmit mode. Then, TDRE in ICSR is set.

- 3. Confirm that TDRE has been set. Then, write the transmit data to ICDRT. The data is transferred from ICDRT to ICDRS, and TDRE is set automatically. The continuous transmission is performed by writing data to ICDRT every time TDRE is set. When changing from transmit mode to receive mode, clear TRS while TDRE is 1.

## 15.5 Interrupt Request

There are six interrupt requests in this module; transmit data empty, transmit end, receive data full, NACK receive, STOP recognition, and arbitration lost/overrun. Table 15.3 shows the contents of each interrupt request.

#### Table 15.3 Interrupt Requests

| Interrupt Request           | Abbreviation | Interrupt Condition            | I <sup>2</sup> C Mode | Clocked<br>Synchronous<br>Mode |

|-----------------------------|--------------|--------------------------------|-----------------------|--------------------------------|

| Transmit Data Empty         | ТХІ          | (TDRE = 1) • (TIE = 1)         | 0                     | 0                              |

| Transmit End                | TEI          | (TEND = 1) • (TEIE = 1)        | 0                     | 0                              |

| Receive Data Full           | RXI          | (RDRF = 1) • (RIE = 1)         | 0                     | 0                              |

| STOP Recognition            | STPI         | $(STOP = 1) \cdot (STIE = 1)$  | 0                     | ×                              |

| NACK Receive                | NAKI         | $\{(NACKF = 1) + (AL = 1)\}$ . | 0                     | ×                              |

| Arbitration<br>Lost/Overrun |              | (NAKIE = 1)                    | 0                     | 0                              |

When interrupt conditions described in table 15.3 are 1 and the I bit in CCR is 0, the CPU executes an interrupt exception processing. Interrupt sources should be cleared in the exception processing. TDRE and TEND are automatically cleared to 0 by writing the transmit data to ICDRT. RDRF are automatically cleared to 0 by reading ICDRR. TDRE is set to 1 again at the same time when transmit data is written to ICDRT. When TDRE is cleared to 0, then an excessive data of one byte may be transmitted.

# Section 17 EEPROM

The H8/3694N has an on-chip 512-byte EEPROM. The block diagram of the EEPROM is shown in figure 17.1.

## 17.1 Features

• Two writing methods:

1-byte write

Page write: Page size 8 bytes

- Three reading methods: Current address read Random address read Sequential read

- Acknowledge polling possible

- Write cycle time:

10 ms (power supply voltage Vcc = 2.7 V or more)

- Write/Erase endurance: 10<sup>4</sup> cycles/byte (byte write mode), 10<sup>5</sup> cycles/page (page write mode)

- Data retention:

10 years after the write cycle of  $10^4$  cycles (page write mode)

• Interface with the CPU

I<sup>2</sup>C bus interface (complies with the standard of Philips Corporation)

Device code 1010

Sleep address code can be changed (initial value: 000)

The I<sup>2</sup>C bus is open to the outside, so the EEPROM can be directly accessed from the outside.

## 17.4.7 Write Operations

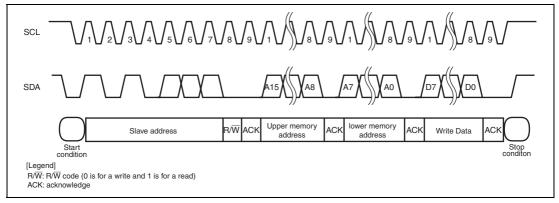

There are two types write operations; byte write operation and page write operation. To initiate the write operation, input 0 to  $R/\overline{W}$  code following the slave address.

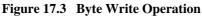

1. Byte Write

A write operation requires an 8-bit data of a 7-bit slave address with  $R/\overline{W}$  code = "0". Then the EEPROM sends acknowledgement "0" at the ninth bit. This enters the write mode. Then, two bytes of the memory address are received from the MSB side in the order of upper and lower. Upon receipt of one-byte memory address, the EEPROM sends acknowledgement "0" and receives a following a one-byte write data. After receipt of write data, the EEPROM sends acknowledgement "0". If the EEPROM receives a stop condition, the EEPROM enters an internally controlled write cycle and terminates receipt of SCL and SDA inputs until completion of the write cycle. The EEPROM returns to a standby mode after completion of the write cycle.

The byte write operation is shown in figure 17.3.

2. Page Write

This LSI is capable of the page write operation which allows any number of bytes up to 8 bytes to be written in a single write cycle. The write data is input in the same sequence as the byte write in the order of a start condition, slave address + R/W code, memory address (n), and write data (Dn) with every ninth bit acknowledgement "0" output. The EEPROM enters the page write operation if the EEPROM receives more write data (Dn+1) is input instead of receiving a stop condition after receiving the write data (Dn). LSB 3 bits (A2 to A0) in the EEPROM address are automatically incremented to be the (n+1) address upon receiving write data (Dn+1). Thus the write data can be received sequentially.

RENESAS

## 18.3 Operation

## 18.3.1 Power-On Reset Circuit

Figure 18.2 shows the timing of the operation of the power-on reset circuit. As the power-supply voltage rises, the capacitor which is externally connected to the  $\overline{\text{RES}}$  pin is gradually charged via the on-chip pull-up resistor (typ. 150 k $\Omega$ ). Since the state of the  $\overline{\text{RES}}$  pin is transmitted within the chip, the prescaler S and the entire chip are in their reset states. When the level on the  $\overline{\text{RES}}$  pin reaches the specified value, the prescaler S is released from its reset state and it starts counting. The OVF signal is generated to release the internal reset signal after the prescaler S has counted 131,072 clock ( $\phi$ ) cycles. The noise cancellation circuit of approximately 100 ns is incorporated to prevent the incorrect operation of the chip by noise on the  $\overline{\text{RES}}$  pin.

To achieve stable operation of this LSI, the power supply needs to rise to its full level and settles within the specified time. The maximum time required for the power supply to rise and settle after power has been supplied ( $t_{PWON}$ ) is determined by the oscillation frequency ( $f_{osc}$ ) and capacitance which is connected to  $\overline{\text{RES}}$  pin ( $C_{\overline{\text{RES}}}$ ). If  $t_{PWON}$  means the time required to reach 90 % of power supply voltage, the power supply circuit should be designed to satisfy the following formula.

$$\begin{split} t_{_{PWON}} \ (ms) &\leq 90 \times C_{\overline{\text{RES}}} \ (\mu F) + 162/f_{_{OSC}} \ (MHz) \\ (t_{_{PWON}} &\leq 3000 \ ms, \ C_{\overline{\text{RES}}} \geq 0.22 \ \mu F, \ \text{and} \ f_{_{OSC}} = 10 \ \text{in 2-MHz to 10-MHz operation}) \end{split}$$

Note that the power supply voltage (Vcc) must fall below Vpor = 100 mV and rise after charge on the  $\overline{\text{RES}}$  pin is removed. To remove charge on the  $\overline{\text{RES}}$  pin, it is recommended that the diode should be placed near Vcc. If the power supply voltage (Vcc) rises from the point above Vpor, a power-on reset may not occur.

## Section 21 Electrical Characteristics

## 21.1 Absolute Maximum Ratings

#### Table 21.1 Absolute Maximum Ratings

| ltem                                             |              | Symbol           | Value                       | Unit | Note |

|--------------------------------------------------|--------------|------------------|-----------------------------|------|------|

| Power supply vol                                 | tage         | V <sub>cc</sub>  | -0.3 to +7.0                | V    | *    |

| Analog power su                                  | oply voltage | $AV_{cc}$        | -0.3 to +7.0                | V    |      |

| Input voltage Ports other than ports<br>B and X1 |              | V <sub>IN</sub>  | –0.3 to V $_{\rm cc}$ +0.3  | V    |      |

|                                                  | Port B       |                  | –0.3 to AV $_{\rm cc}$ +0.3 | V    | _    |

|                                                  | X1           |                  | –0.3 to 4.3                 | V    | _    |

| Operating temperature                            |              | T <sub>opr</sub> | –20 to +75                  | °C   |      |

| Storage temperat                                 | ture         | T <sub>stg</sub> | –55 to +125                 | °C   |      |

|                                                  |              |                  |                             |      |      |

Note: \* Permanent damage may result if maximum ratings are exceeded. Normal operation should be under the conditions specified in Electrical Characteristics. Exceeding these values can result in incorrect operation and reduced reliability.

# 21.2 Electrical Characteristics (F-ZTAT<sup>TM</sup> Version, EEPROM Stacked F-ZTAT<sup>TM</sup> Version)

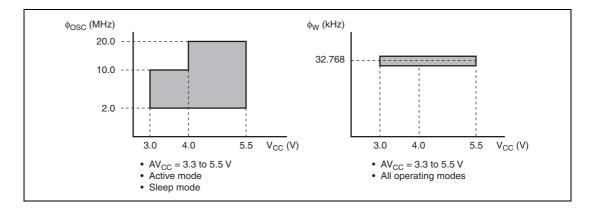

#### 21.2.1 Power Supply Voltage and Operating Ranges

## Power Supply Voltage and Oscillation Frequency Range

RENESAS

## 21.2.2 DC Characteristics

## Table 21.2 DC Characteristics (1)

$V_{cc}$  = 3.0 to 5.5 V,  $V_{ss}$  = 0.0 V,  $T_a$  = -20 to +75°C, unless otherwise indicated.

|                       |                 |                                                             |                                          | Values               |     |                       |      |       |

|-----------------------|-----------------|-------------------------------------------------------------|------------------------------------------|----------------------|-----|-----------------------|------|-------|

| ltem                  | Symbol          | Applicable Pins                                             | Test Condition                           | Min                  | Тур | Max                   | Unit | Notes |

| Input high<br>voltage | V <sub>IH</sub> | RES, NMI,<br>WKP0 to WKP5,<br>IRQ0 to IRQ3,<br>ADTRG,TMRIV, | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | V <sub>cc</sub> ×0.8 |     | V <sub>cc</sub> + 0.3 | V    |       |

|                       |                 | TMCIV, FTCI,<br>FTIOA to FTIOD,<br>SCK3, TRGV               |                                          | $V_{cc} 	imes 0.9$   | —   | V <sub>cc</sub> + 0.3 |      |       |

|                       |                 | RXD, SCL, SDA,<br>P10 to P12,<br>P14 to P17,<br>P20 to P22, | $V_{cc}$ = 4.0 to 5.5 V                  | $V_{cc} \times 0.7$  | _   | V <sub>cc</sub> + 0.3 | V    | _     |

|                       |                 | P50 to P57,<br>P74 to P76,<br>P80 to P87                    |                                          | $V_{cc} 	imes 0.8$   | _   | V <sub>cc</sub> + 0.3 |      |       |

|                       |                 | PB0 to PB7                                                  | $V_{\rm cc}$ = 4.0 to 5.5 V              | $V_{cc} 	imes 0.7$   | —   | $AV_{cc} + 0.3$       | V    | -     |

|                       |                 |                                                             |                                          | $V_{cc} 	imes 0.8$   | _   | $AV_{cc} + 0.3$       | _    |       |

|                       |                 | OSC1                                                        | $V_{cc}$ = 4.0 to 5.5 V                  | $V_{\rm cc} - 0.5$   | —   | $V_{cc}$ + 0.3        | V    |       |

|                       |                 |                                                             |                                          | $V_{\rm cc} - 0.3$   | —   | $V_{cc}$ + 0.3        |      |       |

| Input low<br>voltage  | V <sub>IL</sub> | RES, NMI,<br>WKP0 to WKP5,<br>IRQ0 to IRQ3,<br>ADTRG,TMRIV, | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | -0.3                 | _   | $V_{cc} \times 0.2$   | V    |       |

|                       |                 | TMCIV, FTCI,<br>FTIOA to FTIOD,<br>SCK3, TRGV               |                                          | -0.3                 | —   | $V_{cc} \times 0.1$   |      |       |

|                       |                 | RXD, SCL, SDA,<br>P10 to P12,<br>P14 to P17,<br>P20 to P22, | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | -0.3                 | —   | $V_{cc} \times 0.3$   | V    |       |

|                       |                 | P50 to P57,<br>P74 to P76,<br>P80 to P87<br>PB0 to PB7      |                                          | -0.3                 | _   | $V_{cc} \times 0.2$   |      | _     |

|                       |                 | OSC1                                                        | $V_{\rm cc}$ = 4.0 to 5.5 V              | -0.3                 | _   | 0.5                   | V    |       |

|                       |                 |                                                             |                                          | -0.3                 | _   | 0.3                   |      |       |

RENESAS

## Table 21.2DC Characteristics (3)

$V_{\rm cc}$  = 3.0 to 5.5 V,  $V_{\rm ss}$  = 0.0 V,  $T_{\rm a}$  = –20 to +75°C, unless otherwise indicated.

|                                        |                    | Applicable                                    | able Values                 |     |     |      |      |

|----------------------------------------|--------------------|-----------------------------------------------|-----------------------------|-----|-----|------|------|

| Item                                   | Symbol             | Pins                                          | Test Condition              | Min | Тур | Max  | Unit |

| Allowable output low current (per pin) | I <sub>ol</sub>    | Output pins<br>except port 8,<br>SCL, and SDA | $V_{\rm cc}$ = 4.0 to 5.5 V | _   | _   | 2.0  | mA   |

|                                        |                    | Port 8                                        | _                           | _   | _   | 20.0 |      |

|                                        |                    | Port 8                                        |                             |     | _   | 10.0 |      |

|                                        |                    | SCL and SDA                                   | _                           | —   | —   | 6.0  |      |

|                                        |                    | Output pins<br>except port 8,<br>SCL, and SDA | _                           |     | _   | 0.5  |      |

| Allowable output low current (total)   | $\Sigma I_{OL}$    | Output pins<br>except port 8,<br>SCL, and SDA | $V_{cc}$ = 4.0 to 5.5 V     | _   | _   | 40.0 | mA   |

|                                        |                    | Port 8,<br>SCL, and SDA                       | _                           | _   | _   | 80.0 |      |

|                                        |                    | Output pins<br>except port 8,<br>SCL, and SDA |                             | _   | _   | 20.0 | _    |

|                                        |                    | Port 8,<br>SCL, and SDA                       | _                           | _   | _   | 40.0 |      |

| Allowable output high                  | -I <sub>OH</sub>   | All output pins                               | $V_{\rm cc}$ = 4.0 to 5.5 V | _   | —   | 2.0  | mA   |

| current (per pin)                      |                    |                                               |                             | —   |     | 0.2  |      |

| Allowable output high                  | $ -\Sigma I_{OH} $ | All output pins                               | $V_{cc}$ = 4.0 to 5.5 V     |     | _   | 30.0 | mA   |

| current (total)                        |                    |                                               |                             |     | _   | 8.0  |      |

## Table 21.5 Serial Communication Interface (SCI) Timing

$V_{\rm cc}$  = 3.0 to 5.5 V,  $V_{\rm ss}$  = 0.0 V,  $T_{\rm a}$  = –20 to +75°C, unless otherwise indicated.

| Item                          |                             |                   | Applicable |                               | Values |     |     |                   | Reference   |

|-------------------------------|-----------------------------|-------------------|------------|-------------------------------|--------|-----|-----|-------------------|-------------|

|                               |                             | Symbol            | Pins       | Test Condition                | Min    | Тур | Max | Unit              | Figure      |

| Input<br>clock                | Asynchro-<br>nous           | t <sub>Scyc</sub> | SCK3       |                               | 4      | _   | _   | t <sub>cyc</sub>  | Figure 21.5 |

| cycle                         | Clocked<br>synchro-<br>nous | _                 |            |                               | 6      | _   | _   | -                 |             |

| Input clock pulse width       |                             | t <sub>sскw</sub> | SCK3       |                               | 0.4    | _   | 0.6 | t <sub>Scyc</sub> | _           |

|                               | it data delay               | t <sub>TXD</sub>  | TXD        | $V_{cc}$ = 4.0 V to 5.5 V     | _      | —   | 1   | t <sub>cyc</sub>  | Figure 21.6 |

| time (clo<br>synchro          |                             |                   |            |                               | _      | _   | 1   | _                 |             |

| Receive data setup            |                             | t <sub>RXS</sub>  | RXD        | $V_{cc}$ = 4.0 V to 5.5 V     | 50.0   |     | —   | ns                |             |

| time (clocked<br>synchronous) |                             |                   |            |                               | 100.0  | _   | _   | _                 |             |

| Receive                       | e data hold                 | t <sub>RXH</sub>  | RXD        | $V_{\rm cc}$ = 4.0 V to 5.5 V | 50.0   | _   | _   | ns                | _           |

| time (clo<br>synchro          |                             |                   |            |                               | 100.0  | —   | _   | -                 |             |

## 21.2.4 A/D Converter Characteristics

## Table 21.6 A/D Converter Characteristics

$V_{\rm cc}$  = 3.0 to 5.5 V,  $V_{\rm ss}$  = 0.0 V,  $T_{\rm a}$  = –20 to +75°C, unless otherwise indicated.

|                                   |                     | Applicable<br>mbol Pins | Test<br>Condition                          |                | Value    |                 | Reference             |                                      |

|-----------------------------------|---------------------|-------------------------|--------------------------------------------|----------------|----------|-----------------|-----------------------|--------------------------------------|

| Item                              | Symbol              |                         |                                            | Min            | Тур      | Max             | Unit                  | Figure                               |

| Analog power supply voltage       | $AV_{cc}$           | $AV_{cc}$               |                                            | 3.3            | $V_{cc}$ | 5.5             | V                     | *1                                   |

| Analog input voltage              | $AV_{\text{in}}$    | AN0 to<br>AN7           |                                            | $V_{ss} - 0.3$ | -        | $AV_{cc} + 0.3$ | V                     |                                      |

| Analog power supply current       | Al <sub>ope</sub>   | AV <sub>cc</sub>        | $AV_{cc} = 5.0 V$<br>$f_{osc} =$<br>20 MHz | _              | _        | 2.0             | mA                    |                                      |

|                                   | AI <sub>STOP1</sub> | $AV_{cc}$               |                                            | _              | 50       | _               | μA                    | * <sup>2</sup><br>Reference<br>value |

|                                   | $AI_{\text{STOP2}}$ | AV <sub>cc</sub>        |                                            | —              | _        | 5.0             | μA                    | *3                                   |

| Analog input capacitance          | C <sub>AIN</sub>    | AN0 to<br>AN7           |                                            | _              | _        | 30.0            | pF                    |                                      |

| Allowable signal source impedance | R <sub>AIN</sub>    | AN0 to<br>AN7           |                                            | _              | -        | 5.0             | kΩ                    |                                      |

| Resolution (data length)          |                     |                         |                                            | 10             | 10       | 10              | bit                   |                                      |

| Conversion time (single mode)     |                     |                         | AV <sub>cc</sub> = 3.3 to<br>5.5 V         | 134            | -        | _               | $t_{_{\mathrm{cyc}}}$ |                                      |

| Nonlinearity error                |                     |                         | _                                          | _              | _        | ±7.5            | LSB                   | _                                    |

| Offset error                      |                     |                         | _                                          | _              | —        | ±7.5            | LSB                   | _                                    |

| Full-scale error                  |                     |                         | _                                          | _              | —        | ±7.5            | LSB                   | _                                    |

| Quantization error                |                     |                         | _                                          | _              | —        | ±0.5            | LSB                   | —                                    |

| Absolute accuracy                 |                     |                         |                                            | _              | —        | ±8.0            | LSB                   |                                      |

| Conversion time<br>(single mode)  |                     |                         | AV <sub>cc</sub> = 4.0 to<br>5.5 V         | 70             | _        | _               | t <sub>cyc</sub>      |                                      |

| Nonlinearity error                |                     |                         | _                                          | _              |          | ±7.5            | LSB                   | —                                    |

| Offset error                      |                     |                         | _                                          | _              | —        | ±7.5            | LSB                   | _                                    |

| Full-scale error                  |                     |                         | _                                          | _              | _        | ±7.5            | LSB                   | _                                    |

| Quantization error                |                     |                         | _                                          | _              | —        | ±0.5            | LSB                   | _                                    |

| Absolute accuracy                 |                     |                         | _                                          | _              | _        | ±8.0            | LSB                   | _                                    |

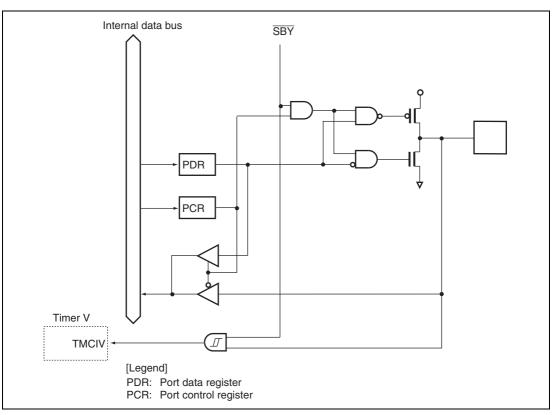

Figure B.12 Port 7 Block Diagram (P75)