# E·XFL

#### Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | H8/300H                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SCI, UART/USART                                               |

| Peripherals                | LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 29                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b SAR                                                                   |

| Oscillator Type            | External, Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3694gfpiv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

so the possible branching range is -126 to +128 bytes (-63 to +64 words) or -32766 to +32768 bytes (-16383 to +16384 words) from the branch instruction. The resulting value should be an even number.

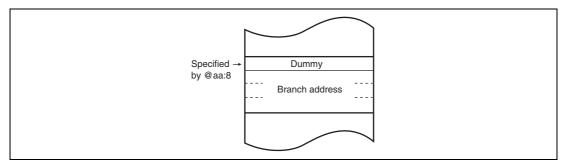

#### Memory Indirect—@@aa:8

This mode can be used by the JMP and JSR instructions. The instruction code contains an 8-bit absolute address specifying a memory operand. This memory operand contains a branch address. The memory operand is accessed by longword access. The first byte of the memory operand is ignored, generating a 24-bit branch address. Figure 2.8 shows how to specify branch address for in memory indirect mode. The upper bits of the absolute address are all assumed to be 0, so the address range is 0 to 255 (H'0000 to H'00FF).

Note that the first part of the address range is also the exception vector area.

Figure 2.8 Branch Address Specification in Memory Indirect Mode

### **3.2 Register Descriptions**

Interrupts are controlled by the following registers.

- Interrupt edge select register 1 (IEGR1)

- Interrupt edge select register 2 (IEGR2)

- Interrupt enable register 1 (IENR1)

- Interrupt flag register 1 (IRR1)

- Wakeup interrupt flag register (IWPR)

#### 3.2.1 Interrupt Edge Select Register 1 (IEGR1)

IEGR1 selects the direction of an edge that generates interrupt requests of pins  $\overline{\text{NMI}}$  and  $\overline{\text{IRQ3}}$  to  $\overline{\text{IRQ0}}$ .

|        |          | Initial |     |                                                                 |

|--------|----------|---------|-----|-----------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                     |

| 7      | NMIEG    | 0       | R/W | NMI Edge Select                                                 |

|        |          |         |     | 0: Falling edge of $\overline{NMI}$ pin input is detected       |

|        |          |         |     | 1: Rising edge of $\overline{\text{NMI}}$ pin input is detected |

| 6 to 4 | —        | All 1   | _   | Reserved                                                        |

|        |          |         |     | These bits are always read as 1.                                |

| 3      | IEG3     | 0       | R/W | IRQ3 Edge Select                                                |

|        |          |         |     | 0: Falling edge of IRQ3 pin input is detected                   |

|        |          |         |     | 1: Rising edge of IRQ3 pin input is detected                    |

| 2      | IEG2     | 0       | R/W | IRQ2 Edge Select                                                |

|        |          |         |     | 0: Falling edge of IRQ2 pin input is detected                   |

|        |          |         |     | 1: Rising edge of IRQ2 pin input is detected                    |

| 1      | IEG1     | 0       | R/W | IRQ1 Edge Select                                                |

|        |          |         |     | 0: Falling edge of IRQ1 pin input is detected                   |

|        |          |         |     | 1: Rising edge of IRQ1 pin input is detected                    |

| 0      | IEG0     | 0       | R/W | IRQ0 Edge Select                                                |

|        |          |         |     | 0: Falling edge of IRQ0 pin input is detected                   |

|        |          |         |     | 1: Rising edge of IRQ0 pin input is detected                    |

pulled up on the board if necessary. After the reset is complete, it takes approximately 100 states before the chip is ready to measure the low-level period.

- 4. After matching the bit rates, the chip transmits one H'00 byte to the host to indicate the completion of bit rate adjustment. The host should confirm that this adjustment end indication (H'00) has been received normally, and transmit one H'55 byte to the chip. If reception could not be performed normally, initiate boot mode again by a reset. Depending on the host's transfer bit rate and system clock frequency of this LSI, there will be a discrepancy between the bit rates of the host and the chip. To operate the SCI properly, set the host's transfer bit rate and system clock frequency of this LSI within the ranges listed in table 7.3.

- 5. In boot mode, a part of the on-chip RAM area is used by the boot program. The area H'F780 to H'FEEF is the area to which the programming control program is transferred from the host. The boot program area cannot be used until the execution state in boot mode switches to the programming control program.

- 6. Before branching to the programming control program, the chip terminates transfer operations by SCI3 (by clearing the RE and TE bits in SCR to 0), however the adjusted bit rate value remains set in BRR. Therefore, the programming control program can still use it for transfer of write data or verify data with the host. The TxD pin is high (PCR22 = 1, P22 = 1). The contents of the CPU general registers are undefined immediately after branching to the programming control program. These registers must be initialized at the beginning of the programming control program, as the stack pointer (SP), in particular, is used implicitly in subroutine calls, etc.

- 7. Boot mode can be cleared by a reset. End the reset after driving the reset pin low, waiting at least 20 states, and then setting the  $\overline{\text{NMI}}$  pin. Boot mode is also cleared when a WDT overflow occurs.

- 8. Do not change the TEST pin and NMI pin input levels in boot mode.

- 5. For a dummy write to a verify address, write 1-byte data H'FF to an address whose lower two bits are B'00. Verify data can be read in longwords from the address to which a dummy write was performed.

- 6. If the read data is not erased successfully, set erase mode again, and repeat the erase/erase-verify sequence as before. The maximum number of repetitions of the erase/erase-verify sequence is 100.

#### 7.4.3 Interrupt Handling when Programming/Erasing Flash Memory

All interrupts, including the NMI interrupt, are disabled while flash memory is being programmed or erased, or while the boot program is executing, for the following three reasons:

- 1. Interrupt during programming/erasing may cause a violation of the programming or erasing algorithm, with the result that normal operation cannot be assured.

- 2. If interrupt exception handling starts before the vector address is written or during programming/erasing, a correct vector cannot be fetched and the CPU malfunctions.

- 3. If an interrupt occurs during boot program execution, normal boot mode sequence cannot be carried out.

## Section 9 I/O Ports

The group of this LSI has twenty-nine general I/O ports (twenty-seven general I/O ports in the H8/3694N) and eight general input-only ports. Port 8 is a large current port, which can drive 20 mA ( $@V_{oL} = 1.5 V$ ) when a low level signal is output. Any of these ports can become an input port immediately after a reset. They can also be used as I/O pins of the on-chip peripheral modules or external interrupt input pins, and these functions can be switched depending on the register settings. The registers for selecting these functions can be divided into two types: those included in I/O ports and those included in each on-chip peripheral module. General I/O ports are comprised of the port control register for controlling inputs/outputs and the port data register for storing output data and can select inputs/outputs in bit units. For functions in each port, see appendix B.1, I/O Port Block Diagrams. For the execution of bit manipulation instructions to the port control register and port data register, see section 2.8.3, Bit Manipulation Instruction.

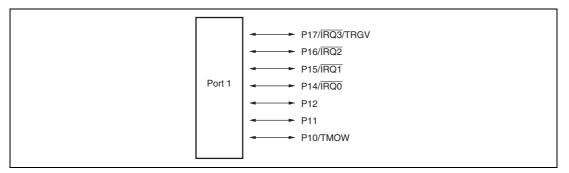

#### 9.1 Port 1

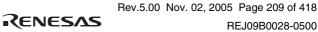

Port 1 is a general I/O port also functioning as IRQ interrupt input pins, a timer A output pin, and a timer V input pin. Figure 9.1 shows its pin configuration.

Figure 9.1 Port 1 Pin Configuration

RENESAS

Port 1 has the following registers.

- Port mode register 1 (PMR1)

- Port control register 1 (PCR1)

- Port data register 1 (PDR1)

- Port pull-up control register 1 (PUCR1)

| φ (MHz)  | Maximum Bit<br>Rate (bit/s) | n | N | φ (MHz) | Maximum Bit<br>Rate (bit/s) | n | N |

|----------|-----------------------------|---|---|---------|-----------------------------|---|---|

| 2        | 62500                       | 0 | 0 | 8       | 250000                      | 0 | 0 |

| 2.097152 | 65536                       | 0 | 0 | 9.8304  | 307200                      | 0 | 0 |

| 2.4576   | 76800                       | 0 | 0 | 10      | 312500                      | 0 | 0 |

| 3        | 93750                       | 0 | 0 | 12      | 375000                      | 0 | 0 |

| 3.6864   | 115200                      | 0 | 0 | 12.288  | 384000                      | 0 | 0 |

| 4        | 125000                      | 0 | 0 | 14      | 437500                      | 0 | 0 |

| 4.9152   | 153600                      | 0 | 0 | 14.7456 | 460800                      | 0 | 0 |

| 5        | 156250                      | 0 | 0 | 16      | 500000                      | 0 | 0 |

| 6        | 187500                      | 0 | 0 | 17.2032 | 537600                      | 0 | 0 |

| 6.144    | 192000                      | 0 | 0 | 18      | 562500                      | 0 | 0 |

| 7.3728   | 230400                      | 0 | 0 | 20      | 625000                      | 0 | 0 |

#### Table 14.3 Maximum Bit Rate for Each Frequency (Asynchronous Mode)

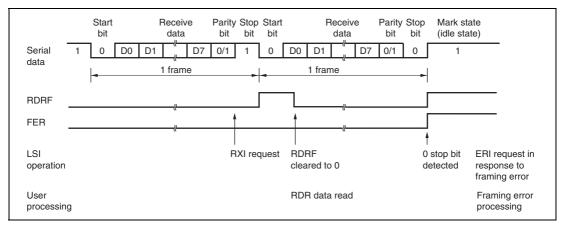

#### 14.4.4 Serial Data Reception

Figure 14.7 shows an example of operation for reception in asynchronous mode. In serial reception, the SCI operates as described below.

- 1. The SCI3 monitors the communication line. If a start bit is detected, the SCI3 performs internal synchronization, receives data in RSR, and checks the parity bit and stop bit.

- 2. If an overrun error occurs (when reception of the next data is completed while the RDRF flag is still set to 1), the OER bit in SSR is set to 1. If the RIE bit in SCR3 is set to 1 at this time, an ERI interrupt request is generated. Receive data is not transferred to RDR.

- 3. If a parity error is detected, the PER bit in SSR is set to 1 and receive data is transferred to RDR. If the RIE bit in SCR3 is set to 1 at this time, an ERI interrupt request is generated.

- 4. If a framing error is detected (when the stop bit is 0), the FER bit in SSR is set to 1 and receive data is transferred to RDR. If the RIE bit in SCR3 is set to 1 at this time, an ERI interrupt request is generated.

- 5. If reception is completed successfully, the RDRF bit in SSR is set to 1, and receive data is transferred to RDR. If the RIE bit in SCR3 is set to 1 at this time, an RXI interrupt request is generated. Continuous reception is possible because the RXI interrupt routine reads the receive data transferred to RDR before reception of the next receive data has been completed.

Figure 14.7 Example SCI3 Operation in Reception in Asynchronous Mode (8-Bit Data, Parity, One Stop Bit)

#### 14.8 Usage Notes

#### 14.8.1 Break Detection and Processing

When framing error detection is performed, a break can be detected by reading the RxD pin value directly. In a break, the input from the RxD pin becomes all 0, setting the FER flag, and possibly the PER flag. Note that as the SCI3 continues the receive operation after receiving a break, even if the FER flag is cleared to 0, it will be set to 1 again.

#### 14.8.2 Mark State and Break Sending

When TE is 0, the TxD pin is used as an I/O port whose direction (input or output) and level are determined by PCR and PDR. This can be used to set the TxD pin to mark state (high level) or send a break during serial data transmission. To maintain the communication line at mark state until TE is set to 1, set both PCR and PDR to 1. As TE is cleared to 0 at this point, the TxD pin becomes an I/O port, and 1 is output from the TxD pin. To send a break during serial transmission, first set PCR to 1 and PDR to 0, and then clear TE to 0. When TE is cleared to 0, the transmitter is initialized regardless of the current transmission state, the TxD pin becomes an I/O port, and 0 is output from the TxD pin.

#### 14.8.3 Receive Error Flags and Transmit Operations (Clocked Synchronous Mode Only)

Transmission cannot be started when a receive error flag (OER, PER, or FER) is set to 1, even if the TDRE flag is cleared to 0. Be sure to clear the receive error flags to 0 before starting transmission. Note also that receive error flags cannot be cleared to 0 even if the RE bit is cleared to 0.

#### 15.3.5 I<sup>2</sup>C Bus Status Register (ICSR)

ICSR performs confirmation of interrupt request flags and status.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                           |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------|

| 7   | TDRE     | 0                | R/W | Transmit Data Register Empty                                                                                          |

|     |          |                  |     | [Setting conditions]                                                                                                  |

|     |          |                  |     | <ul> <li>When data is transferred from ICDRT to ICDRS and<br/>ICDRT becomes empty</li> </ul>                          |

|     |          |                  |     | When TRS is set                                                                                                       |

|     |          |                  |     | <ul> <li>When a start condition (including re-transfer) has<br/>been issued</li> </ul>                                |

|     |          |                  |     | When transmit mode is entered from receive mode in<br>slave mode                                                      |

|     |          |                  |     | [Clearing conditions]                                                                                                 |

|     |          |                  |     | • When 0 is written in TDRE after reading TDRE = 1                                                                    |

|     |          |                  |     | When data is written to ICDRT with an instruction                                                                     |

| 6   | TEND     | 0                | R/W | Transmit End                                                                                                          |

|     |          |                  |     | [Setting conditions]                                                                                                  |

|     |          |                  |     | <ul> <li>When the ninth clock of SCL rises with the I<sup>2</sup>C bus<br/>format while the TDRE flag is 1</li> </ul> |

|     |          |                  |     | When the final bit of transmit frame is sent with the<br>clock synchronous serial format                              |

|     |          |                  |     | [Clearing conditions]                                                                                                 |

|     |          |                  |     | • When 0 is written in TEND after reading TEND = 1                                                                    |

|     |          |                  |     | When data is written to ICDRT with an instruction                                                                     |

| 5   | RDRF     | 0                | R/W | Receive Data Register Full                                                                                            |

|     |          |                  |     | [Setting condition]                                                                                                   |

|     |          |                  |     | <ul> <li>When a receive data is transferred from ICDRS to<br/>ICDRR</li> </ul>                                        |

|     |          |                  |     | [Clearing conditions]                                                                                                 |

|     |          |                  |     | • When 0 is written in RDRF after reading RDRF = 1                                                                    |

|     |          |                  |     | When ICDRR is read with an instruction                                                                                |

#### 15.3.6 Slave Address Register (SAR)

SAR selects the communication format and sets the slave address. When the chip is in slave mode with the  $I^2C$  bus format, if the upper 7 bits of SAR match the upper 7 bits of the first frame received after a start condition, the chip operates as the slave device.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                      |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 1 | SVA6 to  | All 0            | R/W | Slave Address 6 to 0                                                                                                                             |

|        | SVA0     |                  |     | These bits set a unique address in bits SVA6 to SVA0, differing form the addresses of other slave devices connected to the I <sup>2</sup> C bus. |

| 0      | FS       | 0                | R/W | Format Select                                                                                                                                    |

|        |          |                  |     | 0: I <sup>2</sup> C bus format is selected.                                                                                                      |

|        |          |                  |     | 1: Clocked synchronous serial format is selected.                                                                                                |

## Section 17 EEPROM

The H8/3694N has an on-chip 512-byte EEPROM. The block diagram of the EEPROM is shown in figure 17.1.

#### 17.1 Features

• Two writing methods:

1-byte write

Page write: Page size 8 bytes

- Three reading methods: Current address read Random address read Sequential read

- Acknowledge polling possible

- Write cycle time:

10 ms (power supply voltage Vcc = 2.7 V or more)

- Write/Erase endurance: 10<sup>4</sup> cycles/byte (byte write mode), 10<sup>5</sup> cycles/page (page write mode)

- Data retention:

10 years after the write cycle of  $10^4$  cycles (page write mode)

• Interface with the CPU

I<sup>2</sup>C bus interface (complies with the standard of Philips Corporation)

Device code 1010

Sleep address code can be changed (initial value: 000)

The I<sup>2</sup>C bus is open to the outside, so the EEPROM can be directly accessed from the outside.

## 17.5 Usage Notes

#### 17.5.1 Data Protection at $V_{cc}$ On/Off

When  $V_{cc}$  is turned on or off, the data might be destroyed by malfunction. Be careful of the notices described below to prevent the data to be destroyed.

- 1. SCL and SDA should be fixed to  $V_{cc}$  or  $V_{ss}$  during  $V_{cc}$  on/off.

- 2.  $V_{cc}$  should be turned off after the EEPROM is placed in a standby state.

- 3. When  $V_{cc}$  is turned on from the intermediate level, malfunction is caused, so  $V_{cc}$  should be turned on from the ground level ( $V_{ss}$ ).

- 4.  $V_{cc}$  turn on speed should be longer than 10 us.

#### 17.5.2 Write/Erase Endurance

The endurance is  $10^5$  cycles/page (1% cumulative failure rate) in case of page programming and  $10^4$  cycles/byte in case of byte programming. The data retention time is more than 10 years when a device is page-programmed less than  $10^4$  cycles.

#### 17.5.3 Noise Suppression Time

This EEPROM has a noise suppression function at SCL and SDA inputs, that cuts noise of width less than 50 ns. Be careful not to allow noise of width more than 50 ns because the noise of with more than 50 ms is recognized as an active pulse.

#### Table 21.2 DC Characteristics (2)

$V_{cc} = 3.0 \text{ V}$  to 5.5 V,  $V_{ss} = 0.0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$ , unless otherwise indicated.

|                   |                     |                 |                                                                                                                         |     | Va  | ues |      |       |

|-------------------|---------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|-------|

| Item              | Symbol              | Applicable Pins | Test Condition                                                                                                          | Min | Тур | Max | Unit | Notes |

| EEPROM<br>current | I <sub>EEW</sub>    | V <sub>cc</sub> | $V_{cc}$ = 5.0 V, $t_{scL}$ = 2.5 $\mu s$ (when writing)                                                                |     | —   | 2.0 | mA   | *     |

| consump-<br>tion  | I <sub>EER</sub>    | V <sub>cc</sub> | $\label{eq:V_cc} \begin{array}{l} V_{cc} = 5.0 \text{ V}, \ t_{scl} = 2.5 \\ \mu s \ (\text{when reading}) \end{array}$ | —   | _   | 0.3 | mA   | _     |

|                   | I <sub>EESTBY</sub> | V <sub>cc</sub> | $V_{cc}$ = 5.0 V, $t_{scL}$ = 2.5 $\mu$ s (at standby)                                                                  | _   | —   | 3.0 | μA   | _     |

Note: \* The current consumption of the EEPROM chip is shown. For the current consumption of H8/3694N, add the above current values to the current consumption of H8/3694F.

#### 21.3.2 DC Characteristics

#### Table 21.12 DC Characteristics (1)

$V_{cc} = 2.7$  to 5.5 V,  $V_{ss} = 0.0$  V,  $T_a = -20$  to +75°C, unless otherwise indicated.

|                       |                 |                                                             |                                          |                      | Value | es                    |      |       |

|-----------------------|-----------------|-------------------------------------------------------------|------------------------------------------|----------------------|-------|-----------------------|------|-------|

| Item                  | Symbol          | Applicable Pins                                             | Test Condition                           | Min                  | Тур   | Max                   | Unit | Notes |

| Input high<br>voltage | V <sub>IH</sub> | RES, NMI,<br>WKP0 to WKP5,<br>IRQ0 to IRQ3,<br>ADTRG,TMRIV, | $V_{\rm cc}$ = 4.0 to 5.5 V              | V <sub>cc</sub> ×0.8 | —     | V <sub>cc</sub> + 0.3 | V    |       |

|                       |                 | TMCIV, FTCI,<br>FTIOA to FTIOD,<br>SCK3, TRGV               |                                          | $V_{cc} \times 0.9$  | _     | V <sub>cc</sub> + 0.3 | _    |       |

|                       |                 | RXD, SCL, SDA,<br>P10 to P12,<br>P14 to P17,<br>P20 to P22, | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | V <sub>cc</sub> ×0.7 | _     | V <sub>cc</sub> + 0.3 | V    | _     |

|                       |                 | P50 to P57,<br>P74 to P76,<br>P80 to P87                    |                                          | $V_{cc} \times 0.8$  | _     | V <sub>cc</sub> + 0.3 |      |       |

|                       |                 | PB0 to PB7                                                  | $V_{\rm cc}$ = 4.0 to 5.5 V              | $V_{cc} 	imes 0.7$   |       | $AV_{cc} + 0.3$       | V    | -     |

|                       |                 |                                                             |                                          | $V_{cc} 	imes 0.8$   | _     | $AV_{cc} + 0.3$       | _    |       |

|                       |                 | OSC1                                                        | $V_{cc}$ = 4.0 to 5.5 V                  | $V_{cc} - 0.5$       | —     | $V_{cc}$ + 0.3        | V    | _     |

|                       |                 |                                                             |                                          | $V_{\rm cc} - 0.3$   | —     | $V_{cc}$ + 0.3        |      | _     |

| Input low<br>voltage  | V <sub>IL</sub> | RES, NMI,<br>WKP0 to WKP5,<br>IRQ0 to IRQ3,<br>ADTRG,TMRIV, | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | -0.3                 | _     | $V_{cc} \times 0.2$   | V    |       |

|                       |                 | TMCIV, FTCI,<br>FTIOA to FTIOD,<br>SCK3, TRGV               |                                          | -0.3                 | _     | $V_{cc} \times 0.1$   |      |       |

|                       |                 | RXD, SCL, SDA,<br>P10 to P12,<br>P14 to P17,<br>P20 to P22, | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | -0.3                 | —     | $V_{cc} \times 0.3$   | V    |       |

|                       |                 | P50 to P57,<br>P74 to P76,<br>P80 to P87,<br>PB0 to PB7     |                                          | -0.3                 | _     | $V_{cc} \times 0.2$   |      |       |

|                       |                 | OSC1                                                        | $V_{\rm cc}$ = 4.0 to 5.5 V              | -0.3                 | _     | 0.5                   | V    | _     |

|                       |                 |                                                             |                                          | -0.3                 | —     | 0.3                   |      |       |

|       |                                |              | Addressing Mode and<br>Instruction Length (bytes) |               |      |           |             |      |          |       |  |                                                                                                                                                  |   |     |        |        |               |    | No<br>Stat | . of<br>es <sup>*1</sup> |

|-------|--------------------------------|--------------|---------------------------------------------------|---------------|------|-----------|-------------|------|----------|-------|--|--------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|--------|--------|---------------|----|------------|--------------------------|

|       | Mnemonic                       |              | #xx                                               | Rn            | @ERn | @(d, ERn) | @-ERn/@ERn+ | @ aa | @(d, PC) | ) @aa |  | Operation                                                                                                                                        |   |     | ditio  |        | 1             |    | Normal     | Advanced                 |

| 050   |                                | Operand Size | ŧ                                                 | <b>⊮</b><br>2 | ø    | ø         | ø           | ø    | ø        | 0     |  | ERd32–1 $\rightarrow$ ERd32                                                                                                                      | 1 | н   | N<br>↓ | z<br>≎ | <b>∨</b><br>↓ | С  |            | <b>∢</b><br>2            |

| DEC   | DEC.L #1, ERd<br>DEC.L #2, ERd | L            |                                                   | 2             |      |           |             |      |          |       |  | ERd32–1 $\rightarrow$ ERd32<br>ERd32–2 $\rightarrow$ ERd32                                                                                       | _ | -   | ↓ ↓    | ↓ ↓    | ↓ ↓           | -  |            | 2                        |

| DAS   | DAS.Rd                         | B            |                                                   | 2             |      |           |             |      |          |       |  | Rd8 decimal adjust<br>$\rightarrow$ Rd8                                                                                                          | - | *   | \$     | \$     | *             | _  |            | 2                        |

| MULXU | MULXU. B Rs, Rd                | В            |                                                   | 2             |      |           |             |      |          |       |  | $Rd8 \times Rs8 \rightarrow Rd16$<br>(unsigned multiplication)                                                                                   | — | —   | —      | -      | -             | -  | 1          | 4                        |

|       | MULXU. W Rs, ERd               | W            |                                                   | 2             |      |           |             |      |          |       |  | $Rd16 \times Rs16 \rightarrow ERd32$<br>(unsigned multiplication)                                                                                | — | —   | —      | _      | _             | _  | 2          | 2                        |

| MULXS | MULXS. B Rs, Rd                | В            |                                                   | 4             |      |           |             |      |          |       |  | $Rd8 \times Rs8 \rightarrow Rd16$<br>(signed multiplication)                                                                                     | _ | _   | \$     | \$     | _             | _  | 1          | 6                        |

|       | MULXS. W Rs, ERd               | W            |                                                   | 4             |      |           |             |      |          |       |  | $Rd16 \times Rs16 \rightarrow ERd32$<br>(signed multiplication)                                                                                  | - | -   | \$     | \$     | -             | -  | 2          | 4                        |

| DIVXU | DIVXU. B Rs, Rd                | В            |                                                   | 2             |      |           |             |      |          |       |  | Rd16 $\div$ Rs8 $\rightarrow$ Rd16<br>(RdH: remainder,<br>RdL: quotient)<br>(unsigned division)                                                  |   |     | (6)    | (7)    |               |    | 1          | 4                        |

|       | DIVXU. W Rs, ERd               | W            |                                                   | 2             |      |           |             |      |          |       |  | $\label{eq:remainder} \begin{array}{l} ERd32 \div Rs16 \rightarrow ERd32 \\ (Ed: remainder, \\ Rd: quotient) \\ (unsigned division) \end{array}$ |   | _   | (6)    | (7)    |               | _  | 2          | 2                        |

| DIVXS | DIVXS. B Rs, Rd                | В            |                                                   | 4             |      |           |             |      |          |       |  | $\begin{array}{l} Rd16 \div Rs8 \to Rd16 \\ (RdH: remainder, \\ RdL: quotient) \\ (signed division) \end{array}$                                 | - | _   | (8)    | (7)    | _             | —  | 1          | 6                        |

|       | DIVXS. W Rs, ERd               | W            |                                                   | 4             |      |           |             |      |          |       |  | $\label{eq:result} \begin{array}{l} ERd32 \div Rs16 \rightarrow ERd32 \\ (Ed: remainder, \\ Rd: quotient) \\ (signed division) \end{array}$      | _ | _   | (8)    | (7)    | _             | _  | 2          | 4                        |

| CMP   | CMP.B #xx:8, Rd                | В            | 2                                                 |               |      |           |             |      |          |       |  | Rd8–#xx:8                                                                                                                                        | — | \$  | \$     | \$     | \$            | \$ | 2          | 2                        |

|       | CMP.B Rs, Rd                   | В            |                                                   | 2             |      |           |             |      |          |       |  | Rd8–Rs8                                                                                                                                          | _ | \$  | \$     | \$     | \$            | \$ | 2          | 2                        |

|       | CMP.W #xx:16, Rd               | W            | 4                                                 |               |      |           |             |      |          |       |  | Rd16-#xx:16                                                                                                                                      | _ | (1) | \$     | \$     | \$            | \$ | 4          | 1                        |

|       | CMP.W Rs, Rd                   | W            |                                                   | 2             |      |           |             |      |          |       |  | Rd16-Rs16                                                                                                                                        | - | (1) |        | \$     | ↕             | \$ | 2          | 2                        |

|       | CMP.L #xx:32, ERd              | L            | 6                                                 |               |      |           |             |      |          |       |  | ERd32-#xx:32                                                                                                                                     | - | (2) |        | \$     | \$            | \$ | 4          | 4                        |

|       | CMP.L ERs, ERd                 | L            |                                                   | 2             |      |           |             |      |          |       |  | ERd32–ERs32                                                                                                                                      |   | (2) | 1      | 1      | 1             | 1  | 2          | 2                        |

|      |            |         | Addressing Mode and<br>Instruction Length (bytes) |    |      |         |            |     |        |      | ) |                                                                                                   |   |                |                |                |                |                | No<br>Stat | . of<br>es <sup>*1</sup> |

|------|------------|---------|---------------------------------------------------|----|------|---------|------------|-----|--------|------|---|---------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|----------------|----------------|------------|--------------------------|

|      | Mnemonic   |         |                                                   |    | @ERn | d, ERn) | -ERn/@ERn+ | a   | d, PC) | @ aa |   | Operation                                                                                         |   | Con            | ditio          | n Co           | ode            |                | Normal     | Advanced                 |

|      |            | Operand | XX#                                               | Rn | 0    | @(d,    | 8          | @aa | @(d,   | 0    | Ι |                                                                                                   | I | н              | Ν              | z              | v              | С              | ٩          | Ad                       |

| NEG  | NEG.B Rd   | В       |                                                   | 2  |      |         |            |     |        |      |   | $0\text{Rd8} \rightarrow \text{Rd8}$                                                              | - | \$             | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | 1          | 2                        |

|      | NEG.W Rd   | W       |                                                   | 2  |      |         |            |     |        |      |   | $0-Rd16 \rightarrow Rd16$                                                                         | - | \$             | $\updownarrow$ | $\updownarrow$ | \$             | \$             | 1          | 2                        |

|      | NEG.L ERd  | L       |                                                   | 2  |      |         |            |     |        |      |   | $0-ERd32 \rightarrow ERd32$                                                                       | — | $\updownarrow$ | \$             | \$             | $\updownarrow$ | $\updownarrow$ | 1          | 2                        |

| EXTU | EXTU.W Rd  | W       |                                                   | 2  |      |         |            |     |        |      |   | $0 \rightarrow (\text{})$ of Rd16)                                                                | — | -              | 0              | \$             | 0              | —              | :          | 2                        |

|      | EXTU.L ERd | L       |                                                   | 2  |      |         |            |     |        |      |   | $0 \rightarrow (\text{obits 31 to 16})$<br>of ERd32)                                              | - | -              | 0              | \$             | 0              | —              | :          | 2                        |

| EXTS | EXTS.W Rd  | W       |                                                   | 2  |      |         |            |     |        |      |   | ( <bit 7=""> of Rd16) <math>\rightarrow</math><br/>(<bits 15="" 8="" to=""> of Rd16)</bits></bit> | - | -              | \$             | \$             | 0              | -              | :          | 2                        |

|      | EXTS.L ERd | L       |                                                   | 2  |      |         |            |     |        |      |   | $( of ERd32) \rightarrow$<br>( <bits 16="" 31="" to=""> of ERd32)</bits>                          | - | _              | \$             | \$             | 0              | -              | :          | 2                        |

#### 7. System Control Instructions

|       |                       |         |     |    |      | essi<br>tion | •           |      |          |      | ) |                                                                                                                                                       |                |     |    |        |          |    | No<br>Stat | . of<br>es <sup>*1</sup> |

|-------|-----------------------|---------|-----|----|------|--------------|-------------|------|----------|------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|----|--------|----------|----|------------|--------------------------|

|       | Mnemonic              |         | ×   |    | @ERn | @(d, ERn)    | @-ERn/@ERn+ | @ aa | @(d, PC) | @ aa |   | Operation                                                                                                                                             |                | Con |    | Normal | Advanced |    |            |                          |

|       |                       | Operand | XX# | Rn | 0    | 0            | 0           | 0    | 0        | 0    |   |                                                                                                                                                       | Т              | н   | N  | z      | v        | с  | ž          | Ac                       |

| TRAPA | TRAPA #x:2            | -       |     |    |      |              |             |      |          |      | 2 | $\begin{array}{l} PC \rightarrow @-SP \\ CCR \rightarrow @-SP \\ <\!\!vector\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 1              | _   |    |        | _        | -  | 14         | 16                       |

| RTE   | RTE                   | -       |     |    |      |              |             |      |          |      |   | $CCR \leftarrow @SP+$<br>$PC \leftarrow @SP+$                                                                                                         | \$             | \$  | \$ | \$     | \$       | \$ | 1          | 0                        |

| SLEEP | SLEEP                 | -       |     |    |      |              |             |      |          |      |   | Transition to power-<br>down state                                                                                                                    | -              | —   | —  | _      | -        | -  | 2          | 2                        |

| LDC   | LDC #xx:8, CCR        | В       | 2   |    |      |              |             |      |          |      |   | $#xx:8 \rightarrow CCR$                                                                                                                               | \$             | \$  | \$ | \$     | \$       | \$ | 2          | 2                        |

|       | LDC Rs, CCR           | В       |     | 2  |      |              |             |      |          |      |   | $Rs8 \rightarrow CCR$                                                                                                                                 | \$             | \$  | \$ | \$     | \$       | \$ | 2          | 2                        |

|       | LDC @ERs, CCR         | W       |     |    | 4    |              |             |      |          |      |   | $@ERs\toCCR$                                                                                                                                          | \$             | \$  | \$ | \$     | \$       | \$ | 6          | 6                        |

|       | LDC @(d:16, ERs), CCR | W       |     |    |      | 6            |             |      |          |      |   | @(d:16, ERs) → CCR                                                                                                                                    | \$             | \$  | \$ | \$     | \$       | \$ | 8          | 3                        |

|       | LDC @(d:24, ERs), CCR | W       |     |    |      | 10           |             |      |          |      |   | @(d:24, ERs) → CCR                                                                                                                                    | \$             | \$  | \$ | \$     | \$       | \$ | 1          | 2                        |

|       | LDC @ERs+, CCR        | W       |     |    |      |              | 4           |      |          |      |   | @ERs → CCR<br>ERs32+2 → ERs32                                                                                                                         | \$             | \$  | \$ | \$     | \$       | \$ | 8          | 3                        |

|       | LDC @aa:16, CCR       | W       |     |    |      |              |             | 6    |          |      |   | @aa:16 $\rightarrow$ CCR                                                                                                                              | $\updownarrow$ | \$  | \$ | \$     | \$       | \$ | 8          | 3                        |

|       | LDC @aa:24, CCR       | W       |     |    |      |              |             | 8    |          |      |   | @aa:24 $\rightarrow$ CCR                                                                                                                              | \$             | \$  | \$ | \$     | \$       | \$ | 1          | 0                        |

| STC   | STC CCR, Rd           | В       |     | 2  |      |              |             |      |          |      |   | $CCR \rightarrow Rd8$                                                                                                                                 | —              | —   | —  | -      | -        | -  | 2          | 2                        |

|       | STC CCR, @ERd         | W       |     |    | 4    |              |             |      |          |      |   | $CCR \rightarrow @ERd$                                                                                                                                | —              | —   | —  | -      | -        | -  | 6          | 6                        |

|       | STC CCR, @(d:16, ERd) | W       |     |    |      | 6            |             |      |          |      |   | $CCR \rightarrow @(d:16, ERd)$                                                                                                                        | —              | —   | —  | —      | -        | -  | 8          | 3                        |

|       | STC CCR, @(d:24, ERd) | W       |     |    |      | 10           |             |      |          |      |   | $CCR \rightarrow @(d:24, ERd)$                                                                                                                        | —              | —   | —  | -      | -        | -  | 1          | 2                        |

|       | STC CCR, @-ERd        | W       |     |    |      |              | 4           |      |          |      |   | $\begin{array}{l} ERd32-2 \rightarrow ERd32 \\ CCR \rightarrow @ ERd \end{array}$                                                                     | -              | —   | —  | _      | _        | -  | 8          | 3                        |

|       | STC CCR, @aa:16       | W       |     |    |      |              |             | 6    |          |      |   | $CCR \rightarrow @aa:16$                                                                                                                              | —              | —   | —  | —      | —        | —  | 8          | 3                        |

|       | STC CCR, @aa:24       | W       |     |    |      |              |             | 8    |          |      |   | $CCR \rightarrow @aa:24$                                                                                                                              | —              | —   | —  | —      | —        | -  | 1          | 0                        |

| ANDC  | ANDC #xx:8, CCR       | В       | 2   |    |      |              |             |      |          |      |   | $CCR_{\wedge}\#xx:8 \rightarrow CCR$                                                                                                                  | \$             | \$  | \$ | \$     | \$       | \$ | 2          | 2                        |

| ORC   | ORC #xx:8, CCR        | В       | 2   |    |      |              |             |      |          |      |   | $CCR \lor \#xx:8 \rightarrow CCR$                                                                                                                     | \$             | \$  | \$ | \$     | \$       | \$ | 2          | 2                        |

| XORC  | XORC #xx:8, CCR       | В       | 2   |    |      |              |             |      |          |      |   | $CCR \oplus \#xx:8 \rightarrow CCR$                                                                                                                   | $\uparrow$     | \$  | \$ | \$     | \$       | \$ | 2          | 2                        |

| NOP   | NOP                   | -       |     |    |      |              |             |      |          |      | 2 | $PC \leftarrow PC+2$                                                                                                                                  | —              | —   | _  | -      | -        | -  | 2          | 2                        |

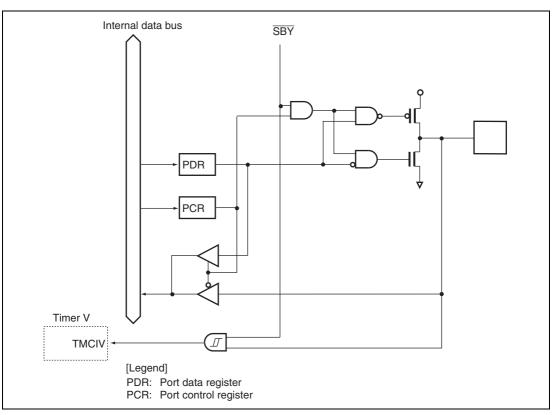

Figure B.12 Port 7 Block Diagram (P75)

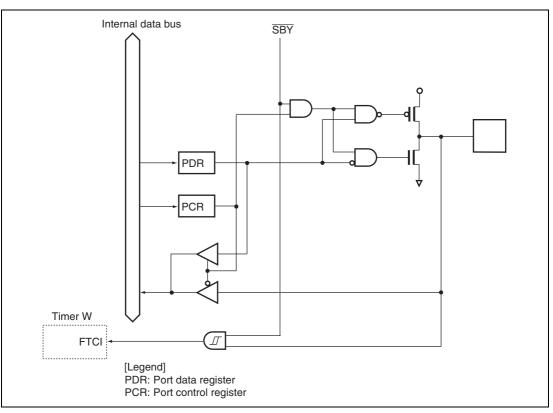

Figure B.16 Port 8 Block Diagram (P80)

# Main Revisions and Additions in this Edition

| Item                                                                                                                            | Page    | Revision (See Manual for Details)                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface                                                                                                                         | vi, vii | Notes:                                                                                                                                                                                                                                          |

|                                                                                                                                 |         | When using the on-chip emulator (E7, E8) for H8/3694 program development and debugging, the following restrictions must be noted.                                                                                                               |

|                                                                                                                                 |         | <ol> <li>The NMI pin is reserved for the E7 or E8, and cannot be<br/>used.</li> </ol>                                                                                                                                                           |

|                                                                                                                                 |         | <ol> <li>Area H'7000 to H'7FFF is used by the E7 or E8, and is not<br/>available to the user.</li> </ol>                                                                                                                                        |

|                                                                                                                                 |         | 5. When the E7 or E8 is used, address breaks can be set as<br>either available to the user or for use by the E7 or E8. If<br>address breaks are set as being used by the E7 or E8, the<br>address break control registers must not be accessed. |

|                                                                                                                                 |         | <ol> <li>When the E7 or E8 is used, NMI is an input/output pin<br/>(open-drain in output mode), P85 and P87 are input pins,<br/>and P86 is an output pin.</li> </ol>                                                                            |

|                                                                                                                                 |         | Note has been deleted.                                                                                                                                                                                                                          |

| Section 1 Overview<br>Figure 1.1 Internal Block<br>Diagram of H8/3694<br>Group of F-ZTAT <sup>™</sup><br>and Mask-ROM Versions, | 4, 5    | Timer V     IIC2       A/D     POR/LVD       converter     POR/LVD       (optional)     m                                                                                                                                                       |

| Figure 1.2 Internal Block<br>Diagram of H8/3694N<br>(EEPROM Stacked<br>Version)                                                 |         | Data bus (upper)                                                                                                                                                                                                                                |

-AVcc