Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | H8/300H                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | I²C, SCI                                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 29                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | 48-LQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3694gfxiv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **General Precautions on Handling of Product**

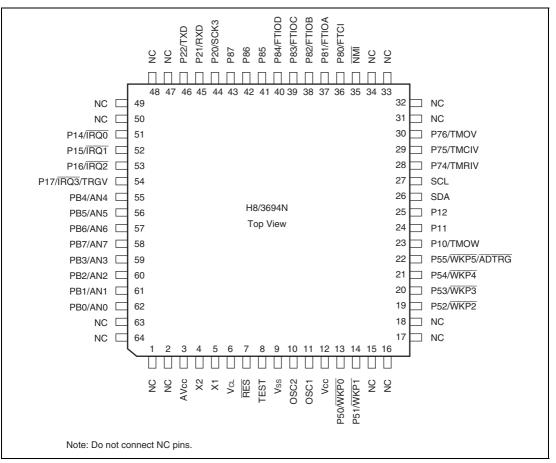

- 1. Treatment of NC Pins

- Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

- 2. Treatment of Unused Input Pins

- Note: Fix all unused input pins to high or low level. Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfunction may occur.

- 3. Processing before Initialization

- Note: When power is first supplied, the product's state is undefined. The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

- 4. Prohibition of Access to Undefined or Reserved Addresses

- Note: Access to undefined or reserved addresses is prohibited. The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

Renesas

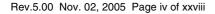

Figure 1.2 Internal Block Diagram of H8/3694N (EEPROM Stacked Version)

Figure 1.5 Pin Arrangement of H8/3694N (EEPROM Stacked Version) (FP-64E)

## 2.3 Data Formats

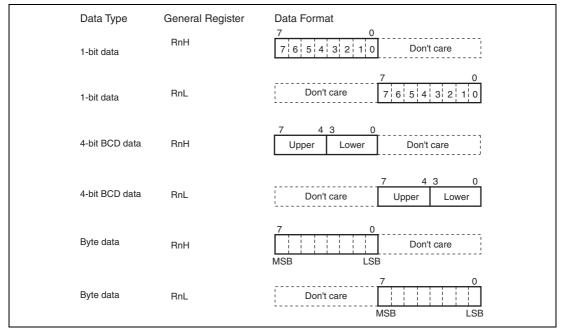

The H8/300H CPU can process 1-bit, 4-bit (BCD), 8-bit (byte), 16-bit (word), and 32-bit (longword) data. Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data. The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

#### 2.3.1 General Register Data Formats

Figure 2.5 shows the data formats in general registers.

Figure 2.5 General Register Data Formats (1)

| No. | Addressing Mode                                                               | Symbol                  |

|-----|-------------------------------------------------------------------------------|-------------------------|

| 1   | Register direct                                                               | Rn                      |

| 2   | Register indirect                                                             | @ERn                    |

| 3   | Register indirect with displacement                                           | @(d:16,ERn)/@(d:24,ERn) |

| 4   | Register indirect with post-increment<br>Register indirect with pre-decrement | @ERn+<br>@–ERn          |

| 5   | Absolute address                                                              | @aa:8/@aa:16/@aa:24     |

| 6   | Immediate                                                                     | #xx:8/#xx:16/#xx:32     |

| 7   | Program-counter relative                                                      | @(d:8,PC)/@(d:16,PC)    |

| 8   | Memory indirect                                                               | @@aa:8                  |

#### Table 2.10 Addressing Modes

#### **Register Direct**—**Rn**

The register field of the instruction specifies an 8-, 16-, or 32-bit general register containing the operand. R0H to R7H and R0L to R7L can be specified as 8-bit registers. R0 to R7 and E0 to E7 can be specified as 16-bit registers. ER0 to ER7 can be specified as 32-bit registers.

#### Register Indirect—@ERn

The register field of the instruction code specifies an address register (ERn), the lower 24 bits of which contain the address of the operand on memory.

#### Register Indirect with Displacement—@(d:16, ERn) or @(d:24, ERn)

A 16-bit or 24-bit displacement contained in the instruction is added to an address register (ERn) specified by the register field of the instruction, and the lower 24 bits of the sum the address of a memory operand. A 16-bit displacement is sign-extended when added.

#### Register Indirect with Post-Increment or Pre-Decrement—@ERn+ or @-ERn

• Register indirect with post-increment—@ERn+

The register field of the instruction code specifies an address register (ERn) the lower 24 bits of which contains the address of a memory operand. After the operand is accessed, 1, 2, or 4 is added to the address register contents (32 bits) and the sum is stored in the address register. The value added is 1 for byte access, 2 for word access, or 4 for longword access. For the word or longword access, the register value should be even.

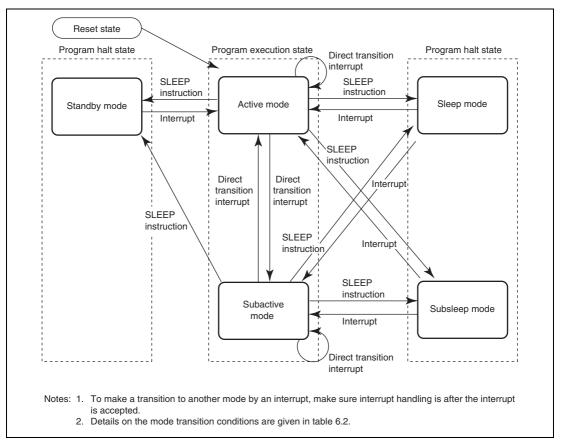

## 6.2 Mode Transitions and States of LSI

Figure 6.1 shows the possible transitions among these operating modes. A transition is made from the program execution state to the program halt state of the program by executing a SLEEP instruction. Interrupts allow for returning from the program halt state to the program execution state of the program. A direct transition between active mode and subactive mode, which are both program execution states, can be made without halting the program. The operating frequency can also be changed in the same modes by making a transition directly from active mode to active mode, and from subactive mode to subactive mode. RES input enables transitions from a mode to the reset state. Table 6.2 shows the transition conditions of each mode after the SLEEP instruction is executed and a mode to return by an interrupt. Table 6.3 shows the internal states of the LSI in each mode.

Figure 6.1 Mode Transition Diagram

#### 9.2.1 Port Control Register 2 (PCR2)

Initial Bit **Bit Name** Value R/W Description 7 to 3 Reserved \_\_\_\_ 2 PCR22 W When each of the port 2 pins P22 to P20 functions as an 0 general I/O port, setting a PCR2 bit to 1 makes the 1 PCR21 0 W corresponding pin an output port, while clearing the bit to 0 PCR20 0 W 0 makes the pin an input port.

PCR2 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 2.

#### 9.2.2 Port Data Register 2 (PDR2)

PDR2 is a general I/O port data register of port 2.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                               |

|--------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3 | —        | All 1            | —   | Reserved                                                                                                                                  |

|        |          |                  |     | These bits are always read as 1.                                                                                                          |

| 2      | P22      | 0                | R/W | PDR2 stores output data for port 2 pins.                                                                                                  |

| 1      | P21      | 0                | R/W | If PDR2 is read while PCR2 bits are set to 1, the value                                                                                   |

| 0      | P20      | 0                | R/W | stored in PDR2 is read. If PDR2 is read while PCR2 bits are cleared to 0, the pin states are read regardless of the value stored in PDR2. |

#### P56/SDA pin

| ICCR1 | PCR5  |                           |

|-------|-------|---------------------------|

| ICE   | PCR56 | Pin Function              |

| 0     | 0     | P56 input pin             |

|       | 1     | P56 output pin            |

| 1     | Х     | SDA I/O pin               |

|       | ICE   | ICE  PCR56    0  0   1  1 |

Legend: X: Don't care.

SDA performs the NMOS open-drain output, that enables a direct bus drive.

## P55/WKP5/ADTRG pin

| Register         | PMR5 | PCR5  |                      |

|------------------|------|-------|----------------------|

| Bit Name         | WKP5 | PCR55 | Pin Function         |

| Setting<br>Value | 0    | 0     | P55 input pin        |

|                  |      | 1     | P55 output pin       |

|                  | 1    | Х     | WKP5/ADTRG input pin |

Legend: X: Don't care.

## P54/WKP4 pin

| Register         | PMR5 | PCR5  |                |

|------------------|------|-------|----------------|

| Bit Name         | WKP4 | PCR54 | Pin Function   |

| Setting<br>Value | 0    | 0     | P54 input pin  |

|                  |      | 1     | P54 output pin |

|                  | 1    | Х     | WKP4 input pin |

Legend: X: Don't care.

#### P85 pin

| Register         | PCR8  |                |

|------------------|-------|----------------|

| Bit Name         | PCR85 | Pin Function   |

| Setting<br>Value | 0     | P85 input pin  |

|                  | 1     | P85 output pin |

#### P84/FTIOD pin

| Register         | TIOR1 |      |      | PCR8  |                            |

|------------------|-------|------|------|-------|----------------------------|

| Bit Name         | IOD2  | IOD1 | IOD0 | PCR84 | Pin Function               |

| Setting<br>Value | 0     | 0    | 0    | 0     | P84 input/FTIOD input pin  |

|                  |       |      |      | 1     | P84 output/FTIOD input pin |

|                  | 0     | 0    | 1    | Х     | FTIOD output pin           |

|                  | 0     | 1    | Х    | Х     | FTIOD output pin           |

|                  | 1     | Х    | Х    | 0     | P84 input/FTIOD input pin  |

|                  |       |      |      | 1     | P84 output/FTIOD input pin |

Legend: X: Don't care.

#### P83/FTIOC pin

| Register         | TIOR1 |      |                           | PCR8 |                            |

|------------------|-------|------|---------------------------|------|----------------------------|

| Bit Name         | IOC2  | IOC1 | 1 IOC0 PCR83 Pin Function |      | Pin Function               |

| Setting<br>Value | 0     | 0    | 0                         | 0    | P83 input/FTIOC input pin  |

|                  |       |      |                           | 1    | P83 output/FTIOC input pin |

|                  | 0     | 0    | 1                         | Х    | FTIOC output pin           |

|                  | 0     | 1    | Х                         | Х    | FTIOC output pin           |

|                  | 1     | Х    | Х                         | 0    | P83 input/FTIOC input pin  |

|                  |       |      |                           | 1    | P83 output/FTIOC input pin |

Legend: X: Don't care.

## 14.2 Input/Output Pins

Table 14.1 shows the SCI3 pin configuration.

#### Table 14.1 Pin Configuration

| Pin Name                  | Abbreviation | I/O    | Function                  |

|---------------------------|--------------|--------|---------------------------|

| SCI3 clock                | SCK3         | I/O    | SCI3 clock input/output   |

| SCI3 receive data input   | RXD          | Input  | SCI3 receive data input   |

| SCI3 transmit data output | TXD          | Output | SCI3 transmit data output |

## 14.3 Register Descriptions

The SCI3 has the following registers.

- Receive shift register (RSR)

- Receive data register (RDR)

- Transmit shift register (TSR)

- Transmit data register (TDR)

- Serial mode register (SMR)

- Serial control register 3 (SCR3)

- Serial status register (SSR)

- Bit rate register (BRR)

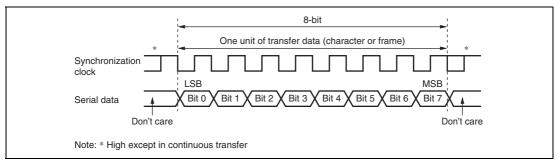

## 14.5 Operation in Clocked Synchronous Mode

Figure 14.9 shows the general format for clocked synchronous communication. In clocked synchronous mode, data is transmitted or received synchronous with clock pulses. A single character in the transmit data consists of the 8-bit data starting from the LSB. In clocked synchronous serial communication, data on the transmission line is output from one falling edge of the serial clock to the next. In clocked synchronous mode, the SCI3 receives data in synchronous with the rising edge of the serial clock. After 8-bit data is output, the transmission line holds the MSB state. In clocked synchronous mode, no parity or multiprocessor bit is added. Inside the SCI3, the transmitter and receiver are independent units, enabling full-duplex communication through the use of a common clock. Both the transmitter and the receiver also have a double-buffered structure, so data can be read or written during transmission or reception, enabling continuous data transfer.

Figure 14.9 Data Format in Clocked Synchronous Communication

## 14.5.1 Clock

Either an internal clock generated by the on-chip baud rate generator or an external synchronization clock input at the SCK3 pin can be selected, according to the setting of the COM bit in SMR and CKE0 and CKE1 bits in SCR3. When the SCI3 is operated on an internal clock, the serial clock is output from the SCK3 pin. Eight serial clock pulses are output in the transfer of one character, and when no transfer is performed the clock is fixed high.

## 14.5.2 SCI3 Initialization

Before transmitting and receiving data, the SCI3 should be initialized as described in a sample flowchart in figure 14.4.

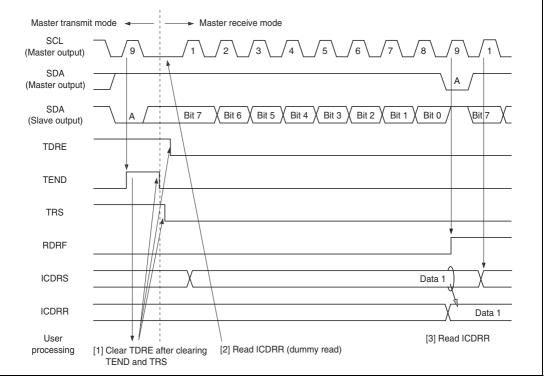

Figure 15.7 Master Receive Mode Operation Timing (1)

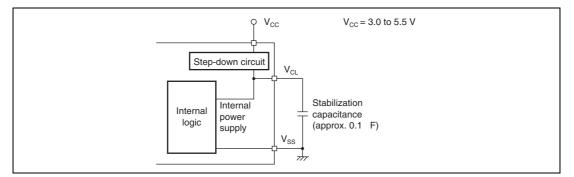

# Section 19 Power Supply Circuit

This LSI incorporates an internal power supply step-down circuit. Use of this circuit enables the internal power supply to be fixed at a constant level of approximately 3.0 V, independently of the voltage of the power supply connected to the external  $V_{cc}$  pin. As a result, the current consumed when an external power supply is used at 3.0 V or above can be held down to virtually the same low level as when used at approximately 3.0 V. If the external power supply is 3.0 V or below, the internal voltage will be practically the same as the external voltage. It is, of course, also possible to use the same level of external power supply voltage and internal power supply voltage without using the internal power supply step-down circuit.

## 19.1 When Using Internal Power Supply Step-Down Circuit

Connect the external power supply to the  $V_{cc}$  pin, and connect a capacitance of approximately 0.1  $\mu$ F between  $V_{cc}$  and  $V_{ss}$ , as shown in figure 19.1. The internal step-down circuit is made effective simply by adding this external circuit. In the external circuit interface, the external power supply voltage connected to  $V_{cc}$  and the GND potential connected to  $V_{ss}$  are the reference levels. For example, for port input/output levels, the  $V_{cc}$  level is the reference for the high level, and the  $V_{ss}$  level is that for the low level. The A/D converter analog power supply is not affected by the internal step-down circuit.

Figure 19.1 Power Supply Connection when Internal Step-Down Circuit is Used

RENESAS

| Register Name                    | Abbre-<br>viation | Bit<br>No | Address             | Module<br>Name    | Data<br>Bus<br>Width | Access<br>State |

|----------------------------------|-------------------|-----------|---------------------|-------------------|----------------------|-----------------|

| A/D data register B              | ADDRB             | 16        | H'FFB2              | A/D<br>converter  | 8                    | 3               |

| A/D data register C              | ADDRC             | 16        | H'FFB4              | A/D<br>converter  | 8                    | 3               |

| A/D data register D              | ADDRD             | 16        | H'FFB6              | A/D<br>converter  | 8                    | 3               |

| A/D control/status register      | ADCSR             | 8         | H'FFB8              | A/D<br>converter  | 8                    | 3               |

| A/D control register             | ADCR              | 8         | H'FFB9              | A/D<br>converter  | 8                    | 3               |

| _                                | _                 | _         | H'FFBA to<br>H'FFBF | _                 | _                    | _               |

| Timer control/status register WD | TCSRW<br>D        | 8         | H'FFC0              | WDT* <sup>3</sup> | 8                    | 2               |

| Timer counter WD                 | TCWD              | 8         | H'FFC1              | WDT* <sup>3</sup> | 8                    | 2               |

| Timer mode register WD           | TMWD              | 8         | H'FFC2              | WDT* <sup>3</sup> | 8                    | 2               |

|                                  | _                 | _         | H'FFC3              | _                 | _                    | _               |

| _                                | _                 | _         | H'FFC4 to<br>H'FFC7 | _                 | _                    | _               |

| Address break control register   | ABRKCR            | 8         | H'FFC8              | Address<br>break  | 8                    | 2               |

| Address break status register    | ABRKSR            | 8         | H'FFC9              | Address<br>break  | 8                    | 2               |

| Break address register H         | BARH              | 8         | H'FFCA              | Address<br>break  | 8                    | 2               |

| Break address register L         | BARL              | 8         | H'FFCB              | Address<br>break  | 8                    | 2               |

| Break data register H            | BDRH              | 8         | H'FFCC              | Address<br>break  | 8                    | 2               |

| Break data register L            | BDRL              | 8         | H'FFCD              | Address<br>break  | 8                    | 2               |

| _                                | —                 | —         | H'FFCE,<br>H'FFCF   | —                 | _                    | _               |

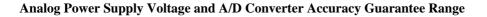

#### 21.2.4 A/D Converter Characteristics

## Table 21.6 A/D Converter Characteristics

$V_{\rm cc}$  = 3.0 to 5.5 V,  $V_{\rm ss}$  = 0.0 V,  $T_{\rm a}$  = –20 to +75°C, unless otherwise indicated.

|                                   |                     | Applicable       | Test                                       |                    | Value    | S               |                       | Reference                            |

|-----------------------------------|---------------------|------------------|--------------------------------------------|--------------------|----------|-----------------|-----------------------|--------------------------------------|

| Item                              | Symbol              | Pins             | Condition                                  | Min                | Тур      | Max             | Unit                  | Figure                               |

| Analog power supply voltage       | $AV_{cc}$           | $AV_{cc}$        |                                            | 3.3                | $V_{cc}$ | 5.5             | V                     | *1                                   |

| Analog input voltage              | $AV_{\text{IN}}$    | AN0 to<br>AN7    |                                            | $V_{\rm ss}$ – 0.3 | -        | $AV_{cc} + 0.3$ | V                     |                                      |

| Analog power supply current       | Al <sub>ope</sub>   | AV <sub>cc</sub> | $AV_{cc} = 5.0 V$<br>$f_{osc} =$<br>20 MHz | _                  | _        | 2.0             | mA                    |                                      |

|                                   | AI <sub>STOP1</sub> | $AV_{cc}$        |                                            | _                  | 50       | _               | μA                    | * <sup>2</sup><br>Reference<br>value |

|                                   | $AI_{\text{STOP2}}$ | AV <sub>cc</sub> |                                            | —                  | _        | 5.0             | μA                    | *3                                   |

| Analog input capacitance          | C <sub>AIN</sub>    | AN0 to<br>AN7    |                                            | _                  | _        | 30.0            | pF                    |                                      |

| Allowable signal source impedance | R <sub>AIN</sub>    | AN0 to<br>AN7    |                                            | _                  | _        | 5.0             | kΩ                    |                                      |

| Resolution (data length)          |                     |                  |                                            | 10                 | 10       | 10              | bit                   |                                      |

| Conversion time (single mode)     |                     |                  | AV <sub>cc</sub> = 3.3 to<br>5.5 V         | 134                | -        | _               | $t_{_{\mathrm{cyc}}}$ |                                      |

| Nonlinearity error                |                     |                  | _                                          | _                  | _        | ±7.5            | LSB                   | _                                    |

| Offset error                      |                     |                  | _                                          | _                  | —        | ±7.5            | LSB                   | _                                    |

| Full-scale error                  |                     |                  | _                                          | _                  | —        | ±7.5            | LSB                   | _                                    |

| Quantization error                |                     |                  | _                                          | _                  | —        | ±0.5            | LSB                   |                                      |

| Absolute accuracy                 |                     |                  |                                            | _                  | —        | ±8.0            | LSB                   | _                                    |

| Conversion time<br>(single mode)  |                     |                  | AV <sub>cc</sub> = 4.0 to<br>5.5 V         | 70                 | _        | _               | t <sub>cyc</sub>      |                                      |

| Nonlinearity error                |                     |                  | _                                          | _                  |          | ±7.5            | LSB                   |                                      |

| Offset error                      |                     |                  | _                                          | _                  | —        | ±7.5            | LSB                   | _                                    |

| Full-scale error                  |                     |                  | _                                          | _                  | _        | ±7.5            | LSB                   | _                                    |

| Quantization error                |                     |                  | _                                          | _                  | —        | ±0.5            | LSB                   | _                                    |

| Absolute accuracy                 |                     |                  | _                                          | _                  | _        | ±8.0            | LSB                   | _                                    |

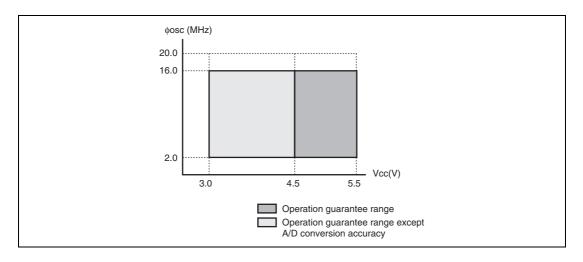

# Range of Power Supply Voltage and Oscillation Frequency when Low-Voltage Detection Circuit is Used

#### Appendix

| Bcc BLT d:8<br>BGT d:8<br>BLE d:8<br>BRA d:16(BT<br>BRN d:16(BF<br>BHI d:16<br>BLS d:16 |          | 2<br>2 |  |   | N |

|-----------------------------------------------------------------------------------------|----------|--------|--|---|---|

| BLE d:8<br>BRA d:16(BT<br>BRN d:16(BF<br>BHI d:16                                       |          |        |  |   |   |

| BRA d:16(BT<br>BRN d:16(BF<br>BHI d:16                                                  |          |        |  |   |   |

| BRN d:16(BF<br>BHI d:16                                                                 |          | 2      |  |   |   |

| BHI d:16                                                                                | d:16)    | 2      |  |   | 2 |

|                                                                                         | d:16)    | 2      |  |   | 2 |

| BLS d:16                                                                                |          | 2      |  |   | 2 |

|                                                                                         |          | 2      |  |   | 2 |

| BCC d:16(BH                                                                             | IS d:16) | 2      |  |   | 2 |

| BCS d:16(BL                                                                             | O d:16)  | 2      |  |   | 2 |

| BNE d:16                                                                                |          | 2      |  |   | 2 |

| BEQ d:16                                                                                |          | 2      |  |   | 2 |

| BVC d:16                                                                                |          | 2      |  |   | 2 |

| BVS d:16                                                                                |          | 2      |  |   | 2 |

| BPL d:16                                                                                |          | 2      |  |   | 2 |

| BMI d:16                                                                                |          | 2      |  |   | 2 |

| BGE d:16                                                                                |          | 2      |  |   | 2 |

| BLT d:16                                                                                |          | 2      |  |   | 2 |

| BGT d:16                                                                                |          | 2      |  |   | 2 |

| BLE d:16                                                                                |          | 2      |  |   | 2 |

| BCLR BCLR #xx:3,                                                                        | Rd       | 1      |  |   |   |

| BCLR #xx:3,                                                                             | @ERd     | 2      |  | 2 |   |

| BCLR #xx:3,                                                                             | @aa:8    | 2      |  | 2 |   |

| BCLR Rn, Ro                                                                             | ł        | 1      |  |   |   |

| BCLR Rn, @                                                                              | ERd      | 2      |  | 2 |   |

| BCLR Rn, @                                                                              | aa:8     | 2      |  | 2 |   |

| BIAND BIAND #xx:3                                                                       | , Rd     | 1      |  |   |   |

| BIAND #xx:3                                                                             | , @ERd   | 2      |  | 1 |   |

| BIAND #xx:3                                                                             | , @aa:8  | 2      |  | 1 |   |

| BILD BILD #xx:3, F                                                                      | Rd       | 1      |  |   |   |

| BILD #xx:3, @                                                                           | @ERd     | 2      |  | 1 |   |

| BILD #xx:3, @                                                                           | @aa:8    | 2      |  | 1 |   |

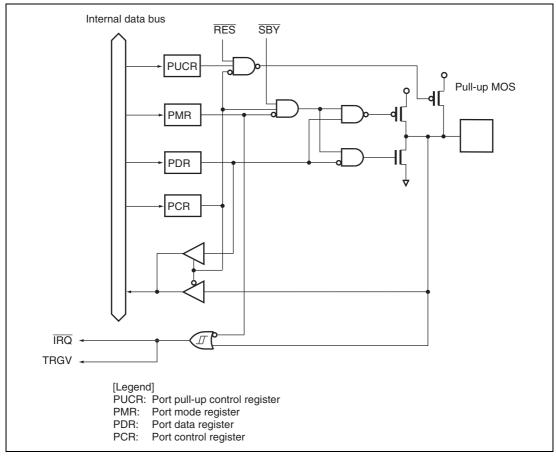

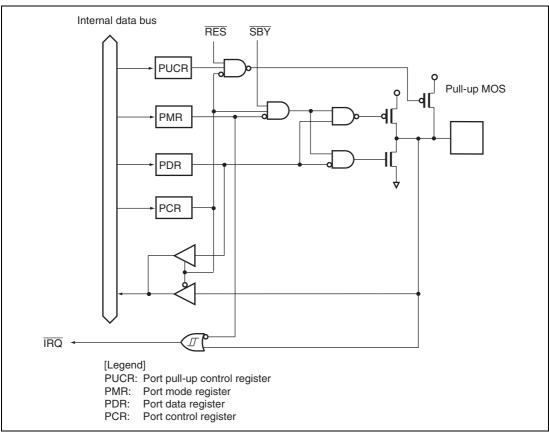

# Appendix B I/O Port Block Diagrams

## **B.1** I/O Port Block Diagrams

$\overline{\text{RES}}$  goes low in a reset, and  $\overline{\text{SBY}}$  goes low in a reset and in standby mode.

Figure B.1 Port 1 Block Diagram (P17)

Figure B.2 Port 1 Block Diagram (P16 to P14)

|   | Classification |                            | Product Code                 | Model Marking     | Package Code     |  |

|---|----------------|----------------------------|------------------------------|-------------------|------------------|--|

|   | Mask ROM       | Standard                   | HD6433692H                   | HD6433692(***)H   | QFP-64 (FP-64A)  |  |

|   | version        | product                    | HD6433692FP HD6433692(***)FP |                   | LQFP-64 (FP-64E) |  |

|   |                |                            | HD6433692FX                  | HD6433692(***)FX  | LQFP-48 (FP-48F) |  |

|   |                |                            | HD6433692FY                  | HD6433692(***)FY  | LQFP-48 (FP-48B) |  |

|   |                |                            | HD6433692FT                  | HD6433692(***)FT  | QFN-48(TNP-48)   |  |

|   |                | Product with<br>POR & LVDC | HD6433692GH                  | HD6433692G(***)H  | QFP-64 (FP-64A)  |  |

|   |                |                            | HD6433692GFP                 | HD6433692G(***)FP | LQFP-64 (FP-64E) |  |

|   |                |                            | HD6433692GFX                 | HD6433692G(***)FX | LQFP-48 (FP-48F) |  |

|   |                |                            | HD6433692GFY                 | HD6433692G(***)FY | LQFP-48 (FP-48B) |  |

|   |                |                            | HD6433692GFT                 | HD6433692G(***)FT | QFN-48(TNP-48)   |  |

|   |                |                            | HD6433691H                   | HD6433691(***)H   | QFP-64 (FP-64A)  |  |

|   | version        | product                    | HD6433691FP                  | HD6433691(***)FP  | LQFP-64 (FP-64E) |  |

|   |                |                            | HD6433691FX                  | HD6433691(***)FX  | LQFP-48 (FP-48F) |  |

|   |                |                            | HD6433691FY                  | HD6433691(***)FY  | LQFP-48 (FP-48B) |  |

|   |                |                            | HD6433691FT                  | HD6433691(***)FT  | QFN-48(TNP-48)   |  |

|   |                | Product with<br>POR & LVDC | HD6433691GH                  | HD6433691G(***)H  | QFP-64 (FP-64A)  |  |

|   |                |                            | HD6433691GFP                 | HD6433691G(***)FP | LQFP-64 (FP-64E) |  |

|   |                |                            | HD6433691GFX                 | HD6433691G(***)FX | LQFP-48 (FP-48F) |  |

|   |                |                            | HD6433691GFY                 | HD6433691G(***)FY | LQFP-48 (FP-48B) |  |

| _ |                |                            | HD6433691GFT                 | HD6433691G(***)FT | QFN-48(TNP-48)   |  |

|   | Mask ROM       | Standard                   | HD6433690H                   | HD6433690(***)H   | QFP-64 (FP-64A)  |  |

|   | version        | product                    | HD6433690FP                  | HD6433690(***)FP  | LQFP-64 (FP-64E) |  |

|   |                |                            | HD6433690FX                  | HD6433690(***)FX  | LQFP-48 (FP-48F) |  |

|   |                |                            | HD6433690FY                  | HD6433690(***)FY  | LQFP-48 (FP-48B) |  |

|   |                |                            | HD6433690FT                  | HD6433690(***)FT  | QFN-48(TNP-48)   |  |

|   |                | Product with<br>POR & LVDC | HD6433690GH                  | HD6433690G(***)H  | QFP-64 (FP-64A)  |  |

|   |                |                            | HD6433690GFP                 | HD6433690G(***)FP | LQFP-64 (FP-64E) |  |

|   |                |                            | HD6433690GFX                 | HD6433690G(***)FX | LQFP-48 (FP-48F) |  |

|   |                |                            | HD6433690GFY                 | HD6433690G(***)FY | LQFP-48 (FP-48B) |  |

|   |                |                            | HD6433690GFT                 | HD6433690G(***)FT | QFN-48(TNP-48)   |  |