# E·XFL

### Renesas - HD64F3694GFXV Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | H8/300H                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SCI, UART/USART                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                             |

| Number of I/O              | 29                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b SAR                                                                  |

| Oscillator Type            | External, Internal                                                             |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-LQFP                                                                        |

| Supplier Device Package    | 48-LQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3694gfxv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 3.2.5   | Wakeup Interrupt Flag Register (IWPR)      | . 55 |

|-------|---------|--------------------------------------------|------|

| 3.3   | Reset 1 | Exception Handling                         | . 56 |

| 3.4   | Interru | pt Exception Handling                      | . 57 |

|       | 3.4.1   | External Interrupts                        | . 57 |

|       | 3.4.2   | Internal Interrupts                        | . 58 |

|       | 3.4.3   | Interrupt Handling Sequence                | . 58 |

|       | 3.4.4   | Interrupt Response Time                    | . 60 |

| 3.5   | Usage   | Notes                                      | . 62 |

|       | 3.5.1   | Interrupts after Reset                     | . 62 |

|       | 3.5.2   | Notes on Stack Area Use                    | . 62 |

|       | 3.5.3   | Notes on Rewriting Port Mode Registers     | . 62 |

| Secti | ion 4   | Address Break                              | 63   |

| 4.1   | Regist  | er Descriptions                            | . 63 |

|       | 4.1.1   | Address Break Control Register (ABRKCR)    | . 64 |

|       | 4.1.2   | Address Break Status Register (ABRKSR)     | . 65 |

|       | 4.1.3   | Break Address Registers (BARH, BARL)       | . 66 |

|       | 4.1.4   | Break Data Registers (BDRH, BDRL)          | . 66 |

| 4.2   | Operat  | ion                                        | . 66 |

|       |         |                                            |      |

| Secti |         | Clock Pulse Generators                     |      |

| 5.1   | System  | n Clock Generator                          |      |

|       | 5.1.1   | Connecting Crystal Resonator               | . 70 |

|       | 5.1.2   | Connecting Ceramic Resonator               | . 71 |

|       | 5.1.3   | External Clock Input Method                | . 71 |

| 5.2   | Subclo  | ck Generator                               |      |

|       | 5.2.1   | Connecting 32.768-kHz Crystal Resonator    | . 72 |

|       | 5.2.2   | Pin Connection when Not Using Subclock     |      |

| 5.3   | Presca  | lers                                       | . 73 |

|       | 5.3.1   | Prescaler S                                | . 73 |

|       | 5.3.2   | Prescaler W                                | . 73 |

| 5.4   | Usage   | Notes                                      | . 74 |

|       | 5.4.1   | Note on Resonators                         | . 74 |

|       | 5.4.2   | Notes on Board Design                      | . 74 |

| Secti | ion 6   | Power-Down Modes                           | 75   |

| 6.1   | Regist  | er Descriptions                            |      |

|       | 6.1.1   | System Control Register 1 (SYSCR1)         |      |

|       | 6.1.2   | System Control Register 2 (SYSCR2)         | . 78 |

|       | 6.1.3   | Module Standby Control Register 1 (MSTCR1) | . 79 |

# RENESAS

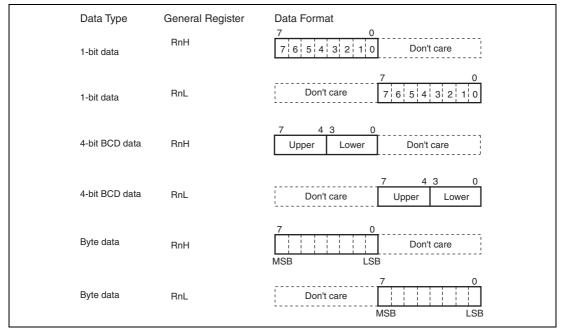

# 2.3 Data Formats

The H8/300H CPU can process 1-bit, 4-bit (BCD), 8-bit (byte), 16-bit (word), and 32-bit (longword) data. Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data. The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

#### 2.3.1 General Register Data Formats

Figure 2.5 shows the data formats in general registers.

Figure 2.5 General Register Data Formats (1)

| Instruction | Size*         | Function                                                                                                                                                                                                                                                                                   |

|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BXOR        | В             | $C \oplus ( of ) \rightarrow C$<br>XORs the carry flag with a specified bit in a general register or memory<br>operand and stores the result in the carry flag.                                                                                                                            |

| BIXOR       | В             | $C \oplus \neg$ ( <bit-no.> of <ead>) <math>\rightarrow C</math><br/>XORs the carry flag with the inverse of a specified bit in a general<br/>register or memory operand and stores the result in the carry flag.<br/>The bit number is specified by 3-bit immediate data.</ead></bit-no.> |

| BLD         | В             | ( <bit-no.> of <ead>) <math>\rightarrow</math> C Transfers a specified bit in a general register or memory operand to the carry flag.</ead></bit-no.>                                                                                                                                      |

| BILD        | В             | ¬ ( <bit-no.> of <ead>) → C<br/>Transfers the inverse of a specified bit in a general register or memory<br/>operand to the carry flag.<br/>The bit number is specified by 3-bit immediate data.</ead></bit-no.>                                                                           |

| BST         | В             | $C \rightarrow$ ( <bit-no.> of <ead>)<br/>Transfers the carry flag value to a specified bit in a general register or<br/>memory operand.</ead></bit-no.>                                                                                                                                   |

| BIST        | В             | $\neg$ C $\rightarrow$ ( <bit-no.> of <ead>)<br/>Transfers the inverse of the carry flag value to a specified bit in a<br/>general register or memory operand.<br/>The bit number is specified by 3-bit immediate data.</ead></bit-no.>                                                    |

| Note: *     | Refers to the | operand size.                                                                                                                                                                                                                                                                              |

#### Table 2.6 **Bit Manipulation Instructions (2)**

Refers to the operand size. Note:

B: Byte

# 3.4 Interrupt Exception Handling

# 3.4.1 External Interrupts

As the external interrupts, there are NMI, IRQ3 to IRQ0, and WKP5 to WKP0 interrupts.

# **NMI Interrupt**

NMI interrupt is requested by input signal edge to pin  $\overline{\text{NMI}}$ . This interrupt is detected by either rising edge sensing or falling edge sensing, depending on the setting of bit NMIEG in IEGR1. NMI is the highest-priority interrupt, and can always be accepted without depending on the I bit value in CCR.

# IRQ3 to IRQ0 Interrupts

IRQ3 to IRQ0 interrupts are requested by input signals to pins  $\overline{IRQ3}$  to  $\overline{IRQ0}$ . These four interrupts are given different vector addresses, and are detected individually by either rising edge sensing or falling edge sensing, depending on the settings of bits IEG3 to IEG0 in IEGR1. When pins  $\overline{IRQ3}$  to  $\overline{IRQ0}$  are designated for interrupt input in PMR1 and the designated signal edge is input, the corresponding bit in IRR1 is set to 1, requesting the CPU of an interrupt. These interrupts can be masked by setting bits IEN3 to IEN0 in IENR1.

# WKP5 to WKP0 Interrupts

WKP5 to WKP0 interrupts are requested by input signals to pins  $\overline{\text{WKP5}}$  to  $\overline{\text{WKP0}}$ . These six interrupts have the same vector addresses, and are detected individually by either rising edge sensing or falling edge sensing, depending on the settings of bits WPEG5 to WPEG0 in IEGR2.

When pins  $\overline{WKP5}$  to  $\overline{WKP0}$  are designated for interrupt input in PMR5 and the designated signal edge is input, the corresponding bit in IWPR is set to 1, requesting the CPU of an interrupt. These interrupts can be masked by setting bit IENWP in IENR1.

When an address break is set in the data read cycle or data write cycle, the data bus used will depend on the combination of the byte/word access and address. Table 4.1 shows the access and data bus used. When an I/O register space with an 8-bit data bus width is accessed in word size, a byte access is generated twice. For details on data widths of each register, see section 20.1, Register Addresses (Address Order).

#### Table 4.1Access and Data Bus Used

|                                         | Word A       | ccess          | Byte Access  |              |  |

|-----------------------------------------|--------------|----------------|--------------|--------------|--|

|                                         | Even Address | Odd<br>Address | Even Address | Odd Address  |  |

| ROM space                               | Upper 8 bits | Lower 8 bits   | Upper 8 bits | Upper 8 bits |  |

| RAM space                               | Upper 8 bits | Lower 8 bits   | Upper 8 bits | Upper 8 bits |  |

| I/O register with 8-bit data bus width  | Upper 8 bits | Upper 8 bits   | Upper 8 bits | Upper 8 bits |  |

| I/O register with 16-bit data bus width | Upper 8 bits | Lower 8 bits   | _            |              |  |

#### 4.1.2 Address Break Status Register (ABRKSR)

ABRKSR consists of the address break interrupt flag and the address break interrupt enable bit.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                        |  |

|--------|----------|------------------|-----|--------------------------------------------------------------------|--|

| ы      | Dit Name | value            |     | Description                                                        |  |

| 7      | ABIF     | 0                | R/W | Address Break Interrupt Flag                                       |  |

|        |          |                  |     | [Setting condition]                                                |  |

|        |          |                  |     | When the condition set in ABRKCR is satisfied                      |  |

|        |          |                  |     | [Clearing condition]                                               |  |

|        |          |                  |     | When 0 is written after ABIF=1 is read                             |  |

| 6      | ABIE     | 0                | R/W | Address Break Interrupt Enable                                     |  |

|        |          |                  |     | When this bit is 1, an address break interrupt request is enabled. |  |

| 5 to 0 | _        | All 1            | _   | Reserved                                                           |  |

|        |          |                  |     | These bits are always read as 1.                                   |  |

# Section 6 Power-Down Modes

This LSI has six modes of operation after a reset. These include a normal active mode and four power-down modes, in which power consumption is significantly reduced. Module standby mode reduces power consumption by selectively halting on-chip module functions.

Active mode

The CPU and all on-chip peripheral modules are operable on the system clock. The system clock frequency can be selected from  $\phi$ osc,  $\phi$ osc/8,  $\phi$ osc/16,  $\phi$ osc/32, and  $\phi$ osc/64.

Subactive mode

The CPU and all on-chip peripheral modules are operable on the subclock. The subclock frequency can be selected from  $\frac{\phi w}{2}$ ,  $\frac{\phi w}{4}$ , and  $\frac{\phi w}{8}$ .

• Sleep mode

The CPU halts. On-chip peripheral modules are operable on the system clock.

• Subsleep mode

The CPU halts. On-chip peripheral modules are operable on the subclock.

• Standby mode

The CPU and all on-chip peripheral modules halt. When the clock time-base function is selected, timer A is operable.

Module standby mode

Independent of the above modes, power consumption can be reduced by halting on-chip peripheral modules that are not used in module units.

# 6.1 Register Descriptions

The registers related to power-down modes are listed below.

- System control register 1 (SYSCR1)

- System control register 2 (SYSCR2)

- Module standby control register 1 (MSTCR1)

#### 9.2.1 Port Control Register 2 (PCR2)

Initial Bit **Bit Name** Value R/W Description 7 to 3 Reserved \_\_\_\_ 2 PCR22 W When each of the port 2 pins P22 to P20 functions as an 0 general I/O port, setting a PCR2 bit to 1 makes the 1 PCR21 0 W corresponding pin an output port, while clearing the bit to 0 PCR20 0 W 0 makes the pin an input port.

PCR2 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 2.

#### 9.2.2 Port Data Register 2 (PDR2)

PDR2 is a general I/O port data register of port 2.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                 |  |

|--------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7 to 3 | —        | All 1            | —   | Reserved                                                                                                                                    |  |

|        |          |                  |     | These bits are always read as 1.                                                                                                            |  |

| 2      | P22      | 0                | R/W | PDR2 stores output data for port 2 pins.                                                                                                    |  |

| 1      | P21      | 0                | R/W | If PDR2 is read while PCR2 bits are set to 1, the value                                                                                     |  |

| 0      | P20      | 0                | R/W | stored in PDR2 is read. If PDR2 is read while PCR2 bi<br>are cleared to 0, the pin states are read regardless of t<br>value stored in PDR2. |  |

# **11.3** Register Descriptions

Time V has the following registers.

- Timer counter V (TCNTV)

- Timer constant register A (TCORA)

- Timer constant register B (TCORB)

- Timer control register V0 (TCRV0)

- Timer control/status register V (TCSRV)

- Timer control register V1 (TCRV1)

## 11.3.1 Timer Counter V (TCNTV)

TCNTV is an 8-bit up-counter. The clock source is selected by bits CKS2 to CKS0 in timer control register V0 (TCRV0). The TCNTV value can be read and written by the CPU at any time. TCNTV can be cleared by an external reset input signal, or by compare match A or B. The clearing signal is selected by bits CCLR1 and CCLR0 in TCRV0.

When TCNTV overflows, OVF is set to 1 in timer control/status register V (TCSRV).

TCNTV is initialized to H'00.

## 11.3.2 Time Constant Registers A and B (TCORA, TCORB)

TCORA and TCORB have the same function.

TCORA and TCORB are 8-bit read/write registers.

TCORA and TCNTV are compared at all times. When the TCORA and TCNTV contents match, CMFA is set to 1 in TCSRV. If CMIEA is also set to 1 in TCRV0, a CPU interrupt is requested. Note that they must not be compared during the T3 state of a TCORA write cycle.

Timer output from the TMOV pin can be controlled by the identifying signal (compare match A) and the settings of bits OS3 to OS0 in TCSRV.

TCORA and TCORB are initialized to H'FF.

## 12.3.2 Timer Control Register W (TCRW)

TCRW selects the timer counter clock source, selects a clearing condition, and specifies the timer output levels.

| 7       CCLR       0       R/W       Counter Clear         The TCNT value is cleared by compare match A when this bit is 1. When it is 0, TCNT operates as a free-running counter.       6         6       CKS2       0       R/W       Clock Select 2 to 0         5       CKS1       0       R/W       Select the TCNT clock source.         4       CKS0       0       R/W       Select the TCNT clock source.         4       CKS0       0       R/W       000: Internal clock: counts on $\phi/2$ 010: Internal clock: counts on $\phi/4$ 011: Internal clock: counts on $\phi/4$ 011: Internal clock: counts on $\phi/8$ 1XX: Counts on rising edges of the external event (FTCI)       When the internal clock source ( $\phi$ ) is selected, subclock sources are counted in subactive and subsleep modes.         3       TOD       0       R/W       Timer Output Level Setting D         Sets the output value of the FTIOD pin until the first compare match D is generated.       0: Output value is 0*         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 0*       1: Output value is 0*       1: Output value is 0*         1       TOB       R/W       Timer Output Level Setting B         Sets the output value is 0*       1: Output value is 0*       1: Output value is 0* <th>Bit</th> <th>Bit Name</th> <th>Initial<br/>Value</th> <th>R/W</th> <th>Description</th>                                                                                                                                                                | Bit | Bit Name | Initial<br>Value | R/W | Description                                              |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------------------|-----|----------------------------------------------------------|--|

| <ul> <li>this bit is 1. When it is 0, TCNT operates as a free-<br/>running counter.</li> <li>CKS2 0 R/W Clock Select 2 to 0</li> <li>CKS1 0 R/W Select the TCNT clock source.</li> <li>CKS0 0 R/W 000: Internal clock: counts on φ</li> <li>001: Internal clock: counts on φ/2</li> <li>010: Internal clock: counts on φ/4</li> <li>011: Internal clock: counts on φ/8</li> <li>1 TOB 0 R/W Timer Output Level Setting B</li> <li>Sets the output value is 1*</li> <li>TOB 0 R/W Timer Output Level Setting B</li> <li>Sets the output value is 0*</li> <li>1 TOB 0 R/W Timer Output Level Setting B</li> <li>Sets the output value is 1*</li> <li>COULPUT value is 0*</li> <li>OUTPUT value is 0*</li> </ul> | 7   | CCLR     | 0                | R/W | Counter Clear                                            |  |

| 5       CKS1       0       R/W       Select the TCNT clock source.         4       CKS0       0       R/W       000: Internal clock: counts on \$\u00e9         4       CKS0       0       R/W       000: Internal clock: counts on \$\u00e9         011: Internal clock: counts on \$\u00e9/2       010: Internal clock: counts on \$\u00e9/2       010: Internal clock: counts on \$\u00e9/2         1       TOD       0       R/W       Timer Output Level Setting D         Sets the output value is 0*       1: Output value is 0*       1: Output value is 1*         2       TOC       0       R/W       Timer Output Level Setting C         Sets the output value is 0*       1: Output value is 0*       1: Output value is 0*         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 0*       1: Output value is 0*       1: Output value is 0*         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 0*       1: Output value is 0*       1: Output value is 0*         1       TOB       R/W       Timer Output Level Setting B         Sets the output value of the FTIOB pin until the first compare match B is generated.       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                      |     |          |                  |     | this bit is 1. When it is 0, TCNT operates as a free-    |  |

| 4       CKS0       0       R/W       000: Internal clock: counts on \$         001: Internal clock: counts on \$       001: Internal clock: counts on \$       011: Internal clock: counts on \$         011: Internal clock: counts on \$       011: Internal clock: counts on \$       011: Internal clock: counts on \$         1       TOB       0       R/W       Timer Output Level Setting B         2       TOB       0       R/W       Timer Output Level Setting C         2       TOC       0       R/W       Timer Output Level Setting C         2       TOC       0       R/W       Timer Output Level Setting C         3       TOD       R/W       Timer Output Level Setting C         3       TOC       0       R/W       Timer Output Level Setting C         3       Sets the output value is 1*       1       OUTC       0         2       TOC       0       R/W       Timer Output Level Setting C         3       Sets the output value of the FTIOC pin until the first compare match C is generated.       0: Output value is 0*         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 1*       1       TOB       R/W       Timer Output Level Setting B         Sets the output val                                                                                                                                                                                                                                                                                                                                                 | 6   | CKS2     | 0                | R/W | Clock Select 2 to 0                                      |  |

| 001: Internal clock: counts on \$\u03c6/2         001: Internal clock: counts on \$\u03c6/2         010: Internal clock: counts on \$\u03c6/2         011: Internal clock: counts on \$\u03c6/2         01: Internal clock: counts on \$\u03c6/2         01: Internal clock: counts on \$\u03c6/2         02: Output value is 0*         1       TOB         0       R/W                                                                                                                                                                                                                                                    | 5   | CKS1     | 0                | R/W | Select the TCNT clock source.                            |  |

| 010: Internal clock: counts on \$\u03c6/4         011: Internal clock: counts on \$\u03c6/8         1XX: Counts on rising edges of the external event (FTCI)         When the internal clock source (\$\u03c6) is selected, subclock sources are counted in subactive and subsleep modes.         3       TOD       0       R/W       Timer Output Level Setting D         Sets the output value of the FTIOD pin until the first compare match D is generated.       0: Output value is 0*       1: Output value is 1*         2       TOC       0       R/W       Timer Output Level Setting C         Sets the output value of the FTIOC pin until the first compare match C is generated.       0: Output value is 0*         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 1*       1       TOB       0       R/W         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 1*       1       COB       Timer Output Level Setting B         Sets the output value is 0*       1: Output value is 1*       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4   | CKS0     | 0                | R/W | 000: Internal clock: counts on $\phi$                    |  |

| 011: Internal clock: counts on \$\u03c6/8         1XX: Counts on rising edges of the external event (FTCI)         When the internal clock source (\$\u03c6) is selected, subclock sources are counted in subactive and subsleep modes.         3       TOD       0       R/W       Timer Output Level Setting D         Sets the output value of the FTIOD pin until the first compare match D is generated.       0: Output value is 0*       1: Output value is 1*         2       TOC       0       R/W       Timer Output Level Setting C         Sets the output value of the FTIOC pin until the first compare match C is generated.       0: Output value is 0*         1       TOB       0       R/W         1       TOB       0       R/W         1       TOB       0       R/W         2       O       R/W       Timer Output Level Setting C         Sets the output value is 1*       0       Output value is 0*         1: Output value is 0*       1: Output value is 1*       0         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value of the FTIOB pin until the first compare match B is generated.       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                 |     |          |                  |     | 001: Internal clock: counts on $\phi/2$                  |  |

| 1XX: Counts on rising edges of the external event (FTCI)         When the internal clock source (\$\phi\$) is selected, subclock sources are counted in subactive and subsleep modes.         3       TOD       0       R/W       Timer Output Level Setting D         Sets the output value of the FTIOD pin until the first compare match D is generated.       0: Output value is 0*       1: Output value is 1*         2       TOC       0       R/W       Timer Output Level Setting C         Sets the output value of the FTIOC pin until the first compare match C is generated.       0: Output value is 0*         1       TOB       0       R/W         1       TOB       0       R/W         1       TOB       0       R/W         1       OB       R/W       Timer Output Level Setting B         Sets the output value is 0*       1: Output value is 1*         1       TOB       0       R/W         1       OB       R/W       Timer Output Level Setting B         Sets the output value is 1*       Sets the output value of the FTIOB pin until the first compare match B is generated.         0: Output value is 0*       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |          |                  |     | 010: Internal clock: counts on $\phi/4$                  |  |

| When the internal clock source (\$) is selected, subclock sources are counted in subactive and subsleep modes.         3       TOD       0       R/W       Timer Output Level Setting D         Sets the output value of the FTIOD pin until the first compare match D is generated.       0: Output value is 0*       1: Output value is 1*         2       TOC       0       R/W       Timer Output Level Setting C         Sets the output value is 1*       2       TOC       0       R/W         1       TOB       0       R/W       Timer Output Level Setting C         Sets the output value is 1*       0: Output value is 0*       1: Output value is 0*         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 1*       1       TOB       0       R/W         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 1*       1       TOB       0       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |          |                  |     | 011: Internal clock: counts on                           |  |

| 3       TOD       0       R/W       Timer Output Level Setting D         3       TOD       0       R/W       Timer Output Level Setting D         Sets the output value of the FTIOD pin until the first compare match D is generated.       0: Output value is 0*         1:       Output value is 1*         2       TOC       0       R/W         Timer Output Level Setting C       Sets the output value of the FTIOC pin until the first compare match C is generated.         0:       Output value is 0*         1:       Output value is 0*         1:       Output value is 1*         1       TOB       0       R/W         1       TOB       0       R/W         1       TOB       0       R/W         2       OUtput value is 1*       Sets the output value of the FTIOC pin until the first compare match C is generated.         0:       Output value is 1*       1         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value of the FTIOB pin until the first compare match B is generated.       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |          |                  |     | 1XX: Counts on rising edges of the external event (FTCI) |  |

| Sets the output value of the FTIOD pin until the first compare match D is generated.       0: Output value is 0*         1: Output value is 1*       1: Output value is 1*         2       TOC       0       R/W         Timer Output Level Setting C       Sets the output value of the FTIOC pin until the first compare match C is generated.         0: Output value is 0*       1: Output value is 0*         1       TOB       0         R/W       Timer Output Level Setting B         Sets the output value is 1*       Sets the output value is 1*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |          |                  |     |                                                          |  |

| compare match D is generated.         0: Output value is 0*         1: Output value is 1*         2       TOC       0       R/W       Timer Output Level Setting C         Sets the output value of the FTIOC pin until the first compare match C is generated.       0: Output value is 0*         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value is 1*       1       TOB       0       R/W         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value of the FTIOB pin until the first compare match B is generated.       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3   | TOD      | 0                | R/W | Timer Output Level Setting D                             |  |

| 1: Output value is 1*         2       TOC       0       R/W       Timer Output Level Setting C         Sets the output value of the FTIOC pin until the first compare match C is generated.       0: Output value is 0*         1: Output value is 0*       1: Output value is 1*         1       TOB       0       R/W         Timer Output Level Setting B       Sets the output value of the FTIOB pin until the first compare match B is generated.         0: Output value is 0*       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |          |                  |     | •                                                        |  |

| 2       TOC       0       R/W       Timer Output Level Setting C         Sets the output value of the FTIOC pin until the first compare match C is generated.       0: Output value is 0*         1: Output value is 1*       1: Output value is 1*         1       TOB       0       R/W         Sets the output value of the FTIOB pin until the first compare match B is generated.       0: Output value is 0*         0: Output value is 0*       0: Output value of the FTIOB pin until the first compare match B is generated.         0: Output value is 0*       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |          |                  |     | 0: Output value is 0*                                    |  |

| Sets the output value of the FTIOC pin until the first compare match C is generated.       0: Output value is 0*         1: Output value is 1*       1: Output value is 1*         1       TOB       0       R/W         Sets the output Level Setting B       Sets the output value of the FTIOB pin until the first compare match B is generated.         0: Output value is 0*       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |          |                  |     | 1: Output value is 1*                                    |  |

| compare match C is generated.         0: Output value is 0*         1: Output value is 1*         1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value of the FTIOB pin until the first compare match B is generated.       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2   | TOC      | 0                | R/W | Timer Output Level Setting C                             |  |

| 1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value of the FTIOB pin until the first compare match B is generated.       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |          |                  |     |                                                          |  |

| 1       TOB       0       R/W       Timer Output Level Setting B         Sets the output value of the FTIOB pin until the first compare match B is generated.       0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |          |                  |     | 0: Output value is 0*                                    |  |

| Sets the output value of the FTIOB pin until the first<br>compare match B is generated.<br>0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |          |                  |     | 1: Output value is 1*                                    |  |

| compare match B is generated.<br>0: Output value is 0*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1   | ТОВ      | 0                | R/W | Timer Output Level Setting B                             |  |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |          |                  |     |                                                          |  |

| 1: Output value is 1*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |          |                  |     | 0: Output value is 0*                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |          |                  |     | 1: Output value is 1*                                    |  |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                          |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------|

| 0   | TOA      | 0                | R/W | Timer Output Level Setting A                                                         |

|     |          |                  |     | Sets the output value of the FTIOA pin until the first compare match A is generated. |

|     |          |                  |     | 0: Output value is 0*                                                                |

|     |          |                  |     | 1: Output value is 1*                                                                |

Legend: X: Don't care.

Note: \* The change of the setting is immediately reflected in the output value.

#### 12.3.3 Timer Interrupt Enable Register W (TIERW)

TIERW controls the timer W interrupt request.

|        |          | Initial |     |                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit    | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 7      | OVIE     | 0       | R/W | Timer Overflow Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                |  |

|        |          |         |     | When this bit is set to 1, FOVI interrupt requested by OVF flag in TSRW is enabled.                                                                                                                                                                                                                                                                                                            |  |

| 6 to 4 | _        | All 1   | _   | Reserved                                                                                                                                                                                                                                                                                                                                                                                       |  |

|        |          |         |     | These bits are always read as 1.                                                                                                                                                                                                                                                                                                                                                               |  |

| 3      | IMIED    | 0       | R/W | Input Capture/Compare Match Interrupt Enable D                                                                                                                                                                                                                                                                                                                                                 |  |

|        |          |         |     | When this bit is set to 1, IMID interrupt requested by IMFD flag in TSRW is enabled.                                                                                                                                                                                                                                                                                                           |  |

| 2      | IMIEC    | 0       | R/W | Input Capture/Compare Match Interrupt Enable C                                                                                                                                                                                                                                                                                                                                                 |  |

|        |          |         |     | When this bit is set to 1, IMIC interrupt requested by IMFC flag in TSRW is enabled.                                                                                                                                                                                                                                                                                                           |  |

| 1      | IMIEB    | 0       | R/W | Input Capture/Compare Match Interrupt Enable B                                                                                                                                                                                                                                                                                                                                                 |  |

|        |          |         |     | When this bit is set to 1, IMIB interrupt requested by IMFB flag in TSRW is enabled.                                                                                                                                                                                                                                                                                                           |  |

| 0      | IMIEA    | 0       | R/W | Input Capture/Compare Match Interrupt Enable A                                                                                                                                                                                                                                                                                                                                                 |  |

|        |          |         |     | When this bit is set to 1, IMIA interrupt requested by IMFA flag in TSRW is enabled.                                                                                                                                                                                                                                                                                                           |  |

| ·      |          | •       |     | <ul> <li>When this bit is set to 1, IMIC interrupt requested by<br/>IMFC flag in TSRW is enabled.</li> <li>Input Capture/Compare Match Interrupt Enable B</li> <li>When this bit is set to 1, IMIB interrupt requested by<br/>IMFB flag in TSRW is enabled.</li> <li>Input Capture/Compare Match Interrupt Enable A</li> <li>When this bit is set to 1, IMIA interrupt requested by</li> </ul> |  |

## 12.3.4 Timer Status Register W (TSRW)

TSRW shows the status of interrupt requests.

|        |          | Initial |     | - · · ·                                                              |  |

|--------|----------|---------|-----|----------------------------------------------------------------------|--|

| Bit    | Bit Name | Value   | R/W | Description                                                          |  |

| 7      | OVF      | 0       | R/W | Timer Overflow Flag                                                  |  |

|        |          |         |     | [Setting condition]                                                  |  |

|        |          |         |     | When TCNT overflows from H'FFFF to H'0000                            |  |

|        |          |         |     | [Clearing condition]                                                 |  |

|        |          |         |     | Read OVF when OVF = 1, then write 0 in OVF                           |  |

| 6 to 4 |          | All 1   |     | Reserved                                                             |  |

|        |          |         |     | These bits are always read as 1.                                     |  |

| 3      | IMFD     | 0       | R/W | Input Capture/Compare Match Flag D                                   |  |

|        |          |         |     | [Setting conditions]                                                 |  |

|        |          |         |     | <ul> <li>TCNT = GRD when GRD functions as an output</li> </ul>       |  |

|        |          |         |     | compare register                                                     |  |

|        |          |         |     | <ul> <li>The TCNT value is transferred to GRD by an input</li> </ul> |  |

|        |          |         |     | capture signal when GRD functions as an input                        |  |

|        |          |         |     | capture register                                                     |  |

|        |          |         |     | [Clearing condition]                                                 |  |

|        |          |         |     | Read IMFD when IMFD = 1, then write 0 in IMFD                        |  |

| 2      | IMFC     | 0       | R/W | Input Capture/Compare Match Flag C                                   |  |

|        |          |         |     | [Setting conditions]                                                 |  |

|        |          |         |     | <ul> <li>TCNT = GRC when GRC functions as an output</li> </ul>       |  |

|        |          |         |     | compare register                                                     |  |

|        |          |         |     | <ul> <li>The TCNT value is transferred to GRC by an input</li> </ul> |  |

|        |          |         |     | capture signal when GRC functions as an input                        |  |

|        |          |         |     | capture register                                                     |  |

|        |          |         |     | [Clearing condition]                                                 |  |

|        |          |         |     | Read IMFC when IMFC = 1, then write 0 in IMFC                        |  |

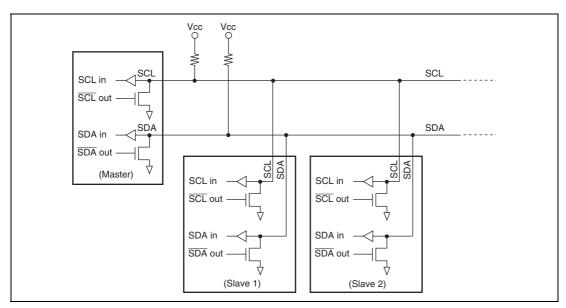

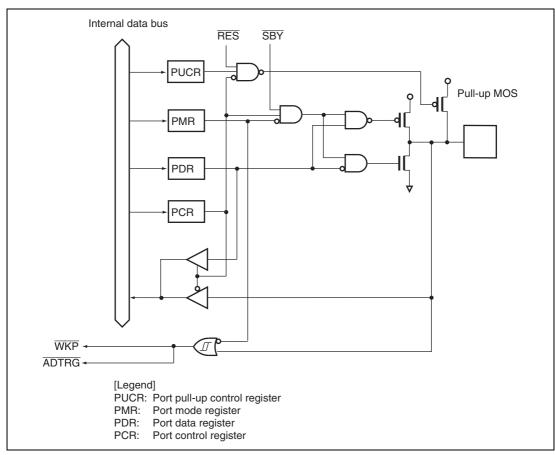

Figure 15.2 External Circuit Connections of I/O Pins

# 15.2 Input/Output Pins

Table 15.1 summarizes the input/output pins used by the I<sup>2</sup>C bus interface 2.

#### Table 15.1 I<sup>2</sup>C Bus Interface Pins

| Name         | Abbreviation | I/O | Function                      |

|--------------|--------------|-----|-------------------------------|

| Serial clock | SCL          | I/O | IIC serial clock input/output |

| Serial data  | SDA          | I/O | IIC serial data input/output  |

# **15.3 Register Descriptions**

The I<sup>2</sup>C bus interface 2 has the following registers:

- I<sup>2</sup>C bus control register 1 (ICCR1)

- I<sup>2</sup>C bus control register 2 (ICCR2)

- I<sup>2</sup>C bus mode register (ICMR)

- I<sup>2</sup>C bus interrupt enable register (ICIER)

- I<sup>2</sup>C bus status register (ICSR)

- I<sup>2</sup>C bus slave address register (SAR)

# 15.5 Interrupt Request

There are six interrupt requests in this module; transmit data empty, transmit end, receive data full, NACK receive, STOP recognition, and arbitration lost/overrun. Table 15.3 shows the contents of each interrupt request.

#### Table 15.3 Interrupt Requests

| Interrupt Request           | Abbreviation | Interrupt Condition            | I <sup>2</sup> C Mode | Clocked<br>Synchronous<br>Mode |

|-----------------------------|--------------|--------------------------------|-----------------------|--------------------------------|

| Transmit Data Empty         | ТХІ          | (TDRE = 1) • (TIE = 1)         | 0                     | 0                              |

| Transmit End                | TEI          | (TEND = 1) • (TEIE = 1)        | 0                     | 0                              |

| Receive Data Full           | RXI          | (RDRF = 1) • (RIE = 1)         | 0                     | 0                              |

| STOP Recognition            | STPI         | $(STOP = 1) \cdot (STIE = 1)$  | 0                     | ×                              |

| NACK Receive                | NAKI         | $\{(NACKF = 1) + (AL = 1)\}$ . | 0                     | ×                              |

| Arbitration<br>Lost/Overrun | _            | (NAKIE = 1)                    | 0                     | 0                              |

When interrupt conditions described in table 15.3 are 1 and the I bit in CCR is 0, the CPU executes an interrupt exception processing. Interrupt sources should be cleared in the exception processing. TDRE and TEND are automatically cleared to 0 by writing the transmit data to ICDRT. RDRF are automatically cleared to 0 by reading ICDRR. TDRE is set to 1 again at the same time when transmit data is written to ICDRT. When TDRE is cleared to 0, then an excessive data of one byte may be transmitted.

# 15.7 Usage Notes

#### 15.7.1 Issue (Retransmission) of Start/Stop Conditions

In master mode, when the start/stop conditions are issued (retransmitted) at the specific timing under the following condition 1 or 2, such conditions may not be output successfully. To avoid this, issue (retransmit) the start/stop conditions after the fall of the ninth clock is confirmed. Check the SCLO bit in the I<sup>2</sup>C control register 2 (IICR2) to confirm the fall of the ninth clock.

- 1. When the rising of SCL falls behind the time specified in section 17.6, Bit Synchronous Circuit, by the load of the SCL bus (load capacitance or pull-up resistance)

- 2. When the bit synchronous circuit is activated by extending the low period of eighth and ninth clocks, that is driven by the slave device

## 15.7.2 WAIT Setting in I<sup>2</sup>C Bus Mode Register (ICMR)

If the WAIT bit is set to 1, and the SCL signal is driven low for two or more transfer clocks by the slave device at the eighth and ninth clocks, the high period of ninth clock may be shortened. To avoid this, set the WAIT bit in ICMR to 0.

#### Table 21.2DC Characteristics (3)

$V_{\rm cc}$  = 3.0 to 5.5 V,  $V_{\rm ss}$  = 0.0 V,  $T_{\rm a}$  = –20 to +75°C, unless otherwise indicated.

|                                        |                    | Applicable                                    |                             |     | Value | s    |      |

|----------------------------------------|--------------------|-----------------------------------------------|-----------------------------|-----|-------|------|------|

| Item                                   | Symbol             | Pins                                          | Test Condition              | Min | Тур   | Max  | Unit |

| Allowable output low current (per pin) | I <sub>ol</sub>    | Output pins<br>except port 8,<br>SCL, and SDA | $V_{\rm cc}$ = 4.0 to 5.5 V | _   | _     | 2.0  | mA   |

|                                        |                    | Port 8                                        | _                           | _   | _     | 20.0 |      |

|                                        |                    | Port 8                                        |                             |     | _     | 10.0 |      |

|                                        |                    | SCL and SDA                                   | _                           | —   | —     | 6.0  |      |

|                                        |                    | Output pins<br>except port 8,<br>SCL, and SDA | _                           |     | _     | 0.5  |      |

| Allowable output low current (total)   | $\Sigma I_{OL}$    | Output pins<br>except port 8,<br>SCL, and SDA | $V_{cc}$ = 4.0 to 5.5 V     | _   | _     | 40.0 | mA   |

|                                        |                    | Port 8,<br>SCL, and SDA                       | _                           | _   | _     | 80.0 |      |

|                                        |                    | Output pins<br>except port 8,<br>SCL, and SDA |                             | _   | _     | 20.0 | _    |

|                                        |                    | Port 8,<br>SCL, and SDA                       | _                           | _   | _     | 40.0 |      |

| Allowable output high                  | -I <sub>OH</sub>   | All output pins                               | $V_{\rm cc}$ = 4.0 to 5.5 V | _   | —     | 2.0  | mA   |

| current (per pin)                      |                    |                                               |                             | —   |       | 0.2  |      |

| Allowable output high                  | $ -\Sigma I_{OH} $ | All output pins                               | $V_{cc}$ = 4.0 to 5.5 V     |     | _     | 30.0 | mA   |

| current (total)                        |                    |                                               |                             | _   | _     | 8.0  |      |

# 3. Logic Instructions

| Mnemonic |                   |              | Addressing Mode and<br>Instruction Length (bytes) |    |      |           |             |      |          |       | ) |                                                                                             |   |                |        |        |          |   |          | No. of<br>States <sup>*1</sup> |  |

|----------|-------------------|--------------|---------------------------------------------------|----|------|-----------|-------------|------|----------|-------|---|---------------------------------------------------------------------------------------------|---|----------------|--------|--------|----------|---|----------|--------------------------------|--|

|          |                   | Operand Size | #xx                                               | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @ aa | @(d, PC) | @ @aa |   | Operation                                                                                   |   | Condition Code |        |        |          |   |          | Advanced                       |  |

| AND      | AND.B #xx:8, Rd   | В            | <b>≢</b><br>2                                     | Ľ. |      |           |             | •    |          |       |   | Rd8∧#xx:8 → Rd8                                                                             | I | н              | N<br>↓ | z<br>≎ | <b>v</b> | С | Normal   | 2                              |  |

| AND      | AND.B #XX.8, Hu   | B            | 2                                                 | 2  |      |           |             |      |          |       |   | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                      |   | _              |        | 2      |          |   |          |                                |  |

|          | AND.W #xx:16. Rd  | W            | 4                                                 | 2  |      |           |             |      |          |       |   | $Rd16_{A}Rs8 \rightarrow Rd8 \qquad -$<br>Rd16_{xx:16 \rightarrow Rd16 -                    |   |                | ↓ ↓    | ↓      | 0        | _ | -        | <u>-</u><br>1                  |  |

|          | AND.W Rs, Rd      | w            | 4                                                 | 2  |      |           |             |      |          |       |   | $Rd16 \land \#XX:16 \rightarrow Rd16 \qquad -$<br>Rd16 \land Rs16 \rightarrow Rd16 \qquad - |   |                | ↓ ↓    | ↓      | 0        |   |          | +<br>2                         |  |

|          | AND.L #xx:32, ERd | L            | 6                                                 | 2  |      |           |             |      |          |       |   | EBd32 $\wedge$ #xx:32 $\rightarrow$ EBd32 $-$                                               |   |                | ↓ ↓    | ↓      | 0        |   |          | <u>-</u><br>6                  |  |

|          | AND.L ERs, ERd    |              |                                                   | 4  |      |           |             |      |          |       |   | $ERd32 \land ERs32 \to ERd32$                                                               | _ | _              | ↓      | ⇒      | 0        | _ |          | 3<br>4                         |  |