# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km101-e-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART2 16x Baud Rate Clock Output               |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

### 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

#### TABLE 4-26: CTMU REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|---------|---------|---------------|

| CTMUCON1L | 35Ah  | CTMUEN  | _       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1   | IRNG0   | 0000          |

| CTMUCON1H | 35Ch  | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _       | _       | 0000          |

| CTMUCON2L | 35Eh  | —       | _       | —        | _        |          |          | —        | -        | -       | -       | _        | IRSTEN   |          | DISCHS2  | DISCHS1 | DISCHS0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-27: ANSEL REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6    | Bit 5                | Bit 4                | Bit 3                | Bit 2                  | Bit 1                  | Bit 0                  | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|----------|----------------------|----------------------|----------------------|------------------------|------------------------|------------------------|---------------------|

| ANSA         | 4E0h  | —      | _      | —      | —      | —      | —      | —     | _     | _     | —        | —                    | ANSA4 <sup>(2)</sup> | ANSA3                | ANSA2                  | ANSA1                  | ANSA0                  | 001F <sup>(1)</sup> |

| ANSB         | 4E2h  | ANSB15 | ANSB14 | ANSB13 | ANSB12 | _      | _      | ANSB9 | ANSB8 | ANSB7 | ANSB6(2) | ANSB5 <sup>(2)</sup> | ANSB4                | ANSB3 <sup>(2)</sup> | ANSB2                  | ANSB1                  | ANSB0                  | <sub>F3FF</sub> (1) |

| ANSC         | 4E4h  | _      |        | —      | _      | —      | —      | _     |       |       | _        |                      | _                    | _                    | ANSC2 <sup>(2,3)</sup> | ANSC1 <sup>(2,3)</sup> | ANSC0 <sup>(2,3)</sup> | 0007 <b>(1)</b>     |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

### TABLE 4-28: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10        | Bit 9          | Bit 8          | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets       |

|-----------|-------|--------|--------|---------|---------|---------|---------------|----------------|----------------|---------|--------|-------|-------|-------|-------|-------|-------|---------------------|

| ALRMVAL   | 620h  |        |        |         |         |         | Alarm Value I | High Register  | Window Based   | on APTR | <1:0>  |       |       |       |       |       |       | XXXX                |

| ALCFGRPT  | 622h  | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0        | ALRMPTR1       | ALRMPTR0       | ARPT7   | ARPT6  | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | <sub>0000</sub> (1) |

| RTCVAL    | 624h  |        |        |         |         | R       | TCC Value H   | igh Register W | /indow Based o | n RTCPT | R<1:0> |       |       |       |       |       |       | xxxx                |

| RCFGCAL   | 626h  | RTCEN  | _      | RTCWREN | RTCSYNC | HALFSEC | RTCOE         | RTCPTR1        | RTCPTR0        | CAL7    | CAL6   | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000 <b>(1)</b>     |

| RTCPWC    | 628h  | PWCEN  | PWCPOL | PWCCPRE | PWCSPRE | RTCCLK1 | RTCCLK0       | RTCOUT1        | RTCOUT0        | _       | _      | _     | _     | _     | -     | _     | _     | <sub>0000</sub> (1) |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** Values are reset only on a VDD POR event.

### REGISTER 8-17: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0     |

|---------|-----|-----|-----|-----|-----|-----|---------|

| —       | —   | —   | —   | —   | —   | —   | —       |

| bit 15  |     |     |     |     |     |     | bit 8   |

|         |     |     |     |     |     |     |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

| —       | —   | —   | —   | —   | —   | —   | ULPWUIE |

| bit 7   |     |     |     |     |     |     | bit 0   |

|         |     |     |     |     |     |     |         |

| Legend: |     |     |     |     |     |     |         |

| Logena.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

### REGISTER 8-18: IEC6: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | —   | —   | _   | CLC2IE | CLC1IE |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IE: Configurable Logic Cell 2 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 0 CLC1IE: Configurable Logic Cell 1 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

### FIGURE 13-4: 32-BIT TIMER MODE

| U-0        | U-0                                 | U-0                              | U-0              | U-0                              | U-0              | U-0               | U-0      |

|------------|-------------------------------------|----------------------------------|------------------|----------------------------------|------------------|-------------------|----------|

| _          | _                                   |                                  | _                | _                                | —                | _                 |          |

| bit 15     | ·                                   |                                  | ·                |                                  |                  |                   | bit      |

|            |                                     |                                  |                  |                                  |                  |                   |          |

| R/W-0      |                                     | R-0                              | R-0              | R-0                              | R-0              | R-0               | R-0      |

| SMP        | CKE                                 | D/A                              | P <sup>(1)</sup> | S <sup>(1)</sup>                 | R/W              | UA                | BF       |

| bit 7      |                                     |                                  |                  |                                  |                  |                   | bit      |

| Legend:    |                                     |                                  |                  |                                  |                  |                   |          |

| R = Read   | able bit                            | W = Writable                     | bit              | U = Unimpler                     | nented bit, read | d as '0'          |          |

| -n = Value | at POR                              | '1' = Bit is se                  | t                | '0' = Bit is cle                 | ared             | x = Bit is unkn   | iown     |

|            |                                     |                                  |                  |                                  |                  |                   |          |

| bit 15-8   | Unimplemen                          | ted: Read as                     | 0'               |                                  |                  |                   |          |

| bit 7      | SMP: Slew R                         | ate Control bit                  |                  |                                  |                  |                   |          |

|            | In Master or S                      |                                  |                  |                                  |                  |                   |          |

|            |                                     |                                  |                  | ard Speed mode                   |                  | I 1 MHz)          |          |

| bit 6      | CKE: SMBus                          |                                  |                  |                                  | (0 KHZ)          |                   |          |

| DIL O      | In Master or S                      |                                  |                  |                                  |                  |                   |          |

|            |                                     | SMBus-specific                   | c inputs         |                                  |                  |                   |          |

|            | 0 = Disables                        | SMBus-specifi                    | c inputs         |                                  |                  |                   |          |

| bit 5      | D/A: Data/Ad                        | ldress bit                       |                  |                                  |                  |                   |          |

|            | <u>In Master mo</u><br>Reserved.    | <u>de:</u>                       |                  |                                  |                  |                   |          |

|            | In Slave mod                        |                                  | (                |                                  |                  |                   |          |

|            |                                     |                                  |                  | transmitted wa<br>transmitted wa |                  |                   |          |

| bit 4      | P: Stop bit <sup>(1)</sup>          |                                  |                  |                                  | 5 4441055        |                   |          |

| bit 4      |                                     | that a Stop bit                  | has been dete    | ected last                       |                  |                   |          |

|            |                                     | vas not detecte                  |                  |                                  |                  |                   |          |

| bit 3      | S: Start bit <sup>(1)</sup>         |                                  |                  |                                  |                  |                   |          |

|            |                                     | that a Start bit vas not detecte |                  | ected last                       |                  |                   |          |

| bit 2      | R/W: Read/W                         | Vrite Informatio                 | n bit            |                                  |                  |                   |          |

|            | In Slave mod                        | <u>e:</u> (2)                    |                  |                                  |                  |                   |          |

|            | 1 = Read                            |                                  |                  |                                  |                  |                   |          |

|            | 0 = Write<br>In Master mo           | do.(3)                           |                  |                                  |                  |                   |          |

|            |                                     | is in progress                   |                  |                                  |                  |                   |          |

|            |                                     | is not in progre                 | ess              |                                  |                  |                   |          |

| bit 1      | UA: Update /                        | Address bit (10                  | -Bit Slave mod   | le only)                         |                  |                   |          |

|            |                                     | that the user r<br>does not need |                  | e the address ir                 | the SSPxADE      | ) register        |          |

| Note 1:    | This bit is cleared                 | d on Reset and                   | when SSPEN       | is cleared.                      |                  |                   |          |

| 2:         | This bit holds the address match to |                                  |                  |                                  | ss match. This   | bit is only valid | from the |

| 3:         | ORing this bit wit                  | h SEN, RSEN,                     | PEN. RCEN        | or ACKEN will in                 | ndicate if the M | SSPx is in Activ  | ve mode  |

### REGISTER 14-2: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

## REGISTER 14-5: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0        | U-0                                        | U-0                                  | U-0                  | U-0                     | U-0                | U-0                 | U-0                |

|------------|--------------------------------------------|--------------------------------------|----------------------|-------------------------|--------------------|---------------------|--------------------|

| _          |                                            | _                                    |                      |                         | _                  | —                   |                    |

| bit 15     |                                            |                                      |                      |                         |                    |                     | bit 8              |

|            |                                            |                                      |                      |                         |                    |                     |                    |

| R/W-0      | R/W-0                                      | R/W-0                                | R/W-0                | R/W-0                   | R/W-0              | R/W-0               | R/W-0              |

| GCEN       | ACKSTAT                                    | ACKDT <sup>(1)</sup>                 | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>     | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7      |                                            |                                      |                      |                         |                    |                     | bit (              |

| Legend:    |                                            |                                      |                      |                         |                    |                     |                    |

| R = Reada  | able bit                                   | W = Writable                         | bit                  | U = Unimplem            | nented bit, read   | d as '0'            |                    |

| -n = Value |                                            | '1' = Bit is set                     |                      | '0' = Bit is clea       |                    | x = Bit is unkn     | lown               |

|            |                                            | 1 Bit io oot                         |                      | o Bit io olot           |                    |                     |                    |

| bit 15-8   | Unimplemen                                 | ted: Read as '                       | 0'                   |                         |                    |                     |                    |

| bit 7      | GCEN: Gene                                 | eral Call Enable                     | bit (Slave mod       | e only)                 |                    |                     |                    |

|            |                                            | interrupt when a call address is o   | 0                    | ddress (0000h)          | is received in     | the SSPxSR          |                    |

| bit 6      |                                            | cknowledge Sta                       |                      | Transmit mode           | ≏ onlv)            |                     |                    |

|            |                                            | edge was not re                      |                      |                         | c only)            |                     |                    |

|            |                                            | edge was receiv                      |                      |                         |                    |                     |                    |

| bit 5      | ACKDT: Ack                                 | nowledge Data                        | bit (Master Red      | ceive mode onl          | y) <sup>(1)</sup>  |                     |                    |

|            | 1 = No Ackno                               | owledge                              |                      |                         |                    |                     |                    |

|            | 0 = Acknowle                               | •                                    |                      |                         |                    |                     |                    |

| bit 4      |                                            | nowledge Sequ                        |                      | -                       | • •                |                     |                    |

|            |                                            |                                      |                      | SDAx and SC             | CLx pins and       | transmits ACI       | KDT data bit       |

|            |                                            | ically cleared by<br>edge sequence   |                      |                         |                    |                     |                    |

| bit 3      |                                            | ive Enable bit (                     |                      | mode only)(2)           |                    |                     |                    |

| bit 0      |                                            | Receive mode f                       | -                    | , mode only)            |                    |                     |                    |

|            | 0 = Receive i                              |                                      |                      |                         |                    |                     |                    |

| bit 2      | PEN: Stop Co                               | ondition Enable                      | bit (Master mo       | de only) <sup>(2)</sup> |                    |                     |                    |

|            |                                            | Stop condition c                     | n SDAx and SO        | CLx pins; auton         | natically cleare   | ed by hardware      |                    |

|            | 0 = Stop cond                              |                                      |                      |                         | (0)                |                     |                    |

| bit 1      | -                                          | ated Start Cond                      |                      | -                       |                    |                     |                    |

|            |                                            | Repeated Start<br>d Start conditio   |                      | DAx and SCLx            | pins; automati     | ically cleared by   | / hardware         |

| bit 0      | -                                          | ondition Enable                      |                      |                         |                    |                     |                    |

|            | Master Mode                                |                                      | DIC                  |                         |                    |                     |                    |

|            |                                            | <u></u><br>Start condition c         | on SDAx and S        | CLx pins: autor         | natically cleare   | ed by hardware      |                    |

|            | 0 = Start con                              |                                      |                      |                         |                    |                     |                    |

|            | Slave Mode:                                |                                      |                      |                         |                    |                     |                    |

|            |                                            | etching is enabl<br>etching is disab |                      | ve transmit and         | slave receive      | (stretch is enab    | oled)              |

| Note 1:    | The value that wi                          | ill be transmitte                    | d when the use       | r initiates an Ao       | cknowledge se      | equence at the e    | end of a           |

|            |                                            |                                      |                      |                         |                    |                     |                    |

| 2:         | receive.<br>If the I <sup>2</sup> C module |                                      | 1.10                 |                         |                    |                     |                    |

| REGISTER 16-2: | RTCPWC: RTCC CONFIGURATION REGISTER 2 <sup>(1)</sup> |

|----------------|------------------------------------------------------|

|                |                                                      |

| R/W-0      | R/W-0       | R/W-0                                | R/W-0                        | R/W-0                                  | R/W-0                  | R/W-0           | R/W-0         |

|------------|-------------|--------------------------------------|------------------------------|----------------------------------------|------------------------|-----------------|---------------|

| PWCEN      | PWCPOL      | PWCCPRE                              | PWCSPRE                      | RTCCLK1 <sup>(2)</sup>                 | RTCCLK0 <sup>(2)</sup> | RTCOUT1         | RTCOUT0       |

| bit 15     |             |                                      |                              |                                        |                        |                 | bit 8         |

|            |             |                                      |                              |                                        |                        |                 |               |

| U-0        | U-0         | U-0                                  | U-0                          | U-0                                    | U-0                    | U-0             | U-0           |

|            | —           |                                      |                              | _                                      | —                      |                 |               |

| bit 7      |             |                                      |                              |                                        |                        |                 | bit (         |

| Legend:    |             |                                      |                              |                                        |                        |                 |               |

| R = Reada  | able bit    | W = Writable                         | bit                          | U = Unimpleme                          | nted bit, read as      | '0'             |               |

| -n = Value | at POR      | '1' = Bit is set                     |                              | '0' = Bit is cleare                    | ed                     | x = Bit is unkr | nown          |

|            |             |                                      |                              |                                        |                        |                 |               |

| bit 15     | PWCEN: Po   | wer Control Er                       | able bit                     |                                        |                        |                 |               |

|            |             | ontrol is enable                     |                              |                                        |                        |                 |               |

|            |             | ontrol is disable                    |                              |                                        |                        |                 |               |

| bit 14     |             | ower Control F                       | •                            |                                        |                        |                 |               |

|            |             | ontrol output is<br>ontrol output is | •                            |                                        |                        |                 |               |

| bit 13     |             | Power Control                        |                              | caler hits                             |                        |                 |               |

|            |             |                                      | •                            | by-2 of source R <sup>-</sup>          | TCC clock              |                 |               |

|            |             |                                      |                              | by-1 of source R                       |                        |                 |               |

| bit 12     | PWCSPRE:    | Power Control                        | Sample Pres                  | caler bits                             |                        |                 |               |

|            |             |                                      |                              | by-2 of source R1<br>by-1 of source R1 |                        |                 |               |

| bit 11-10  | RTCCLK<1:   | 0>: RTCC Clo                         | ck Select bits <sup>(2</sup> | 2)                                     |                        |                 |               |

|            |             |                                      |                              | CC clock, which i                      | s used for all RT      | CC timer opera  | ations.       |

|            |             | al Secondary O<br>I LPRC Oscillat    |                              | C)                                     |                        |                 |               |

|            |             | al power line sc                     |                              |                                        |                        |                 |               |

|            |             | al power line so                     |                              |                                        |                        |                 |               |

| bit 9-8    | RTCOUT<1:   | : <b>0&gt;:</b> RTCC Out             | put Select bits              | 5                                      |                        |                 |               |

|            |             | the source of th                     | ne RTCC pin c                | output.                                |                        |                 |               |

|            | 00 = RTCC a | •                                    |                              |                                        |                        |                 |               |

|            | 01 = RTCC   | seconds clock                        |                              |                                        |                        |                 |               |

|            | 11 = Power  |                                      |                              |                                        |                        |                 |               |

| bit 7-0    | Unimpleme   | nted: Read as                        | '0'                          |                                        |                        |                 |               |

| Note 1:    | The RTCPWC  | register is only                     | affected by a                | POR                                    |                        |                 |               |

|            |             |                                      | -                            | r bits the Secon                       | da Valua ragistar      | should also be  | o urritton to |

2: When a new value is written to these register bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

NOTES:

### 17.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCONL

- CLCxCONH

- CLCxSEL

- CLCxGLSL

- CLCxGLSH

The CLCx Control registers (CLCxCONL and CLCxCONH) are used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Source Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Select registers (CLCxGLSL and CLCxGLSH) allow the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

### REGISTER 17-1: CLCxCONL: CLCx CONTROL REGISTER (LOW)

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 L                                                                                                                                                    | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                              | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   |                                    | U-0<br>—<br>R/W-0<br>MODE1 | U-0<br>bit 8<br>R/W-0<br>MODE0<br>bit 0 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------|----------------------------|-----------------------------------------|

| bit 15<br>R-0<br>LCOE<br>bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15<br>bit 14-12<br>bit 14-12<br>bit 11<br>bit 10<br>bit 9-8<br>bit 7                                                    | LCOUT<br>bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt | LCPOL<br>W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene | bit<br>xing input sign<br>s logic zero c<br>o'<br>nterrupt Enabl<br>ed when a risi | U-0<br>—<br>U = Unimpler<br>'0' = Bit is cle<br>nals<br>putputs | R/W-0<br>MODE2<br>nented bit, read | MODE1                      | R/W-0<br>MODE0<br>bit 0                 |

| R-0<br>LCOE<br>bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PO<br>bit 15<br>bit 14-12<br>bit 14-12<br>bit 11<br>bit 10<br>bit 10<br>bit 9-8<br>bit 7                                                    | LCOUT<br>bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt | LCPOL<br>W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene | bit<br>xing input sign<br>s logic zero c<br>o'<br>nterrupt Enabl<br>ed when a risi | U = Unimpler<br>'0' = Bit is cle<br>nals<br>putputs             | MODE2                              | MODE1                      | R/W-0<br>MODE0<br>bit 0                 |

| LCOE<br>bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15 L<br>bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                          | LCOUT<br>bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt | LCPOL<br>W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene | bit<br>xing input sign<br>s logic zero c<br>o'<br>nterrupt Enabl<br>ed when a risi | U = Unimpler<br>'0' = Bit is cle<br>nals<br>putputs             | MODE2                              | MODE1                      | MODE0<br>bit 0                          |

| LCOE<br>bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15 L<br>bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                          | LCOUT<br>bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt | LCPOL<br>W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene | bit<br>xing input sign<br>s logic zero c<br>o'<br>nterrupt Enabl<br>ed when a risi | U = Unimpler<br>'0' = Bit is cle<br>nals<br>putputs             | MODE2                              | MODE1                      | MODE0<br>bit 0                          |

| bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15<br>bit 14-12<br>bit 14-12<br>bit 10<br>bit 10<br>bit 9-8<br>bit 7                                                                             | bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt          | W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and hance<br>ted: Read as '0<br>Positive Edge In<br>will be generated<br>will not be generated        | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | nented bit, read                   | d as '0'                   | bit 0                                   |

| Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                                                       | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | '1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and ha<br><b>nted:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                           | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | ared                               |                            |                                         |

| R = Readable b         -n = Value at PC         bit 15       L         bit 14-12       L         bit 14-12       L         bit 11       L         bit 10       L         bit 9-8       L         bit 7       L | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | '1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and ha<br><b>nted:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                           | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | ared                               |                            | ıown                                    |

| R = Readable b         -n = Value at PC         bit 15       L         bit 14-12       L         bit 14-12       L         bit 11       L         bit 10       L         bit 9-8       L         bit 7       L | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | '1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and ha<br><b>nted:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                           | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | ared                               |                            | ıown                                    |

| -n = Value at P(<br>bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                                                                                    | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | '1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and ha<br><b>nted:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                           | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | ared                               |                            | nown                                    |

| bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                                                                                                        | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | Enable bit<br>enabled and mi<br>disabled and ha<br><b>ated:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                | ns logic zero c<br>)'<br>nterrupt Enabl<br>ed when a risi                          | nals<br>outputs<br>e bit                                        |                                    | x = Bit is unkr            | nown                                    |

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 L                                                                                                                                                    | 1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                    | enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                              | ns logic zero c<br>)'<br>nterrupt Enabl<br>ed when a risi                          | outputs<br>e bit                                                | on LCOUT                           |                            |                                         |

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 L                                                                                                                                                    | 1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                    | enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                              | ns logic zero c<br>)'<br>nterrupt Enabl<br>ed when a risi                          | outputs<br>e bit                                                | on LCOUT                           |                            |                                         |

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 L                                                                                                                                                    | 0 = CLCx is 0<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                                  | disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                                                | ns logic zero c<br>)'<br>nterrupt Enabl<br>ed when a risi                          | outputs<br>e bit                                                | on LCOUT                           |                            |                                         |

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 I                                                                                                                                        | Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                                                   | nted: Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                                                                          | )'<br>hterrupt Enabl<br>ed when a risi                                             | e bit                                                           | on LCOUT                           |                            |                                         |

| bit 11                                                                                                                                                                                                         | INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                                                                 | Positive Edge Ir<br>will be generate<br>will not be gene                                                                                                                              | nterrupt Enabl<br>ed when a risi                                                   |                                                                 | on LCOUT                           |                            |                                         |

| bit 10 I<br>bit 9-8 I<br>bit 7 I                                                                                                                                                                               | 1 = Interrupt<br>0 = Interrupt                                                                                                 | will be generate<br>will not be gene                                                                                                                                                  | ed when a risi                                                                     |                                                                 | on LCOUT                           |                            |                                         |

| bit 10 I<br>bit 9-8 U<br>bit 7 I                                                                                                                                                                               | 0 = Interrupt                                                                                                                  | will not be gene                                                                                                                                                                      |                                                                                    | ing eage occurs                                                 | ULCOOL                             |                            |                                         |

| bit 9-8                                                                                                                                                                                                        | INTN: CLCx                                                                                                                     |                                                                                                                                                                                       | natoa                                                                              |                                                                 |                                    |                            |                                         |

| bit 9-8                                                                                                                                                                                                        |                                                                                                                                | Negative Edge                                                                                                                                                                         | Interrupt Enat                                                                     | ole bit                                                         |                                    |                            |                                         |

| bit 9-8 <b>U</b><br>bit 7 <b>L</b>                                                                                                                                                                             |                                                                                                                                | will be generate                                                                                                                                                                      |                                                                                    | ing edge occurs                                                 | s on LCOUT                         |                            |                                         |

| bit 7 L                                                                                                                                                                                                        | •                                                                                                                              | will not be gene                                                                                                                                                                      |                                                                                    |                                                                 |                                    |                            |                                         |

|                                                                                                                                                                                                                | -                                                                                                                              | ted: Read as '0                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                         |

|                                                                                                                                                                                                                |                                                                                                                                | Port Enable bit                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                         |

|                                                                                                                                                                                                                |                                                                                                                                | rt pin output is e<br>rt pin output is d                                                                                                                                              |                                                                                    |                                                                 |                                    |                            |                                         |

|                                                                                                                                                                                                                | •                                                                                                                              | x Data Output S                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                         |

|                                                                                                                                                                                                                | 1 = CLCx out                                                                                                                   | •                                                                                                                                                                                     |                                                                                    |                                                                 |                                    |                            |                                         |

|                                                                                                                                                                                                                | 0 = CLCx out                                                                                                                   |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                         |

| bit 5 L                                                                                                                                                                                                        | LCPOL: CLC                                                                                                                     | x Output Polari                                                                                                                                                                       | ty Control bit                                                                     |                                                                 |                                    |                            |                                         |

|                                                                                                                                                                                                                |                                                                                                                                | out of the module                                                                                                                                                                     |                                                                                    |                                                                 |                                    |                            |                                         |

|                                                                                                                                                                                                                | 0 = The outr                                                                                                                   | ut of the medul                                                                                                                                                                       |                                                                                    | ed                                                              |                                    |                            |                                         |

| bit 4-3 <b>L</b>                                                                                                                                                                                               | •                                                                                                                              | out of the module                                                                                                                                                                     |                                                                                    | cu .                                                            |                                    |                            |                                         |

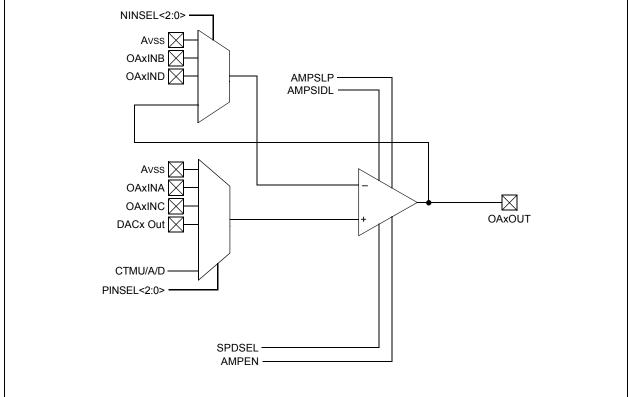

## 21.0 DUAL OPERATIONAL AMPLIFIER MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Operational Amplifier (Op Amp)"* (DS30505). Device-specific information in this data sheet supersedes the information in the *"PIC24F Family Reference Manual"*.

PIC24FV16KM204 family devices include two operational amplifiers to complement the microcontroller's other analog features. They may be used to provide analog signal conditioning, either as stand-alone devices or in addition to other analog peripherals. The two op amps are functionally identical; the block diagram for a single amplifier is shown in Figure 21-1. Each op amp has these features:

- · Internal unity-gain buffer option

- Multiple input options each on the inverting and non-inverting amplifier inputs

- · Rail-to-rail input and output capabilities

- User-selectable option for regular or low-power operation

- User-selectable operation in Idle and Sleep modes

When using the op amps, it is recommended to set the ANSx and TRISx bits of both the input and output pins to configure them as analog pins. See **Section 11.2 "Configuring Analog Port Pins"** for more information.

### REGISTER 25-4: FOSC: OSCILLATOR CONFIGURATION REGISTER

| R/P-1  | R/P-1  | R/P-1   | R/P-1     | R/P-1     | R/P-1    | R/P-1   | R/P-1   |

|--------|--------|---------|-----------|-----------|----------|---------|---------|

| FCKSM1 | FCKSM0 | SOSCSEL | POSCFREQ1 | POSCFREQ0 | OSCIOFNC | POSCMD1 | POSCMD0 |

| bit 7  |        |         |           |           |          |         | bit 0   |

| Legend:           |                      |                            |                    |

|-------------------|----------------------|----------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | <b>FCKSM&lt;1:0&gt;:</b> Clock Switching and Fail-Safe Clock Monitor Selection Configuration bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <b>SOSCSEL:</b> Secondary Oscillator Power Selection Configuration bit<br>1 = Secondary Oscillator is configured for high-power operation<br>0 = Secondary Oscillator is configured for low-power operation                                                                                                                                                          |

| bit 4-3 | <b>POSCFREQ&lt;1:0&gt;:</b> Primary Oscillator Frequency Range Configuration bits<br>11 = Primary Oscillator/External Clock input frequency is greater than 8 MHz<br>10 = Primary Oscillator/External Clock input frequency is between 100 kHz and 8 MHz<br>01 = Primary Oscillator/External Clock input frequency is less than 100 kHz<br>00 = Reserved; do not use |

| bit 2   | <ul> <li>OSCIOFNC: CLKO Enable Configuration bit</li> <li>1 = CLKO output signal is active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock (EC) mode for the CLKO to be active (POSCMD&lt;1:0&gt; = 11 or 00)</li> <li>0 = CLKO output is disabled</li> </ul>                                                              |

| bit 1-0 | POSCMD<1:0>: Primary Oscillator Configuration bits<br>11 = Primary Oscillator mode is disabled<br>10 = HS Oscillator mode is selected<br>01 = XT Oscillator mode is selected                                                                                                                                                                                         |

00 = External Clock mode is selected

NOTES:

### 27.1 DC Characteristics

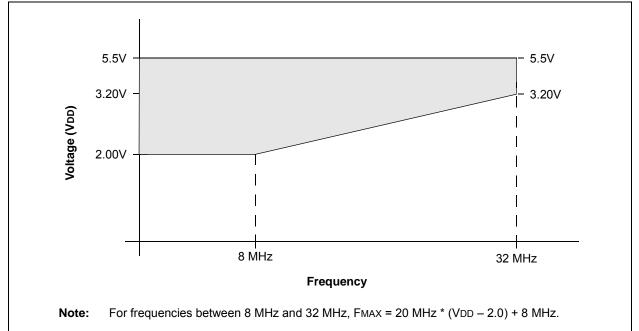

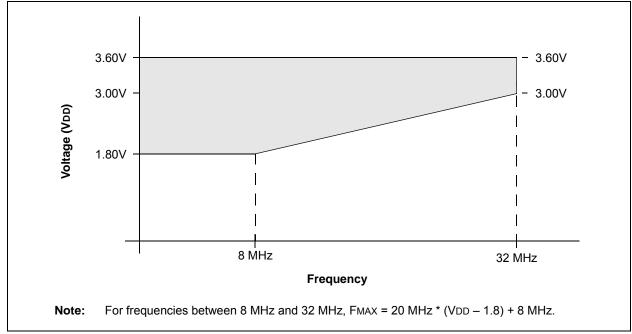

### FIGURE 27-2: PIC24F16KM204 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)