#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 16x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

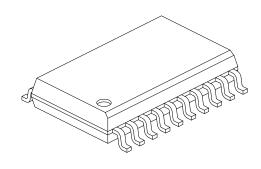

| Mounting Type              | Surface Mount                                                                 |

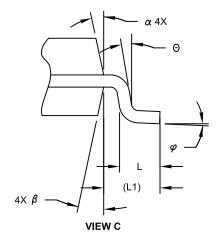

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 20-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km101t-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-15: UART1 REGISTER MAP

|           |       | •                                  |                                      |          |        |        |        |       |       |          |          |           |             |       |        |        |       |               |

|-----------|-------|------------------------------------|--------------------------------------|----------|--------|--------|--------|-------|-------|----------|----------|-----------|-------------|-------|--------|--------|-------|---------------|

| File Name | Addr. | Bit 15                             | Bit 14                               | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE    | 220h  | UARTEN                             | —                                    | USIDL    | IREN   | RTSMD  | -      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD     | URXINV      | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA     | 222h  | UTXISEL1                           | UTXINV                               | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN     | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG   | 224h  | _                                  | _                                    | _        | _      | _      | _      | _     |       |          |          | UART1 Tra | ansmit Regi | ster  |        |        |       | xxxx          |

| U1RXREG   | 226h  | —                                  | — — — — — — — UART1 Receive Register |          |        |        |        |       |       |          | 0000     |           |             |       |        |        |       |               |

| U1BRG     | 228h  | 228h Baud Rate Generator Prescaler |                                      |          |        |        |        |       |       |          |          | 0000      |             |       |        |        |       |               |

|           |       |                                    |                                      |          |        |        |        |       |       |          |          |           |             |       |        |        |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-16: UART2 REGISTER MAP

| File Name              | Addr. | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                    | Bit 7    | Bit 6    | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|------------------------|-------|----------|-------------------------------|----------|--------|--------|--------|-------|--------------------------|----------|----------|-----------|-------------|-------|--------|--------|-------|---------------|

| U2MODE <sup>(1)</sup>  | 230h  | UARTEN   | —                             | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0                     | WAKE     | LPBACK   | ABAUD     | URXINV      | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA <sup>(1)</sup>   | 232h  | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                     | URXISEL1 | URXISEL0 | ADDEN     | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG <sup>(1)</sup> | 234h  | _        | _                             | _        | —      | _      | _      | _     |                          |          |          | UART2 Tra | nsmit Regis | ster  |        |        |       | xxxx          |

| U2RXREG <sup>(1)</sup> | 236h  | _        | _                             | _        | —      | _      | _      | _     | UART2 Receive Register 0 |          |          |           |             | 0000  |        |        |       |               |

| U2BRG <sup>(1)</sup>   | 238h  |          | Baud Rate Generator Prescaler |          |        |        |        |       |                          |          |          | 0000      |             |       |        |        |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

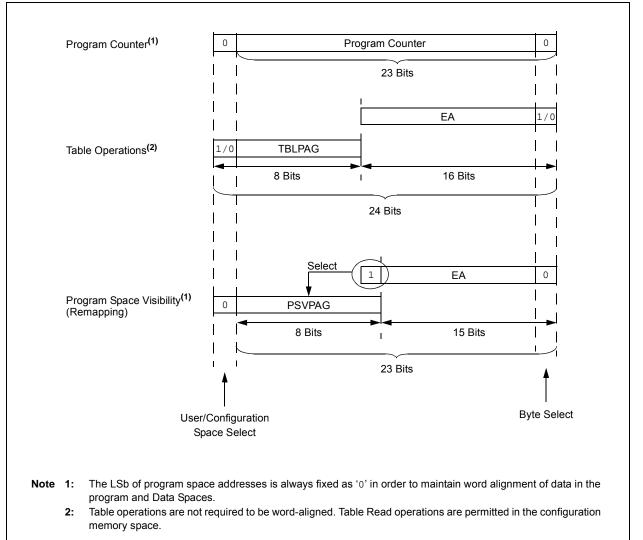

### TABLE 4-35: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        | Program Space Address |            |                         |                      |     |  |  |  |

|--------------------------|---------------|-----------------------|------------|-------------------------|----------------------|-----|--|--|--|

| Access Type              | Space         | <23>                  | <22:16>    | <15>                    | <14:1>               | <0> |  |  |  |

| Instruction Access       | User          | 0                     | PC<22:1>   |                         |                      | 0   |  |  |  |

| (Code Execution)         |               |                       | 0xx xxxx x | xxxx xxxx xxxx xxx0     |                      |     |  |  |  |

| TBLRD/TBLWT              | User          | TB                    | LPAG<7:0>  | Data EA<15:0>           |                      |     |  |  |  |

| (Byte/Word Read/Write)   |               | 02                    | xxx xxxx   | xxx                     | XXXX XXXX XXXX XXXX  |     |  |  |  |

|                          | Configuration | TBLPAG<7:0>           |            | Data EA<15:0>           |                      |     |  |  |  |

|                          |               | 1:                    | xxx xxxx   | xxxx xxxx xxxx xxxx     |                      |     |  |  |  |

| Program Space Visibility | User          | 0                     | PSVPAG<7:  | :0>(2) Data EA<14:0>(1) |                      |     |  |  |  |

| (Block Remap/Read)       |               | 0                     | xxxx xxx   | κx                      | x xxx xxxx xxxx xxxx |     |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on the PIC24F16KM family.

### FIGURE 4-5: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

### 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Flash programming, refer to the "PIC24F Family Reference Manual", "Program Memory" (DS39715).

The PIC24FV16KM204 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FXXXXX device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program Mode Entry Voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self-Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

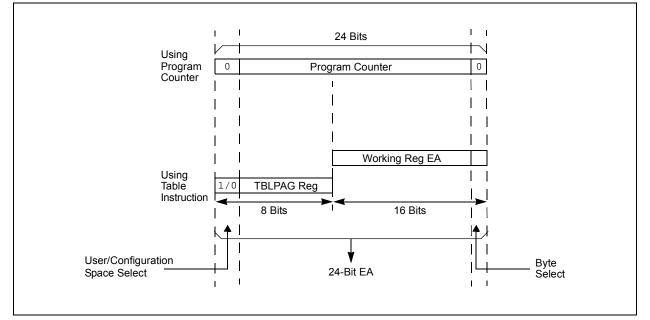

### 5.1 Table Instructions and Flash Programming

Regardless of the method used, Flash memory programming is done with the Table Read and Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### REGISTER 8-31: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

| _       | —   | —   | —   | —   | —       | —       | —       |

| bit 15  | ·   | •   |     |     | •       |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _       | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Logondi |     |     |     |     |         |         |         |

| Legend: |  |

|---------|--|

|---------|--|

bit 2-0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

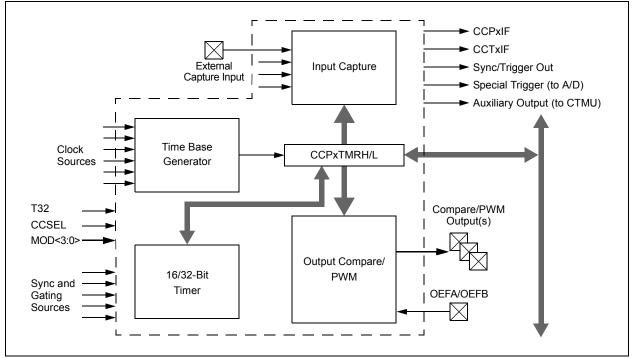

### 13.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive refer-      |

|       | ence source. For more information on the   |

|       | MCCP/SCCP modules, refer to the            |

|       | "PIC24F Family Reference Manual".          |

PIC24FV16KM204 family devices include several Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals of earlier PIC24F devices. The module can operate in one of three major modes:

- General Purpose Timer

- Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single output modules (SCCPs) provide only one PWM output. Multiple output modules (MCCPs) can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical.

The SCCP and MCCP modules can be operated only in one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode. A conceptual block diagram for the module is shown in Figure 13-1. All three modes share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of seven control and status registers:

- CCPxCON1L (Register 13-1)

- CCPxCON1H (Register 13-2)

- CCPxCON2L (Register 13-3)

- CCPxCON2H (Register 13-4)

- CCPxCON3L (Register 13-5)

- CCPxCON3H (Register 13-6)

- CCPxSTATL (Register 13-7)

Each module also includes eight buffer/counter registers that serve as Timer Value registers or data holding buffers:

- CCPxTMRH/CCPxTMRL (Timer High/Low Counters)

- CCPxPRH/CCPxPRL (Timer Period High/Low)

- CCPxRA (Primary Output Compare Data Buffer)

- CCPxRB (Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (Input Capture High/Low Buffers)

### FIGURE 13-1: MCCPx/SCCPx CONCEPTUAL BLOCK DIAGRAM

| U-0           | U-0             | U-0              | U-0                            | U-0                          | U-0               | U-0             | U-0           |

|---------------|-----------------|------------------|--------------------------------|------------------------------|-------------------|-----------------|---------------|

| _             | —               | _                | _                              | —                            | —                 | —               | —             |

| bit 15        | •               |                  |                                | •                            |                   | •               | bit           |

| DA            |                 |                  |                                |                              |                   |                 |               |

| R-0<br>ACKTIM | R/W-0<br>PCIE   | R/W-0<br>SCIE    | R/W-0<br>BOEN <sup>(1)</sup>   | R/W-0<br>SDAHT               | R/W-0<br>SBCDE    | R/W-0<br>AHEN   | R/W-0<br>DHEN |

| bit 7         | FUE             | SUE              | BOEIN'                         | SDAHI                        | SECDE             | ALEN            | bit           |

|               |                 |                  |                                |                              |                   |                 | bit           |

| Legend:       |                 |                  |                                |                              |                   |                 |               |

| R = Readabl   | le bit          | W = Writable     | bit                            | U = Unimplem                 | nented bit, read  | 1 as '0'        |               |

| -n = Value at | t POR           | '1' = Bit is set |                                | '0' = Bit is clea            | ared              | x = Bit is unkn | own           |

|               |                 |                  |                                |                              |                   |                 |               |

| bit 15-8      | -               | ted: Read as '   |                                |                              |                   |                 |               |

| bit 7         |                 | •                | e Status bit (I <sup>2</sup> 0 | C™ mode only)                |                   |                 |               |

|               | Unused in SP    |                  |                                | •                            |                   |                 |               |

| bit 6         |                 |                  | ipt Enable bit (I              | <sup>2</sup> C mode only)    |                   |                 |               |

|               | Unused in SP    |                  |                                | •                            |                   |                 |               |

| bit 5         |                 |                  | ipt Enable bit (I              | <sup>2</sup> C mode only)    |                   |                 |               |

|               | Unused in SP    |                  | (1)                            |                              |                   |                 |               |

| bit 4         |                 | r Overwrite Ena  | able bit <sup>(1)</sup>        |                              |                   |                 |               |

|               | In SPI Slave I  |                  | ny timo that a p               | ew data byte is              | chiffod in igno   | ring the DE bit |               |

|               |                 |                  |                                | bit of the SSPxS             |                   |                 | SSPOV bit     |

|               |                 |                  |                                | buffer is not up             |                   |                 |               |

| bit 3         | SDAHT: SDA      | x Hold Time Se   | election bit (I <sup>2</sup> C | mode only)                   |                   |                 |               |

|               | Unused in SP    | l mode.          |                                |                              |                   |                 |               |

| bit 2         | SBCDE: Slav     | ve Mode Bus C    | ollision Detect                | Enable bit (I <sup>2</sup> C | Slave mode or     | ıly)            |               |

|               | Unused in SP    | l mode.          |                                |                              |                   |                 |               |

| bit 1         | AHEN: Addre     | ess Hold Enabl   | e bit (l <sup>2</sup> C Slave  | mode only)                   |                   |                 |               |

|               | Unused in SP    | l mode.          |                                |                              |                   |                 |               |

| bit 0         | DHEN: Data      | Hold Enable bi   | t (Slave mode o                | only)                        |                   |                 |               |

|               | Unused in SP    | Pl mode.         |                                |                              |                   |                 |               |

| Note 1: F     | or Daisy-Chaine | ed SPI Operatio  | on: Allows the u               | iser to ignore al            | I but the last re | ceived byte S   | SDUV is still |

### REGISTER 14-6: SSPxCON3: MSSPx CONTROL REGISTER 3 (SPI MODE)

**Note 1:** For Daisy-Chained SPI Operation: Allows the user to ignore all but the last received byte. SSPOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSPxBUF.

### REGISTER 15-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0 | R-0, HSC | R-1, HSC |

|----------|--------|----------|-----|-----------|-------|----------|----------|

| UTXISEL1 | UTXINV | UTXISEL0 | —   | UTXBRK    | UTXEN | UTXBF    | TRMT     |

| bit 15   |        |          |     |           |       |          | bit 8    |

| R/W-0    | R/W-0    | R/W-0 | R-1, HSC | R-0, HSC | R-0, HSC | R/C-0, HS | R-0, HSC |

|----------|----------|-------|----------|----------|----------|-----------|----------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE    | PERR     | FERR     | OERR      | URXDA    |

| bit 7    |          |       |          |          |          |           | bit 0    |

| Legend:                    | HC = Hardware Clearable bit |                                    |                    |  |

|----------------------------|-----------------------------|------------------------------------|--------------------|--|

| HS = Hardware Settable bit | C = Clearable bit           | HSC = Hardware Settable/Cle        | earable bit        |  |

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR          | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit

| bit 14  | UTXINV: IrDA <sup>®</sup> Encoder Transmit Polarity Inversion bit                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If IREN = 0:</u>                                                                                                                                                                                                      |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                        |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                        |

|         | <u>If IREN = 1:</u>                                                                                                                                                                                                      |

|         | 1 = UxTX Idle '1'                                                                                                                                                                                                        |

|         | 0 = UxTX Idle '0'                                                                                                                                                                                                        |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                               |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                                                                         |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul>                                                    |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                                                                     |

| bit 10  | UTXEN: UARTx Transmit Enable bit                                                                                                                                                                                         |

|         | <ul> <li>1 = Transmit is enabled; UxTX pin is controlled by UARTx</li> <li>0 = Transmit is disabled; any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by the PORT register</li> </ul> |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                                                                 |

|         | 1 = Transmit buffer is full                                                                                                                                                                                              |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                              |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                      |

|         | <ul> <li>1 = Transmit Shift Register is empty and the transmit buffer is empty (the last transmission has<br/>completed)</li> </ul>                                                                                      |

|         | 0 = Transmit Shift Register is not empty; a transmission is in progress or queued                                                                                                                                        |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                |

|         | 11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)                                                                                                                   |

|         | 10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)                                                                                                               |

|         | 0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters                                                                       |

|         |                                                                                                                                                                                                                          |

#### 16.2.4 RTCC CONTROL REGISTERS

## REGISTER 16-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                  | R-0, HSC                                                                                                                                                                         | R-0, HSC                                                                                                                              | R/W-0                                                                                     | R/W-0                                                                  | R/W-0                                               |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|

| RTCEN <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                        | RTCWREN                                                                                                                                                                                                                                                                                                                                                | RTCSYNC                                                                                                                                                                          | HALFSEC <sup>(3)</sup>                                                                                                                | RTCOE                                                                                     | RTCPTR1                                                                | RTCPTR0                                             |  |  |  |

| bit 15               |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  | 1                                                                                                                                     |                                                                                           |                                                                        | bit 8                                               |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |  |  |  |

| R/W-0                | R/W-0                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                            | R/W-0                                                                                                                                 | R/W-0                                                                                     | R/W-0                                                                  | R/W-0                                               |  |  |  |

| CAL7                 | CAL6                                                                                                                                                                                                                                                                                                                                   | CAL5                                                                                                                                                                                                                                                                                                                                                   | CAL4                                                                                                                                                                             | CAL3                                                                                                                                  | CAL2                                                                                      | CAL1                                                                   | CAL0                                                |  |  |  |

| bit 7                |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        | bit (                                               |  |  |  |

| Legend:              |                                                                                                                                                                                                                                                                                                                                        | HSC = Hardw                                                                                                                                                                                                                                                                                                                                            | are Settable/C                                                                                                                                                                   | learable bit                                                                                                                          |                                                                                           |                                                                        |                                                     |  |  |  |

| R = Readable         | e bit                                                                                                                                                                                                                                                                                                                                  | W = Writable I                                                                                                                                                                                                                                                                                                                                         | oit                                                                                                                                                                              | U = Unimplem                                                                                                                          | ented bit, rea                                                                            | d as '0'                                                               |                                                     |  |  |  |

| -n = Value at        | POR                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  | '0' = Bit is clea                                                                                                                     |                                                                                           | x = Bit is unkr                                                        | iown                                                |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |  |  |  |

| bit 15               | RTCEN: RT                                                                                                                                                                                                                                                                                                                              | CC Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                        | nodule is enable                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                |                                                                                                                                       |                                                                                           |                                                                        |                                                     |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                        | nodule is disable                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |  |  |  |

| bit 14               | •                                                                                                                                                                                                                                                                                                                                      | nted: Read as '0                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |  |  |  |

| bit 13               |                                                                                                                                                                                                                                                                                                                                        | RTCWREN: RTCC Value Registers Write Enable bit                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |  |  |  |

|                      | <ul> <li>1 = RTCVALH and RTCVALL registers can be written to by the user</li> <li>0 = RTCVALH and RTCVALL registers are locked out from being written to by the user</li> </ul>                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           | n to by the user                                                       |                                                     |  |  |  |

| bit 12               | 0 = RTCVAL                                                                                                                                                                                                                                                                                                                             | H and RTCVAL                                                                                                                                                                                                                                                                                                                                           | L registers are                                                                                                                                                                  | locked out from                                                                                                                       | n being writter                                                                           | n to by the user                                                       |                                                     |  |  |  |

| bit 12               | 0 = RTCVAL<br>RTCSYNC:                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                        | L registers are<br>gisters Read S                                                                                                                                                | locked out from                                                                                                                       | h being writter<br>bit                                                                    |                                                                        | rollover ripple                                     |  |  |  |

| bit 12               | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting                                                                                                                                                                                                                                                                                      | ∟H and RTCVAL<br>RTCC Value Reo<br>∟H, RTCVALL ar<br>g in an invalid da                                                                                                                                                                                                                                                                                | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the                                                                                                              | locked out from<br>ynchronization<br>registers can c                                                                                  | n being writter<br>bit<br>hange while r                                                   | eading due to a                                                        |                                                     |  |  |  |

| bit 12               | 0 = RTCVAI<br>RTCSYNC:<br>1 = RTCVAI<br>resulting<br>can be a                                                                                                                                                                                                                                                                          | ₋H and RTCVAL<br>RTCC Value Reg<br>∟H, RTCVALL ar<br>g in an invalid da<br>assumed to be va                                                                                                                                                                                                                                                            | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the<br>alid.                                                                                                     | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |  |  |  |

|                      | 0 = RTCVAL<br><b>RTCSYNC:</b><br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL                                                                                                                                                                                                                                                     | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or                                                                                                                                                                                                                                               | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r                                                                                       | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |  |  |  |

| bit 12<br>bit 11     | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H                                                                                                                                                                                                                                              | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or<br>Half Second Stat                                                                                                                                                                                                                           | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>tus bit <sup>(3)</sup>                                                             | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |  |  |  |

|                      | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC:<br>1 = Second                                                                                                                                                                                                                                  | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or                                                                                                                                                                                                                                               | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>sus bit <sup>(3)</sup><br>second                                                   | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |  |  |  |

|                      | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal                                                                                                                                                                                                               | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a s                                                                                                                                                                                                | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>sus bit <sup>(3)</sup><br>second<br>ond                                            | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |  |  |  |

| bit 11               | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: 1<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o                                                                                                                                                                                 | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled                                                                                                                                                        | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>tus bit <sup>(3)</sup><br>second<br>ond<br>le bit                                  | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o                                                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled                                                                                                                                 | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>second<br>ond<br>le bit                                                            | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be                                         | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without                 | eading due to a<br>ults in the same                                    | data, the data                                      |  |  |  |

| bit 11               | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:                                                                                                                                                      | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0-:</b> RTCC Value                                                                                                              | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind                  | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be                                         | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without                 | eading due to a<br>ults in the same<br>concern over a                  | data, the data                                      |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled                                                                                                                                 | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>LH, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>LH, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec                                                                | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT                                                                                  | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>: <u>8&gt;:</u><br>ES                                       | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKI                                                                    | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>: <u>8&gt;:</u><br>ES<br>DAY                              | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT                                                                                  | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>:8>:<br>ES<br>DAY<br>H                                      | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKE<br>10 = MONTH                                                      | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enabled<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>: <u>8&gt;:</u><br>ES<br>DAY<br>H<br>ed                    | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKI<br>10 = MONTH<br>11 = Reserv<br><u>RTCVAL&lt;7:(</u><br>00 = SECON | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va-<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br><u>:8&gt;:</u><br>ES<br>DAY<br>H<br>ed<br><u>)&gt;:</u><br>NDS | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |  |  |  |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKI<br>10 = MONTH<br>11 = Reserv<br><u>RTCVAL&lt;7:0</u>               | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va-<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br><u>:8&gt;:</u><br>ES<br>DAY<br>H<br>ed<br><u>)&gt;:</u><br>NDS | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |  |  |  |

Note 1: The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

### REGISTER 19-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                 | R/W-0                                                                      | R/W-0               | R/W-0                     | R/W-0            | R/W-0            | R/W-0          | R/W-0                 |

|-----------------------|----------------------------------------------------------------------------|---------------------|---------------------------|------------------|------------------|----------------|-----------------------|

| CHH15                 | CHH14                                                                      | CHH13               | CHH12                     | CHH11            | CHH10            | CHH9           | CHH8 <sup>(2,3)</sup> |

| bit 15                |                                                                            |                     |                           | •                | •                | •              | bit 8                 |

|                       |                                                                            |                     |                           |                  |                  |                |                       |

| R/W-0                 | R/W-0                                                                      | R/W-0               | R/W-0                     | R/W-0            | R/W-0            | R/W-0          | R/W-0                 |

| CHH7 <sup>(2,3)</sup> | CHH6 <sup>(2,3)</sup>                                                      | CHH5 <sup>(2)</sup> | CHH4                      | CHH3             | CHH2             | CHH1           | CHH0                  |