#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km102-e-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

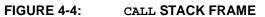

#### 4.2.5 SOFTWARE STACK

In addition to its use as a working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as depicted in Figure 4-4.

For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | will concatenate the SRL register to the |  |  |  |  |  |  |  |  |

|       | MSB of the PC prior to the push.         |  |  |  |  |  |  |  |  |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6 in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit-wide program space and 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the Data Space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

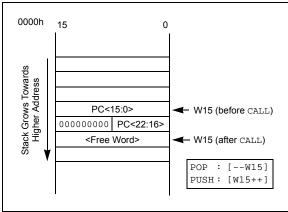

#### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

See Table 4-35 and Figure 4-5 to know how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a Data Space word.

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through Data Space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

Note: The TBLRDH and TBLWTH instructions are not used while accessing data EEPROM memory.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit, word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table Write operations are not allowed.

© 2013 Microchip Technology Inc.

#### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS |  |  |  |

|-------|-----|-----|-----|-----|-----|-----|-----------|--|--|--|

| —     | —   | —   | _   | —   | _   | —   | ULPWUIF   |  |  |  |

| bit 7 |     |     |     |     |     |     |           |  |  |  |

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

#### REGISTER 8-11: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----------|-----------|

| _     | —   | —   | —   | —   | —   | CLC2IF    | CLC1IF    |

| bit 7 |     |     |     |     |     |           | bit 0     |

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IF: Configurable Logic Cell 2 Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

bit 0 CLC1IF: Configurable Logic Cell 1 Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

#### REGISTER 8-14: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| U-0                                | U-0        | U-0                       | U-0             | U-0                                     | U-0              | R/W-0  | U-0   |

|------------------------------------|------------|---------------------------|-----------------|-----------------------------------------|------------------|--------|-------|

| _                                  | —          | —                         | —               | —                                       | —                | CCT5IE | —     |

| bit 15                             |            |                           |                 |                                         |                  |        | bit 8 |

|                                    |            |                           |                 |                                         |                  |        |       |

| U-0                                | U-0        | U-0                       | U-0             | U-0                                     | U-0              | U-0    | U-0   |

|                                    | —          | —                         | —               | —                                       | _                |        | —     |

| bit 7                              |            |                           |                 |                                         |                  |        | bit 0 |

|                                    |            |                           |                 |                                         |                  |        |       |

| Legend:                            |            |                           |                 |                                         |                  |        |       |

| R = Readable                       | e bit      | W = Writable              | bit             | U = Unimplem                            | nented bit, read | as '0' |       |

| -n = Value at POR '1' = Bit is set |            |                           |                 | '0' = Bit is cleared x = Bit is unknown |                  |        | iown  |

|                                    |            |                           |                 |                                         |                  |        |       |

| bit 15-10                          | Unimplemen | ted: Read as '            | כי              |                                         |                  |        |       |

| hit 9                              | CCT5IE Can | ture/Compare <sup>J</sup> | 5 Timer Interru | ot Enable bit                           |                  |        |       |

| bit 9 | <b>CCT5IE:</b> Capture/Compare 5 Timer Interrupt Enable bit |

|-------|-------------------------------------------------------------|

|       | 1 = Interrupt request is enabled                            |

|       | 0 = Interrupt request is not enabled                        |

|       |                                                             |

bit 8-0 Unimplemented: Read as '0'

#### REGISTER 8-15: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| U-0    | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-------|-----|-----|-----|-----|-----|-------|

| —      | RTCIE | —   | —   | —   | —   | —   | —     |

| bit 15 |       |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0   |

|-------|-----|-----|-----|-----|--------|--------|-------|

| —     | —   | —   | —   | —   | BCL2IE | SSP2IE | —     |

| bit 7 |     |     |     |     |        |        | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                                      |

|----------|-------------------------------------------------------------------------------------------------|

| bit 14   | RTCIE: Real-Time Clock and Calendar Interrupt Enable bit                                        |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul> |

| bit 13-3 | Unimplemented: Read as '0'                                                                      |

| bit 2    | BCL2IE: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Enable bit                  |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul> |

| bit 1    | SSP2IE: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Enable bit                                   |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul> |

| bit 0    | Unimplemented: Read as '0'                                                                      |

|          |                                                                                                 |

#### REGISTER 8-17: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0     |

|---------|-----|-----|-----|-----|-----|-----|---------|

| —       | —   | —   | —   | —   | —   | —   | —       |

| bit 15  |     |     |     |     |     |     | bit 8   |

|         |     |     |     |     |     |     |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

| —       | —   | —   | —   | —   | —   | —   | ULPWUIE |

| bit 7   |     |     |     |     |     |     | bit 0   |

|         |     |     |     |     |     |     |         |

| Legend: |     |     |     |     |     |     |         |

| Logena.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### REGISTER 8-18: IEC6: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | —   | —   | _   | CLC2IE | CLC1IE |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IE: Configurable Logic Cell 2 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 0 CLC1IE: Configurable Logic Cell 1 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### REGISTER 8-21: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0                 | R/W-1      | R/W-0                            | R/W-0   | U-0               | U-0              | U-0             | U-0     |

|---------------------|------------|----------------------------------|---------|-------------------|------------------|-----------------|---------|

|                     | U1RXIP2    | U1RXIP1                          | U1RXIP0 | —                 | —                | —               | _       |

| bit 15              |            |                                  |         |                   |                  |                 | bit 8   |

| U-0                 | U-0        | U-0                              | U-0     | U-0               | R/W-1            | R/W-0           | R/W-0   |

| _                   | _          | _                                | _       | _                 | CCT2IP2          | CCT2IP1         | CCT2IP0 |

| bit 7               |            |                                  |         | •                 |                  |                 | bit 0   |

|                     |            |                                  |         |                   |                  |                 |         |

| Legend:             |            |                                  |         |                   |                  |                 |         |

| R = Readab          | le bit     | W = Writable                     | bit     | U = Unimplem      | nented bit, read | l as '0'        |         |

| -n = Value a        | t POR      | '1' = Bit is set                 |         | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|                     |            |                                  |         |                   |                  |                 |         |

|                     |            |                                  |         |                   |                  |                 |         |

| bit 15              | Unimplemen | ted: Read as 'd                  | כ'      |                   |                  |                 |         |

| bit 15<br>bit 14-12 | •          | ted: Read as 'd<br>•: UART1 Rece |         | Priority bits     |                  |                 |         |

- bit 11-3

bit 2-0

CCT2IP<2:0>: Capture/Compare 2 Timer Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt)

- ٠

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 8-29: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0           | U-0           | U-0                | U-0              | U-0                                | R/W-1      | R/W-0              | R/W-0  |  |  |

|---------------|---------------|--------------------|------------------|------------------------------------|------------|--------------------|--------|--|--|

|               | —             | _                  | —                |                                    | RTCIP2     | RTCIP1             | RTCIP0 |  |  |

| bit 15        | -             | -                  |                  |                                    |            |                    | bit 8  |  |  |

|               |               |                    |                  |                                    |            |                    |        |  |  |

| U-0           | U-0           | U-0                | U-0              | U-0                                | U-0        | U-0                | U-0    |  |  |

|               | —             | —                  | —                | —                                  | —          | —                  | —      |  |  |

| bit 7         |               |                    |                  |                                    |            | -                  | bit 0  |  |  |

|               |               |                    |                  |                                    |            |                    |        |  |  |

| Legend:       |               |                    |                  |                                    |            |                    |        |  |  |

| R = Readable  | e bit         | W = Writable       | bit              | U = Unimplemented bit, read as '0' |            |                    |        |  |  |

| -n = Value at | POR           | '1' = Bit is set   |                  | '0' = Bit is clea                  | ared       | x = Bit is unknown |        |  |  |

|               |               |                    |                  |                                    |            |                    |        |  |  |

| bit 15-11     | Unimplemen    | ted: Read as '     | )'               |                                    |            |                    |        |  |  |

| bit 10-8      | RTCIP<2:0>:   | Real-Time Clo      | ck and Calend    | ar Interrupt Pric                  | ority bits |                    |        |  |  |

|               | 111 = Interru | pt is Priority 7 ( | highest priority | interrupt)                         |            |                    |        |  |  |

|               | •             |                    |                  |                                    |            |                    |        |  |  |

|               | •             |                    |                  |                                    |            |                    |        |  |  |

|               | •             |                    |                  |                                    |            |                    |        |  |  |

|               |               | pt is Priority 1   |                  |                                    |            |                    |        |  |  |

|               | 000 = Interru | pt source is dis   | abled            |                                    |            |                    |        |  |  |

| bit 7-0       | Unimplemen    | ted: Read as '     | )'               |                                    |            |                    |        |  |  |

|               |               |                    |                  |                                    |            |                    |        |  |  |

### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24FXXXXX family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator:

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The Primary Oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

#### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 25.1 "Configuration Bits"). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

## 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                      | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|------------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler<br>(LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                       | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)                 | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)      | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)      | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                              | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                              | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                              | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

| R/W-0        | U-0                                                                                                 | R/W-0                                                                                                            | U-0                                | U-0                     | U-0              | R/W-0                | R/W-0                |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------|------------------|----------------------|----------------------|--|--|--|--|

| TON          |                                                                                                     | TSIDL                                                                                                            | —                                  | _                       | —                | TECS1 <sup>(1)</sup> | TECS0 <sup>(1)</sup> |  |  |  |  |

| bit 15       |                                                                                                     | •                                                                                                                | -                                  |                         |                  |                      | bit                  |  |  |  |  |

|              |                                                                                                     |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

| U-0          | R/W-0                                                                                               | R/W-0                                                                                                            | R/W-0                              | U-0                     | R/W-0            | R/W-0                | U-0                  |  |  |  |  |

| —            | TGATE                                                                                               | TCKPS1                                                                                                           | TCKPS0                             | —                       | TSYNC            | TCS                  | —                    |  |  |  |  |

| bit 7        |                                                                                                     |                                                                                                                  |                                    |                         |                  |                      | bit                  |  |  |  |  |

| Legend:      |                                                                                                     |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

| R = Readab   | ole bit                                                                                             | W = Writable                                                                                                     | bit                                | U = Unimpler            | mented bit, read | d as '0'             |                      |  |  |  |  |

| -n = Value a | It POR                                                                                              | '1' = Bit is set                                                                                                 |                                    | '0' = Bit is cle        | ared             | x = Bit is unkr      | iown                 |  |  |  |  |

|              |                                                                                                     |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

| bit 15       | TON: Timer1                                                                                         | On bit                                                                                                           |                                    |                         |                  |                      |                      |  |  |  |  |

|              | 1 = Starts 16-<br>0 = Stops 16-                                                                     |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

| bit 14       | Unimplemen                                                                                          | ted: Read as '                                                                                                   | 0'                                 |                         |                  |                      |                      |  |  |  |  |

| bit 13       | TSIDL: Timer                                                                                        | 1 Stop in Idle I                                                                                                 | Node bit                           |                         |                  |                      |                      |  |  |  |  |

|              |                                                                                                     |                                                                                                                  | eration when o<br>ation in Idle mo | device enters lo<br>ode | lle mode         |                      |                      |  |  |  |  |

| bit 12-10    | Unimplemen                                                                                          | ted: Read as '                                                                                                   | 0'                                 |                         |                  |                      |                      |  |  |  |  |

| bit 9-8      |                                                                                                     |                                                                                                                  | ed Clock Seled                     | ct bits <sup>(1)</sup>  |                  |                      |                      |  |  |  |  |

|              | 11 = Reserve                                                                                        | •                                                                                                                | as the sleek s                     | 0.1700                  |                  |                      |                      |  |  |  |  |

|              | 10 = Timer1 uses the LPRC as the clock source<br>01 = Timer1 uses the External Clock (EC) from T1CK |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

|              |                                                                                                     |                                                                                                                  |                                    | r (SOSC) as th          | e clock source   |                      |                      |  |  |  |  |

| bit 7        | Unimplemented: Read as '0'                                                                          |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

| bit 6        |                                                                                                     |                                                                                                                  | Accumulation                       | Enable bit              |                  |                      |                      |  |  |  |  |

|              | When TCS =                                                                                          |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

|              | When TCS = $\frac{1}{2}$                                                                            |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

|              |                                                                                                     | <u>o.</u><br>ne accumulatio                                                                                      | n is enabled                       |                         |                  |                      |                      |  |  |  |  |

|              | 0 = Gated tim                                                                                       | ne accumulatio                                                                                                   | n is disabled                      |                         |                  |                      |                      |  |  |  |  |

| bit 5-4      | TCKPS<1:0>                                                                                          | : Timer1 Input                                                                                                   | Clock Prescale                     | e Select bits           |                  |                      |                      |  |  |  |  |

|              | 11 = 1:256                                                                                          |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

|              | 10 = 1:64<br>01 = 1:8                                                                               |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

|              | 00 = 1:1                                                                                            |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

| bit 3        | Unimplemen                                                                                          | ted: Read as '                                                                                                   | 0'                                 |                         |                  |                      |                      |  |  |  |  |

| bit 2        | TSYNC: Time                                                                                         | er1 External Cl                                                                                                  | ock Input Sync                     | hronization Se          | lect bit         |                      |                      |  |  |  |  |

|              | <u>When TCS =</u>                                                                                   |                                                                                                                  | Clock input                        |                         |                  |                      |                      |  |  |  |  |

|              |                                                                                                     | <ul> <li>1 = Synchronizes External Clock input</li> <li>0 = Does not synchronize External Clock input</li> </ul> |                                    |                         |                  |                      |                      |  |  |  |  |

|              | When TCS =                                                                                          | -                                                                                                                |                                    |                         |                  |                      |                      |  |  |  |  |

|              | This bit is igno                                                                                    | ored.                                                                                                            |                                    |                         |                  |                      |                      |  |  |  |  |

| bit 1        |                                                                                                     | Clock Source                                                                                                     |                                    |                         |                  |                      |                      |  |  |  |  |

|              |                                                                                                     |                                                                                                                  | selected by TE                     | CS<1:0>                 |                  |                      |                      |  |  |  |  |

|              | 0 = Internal c                                                                                      |                                                                                                                  |                                    |                         |                  |                      |                      |  |  |  |  |

| bit 0        | Unimplemen                                                                                          | tod. Dood oo .                                                                                                   | Ω'                                 |                         |                  |                      |                      |  |  |  |  |

### 14.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on MSSP, refer to the "PIC24F Family Reference Manual".

The Master Synchronous Serial Port (MSSP) module is an 8-bit serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, Shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The SPI interface supports these modes in hardware:

- Master mode

- Slave mode

- · Daisy-Chaining Operation in Slave mode

- Synchronized Slave Operation

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode with 10-Bit and 7-Bit Addressing and Address Masking

- Byte NACKing

- Selectable Address and Data Hold, and Interrupt Masking

#### 14.1 I/O Pin Configuration for SPI

In SPI Master mode, the MSSP module will assert control over any pins associated with the SDOx and SCKx outputs. This does not automatically disable other digital functions associated with the pin and may result in the module driving the digital I/O port inputs. To prevent this, the MSSP module outputs must be disconnected from their output pins while the module is in SPI Master mode. While disabling the module temporarily may be an option, it may not be a practical solution in all applications.

The SDOx and SCKx outputs for the module can be selectively disabled by using the SDOxDIS and SCKxDIS bits in the PADCFG1 register (Register 14-10). Setting the bit disconnects the corresponding output for a particular module from its assigned pin.

'1' = Bit is set

#### REGISTER 14-8: SSPxADD: MSSPx SLAVE ADDRESS/BAUD RATE GENERATOR REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | U-0      | U-0   |

|--------------|-------|--------------|-------|--------------|------------------|----------|-------|

| —            | —     | —            |       | —            | _                | —        | _     |

| bit 15       |       |              |       |              |                  |          | bit 8 |

|              |       |              |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| ADD7         | ADD6  | ADD5         | ADD4  | ADD3         | ADD2             | ADD1     | ADD0  |

| bit 7        |       |              |       |              |                  |          | bit 0 |

|              |       |              |       |              |                  |          |       |

| Legend:      |       |              |       |              |                  |          |       |

| R = Readable | e bit | W = Writable | bit   | U = Unimplen | nented bit, read | l as '0' |       |

'0' = Bit is cleared

x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0

ADD<7:0>: Slave Address/Baud Rate Generator Value bits

SPI Master and I<sup>2</sup>C™ Master modes:

Reload value for the Baud Rate Generator. Clock period is (([SPxADD] + 1) \* 2)/Fosc.

I<sup>2</sup>C Slave modes:

Represents 7 or 8 bits of the slave address, depending on the addressing mode used:

7-Bit mode:

Address is ADD<7:1>; ADD<0> is ignored.

10-Bit LSb mode:

ADD<7:0> are the Least Significant bits of the address.

10-Bit MSb mode:

ADD<2:1> are the two Most Significant bits of the address; ADD<7:3> are always '11110' as a specification requirement; ADD<0> is ignored.

#### REGISTER 14-9: SSPxMSK: I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(1)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                              |

|----------|---------------------------------------------------------|

| bit 7-0  | MSK<7:0>: Slave Address Mask Select bits <sup>(1)</sup> |

|          | 1 = Masking of corresponding bit of SSPxADD is enabled  |

|          | 0 = Masking of corresponding bit of SSPxADD is disabled |

Note 1: MSK0 is not used as a mask bit in 7-bit addressing.

### 15.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features of  |

|-------|---------------------------------------------|

|       | this group of PIC24F devices. It is not     |

|       | intended to be a comprehensive reference    |

|       | source. For more information on the Univer- |

|       | sal Asynchronous Receiver Transmitter,      |

|       | refer to the "PIC24F Family Reference       |

|       | Manual", " <b>UART"</b> (DS39708).          |

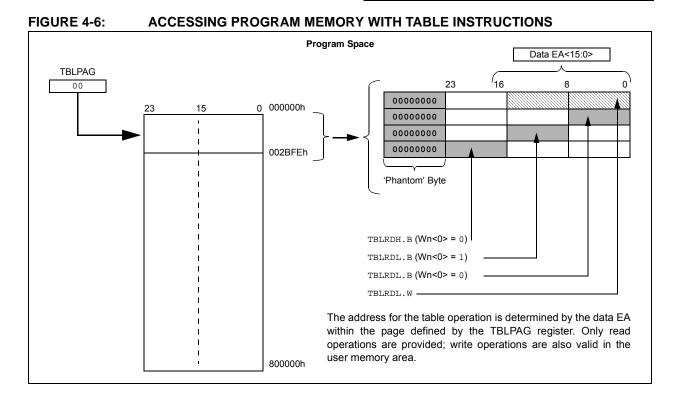

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 15-1. The UARTx module consists of these important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

- Note: Throughout this section, references to register and bit names that may be associated with a specific USART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the USART Status register for either USART1 or USART2.

#### FIGURE 15-1: UARTX MODULE SIMPLIFIED BLOCK DIAGRAM

NOTES:

| R/W-0              | R-0                                    | r-0                                             | R/W-0  | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|--------------------|----------------------------------------|-------------------------------------------------|--------|-------------------|------------------|-----------------|-------|

| ADRC               | EXTSAM                                 | r                                               | SAMC4  | SAMC3             | SAMC2            | SAMC1           | SAMC0 |

| bit 15             |                                        |                                                 |        |                   |                  |                 | bit   |

| R/W-0              | R/W-0                                  | R/W-0                                           | R/W-0  | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| ADCS7              | ADCS6                                  | ADCS5                                           | ADCS4  | ADCS3             | ADCS2            | ADCS1           | ADCS0 |

| bit 7              |                                        |                                                 | 1      |                   |                  |                 | bit   |

| Legend:            |                                        | r = Reserved                                    | bit    |                   |                  |                 |       |

| R = Readab         | le bit                                 | W = Writable                                    | bit    | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                  | '1' = Bit is set                                |        | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 13<br>bit 12-8 | 0 = A/D is fir<br><b>Reserved:</b> M   | Auto-Sample                                     | ]      | S                 |                  |                 |       |

|                    | •<br>•<br>00001 = 1 T.<br>00000 = 0 T. |                                                 |        |                   |                  |                 |       |

| bit 7-0            | 11111111-0                             | A/D Conversio<br>1000000 = Re<br>64 * TCY = TAC | served | : bits            |                  |                 |       |

|                    | •<br>00000001 =<br>00000000 =          | 2 * TCY = TAD                                   |        |                   |                  |                 |       |

#### REGISTER 19-3: AD1CON3: A/D CONTROL REGISTER 3

| R/W-0         | U-0               | R/W-0                                | R/W-0          | U-0               | U-0              | U-0             | U-0     |

|---------------|-------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|---------|

| AMPEN         |                   | AMPSIDL                              | AMPSLP         |                   |                  |                 |         |

| bit 15        |                   |                                      | •              |                   |                  |                 | bit 8   |

|               |                   |                                      |                |                   |                  |                 |         |

| R/W-0         | U-0               | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

| SPDSEL        | —                 | NINSEL2                              | NINSEL1        | NINSEL0           | PINSEL2          | PINSEL1         | PINSEL0 |

| bit 7         |                   |                                      |                |                   |                  |                 | bit 0   |

| Legend:       |                   |                                      |                |                   |                  |                 |         |

| R = Readabl   | e bit             | W = Writable                         | bit            | U = Unimplen      | nented bit, read | 1 as '0'        |         |

| -n = Value at | POR               | '1' = Bit is set                     |                | '0' = Bit is clea |                  | x = Bit is unkr | nown    |

|               |                   |                                      |                |                   |                  |                 | -       |

| bit 15        | AMPEN: Op         | Amp x Control                        | Module Enable  | e bit             |                  |                 |         |

|               | 1 = Module        |                                      |                |                   |                  |                 |         |

|               | 0 = Module        |                                      |                |                   |                  |                 |         |

| bit 14        | -                 | nted: Read as '                      |                |                   |                  |                 |         |

| bit 13        |                   | Dp Amp x Periph                      |                |                   |                  |                 |         |

|               |                   | nues module op<br>es module opera    |                |                   | le mode          |                 |         |

| bit 12        |                   | p Amp x Periph                       |                |                   | it               |                 |         |

|               |                   | es module opera                      |                | -                 |                  |                 |         |

|               |                   | nues module op                       |                |                   | pinouo           |                 |         |

| bit 11-8      | Unimpleme         | nted: Read as '                      | כי             |                   |                  |                 |         |

| bit 7         | SPDSEL: Op        | p Amp x Power/                       | Speed Select b | bit               |                  |                 |         |

|               | • •               | ower and band                        | •              | • •               |                  |                 |         |

| bit 6         |                   | ower and bandw                       | -              | sponse (me)       |                  |                 |         |

|               | -                 | nted: Read as '                      |                | oot hito          |                  |                 |         |

| bit 5-3       |                   | I>: Negative Op<br>rved; do not use  |                | ect bits          |                  |                 |         |

|               |                   | rved; do not use                     |                |                   |                  |                 |         |

|               |                   | np negative inpu                     |                | to the op amp     | output (voltage  | e follower)     |         |

|               |                   | rved; do not use                     |                |                   |                  |                 |         |

|               |                   | rved; do not use<br>np negative inpu |                | to the OAVING     | nin              |                 |         |

|               |                   | np negative inpl                     |                |                   |                  |                 |         |

|               |                   | np negative inpu                     |                |                   |                  |                 |         |

| bit 2-0       | PINSEL<2:0        | >: Positive Op /                     | Amp Input Sele | ect bits          |                  |                 |         |

|               | -                 | np positive inpu                     |                | to the output of  | the A/D input i  | multiplexer     |         |

|               |                   | rved; do not use                     |                | to the DAC1 of    | tout for OA1 /   |                 |         |

|               |                   | np positive inpu<br>rved; do not use |                |                   |                  |                 | i (JAZ) |

|               |                   | rved; do not use                     |                |                   |                  |                 |         |

|               |                   | np positive inpu                     |                |                   |                  |                 |         |

|               | •                 | np positive inpu                     |                |                   | pin              |                 |         |

|               | 000 = Op an       | np positive inpu                     | i is connected | IU AVSS           |                  |                 |         |

| Note 1: The   | nis register is a | vailable only on                     | PIC24F(V)16    | KM2XX devices     |                  |                 |         |

|               |                   |                                      |                |                   |                  |                 |         |

### REGISTER 21-1: AMPxCON: OP AMP x CONTROL REGISTER<sup>(1)</sup>

### 24.3 Pulse Generation and Delay

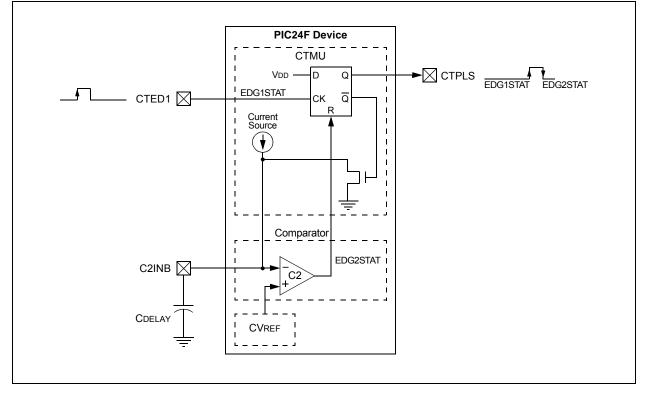

The CTMU module can also generate an output pulse with edges that are not synchronous with the device's system clock. More specifically, it can generate a pulse with a programmable delay from an edge event input to the module.

When the module is configured for pulse generation delay by setting the TGEN bit (CTMUCON1L<12>), the internal current source is connected to the B input of Comparator 2. A Capacitor (CDELAY) is connected to the Comparator 2 pin, C2INB, and the Comparator Voltage Reference, CVREF, is connected to C2INA. CVREF is then configured for a specific trip point. The module begins to charge CDELAY when an edge event is detected. While CVREF is greater than the voltage on CDELAY, the CTPLS pin is high.

When the voltage on CDELAY equals CVREF, CTPLS goes low. With Comparator 2 configured as the second edge, this stops the CTMU from charging. In this state event, the CTMU automatically connects to ground. The IDISSEN bit doesn't need to be set and cleared before the next CTPLS cycle.

Figure 24-3 illustrates the external connections for pulse generation, as well as the relationship of the different analog modules required. While CTED1 is shown as the input pulse source, other options are available. A detailed discussion on pulse generation with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

### FIGURE 24-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE DELAY GENERATION

#### REGISTER 24-2: CTMUCON1H: CTMU CONTROL 1 HIGH REGISTER (CONTINUED)

- bit 6 EDG2POL: Edge 2 Polarity Select bit 1 = Edge 2 is programmed for a positive edge 0 = Edge 2 is programmed for a negative edge bit 5-2 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = Edge 2 source is the Comparator 3 output 1110 = Edge 2 source is the Comparator 2 output 1101 = Edge 2 source is the Comparator 1 output 1100 = Unimplemented; do not use 1011 = Edge 2 source is CLC1 1010 = Edge 2 source is the MCCP2 Compare Event (CCP2IF) 1001 = Unimplemented; do not use 1000 = Edge 2 source is CTED13 0111 = Edge 2 source is CTED12 0110 = Edge 2 source is CTED11<sup>(2)</sup> 0101 = Edge 2 source is CTED10 0100 = Edge 2 source is CTED9<sup>(2)</sup> 0011 = Edge 2 source is CTED1 0010 = Edge 2 source is CTED2 0001 = Edge 2 source is the MCCP1 Compare Event (CCP1IF) 0000 = Edge 2 source is Timer1

- bit 1-0 Unimplemented: Read as '0'

- Note 1: Edge sources, CTED7 and CTED8, are not available on 28-pin and 20-pin devices.

- 2: Edge sources, CTED3, CTED9 and CTED11, are not available on 20-pin devices.

| DC CHARACTERISTICS |                | Standard C |     |       | 1.8V to 3.6V (PIC24F16KMXXX)<br>2.0V to 5.5V (PIC24FV16KMXXX)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                              |  |

|--------------------|----------------|------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| Parameter No.      | Device         | Typical    | Max | Units | Conditions                                                                                                                                                                     |                              |  |

| Idle Current (III  | DLE)           |            |     |       |                                                                                                                                                                                |                              |  |

| DC40               | PIC24FV16KMXXX | 120        | 200 | μA    | 2.0V                                                                                                                                                                           |                              |  |

|                    |                | 160        | 430 | μA    | 5.0V                                                                                                                                                                           | 0.5 MIPS,                    |  |

|                    | PIC24F16KMXXX  | 50         | 100 | μA    | 1.8V                                                                                                                                                                           | Fosc = 1 MHz <sup>(1)</sup>  |  |

|                    |                | 90         | 370 | μA    | 3.3V                                                                                                                                                                           |                              |  |

| DC42               | PIC24FV16KMXXX | 165        | _   | μA    | 2.0V                                                                                                                                                                           |                              |  |

|                    |                | 260        | _   | μA    | 5.0V                                                                                                                                                                           | 1 MIPS,                      |  |

|                    | PIC24F16KMXXX  | 95         | _   | μA    | 1.8V                                                                                                                                                                           | Fosc = 2 MHz <sup>(1)</sup>  |  |

|                    |                | 180        | _   | μA    | 3.3V                                                                                                                                                                           |                              |  |

| DC44               | PIC24FV16KMXXX | 3.1        | 6.5 | mA    | 5.0V                                                                                                                                                                           | 16 MIPS,                     |  |

|                    | PIC24F16KMXXX  | 2.9        | 6.0 | mA    | 3.3V                                                                                                                                                                           | Fosc = 32 MHz <sup>(1)</sup> |  |

| DC46               | PIC24FV16KMXXX | 0.65       |     | mA    | 2.0V                                                                                                                                                                           |                              |  |

|                    |                | 1.0        | _   | mA    | 5.0V                                                                                                                                                                           | FRC (4 MIPS),                |  |

|                    | PIC24F16KMXXX  | 0.55       | _   | mA    | 1.8V                                                                                                                                                                           | Fosc = 8 MHz                 |  |

|                    |                | 1.0        | —   | mA    | 3.3V                                                                                                                                                                           |                              |  |

| DC50               | PIC24FV16KMXXX | 42         | 200 | μA    | 2.0V                                                                                                                                                                           |                              |  |

|                    |                | 65         | 225 | μA    | 5.0V                                                                                                                                                                           | LPRC (15.5 KIPS),            |  |

|                    | PIC24F16KMXXX  | 2.2        | 18  | μA    | 1.8V                                                                                                                                                                           | Fosc = 31 kHz                |  |

|                    |                | 4.0        | 40  | μA    | 3.3V                                                                                                                                                                           |                              |  |

### TABLE 27-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Legend:** Unshaded rows represent PIC24F16KMXXX devices and shaded rows represent PIC24FV16KMXXX devices. **Note 1:** The oscillator is in External Clock mode (FOSCSEL<2:0> = 010, FOSC<1:0> = 00).

### т

| Timer1                                               | 1 |

|------------------------------------------------------|---|

| Timing Diagrams                                      |   |

| A/D Conversion                                       | 5 |

| Brown-out Reset Characteristics                      | 4 |

| Capture/Compare/PWM (MCCPx, SCCPx)                   | 5 |

| CLKO and I/O Timing                                  | 2 |

| Example SPI Master Mode (CKE = 0)                    | ô |

| Example SPI Master Mode (CKE = 1)287                 | 7 |

| Example SPI Slave Mode (CKE = 0)288                  |   |

| Example SPI Slave Mode (CKE = 1)289                  |   |

| External Clock                                       |   |

| I <sup>2</sup> C Bus Data                            |   |

| I <sup>2</sup> C Bus Start/Stop Bits                 | C |

| MSSPx I <sup>2</sup> C Bus Data                      | 3 |

| MSSPx I <sup>2</sup> C Bus Start/Stop Bits           | 2 |

| Reset, Watchdog Timer. Oscillator Start-up Timer,    |   |

| Power-up Timer Characteristics                       | 3 |

| Timing Requirements                                  |   |

| Capture/Compare/PWM (MCCPx, SCCPx)                   |   |

| Comparator                                           |   |

| Comparator Voltage Reference Settling Time           |   |

| I <sup>2</sup> C Bus Data (Slave Mode)               |   |

| I <sup>2</sup> C Bus Data Requirements (Master Mode) |   |

| I <sup>2</sup> C Bus Start/Stop Bits (Master Mode)   |   |

| I <sup>2</sup> C Bus Start/Stop Bits (Slave Mode)    |   |

| SPI Mode (Master Mode, CKE = 0)                      |   |

| SPI Mode (Master Mode, CKE = 1)287                   |   |

| SPI Mode (Slave Mode, CKE = 0)288                    |   |

| SPI Slave Mode (CKE = 1)289                          | 9 |

###

| UARI                                                       |     |

|------------------------------------------------------------|-----|

| Baud Rate Generator (BRG) 1                                | 74  |

| Break and Sync Transmit Sequence 1                         | 75  |

| IrDA Support 1                                             | 75  |

| IrDA Support 1 Operation of UxCTS and UxRTS Control Pins 1 | 75  |

| Receiving in 8-Bit or 9-Bit Data Mode 1                    |     |

| Transmitting in 8-Bit Data Mode 1                          | 75  |

| Transmitting in 9-Bit Data Mode 1                          | 75  |

| Universal Asynchronous Receiver                            |     |

| Transmitter (UART) 1                                       | 73  |

| V                                                          |     |

| Voltage Regulator (VREG) 1                                 | 34  |

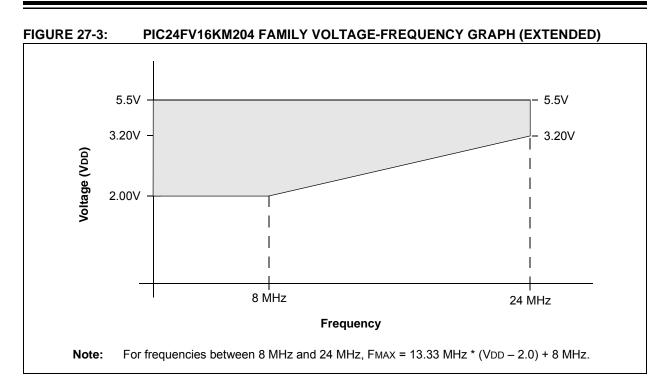

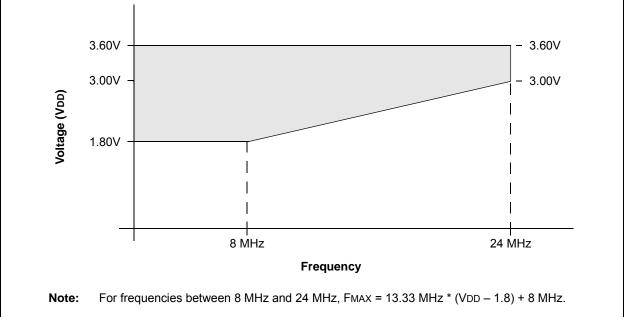

| Voltage-Frequency Graph                                    |     |

| (PIC24F16KM204 Extended) 2                                 | 267 |

| Voltage-Frequency Graph                                    |     |

| (PIC24F16KM204 Industrial) 2                               | 266 |

| Voltage-Frequency Graph                                    |     |

| (PIC24FV16KM204 Extended) 2                                | 267 |

| Voltage-Frequency Graph                                    |     |

| (PIC24FV16KM204 Industrial) 2                              | 266 |

| W                                                          |     |

| Watchdog Timer (WDT) 2                                     | 257 |

|                                                            |     |

| Watchdog Timer (WDT) | 257 |

|----------------------|-----|

| Windowed Operation   | 258 |

| WWW Address          | 332 |

| WWW, On-Line Support | 11  |