Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

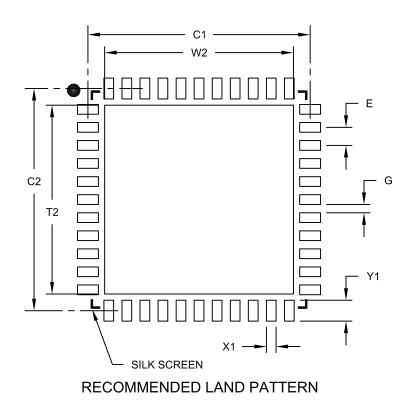

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km102-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-2: DEVICE FEATURES FOR THE PIC24F16KM104 FAMILY

|                                                     |                                                                                                                                                     |                    |                       | 1                                        |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|------------------------------------------|--|--|--|--|

| Features                                            | PIC24F16KM104                                                                                                                                       | PIC24F16KM102      | PIC24F08KM102         | PIC24F08KM101                            |  |  |  |  |

| Operating Frequency                                 | DC-32 MHz                                                                                                                                           |                    |                       |                                          |  |  |  |  |

| Program Memory (bytes)                              | 16K                                                                                                                                                 | 16K                | 8K                    | 8K                                       |  |  |  |  |

| Program Memory (instructions)                       | 5632                                                                                                                                                | 5632               | 2816                  | 2816                                     |  |  |  |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 10                 | 24                    |                                          |  |  |  |  |

| Data EEPROM Memory (bytes)                          |                                                                                                                                                     | 5                  | 12                    |                                          |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)          |                                                                                                                                                     | 25 (2              | 21/4)                 |                                          |  |  |  |  |

| Voltage Range                                       |                                                                                                                                                     | 1.8-               | 3.6V                  |                                          |  |  |  |  |

| I/O Ports                                           | PORTA<11:0><br>PORTB<15:0><br>PORTC<9:0>                                                                                                            | PORTA<br>PORTB     |                       | PORTA<6:0><br>PORTB<15:12,9:7,<br>4,2:0> |  |  |  |  |

| Total I/O Pins                                      | 38                                                                                                                                                  | 24                 | ŀ                     | 18                                       |  |  |  |  |

| Timers                                              | (One 16-bit timer, t                                                                                                                                |                    | 5<br>Ps with up to tv | vo 16/32 timers each)                    |  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                                                                                                                                                     |                    | 1                     |                                          |  |  |  |  |

| Serial Communications<br>MSSP<br>UART               |                                                                                                                                                     |                    | 1                     |                                          |  |  |  |  |

| Input Change Notification Interrupt                 | 37                                                                                                                                                  | 23                 | }                     | 17                                       |  |  |  |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                                                                                                                                  | 19                 | )                     | 16                                       |  |  |  |  |

| Analog Comparators                                  |                                                                                                                                                     |                    | 1                     |                                          |  |  |  |  |

| 8-Bit Digital-to-Analog Converters                  |                                                                                                                                                     | _                  | _                     |                                          |  |  |  |  |

| Operational Amplifiers                              |                                                                                                                                                     | -                  | _                     |                                          |  |  |  |  |

| Charge Time Measurement Unit (CTMU)                 |                                                                                                                                                     | Y                  | es                    |                                          |  |  |  |  |

| Real-Time Clock and Calendar (RTCC)                 |                                                                                                                                                     | -                  | _                     |                                          |  |  |  |  |

| Configurable Logic Cell (CLC)                       |                                                                                                                                                     |                    | 1                     |                                          |  |  |  |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                    |                       |                                          |  |  |  |  |

| Instruction Set                                     | 76 Base Inst                                                                                                                                        | ructions, Multiple | e Addressing N        | Iode Variations                          |  |  |  |  |

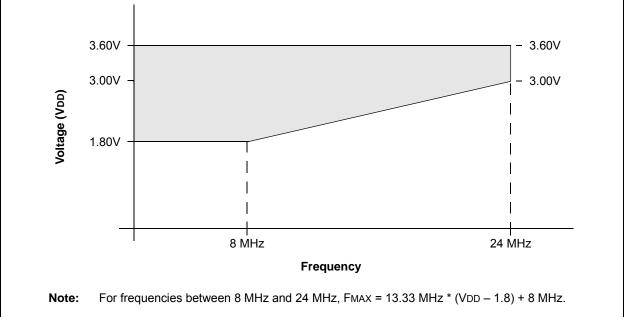

| Packages                                            | 44-Pin<br>QFN/TQFP,<br>48-Pin UQFN                                                                                                                  |                    |                       |                                          |  |  |  |  |

### 2.4 Voltage Regulator Pin (VCAP)

| Note: | This               | section | appli   | ies  | or | to  |      |  |

|-------|--------------------|---------|---------|------|----|-----|------|--|

|       | PIC24F             | V16KM   | devices | with | an | on- | chip |  |

|       | voltage regulator. |         |         |      |    |     |      |  |

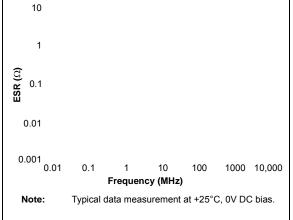

Some of the PIC24FV16KM devices have an internal voltage regulator. These devices have the voltage regulator output brought out on the VCAP pin. On the PIC24F K devices with regulators, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the voltage regulator output. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 27.0** "**Electrical Characteristics**" for additional information. Refer to **Section 27.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

## FIGURE 2-3: FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

### TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range   |

|-----------|--------------------|------------------------|----------------|---------------|---------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

### TABLE 4-4: ICN REGISTER MAP

| File<br>Name | Addr. | Bit 15                   | Bit 14  | Bit 13  | Bit 12                 | Bit 11                   | Bit 10                 | Bit 9                   | Bit 8                    | Bit 7                   | Bit 6   | Bit 5   | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0                    | All<br>Resets |

|--------------|-------|--------------------------|---------|---------|------------------------|--------------------------|------------------------|-------------------------|--------------------------|-------------------------|---------|---------|------------------------|------------------------|------------------------|------------------------|--------------------------|---------------|

| CNPD1        | 56h   | CN15PDE <sup>(1,2)</sup> | CN14PDE | CN13PDE | CN12PDE                | CN11PDE                  | CN10PDE <sup>(2)</sup> | CN9PDE <sup>(1,2)</sup> | —                        | CN7PDE <sup>(1,2)</sup> | CN6PDE  | CN5PDE  | CN4PDE                 | CN3PDE                 | CN2PDE                 | CN1PDE                 | CN0PDE                   | 0000          |

| CNPD2        | 58h   | CN31PDE <sup>(2)</sup>   | CN30PDE | CN29PDE | CN28PDE <sup>(2)</sup> | CN27PDE <sup>(1,2)</sup> | CN26PDE <sup>(2)</sup> | CN25PDE <sup>(2)</sup>  | CN24PDE <sup>(1,2)</sup> | CN23PDE                 | CN22PDE | CN21PDE | CN20PDE <sup>(2)</sup> | CN19PDE <sup>(2)</sup> | CN18PDE <sup>(2)</sup> | CN17PDE <sup>(2)</sup> | CN16PDE <sup>(1,2)</sup> | 0000          |

| CNPD3        | 5Ah   | _                        | _       | _       | _                      | _                        | _                      | _                       | _                        | _                       | _       | _       | CN36PDE <sup>(2)</sup> | CN35PDE <sup>(2)</sup> | CN34PDE <sup>(2)</sup> | CN33PDE <sup>(2)</sup> | CN32PDE <sup>(2)</sup>   | 0000          |

| CNEN1        | 62h   | CN15IE <sup>(1,2)</sup>  | CN14IE  | CN13IE  | CN12IE                 | CN11IE                   | CN10IE <sup>(2)</sup>  | CN9IE <sup>(1,2)</sup>  | _                        | CN7IE <sup>(1,2)</sup>  | CN6IE   | CN5IE   | CN4IE                  | CN3IE                  | CN2IE                  | CN1IE                  | CN0IE                    | 0000          |

| CNEN2        | 64h   | CN31IE <sup>(2)</sup>    | CN30IE  | CN29IE  | CN28IE <sup>(2)</sup>  | CN27IE <sup>(1,2)</sup>  | CN26IE <sup>(2)</sup>  | CN25IE <sup>(2)</sup>   | CN24IE <sup>(1,2)</sup>  | CN23IE                  | CN22IE  | CN21IE  | CN20IE <sup>(2)</sup>  | CN19IE <sup>(2)</sup>  | CN18IE <sup>(2)</sup>  | CN17IE <sup>(2)</sup>  | CN16IE <sup>(1,2)</sup>  | 0000          |

| CNEN3        | 66h   | _                        | -       | _       | _                      | _                        | _                      | _                       | _                        | _                       | _       | _       | CN36IE <sup>(2)</sup>  | CN35IE <sup>(2)</sup>  | CN34IE <sup>(2)</sup>  | CN33IE <sup>(2)</sup>  | CN32IE <sup>(2)</sup>    | 0000          |

| CNPU1        | 6Eh   | CN15PUE <sup>(1,2)</sup> | CN14PUE | CN13PUE | CN12PUE                | CN11PUE                  | CN10PUE <sup>(2)</sup> | CN9PUE <sup>(1,2)</sup> | _                        | CN7PUE <sup>(1,2)</sup> | CN6PUE  | CN5PUE  | CN4PUE                 | CN3PUE                 | CN2PUE                 | CN1PUE                 | CN0PUE                   | 0000          |

| CNPU2        | 70h   | CN31PUE <sup>(2)</sup>   | CN30PUE | CN29PUE | CN28PUE <sup>(2)</sup> | CN27PUE <sup>(1,2)</sup> | CN26PUE <sup>(2)</sup> | CN25PUE <sup>(2)</sup>  | CN24PUE <sup>(1,2)</sup> | CN23PUE                 | CN22PUE | CN21PUE | CN20PUE <sup>(2)</sup> | CN19PUE <sup>(2)</sup> | CN18PUE <sup>(2)</sup> | CN17PUE <sup>(2)</sup> | CN16PUE <sup>(1,2)</sup> | 0000          |

| CNPU3        | 72h   | _                        | _       | _       |                        | _                        | —                      | -                       | _                        | -                       | —       |         | CN36PUE <sup>(2)</sup> | CN35PUE <sup>(2)</sup> | CN34PUE <sup>(2)</sup> | CN33PUE <sup>(2)</sup> | CN32PUE <sup>(2)</sup>   | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on 28-pin devices

2: These bits are available only on 44-pin devices

### TABLE 4-6: TIMER1 REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                                                         | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|----------------------------------------------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TMR1      | 100h  |        | Timer1 Register xx                                             |        |        |        |        |       |       |       |       |       | xxxx  |       |       |       |       |               |

| PR1       | 102h  |        | Timer1 Period Register FFFF                                    |        |        |        |        |       |       |       |       | FFFF  |       |       |       |       |       |               |

| T1CON     | 104h  | TON    | N - TSIDL TECS1 TECS0 - TGATE TCKPS1 TCKPS0 - TSYNC TCS - 0000 |        |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

| Lanandi   |       |        |                                                                |        |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-7: CLC1-2 REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |  |  |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|--|--|

| CLC1CONL                | 122h  | LCEN   | —      | _      | —      | INTP   | INTN   | —     | —     | LCOE  | LCOUT | LCPOL | —     | _     | MODE2 | MODE1 | MODE0 | 0000          |  |  |

| CLC1CONH                | 124h  | _      | _      |        | _      | _      | _      | _     | _     | _     | _     | _     | _     | G4POL | G3POL | G2POL | G1POL | 0000          |  |  |

| CLC1SEL                 | 126h  | _      | DS42   | DS41   | DS40   |        | DS32   | DS31  | DS30  | —     | DS22  | DS21  | DS20  | _     | DS12  | DS11  | DS10  | 0000          |  |  |

| CLC1GLSL                | 12Ah  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |  |  |

| CLC1GLSH                | 12Ch  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |  |  |

| CLC2CONL <sup>(1)</sup> | 12Eh  | LCEN   | _      | -      | _      | INTP   | INTN   | _     | _     | LCOE  | LCOUT | LCPOL | _     | _     | MODE2 | MODE1 | MODE0 | 0000          |  |  |

| CLC2CONH <sup>(1)</sup> | 130h  | —      | —      | _      | —      | _      | _      | —     | _     | _     | _     | _     | —     | G4POL | G3POL | G2POL | G1POL | 0000          |  |  |

| CLC2SEL <sup>(1)</sup>  | 132h  | —      | DS42   | DS41   | DS40   | _      | DS32   | DS31  | DS30  | _     | DS22  | DS21  | DS20  | —     | DS12  | DS11  | DS10  | 0000          |  |  |

| CLC2GLSL <sup>(1)</sup> | 136h  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |  |  |

| CLC2GLSH <sup>(1)</sup> | 138h  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |  |  |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

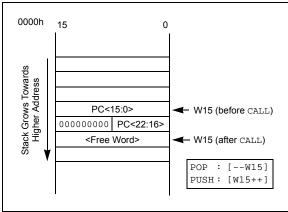

### 4.2.5 SOFTWARE STACK

In addition to its use as a working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as depicted in Figure 4-4.

For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | will concatenate the SRL register to the |  |  |  |  |  |  |

|       | MSB of the PC prior to the push.         |  |  |  |  |  |  |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6 in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit-wide program space and 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the Data Space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

See Table 4-35 and Figure 4-5 to know how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a Data Space word.

### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as displayed in Example 5-5.

| EXAMPLE 5-1: | ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE |

|--------------|-------------------------------------------------------|

|              |                                                       |

| ; Set up NVMCON fo | or row erase operation               |                                     |

|--------------------|--------------------------------------|-------------------------------------|

| MOV #0x            | x4058, WO ;                          |                                     |

| MOV W0,            | , NVMCON ;                           | Initialize NVMCON                   |

| ; Init pointer to  | row to be ERASED                     |                                     |

| MOV #tk            | <pre>blpage(PROG_ADDR), W0 ;</pre>   |                                     |

| MOV W0,            | , TBLPAG ;                           | Initialize PM Page Boundary SFR     |

| MOV #tk            | <pre>bloffset(PROG_ADDR), W0 ;</pre> | Initialize in-page EA[15:0] pointer |

| TBLWTL W0,         | , [WO] ;                             | Set base address of erase block     |

| DISI #5            | ;                                    | Block all interrupts                |

|                    |                                      | for next 5 instructions             |

| MOV #0×            | x55, WO                              |                                     |

| MOV W0,            | , NVMKEY ;                           | Write the 55 key                    |

| MOV #0×            | xAA, W1 ;                            |                                     |

| MOV W1,            | , NVMKEY ;                           | Write the AA key                    |

| BSET NVM           | MCON, #WR ;                          | Start the erase sequence            |

| NOP                | ;                                    | Insert two NOPs after the erase     |

| NOP                | ;                                    | command is asserted                 |

|                    |                                      |                                     |

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

// Variable located in Pgm Memory, declared as a

int __attribute__ ((space(auto_psv))) progAddr = 0x1234;

// global variable

unsigned int offset;

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

__builtin_tblwtl(offset, 0x0000);

// Set base address of erase block

// with dummy latch write

NVMCON = 0 \times 4058;

// Initialize NVMCON

asm("DISI #5");

// Block all interrupts for next 5 instructions

_builtin_write_NVM();

\ensuremath{{//}} C30 function to perform unlock

// sequence and set WR

```

# **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit<br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | SLEEP: Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode                                       |

| bit 2 | IDLE: Wake-up from Idle Flag bit<br>1 = Device has been in Idle mode<br>0 = Device has not been in Idle mode                                           |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred (the BOR is also set after a POR)<br>0 = A Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-on Reset has occurred<br>0 = A Power-on Reset has not occurred                                      |

|       |                                                                                                                                                        |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

### TABLE 7-1: RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

Note: All Reset flag bits may be set or cleared by the user software.

### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| —     | —   | —   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | —     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:       | egend: HS = Hardy                                                                                                 |                                                                                                          | t                      |                    |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------|--------------------|--|--|

| R = Readabl   | e bit                                                                                                             | W = Writable bit                                                                                         | U = Unimplemented bit, | read as '0'        |  |  |

| -n = Value at | POR                                                                                                               | '1' = Bit is set                                                                                         | '0' = Bit is cleared   | x = Bit is unknown |  |  |

| bit 15        | 1 = Interru                                                                                                       | Interrupt Nesting Disable bit<br>Ipt nesting is disabled                                                 |                        |                    |  |  |

| bit 14-5      |                                                                                                                   | ipt nesting is enabled<br>nented: Read as '0'                                                            |                        |                    |  |  |

| bit 4         | MATHERR: Arithmetic Error Trap Status bit<br>1 = Overflow trap has occurred<br>0 = Overflow trap has not occurred |                                                                                                          | bit                    |                    |  |  |

| bit 3         | 1 = Addre                                                                                                         | R: Address Error Trap Status bit<br>ss error trap has occurred<br>ss error trap has not occurred         |                        |                    |  |  |

| bit 2         | 1 = Stack                                                                                                         | Stack Error Trap Status bit<br>error trap has occurred<br>error trap has not occurred                    |                        |                    |  |  |

| bit 1         | 1 = Oscilla                                                                                                       | Oscillator Failure Trap Status t<br>ator failure trap has occurred<br>ator failure trap has not occurred |                        |                    |  |  |

| bit 0         | Unimplen                                                                                                          | nented: Read as '0'                                                                                      |                        |                    |  |  |

| R/W-0, HS       | R/W-0, HS                                                                                  | R/W-0, HS                           | U-0              | U-0              | U-0              | U-0             | R/W-0, HS |

|-----------------|--------------------------------------------------------------------------------------------|-------------------------------------|------------------|------------------|------------------|-----------------|-----------|

| DAC2IF          | DAC1IF                                                                                     | CTMUIF                              | —                |                  | _                |                 | HLVDIF    |

| bit 15          |                                                                                            |                                     |                  |                  |                  |                 | bit 8     |

|                 |                                                                                            |                                     |                  |                  |                  |                 |           |

| U-0             | U-0                                                                                        | U-0                                 | U-0              | U-0              | R/W-0, HS        | R/W-0, HS       | U-0       |

| —               | —                                                                                          | —                                   | _                | —                | U2ERIF           | U1ERIF          | —         |

| bit 7           |                                                                                            |                                     |                  |                  |                  |                 | bit 0     |

|                 |                                                                                            |                                     |                  |                  |                  |                 |           |

| Legend:         |                                                                                            | HS = Hardwar                        | re Settable bit  |                  |                  |                 |           |

| R = Readable    | e bit                                                                                      | W = Writable I                      | oit              | U = Unimpler     | nented bit, read | l as '0'        |           |

| -n = Value at I | POR                                                                                        | '1' = Bit is set                    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | iown      |

|                 |                                                                                            |                                     |                  |                  |                  |                 |           |

| bit 15          | •                                                                                          | tal-to-Analog C                     |                  | rrupt Flag Stat  | us bit           |                 |           |

|                 |                                                                                            | request has occ<br>request has not  |                  |                  |                  |                 |           |

| bit 14          |                                                                                            | •                                   |                  | reunt Flog Stat  | ua hit           |                 |           |

| DIL 14          | •                                                                                          | tal-to-Analog Co<br>request has occ |                  | mupt Flag Stat   |                  |                 |           |

|                 |                                                                                            | request has not                     |                  |                  |                  |                 |           |

| bit 13          |                                                                                            | MU Interrupt Fla                    |                  |                  |                  |                 |           |

|                 |                                                                                            | request has occ                     | •                |                  |                  |                 |           |

|                 | 0 = Interrupt r                                                                            | request has not                     | occurred         |                  |                  |                 |           |

| bit 12-9        | Unimplemen                                                                                 | ted: Read as 'o                     | )'               |                  |                  |                 |           |

| bit 8           | HLVDIF: High                                                                               | n/Low-Voltage D                     | Detect Interrupt | t Flag Status bi | t                |                 |           |

|                 |                                                                                            | request has occ                     |                  |                  |                  |                 |           |

|                 |                                                                                            | request has not                     |                  |                  |                  |                 |           |

| bit 7-3         | -                                                                                          | ted: Read as '0                     |                  |                  |                  |                 |           |

| bit 2           | <b>U2ERIF:</b> UART2 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                     |                  |                  |                  |                 |           |

|                 |                                                                                            | request has occ<br>request has not  |                  |                  |                  |                 |           |

| bit 1           | •                                                                                          | RT1 Error Interro                   |                  | s bit            |                  |                 |           |

|                 |                                                                                            | request has occ                     |                  |                  |                  |                 |           |

|                 |                                                                                            | request has not                     |                  |                  |                  |                 |           |

| bit 0           | Unimplemen                                                                                 | ted: Read as 'o                     | )'               |                  |                  |                 |           |

|                 |                                                                                            |                                     |                  |                  |                  |                 |           |

### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| R-0           | U-0                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0              | R-0              | R-0               | R-0               | R-0              |

|---------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|------------------|

| CPUIRQ        |                     | VHOLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | ILR3             | ILR2              | ILR1              | ILR0             |

| bit 15        |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   | bit 8            |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| U-0           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   | R-0               |                  |

| <br>bit 7     | VECNUM6             | VECNUM5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VECNUM4          | VECNUM3          | VECNUM2           | VECNUM1           | VECNUM0<br>bit 0 |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   | 511 0            |

| Legend:       |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| R = Readable  | e bit               | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit              | U = Unimpler     | nented bit, read  | l as '0'          |                  |

| -n = Value at | POR                 | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | '0' = Bit is cle | ared              | x = Bit is unkr   | nown             |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| bit 15        |                     | errupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                |                  |                   |                   |                  |

|               |                     | upt request have the version of the |                  |                  | been Acknowl      | eagea by the      | CPU (this will   |

|               |                     | upt request is l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                  | (independency)    |                   |                  |