#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

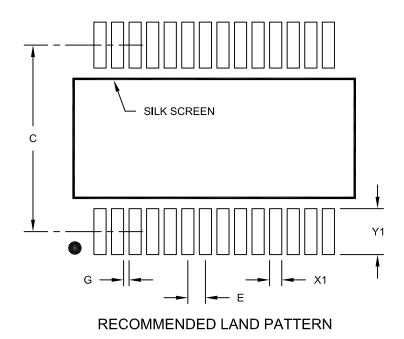

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km102-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Diagrams**

| 20-Pin PDIP/SSOP/SOIC | RA5       1       20       VDD         RA0       2       19       VSs         RA1       3       18       RB15         RB0       4       17       RB14         RB1       5       RB12         RA2       6       9       16         RA3       8       20       15         RB4       9       12       RB8         RA4       10       11       RB7 |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Pin Features                                                         |                                            |  |  |  |  |

|-----|----------------------------------------------------------------------|--------------------------------------------|--|--|--|--|

| Pin | PIC24F08KM101                                                        | PIC24FVKM08KM101                           |  |  |  |  |

| 1   | MCLR/Vpp/RA5                                                         |                                            |  |  |  |  |

| 2   | PGEC2/CVREF+/VREF+/AN0/CN2/RA0                                       |                                            |  |  |  |  |

| 3   | PGED2/CVREF-/VREF-/AN1/CN3/RA1                                       |                                            |  |  |  |  |

| 4   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0                             |                                            |  |  |  |  |

| 5   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                                       |                                            |  |  |  |  |

| 6   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                                        |                                            |  |  |  |  |

| 7   | OSCI/CLKI/AN13/C1INB/CN30/RA2                                        |                                            |  |  |  |  |

| 8   | OSCO/CLKO/AN14/C1INA/CN29/RA3                                        |                                            |  |  |  |  |

| 9   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4                                      |                                            |  |  |  |  |

| 10  | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/                           | RA4                                        |  |  |  |  |

| 11  | AN19/U1TX/CTED1/INT0/CN23/RB7 AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7 |                                            |  |  |  |  |

| 12  | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8                                 |                                            |  |  |  |  |

| 13  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4                          | /CN21/RB9                                  |  |  |  |  |

| 14  | IC1/OC1A/INT2/CN8/RA6                                                | VCAP OR VDDCORE                            |  |  |  |  |

| 15  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12                                | AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |

| 16  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13                                  |                                            |  |  |  |  |

| 17  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RE                        | 814                                        |  |  |  |  |

| 18  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15                                   |                                            |  |  |  |  |

| 19  | Vss/AVss                                                             |                                            |  |  |  |  |

| 20  | Vdd/AVdd                                                             |                                            |  |  |  |  |

| TABLE 1-1: | DEVICE FEATURES FOR THE PIC24F16KM204 FAMILY |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| TABLE 1-1: DEVICE FEATURES FO                    | R THE PIC24F16                                                                                                                                      |                    | •                      |                       |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|-----------------------|--|

| Features                                         | PIC24F16KM204                                                                                                                                       | PIC24F08KM204      | PIC24F16KM202          | PIC24F08KM202         |  |

| Operating Frequency                              |                                                                                                                                                     | DC-3               | 2 MHz                  |                       |  |

| Program Memory (bytes)                           | 16K                                                                                                                                                 | 8K                 | 16K                    | 8K                    |  |

| Program Memory (instructions)                    | 5632                                                                                                                                                | 2816               | 5632                   | 2816                  |  |

| Data Memory (bytes)                              |                                                                                                                                                     | 20                 | )48                    |                       |  |

| Data EEPROM Memory (bytes)                       |                                                                                                                                                     | 5                  | 12                     |                       |  |

| Interrupt Sources (soft vectors/NMI traps)       |                                                                                                                                                     | 40 (               | 36/4)                  |                       |  |

| Voltage Range                                    |                                                                                                                                                     | 1.8-               | 3.6V                   |                       |  |

| I/O Ports                                        | PORTA<<br>PORTB<<br>PORTC                                                                                                                           | :15:0>             | -                      | RTA<7:0><br>RTB<15:0> |  |

| Total I/O Pins                                   | 38                                                                                                                                                  |                    |                        | 24                    |  |

| Timers                                           | (One 16-bit timer, f                                                                                                                                |                    | l1<br>Ps with up to tv | vo 16/32 timers each) |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP      |                                                                                                                                                     |                    | 3<br>2                 |                       |  |

| Serial Communications<br>MSSP<br>UART            |                                                                                                                                                     |                    | 2<br>2                 |                       |  |

| Input Change Notification Interrupt              | 37                                                                                                                                                  |                    |                        | 23                    |  |

| 12-Bit Analog-to-Digital Module (input channels) | 22                                                                                                                                                  | 22                 | 19                     | 19                    |  |

| Analog Comparators                               | 3                                                                                                                                                   |                    |                        |                       |  |

| 8-Bit Digital-to-Analog Converters               | 2                                                                                                                                                   |                    |                        |                       |  |

| Operational Amplifiers                           |                                                                                                                                                     |                    | 2                      |                       |  |

| Charge Time Measurement Unit (CTMU)              |                                                                                                                                                     | Y                  | es                     |                       |  |

| Real-Time Clock and Calendar (RTCC)              |                                                                                                                                                     | Y                  | es                     |                       |  |

| Configurable Logic Cell (CLC)                    |                                                                                                                                                     |                    | 2                      |                       |  |

| Resets (and delays)                              | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                    |                        |                       |  |

| Instruction Set                                  | 76 Base Inst                                                                                                                                        | ructions, Multiple | e Addressing N         | lode Variations       |  |

| Packages                                         | 44-Pin QFN/TQFP,28-Pin48-Pin UQFNSPDIP/SSOP/SOIC/QFN                                                                                                |                    |                        |                       |  |

### TABLE 1-2: DEVICE FEATURES FOR THE PIC24F16KM104 FAMILY

|                                                     |                                                                                                                                                     |                                       |                       | 1                                        |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|------------------------------------------|--|

| Features                                            | PIC24F16KM104                                                                                                                                       | PIC24F16KM102                         | PIC24F08KM102         | PIC24F08KM101                            |  |

| Operating Frequency                                 |                                                                                                                                                     | DC-3                                  | 2 MHz                 |                                          |  |

| Program Memory (bytes)                              | 16K                                                                                                                                                 | 16K                                   | 8K                    | 8K                                       |  |

| Program Memory (instructions)                       | 5632                                                                                                                                                | 5632                                  | 2816                  | 2816                                     |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 10                                    | 24                    |                                          |  |

| Data EEPROM Memory (bytes)                          |                                                                                                                                                     | 5                                     | 12                    |                                          |  |

| Interrupt Sources (soft vectors/NMI traps)          |                                                                                                                                                     | 25 (2                                 | 21/4)                 |                                          |  |

| Voltage Range                                       |                                                                                                                                                     | 1.8-                                  | 3.6V                  |                                          |  |

| I/O Ports                                           | PORTA<11:0><br>PORTB<15:0><br>PORTC<9:0>                                                                                                            | PORTA<br>PORTB                        |                       | PORTA<6:0><br>PORTB<15:12,9:7,<br>4,2:0> |  |

| Total I/O Pins                                      | 38                                                                                                                                                  | 24                                    | ŀ                     | 18                                       |  |

| Timers                                              | (One 16-bit timer, t                                                                                                                                |                                       | 5<br>Ps with up to tv | vo 16/32 timers each)                    |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                                                                                                                                                     |                                       | 1                     |                                          |  |

| Serial Communications<br>MSSP<br>UART               |                                                                                                                                                     |                                       | 1                     |                                          |  |

| Input Change Notification Interrupt                 | 37                                                                                                                                                  | 23                                    | }                     | 17                                       |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                                                                                                                                  | 19                                    | )                     | 16                                       |  |

| Analog Comparators                                  |                                                                                                                                                     |                                       | 1                     |                                          |  |

| 8-Bit Digital-to-Analog Converters                  |                                                                                                                                                     | _                                     | _                     |                                          |  |

| Operational Amplifiers                              |                                                                                                                                                     | -                                     | _                     |                                          |  |

| Charge Time Measurement Unit (CTMU)                 |                                                                                                                                                     | Y                                     | es                    |                                          |  |

| Real-Time Clock and Calendar (RTCC)                 |                                                                                                                                                     | -                                     | _                     |                                          |  |

| Configurable Logic Cell (CLC)                       |                                                                                                                                                     |                                       | 1                     |                                          |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                                       |                       |                                          |  |

| Instruction Set                                     | 76 Base Inst                                                                                                                                        | ructions, Multiple                    | e Addressing N        | Iode Variations                          |  |

| Packages                                            | 44-Pin<br>QFN/TQFP,<br>48-Pin UQFN                                                                                                                  | RN/TQFP, SPDIP/SSOP/SOIC/OFN SOIC/SSO |                       |                                          |  |

NOTES:

## **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit<br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | SLEEP: Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode                                       |

| bit 2 | IDLE: Wake-up from Idle Flag bit<br>1 = Device has been in Idle mode<br>0 = Device has not been in Idle mode                                           |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred (the BOR is also set after a POR)<br>0 = A Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-on Reset has occurred<br>0 = A Power-on Reset has not occurred                                      |

|       |                                                                                                                                                        |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

### TABLE 7-1: RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

Note: All Reset flag bits may be set or cleared by the user software.

| R/W-0, HS                                                                                 | R/W-0, HS                                                                                              | R/W-0, HS                          | U-0              | U-0              | U-0              | U-0             | R/W-0, HS |  |  |  |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------|-----------|--|--|--|

| DAC2IF                                                                                    | DAC1IF                                                                                                 | CTMUIF                             | —                |                  | _                |                 | HLVDIF    |  |  |  |

| bit 15                                                                                    |                                                                                                        |                                    |                  |                  |                  |                 | bit 8     |  |  |  |

|                                                                                           |                                                                                                        |                                    |                  |                  |                  |                 |           |  |  |  |

| U-0                                                                                       | U-0                                                                                                    | U-0                                | U-0              | U-0              | R/W-0, HS        | R/W-0, HS       | U-0       |  |  |  |

| —                                                                                         | —                                                                                                      | —                                  | _                | —                | U2ERIF           | U1ERIF          | —         |  |  |  |

| bit 7                                                                                     |                                                                                                        |                                    |                  |                  |                  |                 | bit 0     |  |  |  |

|                                                                                           |                                                                                                        |                                    |                  |                  |                  |                 |           |  |  |  |

| Legend:                                                                                   |                                                                                                        | HS = Hardwar                       | re Settable bit  |                  |                  |                 |           |  |  |  |

| R = Readable                                                                              | e bit                                                                                                  | W = Writable I                     | oit              | U = Unimpler     | nented bit, read | l as '0'        |           |  |  |  |

| -n = Value at I                                                                           | POR                                                                                                    | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr | iown      |  |  |  |

|                                                                                           |                                                                                                        |                                    |                  |                  |                  |                 |           |  |  |  |

| bit 15                                                                                    | •                                                                                                      | tal-to-Analog C                    |                  | rrupt Flag Stat  | us bit           |                 |           |  |  |  |

|                                                                                           |                                                                                                        | request has occ<br>request has not |                  |                  |                  |                 |           |  |  |  |

| bit 14                                                                                    |                                                                                                        | •                                  |                  | reunt Flog Stat  | ua hit           |                 |           |  |  |  |

| DIL 14                                                                                    | •                                                                                                      | tal-to-Analog Co                   |                  | mupt Flag Stat   |                  |                 |           |  |  |  |

|                                                                                           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                    |                  |                  |                  |                 |           |  |  |  |

| bit 13                                                                                    |                                                                                                        | MU Interrupt Fla                   |                  |                  |                  |                 |           |  |  |  |

|                                                                                           |                                                                                                        | request has occ                    | •                |                  |                  |                 |           |  |  |  |

|                                                                                           | 0 = Interrupt r                                                                                        | request has not                    | occurred         |                  |                  |                 |           |  |  |  |

| bit 12-9                                                                                  | Unimplemented: Read as '0'                                                                             |                                    |                  |                  |                  |                 |           |  |  |  |

| bit 8                                                                                     | HLVDIF: High                                                                                           | n/Low-Voltage D                    | Detect Interrupt | t Flag Status bi | t                |                 |           |  |  |  |

|                                                                                           |                                                                                                        | request has occ                    |                  |                  |                  |                 |           |  |  |  |

|                                                                                           | 0 = Interrupt request has not occurred                                                                 |                                    |                  |                  |                  |                 |           |  |  |  |

| bit 7-3                                                                                   | Unimplemented: Read as '0'                                                                             |                                    |                  |                  |                  |                 |           |  |  |  |

| bit 2 U2ERIF: UART2 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                                                                                        |                                    |                  |                  |                  |                 |           |  |  |  |

|                                                                                           |                                                                                                        | request has occ<br>request has not |                  |                  |                  |                 |           |  |  |  |

| bit 1                                                                                     | •                                                                                                      | •                                  |                  | s bit            |                  |                 |           |  |  |  |

|                                                                                           | <b>U1ERIF:</b> UART1 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred             |                                    |                  |                  |                  |                 |           |  |  |  |

|                                                                                           |                                                                                                        | request has not                    |                  |                  |                  |                 |           |  |  |  |

| bit 0                                                                                     | Unimplemen                                                                                             | ted: Read as 'o                    | )'               |                  |                  |                 |           |  |  |  |

|                                                                                           |                                                                                                        |                                    |                  |                  |                  |                 |           |  |  |  |

### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enable bit<br><u>If FSCM is Enabled (FCKSM1 = 1):</u><br>1 = Clock and PLL selections are locked<br>0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit<br><u>If FSCM is Disabled (FCKSM1 = 0):</u><br>Clock and PLL selections are never locked and may be modified by setting the OSWEN bit. |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                        |

| bit 5   | LOCK: PLL Lock Status bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>1 = PLL module is in lock or PLL module start-up timer is satisfied</li> <li>0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled</li> </ul>                                                                                                                                                                                  |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                        |

| bit 3   | CF: Clock Fail Detect bit                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> </ul>                                                                                                                                                                                                                                                         |

| bit 2   | SOSCDRV: Secondary Oscillator Drive Strength bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = High-power SOSC circuit is selected</li> <li>0 = Low/high-power select is done via the SOSCSRC Configuration bit</li> </ul>                                                                                                                                                                                                                          |

| bit 1   | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>1 = Enables the Secondary Oscillator</li> <li>0 = Disables the Secondary Oscillator</li> </ul>                                                                                                                                                                                                                                                           |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                                                                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = Initiates an oscillator switch to the clock source specified by the NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                                                                                                                                                                                                       |

| Note 1: | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                      |

- 2: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

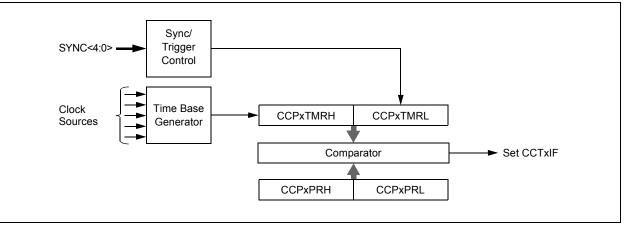

## FIGURE 13-4: 32-BIT TIMER MODE

#### REGISTER 13-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

| R/W-0         | R/W-0                                                                                                                                                                                      | R/W-0                                                                                                                                                                                      | R/W-0                 | U-0              | R/W-0                | R/W-0                  | R/W-0                  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|----------------------|------------------------|------------------------|--|--|--|

| OETRIG        | OSCNT2                                                                                                                                                                                     | OSCNT1                                                                                                                                                                                     | OSCNT0                | _                | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup>   | OUTM0 <sup>(1)</sup>   |  |  |  |

| bit 15        |                                                                                                                                                                                            |                                                                                                                                                                                            |                       |                  |                      |                        | bit 8                  |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

| U-0           | U-0                                                                                                                                                                                        | R/W-0                                                                                                                                                                                      | R/W-0                 | R/W-0            | R/W-0                | R/W-0                  | R/W-0                  |  |  |  |

|               |                                                                                                                                                                                            | POLACE                                                                                                                                                                                     | POLBDF <sup>(1)</sup> | PSSACE1          | PSSACE0              | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> |  |  |  |

| bit 7         |                                                                                                                                                                                            |                                                                                                                                                                                            |                       |                  |                      |                        | bit C                  |  |  |  |

| Legend:       |                                                                                                                                                                                            |                                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

| R = Readabl   | le bit                                                                                                                                                                                     | W = Writable                                                                                                                                                                               | bit                   | U = Unimplen     | nented bit, read     | d as '0'               |                        |  |  |  |

| -n = Value at | POR                                                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                           |                       | '0' = Bit is cle |                      | x = Bit is unkn        | own                    |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            |                       |                  |                      |                        | -                      |  |  |  |

| bit 15        | OETRIG: CC                                                                                                                                                                                 | Px Dead-Time                                                                                                                                                                               | Select bit            |                  |                      |                        |                        |  |  |  |

|               | 1 = For Trigg                                                                                                                                                                              | ered mode (TF                                                                                                                                                                              | RIGEN = 1): Mo        | dule does not    | drive enabled o      | output pins until      | triggered              |  |  |  |

|               |                                                                                                                                                                                            | output pin opera                                                                                                                                                                           |                       |                  |                      |                        |                        |  |  |  |

| bit 14-12     | OSCNT<2:0>                                                                                                                                                                                 | : One-Shot Ev                                                                                                                                                                              | ent Count bits        |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            | nt by 7 time ba       |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            | nt by 6 time ba       |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                            | <ul> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>100 = Extend one-shot event by 4 time base periods (5 time base periods total)</li> </ul> |                       |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

|               | <ul> <li>011 = Extend one-shot event by 3 time base periods (4 time base periods total)</li> <li>010 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> </ul> |                                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

|               | 001 = Extend one-shot event by 1 time base period (2 time base periods total)                                                                                                              |                                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

|               | 000 <b>= Do no</b>                                                                                                                                                                         | t extend one-sl                                                                                                                                                                            | not Trigger ever      | nt               |                      |                        |                        |  |  |  |

| bit 11        | -                                                                                                                                                                                          | ted: Read as '                                                                                                                                                                             |                       |                  |                      |                        |                        |  |  |  |

| bit 10-8      | OUTM<2:0>: PWMx Output Mode Control bits <sup>(1)</sup>                                                                                                                                    |                                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

|               | 111 = Reserv                                                                                                                                                                               |                                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

|               | 110 = Output                                                                                                                                                                               |                                                                                                                                                                                            | 1. f                  |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                            | DC Output mod<br>DC Output mod                                                                                                                                                             |                       |                  |                      |                        |                        |  |  |  |

|               | 011 = Reserv                                                                                                                                                                               | •                                                                                                                                                                                          |                       |                  |                      |                        |                        |  |  |  |

|               | 010 = Half-Br                                                                                                                                                                              | idge Output me                                                                                                                                                                             | ode                   |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                            | Pull Output mod                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

|               | 000 <b>= Steera</b> l                                                                                                                                                                      | ble Single Outp                                                                                                                                                                            | out mode              |                  |                      |                        |                        |  |  |  |

| bit 7-6       | -                                                                                                                                                                                          | ted: Read as '                                                                                                                                                                             |                       |                  |                      |                        |                        |  |  |  |

| bit 5         |                                                                                                                                                                                            | -                                                                                                                                                                                          | s, OCxA, OCxC         | and OCxE, P      | olarity Control      | bit                    |                        |  |  |  |

|               |                                                                                                                                                                                            | in polarity is ac<br>in polarity is ac                                                                                                                                                     |                       |                  |                      |                        |                        |  |  |  |

| bit 4         |                                                                                                                                                                                            |                                                                                                                                                                                            | -                     | and OCxF Po      | plarity Control b    | <sub>Dit</sub> (1)     |                        |  |  |  |

|               | <b>POLBDF:</b> CCPx Output Pins, OCxB, OCxD and OCxF, Polarity Control bit <sup>(1)</sup><br>1 = Output pin polarity is active-low                                                         |                                                                                                                                                                                            |                       |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                            | in polarity is ac                                                                                                                                                                          |                       |                  |                      |                        |                        |  |  |  |

| bit 3-2       | PSSACE<1:0                                                                                                                                                                                 | >: PWMx Outp                                                                                                                                                                               | out Pins, OCxA        | , OCxC and O     | CxE, Shutdowr        | State Control b        | oits                   |  |  |  |

|               | 11 = Pins are                                                                                                                                                                              | driven active v                                                                                                                                                                            | vhen a shutdow        | n event occur    | S                    |                        |                        |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            | when a shutdo         |                  | urs                  |                        |                        |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            | n a shutdown e        |                  |                      |                        | (4)                    |  |  |  |

| bit 1-0       |                                                                                                                                                                                            |                                                                                                                                                                                            |                       |                  |                      | State Control b        | oits <sup>(1)</sup>    |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            | vhen a shutdov        |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                            |                                                                                                                                                                                            | when a shutdo         |                  |                      |                        |                        |  |  |  |

|               | ux = Pins are                                                                                                                                                                              | па пуп-тпре                                                                                                                                                                                | dance state wh        | ien a shuluowi   | i eveni occurs       |                        |                        |  |  |  |

**Note 1:** These bits are implemented in MCCPx modules only.

### REGISTER 15-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0 | R-0, HSC | R-1, HSC |

|----------|--------|----------|-----|-----------|-------|----------|----------|

| UTXISEL1 | UTXINV | UTXISEL0 | —   | UTXBRK    | UTXEN | UTXBF    | TRMT     |

| bit 15   |        |          |     |           |       |          | bit 8    |

| R/W-0       | R/W-0    | R/W-0 | R-1, HSC | R-0, HSC | R-0, HSC | R/C-0, HS | R-0, HSC |  |

|-------------|----------|-------|----------|----------|----------|-----------|----------|--|

| URXISEL1    | URXISEL0 | ADDEN | RIDLE    | PERR     | FERR     | OERR      | URXDA    |  |

| bit 7 bit C |          |       |          |          |          |           |          |  |

| Legend:                           | HC = Hardware Clearable bit |                                       |                    |  |

|-----------------------------------|-----------------------------|---------------------------------------|--------------------|--|

| HS = Hardware Settable bit        | C = Clearable bit           | HSC = Hardware Settable/Clearable bit |                    |  |

| R = Readable bit W = Writable bit |                             | U = Unimplemented bit, read as '0'    |                    |  |

| -n = Value at POR                 | '1' = Bit is set            | '0' = Bit is cleared                  | x = Bit is unknown |  |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit

| bit 14  | UTXINV: IrDA <sup>®</sup> Encoder Transmit Polarity Inversion bit                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If IREN = 0:</u>                                                                                                                                                                                                      |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                        |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                        |

|         | <u>If IREN = 1:</u>                                                                                                                                                                                                      |

|         | 1 = UxTX Idle '1'                                                                                                                                                                                                        |

|         | 0 = UxTX Idle '0'                                                                                                                                                                                                        |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                               |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                                                                         |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul>                                                    |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                                                                     |

| bit 10  | UTXEN: UARTx Transmit Enable bit                                                                                                                                                                                         |

|         | <ul> <li>1 = Transmit is enabled; UxTX pin is controlled by UARTx</li> <li>0 = Transmit is disabled; any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by the PORT register</li> </ul> |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                                                                 |

|         | 1 = Transmit buffer is full                                                                                                                                                                                              |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                              |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                      |

|         | <ul> <li>1 = Transmit Shift Register is empty and the transmit buffer is empty (the last transmission has<br/>completed)</li> </ul>                                                                                      |

|         | 0 = Transmit Shift Register is not empty; a transmission is in progress or queued                                                                                                                                        |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                |

|         | 11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)                                                                                                                   |

|         | 10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)                                                                                                               |

|         | 0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters                                                                       |

|         |                                                                                                                                                                                                                          |

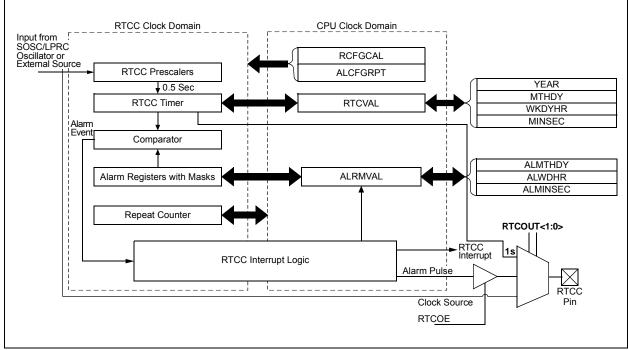

## 16.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Sleep and Retention Sleep modes

- · Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

## 16.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

## FIGURE 16-1: RTCC BLOCK DIAGRAM

NOTES:

| R/W-0         | R/W-0                                                                                               | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|

| CH0NB2        | CH0NB1                                                                                              | CH0NB0                               | CH0SB4         | CH0SB3            | CH0SB2           | CH0SB1          | CH0SB0 |  |  |  |  |  |

| bit 15        |                                                                                                     |                                      |                |                   |                  |                 | bit    |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                               | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |