#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

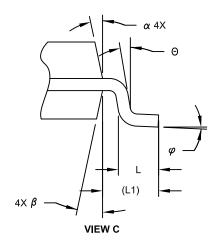

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km102-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-2: DEVICE FEATURES FOR THE PIC24F16KM104 FAMILY

|                                                     |                                                                                                                                                     |                    |                       | 1                                        |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|------------------------------------------|--|

| Features                                            | PIC24F16KM104                                                                                                                                       | PIC24F16KM102      | PIC24F08KM102         | PIC24F08KM101                            |  |

| Operating Frequency                                 |                                                                                                                                                     | DC-3               | 2 MHz                 |                                          |  |

| Program Memory (bytes)                              | 16K                                                                                                                                                 | 16K                | 8K                    | 8K                                       |  |

| Program Memory (instructions)                       | 5632                                                                                                                                                | 5632               | 2816                  | 2816                                     |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 10                 | 24                    |                                          |  |

| Data EEPROM Memory (bytes)                          |                                                                                                                                                     | 5                  | 12                    |                                          |  |

| Interrupt Sources (soft vectors/NMI traps)          |                                                                                                                                                     | 25 (2              | 21/4)                 |                                          |  |

| Voltage Range                                       |                                                                                                                                                     | 1.8-               | 3.6V                  |                                          |  |

| I/O Ports                                           | PORTA<11:0><br>PORTB<15:0><br>PORTC<9:0>                                                                                                            | PORTA<br>PORTB     |                       | PORTA<6:0><br>PORTB<15:12,9:7,<br>4,2:0> |  |

| Total I/O Pins                                      | 38                                                                                                                                                  | 24                 | ŀ                     | 18                                       |  |

| Timers                                              | (One 16-bit timer, t                                                                                                                                |                    | 5<br>Ps with up to tv | vo 16/32 timers each)                    |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                                                                                                                                                     |                    | 1                     |                                          |  |

| Serial Communications<br>MSSP<br>UART               |                                                                                                                                                     |                    | 1                     |                                          |  |

| Input Change Notification Interrupt                 | 37                                                                                                                                                  | 23                 | }                     | 17                                       |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                                                                                                                                  | 19                 | )                     | 16                                       |  |

| Analog Comparators                                  |                                                                                                                                                     |                    | 1                     |                                          |  |

| 8-Bit Digital-to-Analog Converters                  |                                                                                                                                                     | _                  | _                     |                                          |  |

| Operational Amplifiers                              |                                                                                                                                                     | -                  | _                     |                                          |  |

| Charge Time Measurement Unit (CTMU)                 |                                                                                                                                                     | Y                  | es                    |                                          |  |

| Real-Time Clock and Calendar (RTCC)                 |                                                                                                                                                     | -                  | _                     |                                          |  |

| Configurable Logic Cell (CLC)                       |                                                                                                                                                     |                    | 1                     |                                          |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                    |                       |                                          |  |

| Instruction Set                                     | 76 Base Inst                                                                                                                                        | ructions, Multiple | e Addressing N        | Iode Variations                          |  |

| Packages                                            | 44-Pin<br>QFN/TQFP,<br>48-Pin UQFN                                                                                                                  | 28-F<br>SPDIP/SSOP |                       | 20-Pin<br>SOIC/SSOP/PDIP                 |  |

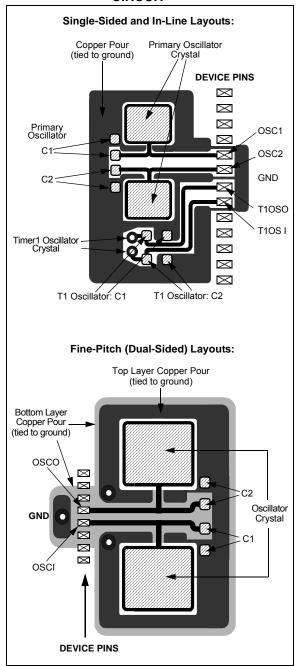

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to for **Section 9.0 "Oscillator Configuration**" details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals, in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

### FIGURE 2-5: SU

### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

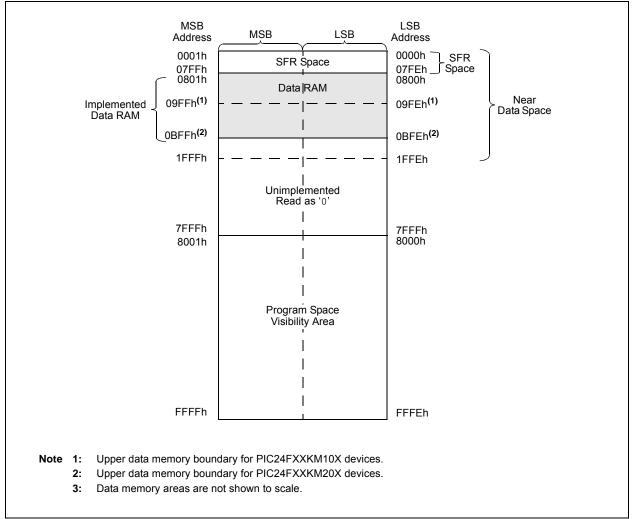

#### 4.2 **Data Address Space**

The PIC24F core has a separate, 16-bit-wide data memory space, addressable as a single linear range. The Data Space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The Data Space memory map is displayed in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This gives a Data Space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility").

Depending on the particular device, PIC24FV16KM family devices implement either 512 or 1024 words of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

FIGURE 4-3:

#### 4.2.1 DATA SPACE WIDTH

The data organized memory space is in byte-addressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all the Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

DATA SPACE MEMORY MAP FOR PIC24FXXXXX FAMILY DEVICES<sup>(3)</sup>

| REGISTER      |                                                                     |                                                                                         |                    | KI CONTRO        | LREGISTE       | ĸ              |        |  |  |

|---------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|------------------|----------------|----------------|--------|--|--|

| R/SO-0, HC    | R/W-0                                                               | R/W-0                                                                                   | R/W-0              | U-0              | U-0            | U-0            | U-0    |  |  |

| WR            | WREN                                                                | WRERR                                                                                   | PGMONLY            | _                | _              | —              | _      |  |  |

| bit 15        | •                                                                   |                                                                                         |                    | ·                |                |                | bit 8  |  |  |

|               |                                                                     |                                                                                         |                    |                  |                |                |        |  |  |

| U-0           | R/W-0                                                               | R/W-0                                                                                   | R/W-0              | R/W-0            | R/W-0          | R/W-0          | R/W-0  |  |  |

| _             | ERASE                                                               | NVMOP5                                                                                  | NVMOP4             | NVMOP3           | NVMOP2         | NVMOP1         | NVMOP0 |  |  |

| bit 7         |                                                                     |                                                                                         |                    |                  |                |                | bit 0  |  |  |

|               |                                                                     |                                                                                         |                    |                  |                |                |        |  |  |

| Legend:       |                                                                     | HC = Hardware                                                                           | Clearable bit      | U = Unimple      | mented bit, re | ead as '0'     |        |  |  |

| R = Readable  | bit                                                                 | W = Writable bit                                                                        |                    | S = Settable     | Only bit       |                |        |  |  |

| -n = Value at | POR                                                                 | '1' = Bit is set                                                                        |                    | '0' = Bit is cle | eared          | x = Bit is unk | nown   |  |  |

| bit 15        |                                                                     | ontrol bit (program<br>a data EEPROM e                                                  |                    | cle (can be set  | . but not clea | red in softwar | e)     |  |  |

|               |                                                                     | le is complete (cle                                                                     |                    |                  |                |                | -,     |  |  |

| bit 14        | WREN: Write                                                         | Enable bit (erase                                                                       | or program)        |                  |                |                |        |  |  |

|               | 1 = Enables an erase or program operation                           |                                                                                         |                    |                  |                |                |        |  |  |

|               | 0 = No operat                                                       | tion allowed (devic                                                                     | ce clears this bit | on completion    | of the write/e | erase operatio | on)    |  |  |

| bit 13        |                                                                     | sh Error Flag bit                                                                       |                    |                  |                |                |        |  |  |

|               |                                                                     | = A write operation is prematurely terminated (any MCLR or WDT Reset during programming |                    |                  |                |                |        |  |  |

|               | operation<br>0 = The write                                          | )<br>operation comple                                                                   | eted successfully  | /                |                |                |        |  |  |

| bit 12        |                                                                     | Program Only Enal                                                                       | ,                  | ,                |                |                |        |  |  |

| 511 12        |                                                                     | eration is executed                                                                     |                    | a target addres  | s(es) first    |                |        |  |  |

|               |                                                                     | c erase-before-wr                                                                       | -                  | ,                | -()            |                |        |  |  |

|               | Write operation                                                     | ons are preceded                                                                        | automatically by   | an erase of th   | e target addr  | ess(es).       |        |  |  |

| bit 11-7      | Unimplemen                                                          | ted: Read as '0'                                                                        |                    |                  |                |                |        |  |  |

| bit 6         |                                                                     | e Operation Selec                                                                       |                    |                  |                |                |        |  |  |

|               |                                                                     | an erase operation                                                                      |                    |                  |                |                |        |  |  |

|               |                                                                     | a write operation                                                                       |                    |                  |                |                |        |  |  |

| bit 5-0       | NVMOP<5:0>: Programming Operation Command Byte bits                 |                                                                                         |                    |                  |                |                |        |  |  |

|               | Erase Operations (when ERASE bit is '1'):<br>011010 = Erase 8 words |                                                                                         |                    |                  |                |                |        |  |  |

|               | 011001 = Era                                                        |                                                                                         |                    |                  |                |                |        |  |  |

|               | 011000 = Era                                                        |                                                                                         |                    |                  |                |                |        |  |  |

|               |                                                                     | ase entire data EE                                                                      | -                  |                  |                |                |        |  |  |

|               | • •                                                                 | Operations (when                                                                        | n ERASE bit is '   | <u>0'):</u>      |                |                |        |  |  |

|               | 0001xx = Wr                                                         | ite 1 word                                                                              |                    |                  |                |                |        |  |  |

|               |                                                                     |                                                                                         |                    |                  |                |                |        |  |  |

### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| —     | —   | —   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | —     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:       |                              | HS = Hardware Settable bi                                                                                | t                      |                    |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------|------------------------|--------------------|

| R = Readabl   | e bit                        | W = Writable bit                                                                                         | U = Unimplemented bit, | read as '0'        |

| -n = Value at | POR                          | '1' = Bit is set                                                                                         | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15        | 1 = Interru                  | Interrupt Nesting Disable bit<br>Ipt nesting is disabled                                                 |                        |                    |

| bit 14-5      |                              | ipt nesting is enabled<br>nented: Read as '0'                                                            |                        |                    |

| bit 4         | <b>MATHERI</b><br>1 = Overfl | R: Arithmetic Error Trap Status t<br>ow trap has occurred<br>ow trap has not occurred                    | bit                    |                    |

| bit 3         | 1 = Addre                    | R: Address Error Trap Status bit<br>ss error trap has occurred<br>ss error trap has not occurred         |                        |                    |

| bit 2         | 1 = Stack                    | Stack Error Trap Status bit<br>error trap has occurred<br>error trap has not occurred                    |                        |                    |

| bit 1         | 1 = Oscilla                  | Oscillator Failure Trap Status t<br>ator failure trap has occurred<br>ator failure trap has not occurred |                        |                    |

| bit 0         | Unimplen                     | nented: Read as '0'                                                                                      |                        |                    |

### REGISTER 8-33: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0           | U-0        | U-0              | U-0          | U-0               | U-0              | U-0             | U-0      |

|---------------|------------|------------------|--------------|-------------------|------------------|-----------------|----------|

| —             | —          | —                | —            | —                 | —                | —               | —        |

| bit 15        |            |                  |              |                   |                  |                 | bit 8    |

|               |            |                  |              |                   |                  |                 |          |

| U-0           | U-0        | U-0              | U-0          | U-0               | R/W-1            | R/W-0           | R/W-0    |

| _             | _          | _                | _            | —                 | ULPWUIP2         | ULPWUIP1        | ULPWUIP0 |

| bit 7         |            |                  |              |                   |                  |                 | bit 0    |

| Legend:       |            |                  |              |                   |                  |                 |          |

| R = Readable  | e bit      | W = Writable     | bit          | U = Unimplem      | nented bit, read | l as '0'        |          |

| -n = Value at | POR        | '1' = Bit is set |              | '0' = Bit is clea | ared             | x = Bit is unkr | iown     |

|               |            |                  |              |                   |                  |                 |          |

| bit 15-3      | Unimplemer | ted: Read as '0  | )'           |                   |                  |                 |          |

| bit 2-0       | ULPWUIP<2  | :0>: Ultra Low-F | Power Wake-u | p Interrupt Prior | rity bits        |                 |          |

111 = Interrupt is Priority 7 (highest priority interrupt)

- •

- 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### REGISTER 8-34: IPC24: INTERRUPT PRIORITY CONTROL REGISTER 24

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | CLC2IP2 | CLC2IP1 | CLC2IP0 | —   | CLC1IP2 | CLC1IP1 | CLC1IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-7 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 6-4  | CLC2IP<2:0>: CLC2 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

| bit 3    | Unimplemented: Read as '0'                                 |

| bit 2-0  | CLC1IP<2:0>: CLC1 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

|          |                                                            |

| U-0             | U-0                | U-0                 | U-0                       | U-0                 | U-0                 | U-0                 | U-0                 |

|-----------------|--------------------|---------------------|---------------------------|---------------------|---------------------|---------------------|---------------------|

|                 | —                  | —                   | —                         | —                   | —                   | —                   | —                   |

| bit 15          |                    |                     |                           |                     |                     |                     | bit 8               |

|                 |                    |                     |                           |                     |                     |                     |                     |

| U-0             | U-0                | R/W-0               | R/W-0                     | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

| —               | —                  | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>       | TUN3 <sup>(1)</sup> | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| bit 7           |                    |                     |                           |                     |                     |                     | bit 0               |

|                 |                    |                     |                           |                     |                     |                     |                     |

| Legend:         |                    |                     |                           |                     |                     |                     |                     |

| R = Readable    | bit                | W = Writable        | bit                       | U = Unimplem        | nented bit, read    | l as '0'            |                     |

| -n = Value at l | POR                | '1' = Bit is set    |                           | '0' = Bit is clea   | ared                | x = Bit is unkn     | nown                |

|                 |                    |                     |                           |                     |                     |                     |                     |

| bit 15-6        | Unimplement        | ted: Read as 'd     | )'                        |                     |                     |                     |                     |

| bit 5-0         | TUN<5:0>: FI       | RC Oscillator T     | uning bits <sup>(1)</sup> |                     |                     |                     |                     |

|                 |                    | ximum frequen       | cy deviation              |                     |                     |                     |                     |

|                 | 011110             |                     |                           |                     |                     |                     |                     |

|                 | •                  |                     |                           |                     |                     |                     |                     |

|                 | •                  |                     |                           |                     |                     |                     |                     |

|                 | 000001             |                     |                           |                     |                     |                     |                     |

|                 | 000000 <b>= Ce</b> | nter frequency,     | oscillator is ru          | nning at factory    | calibrated free     | quency              |                     |

|                 | 111111             |                     |                           |                     |                     |                     |                     |

|                 | •                  |                     |                           |                     |                     |                     |                     |

|                 | •                  |                     |                           |                     |                     |                     |                     |

|                 | 100001             |                     |                           |                     |                     |                     |                     |

|                 |                    | nimum frequen       | cv deviation              |                     |                     |                     |                     |

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

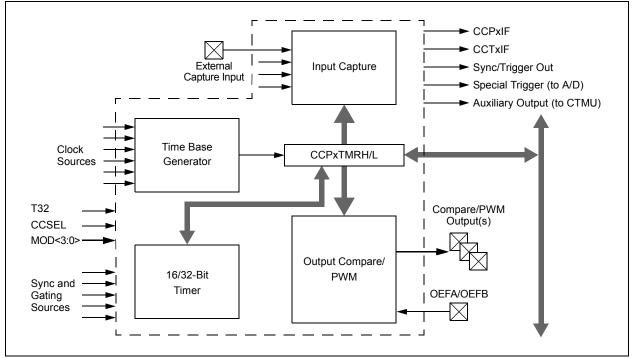

### 13.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive refer-      |

|       | ence source. For more information on the   |

|       | MCCP/SCCP modules, refer to the            |

|       | "PIC24F Family Reference Manual".          |

PIC24FV16KM204 family devices include several Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals of earlier PIC24F devices. The module can operate in one of three major modes:

- General Purpose Timer

- Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single output modules (SCCPs) provide only one PWM output. Multiple output modules (MCCPs) can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical.

The SCCP and MCCP modules can be operated only in one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode. A conceptual block diagram for the module is shown in Figure 13-1. All three modes share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of seven control and status registers:

- CCPxCON1L (Register 13-1)

- CCPxCON1H (Register 13-2)

- CCPxCON2L (Register 13-3)

- CCPxCON2H (Register 13-4)

- CCPxCON3L (Register 13-5)

- CCPxCON3H (Register 13-6)

- CCPxSTATL (Register 13-7)

Each module also includes eight buffer/counter registers that serve as Timer Value registers or data holding buffers:

- CCPxTMRH/CCPxTMRL (Timer High/Low Counters)

- CCPxPRH/CCPxPRL (Timer Period High/Low)

- CCPxRA (Primary Output Compare Data Buffer)

- CCPxRB (Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (Input Capture High/Low Buffers)

### FIGURE 13-1: MCCPx/SCCPx CONCEPTUAL BLOCK DIAGRAM

| SYNC<4:0>             | Synchronization Source                                     |  |  |  |  |

|-----------------------|------------------------------------------------------------|--|--|--|--|

| 00000                 | None; Timer with Rollover on CCPxPR Match or FFFFh         |  |  |  |  |

| 00001                 | MCCP1 or SCCP1 Sync Output                                 |  |  |  |  |

| 00010                 | MCCP2 or SCCP2 Sync Output                                 |  |  |  |  |

| 00011                 | MCCP3 or SCCP3 Sync Output                                 |  |  |  |  |

| 00100                 | MCCP4 or SCCP4 Sync Output                                 |  |  |  |  |

| 00101                 | MCCP5 or SCCP5 Sync Output                                 |  |  |  |  |

| 00110 <b>to</b> 01010 | Unused                                                     |  |  |  |  |

| 01011                 | Timer1 Sync Output <sup>(1)</sup>                          |  |  |  |  |

| 01100 <b>to</b> 10000 | Unused                                                     |  |  |  |  |

| 10001                 | CLC1 Output <sup>(1)</sup>                                 |  |  |  |  |

| 10010                 | CLC2 Output <sup>(1)</sup>                                 |  |  |  |  |

| 10011 <b>to</b> 11010 | Unused                                                     |  |  |  |  |

| 11011                 | A/D <sup>(1)</sup>                                         |  |  |  |  |

| 11110                 | Unused                                                     |  |  |  |  |

| 11111                 | None; Timer with Auto-Rollover (FFFFh $\rightarrow$ 0000h) |  |  |  |  |

### TABLE 13-6: SYNCHRONIZATION SOURCES

Note 1: These sources are only available when the source module is being used in a Synchronous mode.

### REGISTER 14-5: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0        | U-0                                                                   | U-0                                                                      | U-0                  | U-0                     | U-0                | U-0                 | U-0                |  |  |  |

|------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------|-------------------------|--------------------|---------------------|--------------------|--|--|--|

| _          |                                                                       | _                                                                        |                      |                         | _                  | —                   |                    |  |  |  |

| bit 15     |                                                                       |                                                                          |                      |                         |                    |                     | bit 8              |  |  |  |

|            |                                                                       |                                                                          |                      |                         |                    |                     |                    |  |  |  |

| R/W-0      | R/W-0                                                                 | R/W-0                                                                    | R/W-0                | R/W-0                   | R/W-0              | R/W-0               | R/W-0              |  |  |  |

| GCEN       | ACKSTAT                                                               | ACKDT <sup>(1)</sup>                                                     | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>     | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |  |  |  |

| bit 7      |                                                                       |                                                                          |                      |                         |                    |                     | bit (              |  |  |  |

| Legend:    |                                                                       |                                                                          |                      |                         |                    |                     |                    |  |  |  |

| R = Reada  | able bit                                                              | W = Writable                                                             | bit                  | U = Unimplem            | nented bit, read   | d as '0'            |                    |  |  |  |

| -n = Value |                                                                       | '1' = Bit is set                                                         |                      | '0' = Bit is clea       |                    | x = Bit is unkn     | lown               |  |  |  |

|            |                                                                       | 1 Bit io oot                                                             |                      | o Bit io olot           |                    |                     |                    |  |  |  |

| bit 15-8   | Unimplemen                                                            | ted: Read as '                                                           | 0'                   |                         |                    |                     |                    |  |  |  |

| bit 7      | GCEN: Gene                                                            | eral Call Enable                                                         | bit (Slave mod       | e only)                 |                    |                     |                    |  |  |  |

|            |                                                                       | interrupt when a call address is o                                       | 0                    | ddress (0000h)          | is received in     | the SSPxSR          |                    |  |  |  |

| bit 6      |                                                                       | cknowledge Sta                                                           |                      | Transmit mode           | ≏ onlv)            |                     |                    |  |  |  |

|            |                                                                       | edge was not re                                                          |                      |                         | c only)            |                     |                    |  |  |  |

|            |                                                                       | edge was receiv                                                          |                      |                         |                    |                     |                    |  |  |  |

| bit 5      | ACKDT: Acknowledge Data bit (Master Receive mode only) <sup>(1)</sup> |                                                                          |                      |                         |                    |                     |                    |  |  |  |

|            | 1 = No Ackno                                                          | owledge                                                                  |                      |                         |                    |                     |                    |  |  |  |

|            | 0 = Acknowle                                                          | •                                                                        |                      |                         |                    |                     |                    |  |  |  |

| bit 4      |                                                                       | ACKEN: Acknowledge Sequence Enable bit (Master mode only) <sup>(2)</sup> |                      |                         |                    |                     |                    |  |  |  |

|            |                                                                       |                                                                          |                      | SDAx and SC             | CLx pins and       | transmits ACI       | KDT data bit       |  |  |  |

|            |                                                                       | ically cleared by<br>edge sequence                                       |                      |                         |                    |                     |                    |  |  |  |

| bit 3      |                                                                       | ive Enable bit (                                                         |                      | mode only)(2)           |                    |                     |                    |  |  |  |

| bit 0      |                                                                       | Receive mode f                                                           | -                    | , mode only)            |                    |                     |                    |  |  |  |

|            | 0 = Receive i                                                         |                                                                          |                      |                         |                    |                     |                    |  |  |  |

| bit 2      | PEN: Stop Co                                                          | ondition Enable                                                          | bit (Master mo       | de only) <sup>(2)</sup> |                    |                     |                    |  |  |  |

|            |                                                                       | Stop condition c                                                         | n SDAx and SO        | CLx pins; auton         | natically cleare   | ed by hardware      |                    |  |  |  |

|            | 0 = Stop cond                                                         |                                                                          |                      |                         | (0)                |                     |                    |  |  |  |

| bit 1      | -                                                                     | ated Start Cond                                                          |                      | -                       |                    |                     |                    |  |  |  |

|            |                                                                       | Repeated Start<br>d Start conditio                                       |                      | DAx and SCLx            | pins; automati     | ically cleared by   | / hardware         |  |  |  |

| bit 0      | -                                                                     | ondition Enable                                                          |                      |                         |                    |                     |                    |  |  |  |

|            | Master Mode                                                           |                                                                          | DIC                  |                         |                    |                     |                    |  |  |  |

|            |                                                                       | <u></u><br>Start condition c                                             | on SDAx and S        | CLx pins: autor         | natically cleare   | ed by hardware      |                    |  |  |  |

|            | 0 = Start con                                                         |                                                                          |                      |                         |                    |                     |                    |  |  |  |

|            | Slave Mode:                                                           |                                                                          |                      |                         |                    |                     |                    |  |  |  |

|            |                                                                       | etching is enabl<br>etching is disab                                     |                      | ve transmit and         | slave receive      | (stretch is enab    | oled)              |  |  |  |

| Note 1:    | The value that wi                                                     | ill be transmitte                                                        | d when the use       | r initiates an Ao       | cknowledge se      | equence at the e    | end of a           |  |  |  |

|            |                                                                       |                                                                          |                      |                         |                    |                     |                    |  |  |  |

| 2:         | receive.<br>If the I <sup>2</sup> C module                            |                                                                          | 1.10                 |                         |                    |                     |                    |  |  |  |

| U-0           | U-0                                                                                                                                                                                                                     | U-0                | U-0                            | U-0                          | U-0               | U-0             | U-0           |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------|------------------------------|-------------------|-----------------|---------------|--|--|--|

| _             | —                                                                                                                                                                                                                       | _                  | _                              | —                            | —                 | —               | —             |  |  |  |

| bit 15        | •                                                                                                                                                                                                                       |                    |                                | ·                            |                   | ·               | bit           |  |  |  |

| DA            |                                                                                                                                                                                                                         |                    |                                |                              |                   |                 |               |  |  |  |

| R-0<br>ACKTIM | R/W-0<br>PCIE                                                                                                                                                                                                           | R/W-0<br>SCIE      | R/W-0<br>BOEN <sup>(1)</sup>   | R/W-0<br>SDAHT               | R/W-0<br>SBCDE    | R/W-0<br>AHEN   | R/W-0<br>DHEN |  |  |  |

| bit 7         | FUE                                                                                                                                                                                                                     | SUE                | BOEIN',                        | SDATI                        | SECDE             | ALEN            | bit           |  |  |  |

|               |                                                                                                                                                                                                                         |                    |                                |                              |                   |                 | bit           |  |  |  |

| Legend:       |                                                                                                                                                                                                                         |                    |                                |                              |                   |                 |               |  |  |  |

| R = Readabl   | le bit                                                                                                                                                                                                                  | W = Writable       | bit                            | U = Unimplem                 | nented bit, read  | 1 as '0'        |               |  |  |  |

| -n = Value at | t POR                                                                                                                                                                                                                   | '1' = Bit is set   |                                | '0' = Bit is clea            | ared              | x = Bit is unkn | own           |  |  |  |

|               |                                                                                                                                                                                                                         |                    |                                |                              |                   |                 |               |  |  |  |

| bit 15-8      | -                                                                                                                                                                                                                       | ted: Read as '     |                                |                              |                   |                 |               |  |  |  |

| bit 7         | ACKTIM: Acknowledge Time Status bit (I <sup>2</sup> C™ mode only)                                                                                                                                                       |                    |                                |                              |                   |                 |               |  |  |  |

|               | Unused in SPI mode.                                                                                                                                                                                                     |                    |                                |                              |                   |                 |               |  |  |  |

| bit 6         | PCIE: Stop Condition Interrupt Enable bit (I <sup>2</sup> C mode only)                                                                                                                                                  |                    |                                |                              |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                            |                    |                                | •                            |                   |                 |               |  |  |  |

| bit 5         |                                                                                                                                                                                                                         |                    | ipt Enable bit (I              | <sup>2</sup> C mode only)    |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                            |                    | (1)                            |                              |                   |                 |               |  |  |  |

| bit 4         |                                                                                                                                                                                                                         | r Overwrite Ena    | able bit <sup>(1)</sup>        |                              |                   |                 |               |  |  |  |

|               |                                                                                                                                                                                                                         | In SPI Slave mode: |                                |                              |                   |                 |               |  |  |  |

|               | <ul> <li>1 = SSPxBUF updates every time that a new data byte is shifted in, ignoring the BF bit</li> <li>0 = If a new byte is received with the BF bit of the SSPxSTAT register already set, the SSPOV bit o</li> </ul> |                    |                                |                              |                   |                 |               |  |  |  |

|               |                                                                                                                                                                                                                         |                    |                                | buffer is not up             |                   |                 |               |  |  |  |

| bit 3         | SDAHT: SDA                                                                                                                                                                                                              | x Hold Time Se     | election bit (I <sup>2</sup> C | mode only)                   |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                            | l mode.            |                                |                              |                   |                 |               |  |  |  |

| bit 2         | SBCDE: Slav                                                                                                                                                                                                             | ve Mode Bus C      | ollision Detect                | Enable bit (I <sup>2</sup> C | Slave mode or     | ıly)            |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                            | l mode.            |                                |                              |                   |                 |               |  |  |  |

| bit 1         | AHEN: Addre                                                                                                                                                                                                             | ess Hold Enabl     | e bit (l <sup>2</sup> C Slave  | mode only)                   |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                            | l mode.            |                                |                              |                   |                 |               |  |  |  |

| bit 0         | DHEN: Data                                                                                                                                                                                                              | Hold Enable bi     | t (Slave mode o                | only)                        |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                            | Pl mode.           |                                |                              |                   |                 |               |  |  |  |

| Note 1: F     | or Daisy-Chaine                                                                                                                                                                                                         | ed SPI Operatio    | on: Allows the u               | iser to ignore al            | I but the last re | ceived byte S   | SDUV is still |  |  |  |

### REGISTER 14-6: SSPxCON3: MSSPx CONTROL REGISTER 3 (SPI MODE)

**Note 1:** For Daisy-Chained SPI Operation: Allows the user to ignore all but the last received byte. SSPOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSPxBUF.

| R/W-0         | U-0                                                                   | R/W-0                                                               | R/W-0                         | R/W-0                                      | U-0                                        | R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup> |

|---------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------|--------------------------------------------|--------------------------------------------|----------------------|----------------------|

| UARTEN        | —                                                                     | USIDL                                                               | IREN <sup>(1)</sup>           | RTSMD                                      | _                                          | UEN1                 | UEN0                 |

| bit 15        |                                                                       |                                                                     |                               |                                            |                                            |                      | bit 8                |

| R/C-0, HC     | R/W-0                                                                 | R/W-0, HC                                                           | R/W-0                         | R/W-0                                      | R/W-0                                      | R/W-0                | R/W-0                |

| WAKE          | LPBACK                                                                | ABAUD                                                               | URXINV                        | BRGH                                       | PDSEL1                                     | PDSEL0               | STSEL                |

| bit 7         | LI DAOR                                                               |                                                                     | UIXIIIV                       | BRGH                                       | TDSELT                                     | T DOLLO              | bit 0                |

|               |                                                                       |                                                                     |                               |                                            |                                            |                      |                      |

| Legend:       |                                                                       | C = Clearable                                                       |                               |                                            | are Clearable bi                           |                      |                      |

| R = Readabl   |                                                                       | W = Writable                                                        | oit                           |                                            | mented bit, read                           |                      |                      |

| -n = Value at | POR                                                                   | '1' = Bit is set                                                    |                               | '0' = Bit is cle                           | ared                                       | x = Bit is unkn      | iown                 |

| bit 15        | UARTEN: UA                                                            | ARTx Enable bit                                                     |                               |                                            |                                            |                      |                      |

|               |                                                                       | s enabled; all U                                                    |                               | e controlled by l                          | JARTx. as defir                            | ned by UEN<1:        | 0>                   |

|               |                                                                       | s disabled; all L                                                   |                               |                                            |                                            |                      |                      |

| bit 14        | Unimplemen                                                            | ted: Read as 'd                                                     | )'                            |                                            |                                            |                      |                      |

| bit 13        | USIDL: UAR                                                            | Tx Stop in Idle N                                                   | /lode bit                     |                                            |                                            |                      |                      |

|               |                                                                       | nues module op                                                      |                               |                                            | ers Idle mode                              |                      |                      |

|               |                                                                       | s module opera                                                      |                               |                                            |                                            |                      |                      |

| bit 12        | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(1)</sup> |                                                                     |                               |                                            |                                            |                      |                      |

|               |                                                                       | oder and decoo<br>oder and decoo                                    |                               |                                            |                                            |                      |                      |

| bit 11        | RTSMD: Mod                                                            | le Selection for                                                    | UxRTS Pin bi                  | t                                          |                                            |                      |                      |

|               |                                                                       | in is in Simplex<br>in is in Flow Co                                |                               |                                            |                                            |                      |                      |

| bit 10        | Unimplemen                                                            | ted: Read as 'd                                                     | )'                            |                                            |                                            |                      |                      |

| bit 9-8       | UEN<1:0>: U                                                           | IARTx Enable b                                                      | its <sup>(2)</sup>            |                                            |                                            |                      |                      |

|               | 10 = UxTX, U<br>01 = UxTX, U                                          | JxRX and UxBC<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins are | nd UxRTS pin<br>S pins are en | is are enabled a<br>abled <u>and us</u> ec | an <u>d used</u><br>I; <u>UxCTS</u> pin is | controlled by p      | ort latches          |

| bit 7         | WAKE: Wake                                                            | e-up on Start Bit                                                   | Detect During                 | g Sleep Mode E                             | Enable bit                                 |                      |                      |

|               | cleared in                                                            | vill continue to<br>n hardware on t                                 | •                             |                                            | rupt is generate                           | ed on the fallin     | ig edge, bit is      |

| hit C         |                                                                       | -up is enabled                                                      | Mada Salaat                   | hit                                        |                                            |                      |                      |

| bit 6         |                                                                       | ARTx Loopback<br>Loopback mode                                      |                               | DIL                                        |                                            |                      |                      |

|               |                                                                       | k mode is disab                                                     |                               |                                            |                                            |                      |                      |

| bit 5         | -                                                                     | o-Baud Enable                                                       |                               |                                            |                                            |                      |                      |

|               | cleared in                                                            | baud rate meas<br>n hardware upo                                    | n completion                  |                                            | er – requires re                           | ception of a Sy      | nc field (55h);      |

|               |                                                                       | e measurement                                                       |                               | •                                          |                                            |                      |                      |

| bit 4         |                                                                       | RTx Receive Po                                                      | plarity Inversio              | n dit                                      |                                            |                      |                      |

|               | 1 = UxRX IdI<br>0 = UxRX IdI                                          |                                                                     |                               |                                            |                                            |                      |                      |

| Note 1: Th    | nis feature is is                                                     | only available fo                                                   | or the 16x BR                 | G mode (BRGF                               | <b>I</b> = 0).                             |                      |                      |

|               |                                                                       | , donondo on th                                                     |                               | -                                          |                                            |                      |                      |

### REGISTER 15-1: UXMODE: UARTX MODE REGISTER

**2:** The bit availability depends on the pin availability.

| U-0               | R/W-x                                                               | R/W-x            | R/W-x          | R/W-x                         | R/W-x           | R/W-x              | R/W-x   |

|-------------------|---------------------------------------------------------------------|------------------|----------------|-------------------------------|-----------------|--------------------|---------|