#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km102t-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 CPU

| Note: | This data sheet summarizes the features<br>of this group of PIC24F devices. It is not |

|-------|---------------------------------------------------------------------------------------|

|       | intended to be a comprehensive refer-                                                 |

|       | ence source. For more information on the                                              |

|       | CPU, refer to the "PIC24F Family                                                      |

|       | Reference Manual", "CPU" (DS39703).                                                   |

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16<sup>th</sup> working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into program space at any 16K word boundary of either program memory or data EEPROM memory, defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to Data Space mapping feature lets any instruction access program space as if it were Data Space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (i.e., A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to eight sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is illustrated in Figure 3-1.

### 3.1 Programmer's Model

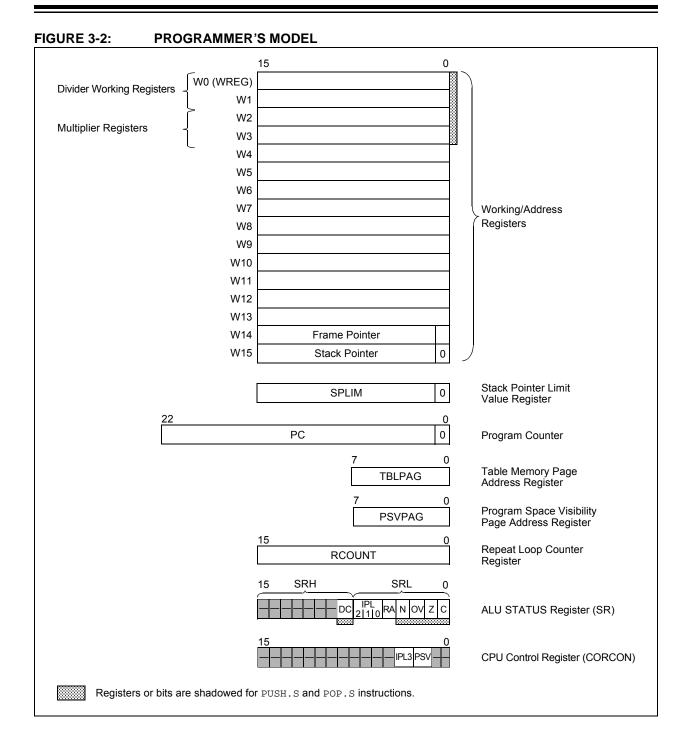

Figure 3-2 displays the programmer's model for the PIC24F. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions.

Table 3-1 provides a description of each register. All registers associated with the programmer's model are memory mapped.

### 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

|                    |                                             |                                                 |                          |                   |                              |                  | <b>DM</b> (0):000 |  |

|--------------------|---------------------------------------------|-------------------------------------------------|--------------------------|-------------------|------------------------------|------------------|-------------------|--|

| U-0                | U-0                                         | U-0                                             | U-0                      | U-0               | U-0                          | U-0              | R/W-0, HSC        |  |

|                    |                                             |                                                 |                          | —                 | —                            | —                | DC                |  |

| bit 15             |                                             |                                                 |                          |                   |                              |                  | bit 8             |  |

| R/W-0, HS          | SC <sup>(1)</sup> R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup>                       |                          |                   |                              |                  | R/W-0, HSC        |  |

| IPL2 <sup>(2</sup> |                                             | IPL0 <sup>(2)</sup>                             |                          |                   |                              |                  |                   |  |

| bit 7              |                                             | 11 2011                                         |                          | IN                | 00                           | 2                | C<br>bit 0        |  |

| Sit 1              |                                             |                                                 |                          |                   |                              |                  |                   |  |

| Legend:            |                                             | HSC = Hardwa                                    | re Settable/0            | Clearable bit     |                              |                  |                   |  |

| R = Reada          | able bit                                    | W = Writable bi                                 | t                        | U = Unimplei      | mented bit, rea              | id as '0'        |                   |  |

| -n = Value         | at POR                                      | '1' = Bit is set                                |                          | '0' = Bit is cle  | ared                         | x = Bit is unk   | nown              |  |

|                    |                                             |                                                 |                          |                   |                              |                  |                   |  |

| bit 15-9           | Unimplement                                 | ed: Read as '0'                                 |                          |                   |                              |                  |                   |  |

| bit 8              |                                             | Carry/Borrow bit                                |                          |                   |                              |                  |                   |  |

|                    |                                             | It from the 4 <sup>th</sup> low-                | -order bit (foi          | byte-sized da     | ta) or 8 <sup>th</sup> Iow-o | rder bit (for wo | rd-sized data)    |  |

|                    |                                             | ult occurred<br>out from the 4 <sup>th</sup> or | 8 <sup>th</sup> low-orde | er bit of the res | sult has occurr              | ed               |                   |  |

| bit 7-5            | •                                           | J Interrupt Priority                            |                          |                   |                              |                  |                   |  |

|                    |                                             | errupt Priority Le                              |                          |                   | s are disabled               |                  |                   |  |

|                    |                                             | errupt Priority Le                              |                          |                   |                              |                  |                   |  |

|                    |                                             | errupt Priority Le                              | · · · ·                  |                   |                              |                  |                   |  |

|                    |                                             | errupt Priority Le                              |                          |                   |                              |                  |                   |  |

|                    |                                             | errupt Priority Le                              |                          |                   |                              |                  |                   |  |

|                    |                                             | errupt Priority Lev<br>errupt Priority Lev      |                          |                   |                              |                  |                   |  |

| bit 4              | RA: REPEAT L                                |                                                 |                          |                   |                              |                  |                   |  |

|                    | 1 = REPEAT <b>IO</b>                        | •                                               |                          |                   |                              |                  |                   |  |

|                    | 0 = REPEAT IO                               | op not in progres                               | S                        |                   |                              |                  |                   |  |

| bit 3              | N: ALU Negati                               |                                                 |                          |                   |                              |                  |                   |  |

|                    | 1 = Result was                              | s negative<br>s non-negative (ze                | oro or popitiv           | (D)               |                              |                  |                   |  |

| bit 2              | OV: ALU Over                                |                                                 |                          | (6)               |                              |                  |                   |  |

|                    |                                             | occurred for signe                              | d (2's compl             | ement) arithm     | etic in this arith           | metic operatio   | on                |  |

|                    |                                             | w has occurred                                  | - (                      | ,                 |                              |                  |                   |  |

| bit 1              | Z: ALU Zero b                               | it                                              |                          |                   |                              |                  |                   |  |

|                    | •                                           | on, which effects                               |                          |                   |                              |                  | 10                |  |

| L:1 0              | _                                           | recent operation,                               | which effects            | s the Z bit, has  | s cleared it (i.e.           | , a non-zero re  | esuit)            |  |

| bit 0              | <b>C:</b> ALU Carry/<br>1 = A carry-ou      | Borrow bit<br>t from the Most S                 | ionificant bit           | (MSb) of the r    | esult occurred               |                  |                   |  |

|                    |                                             | ut from the Most                                |                          |                   |                              |                  |                   |  |

| Note 1:            | The IPLx Status bits                        | are read-only wh                                | en NSTDIS                | (INTCON1<1        | 5>) = 1.                     |                  |                   |  |

| 2:                 | The IPL<2:0> Status                         | •                                               |                          |                   | -                            | o form the CPL   | J Interrupt       |  |

|                    | Priority Level (IPL).                       |                                                 |                          |                   |                              |                  | •                 |  |

|                    |                                             |                                                 |                          |                   |                              |                  |                   |  |

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> devices and improve Data Space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all EA calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word, which contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, the data memory and the registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register, which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed, but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow the users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

#### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the Data Space is addressable indirectly. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing (MDA) with a 16-bit address field. For PIC24FV16KM204 family devices, the entire implemented data memory lies in Near Data Space (NDS).

#### 4.2.4 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by that module. Much of the SFR space contains unused addresses; these are read as '0'. The SFR space, where the SFRs are actually implemented, is provided in Table 4-2. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete listing of implemented SFRs, including their addresses, is provided in Table 4-3 through Table 4-26.

|      | SFR Space Address |            |                 |          |              |      |      |       |  |  |  |  |

|------|-------------------|------------|-----------------|----------|--------------|------|------|-------|--|--|--|--|

|      | xx00              | xx20       | xx40            | xx60     | xx80         | xxA0 | xxC0 | xxE0  |  |  |  |  |

| 000h |                   | Core       |                 | ICN      | Interrupts — |      |      |       |  |  |  |  |

| 100h | Timers            | Timers CLC |                 |          | MCCP/SCCP    |      |      |       |  |  |  |  |

| 200h | MSSP              | UART       | Op Amp          | DAC      | — — I/O      |      |      |       |  |  |  |  |

| 300h |                   | A/D/C      | CMTU            |          | —            | —    | —    | —     |  |  |  |  |

| 400h | —                 | —          | —               | —        | —            | —    | —    | ANSEL |  |  |  |  |

| 500h | —                 | —          | —               | —        | —            | —    | —    | —     |  |  |  |  |

| 600h | —                 | RTCC/Comp  | —               | Band Gap |              |      |      |       |  |  |  |  |

| 700h | _                 | —          | System/<br>HLVD | NVM/PMD  | —            | —    | _    | —     |  |  |  |  |

#### TABLE 4-2: IMPLEMENTED REGIONS OF SFR DATA SPACE

**Legend:** — = No implemented SFRs in this block.

| U-0                          | U-0                                      | U-0                                                                                                                                     | U-0                             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|---------|

| _                            |                                          |                                                                                                                                         |                                 | _                | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| oit 15                       |                                          |                                                                                                                                         | •                               |                  |                  | •               | bit 8   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| U-0                          | R/W-1                                    | R/W-0                                                                                                                                   | R/W-0                           | U-0              | U-0              | U-0             | U-0     |

| —                            | U1ERIP2                                  | U1ERIP1                                                                                                                                 | U1ERIP0                         | —                | —                | —               | —       |

| bit 7                        |                                          |                                                                                                                                         |                                 |                  |                  |                 | bit 0   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| Legend:                      |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| R = Readab                   | ole bit                                  | W = Writable                                                                                                                            | bit                             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value a                 | at POR                                   | '1' = Bit is set                                                                                                                        |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8<br>bit 7<br>bit 6-4 | <pre>111 = Interru </pre>                | >: UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>>: UART1 Error<br>pt is Priority 7 ( | highest priority<br>abled<br>o' | interrupt)       |                  |                 |         |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '                                                             | abled                           | interrupt)       |                  |                 |         |

#### REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| R-0           | U-0                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0              | R-0              | R-0               | R-0               | R-0              |

|---------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|------------------|

| CPUIRQ        |                     | VHOLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | ILR3             | ILR2              | ILR1              | ILR0             |

| bit 15        |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   | bit 8            |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| U-0           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   | R-0               |                  |

| <br>bit 7     | VECNUM6             | VECNUM5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VECNUM4          | VECNUM3          | VECNUM2           | VECNUM1           | VECNUM0<br>bit 0 |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   | 511 0            |

| Legend:       |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| R = Readable  | e bit               | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit              | U = Unimpler     | nented bit, read  | l as '0'          |                  |

| -n = Value at | POR                 | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | '0' = Bit is cle | ared              | x = Bit is unkr   | nown             |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| bit 15        |                     | errupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                |                  |                   |                   |                  |

|               |                     | upt request have the version of the |                  |                  | been Acknowl      | eagea by the      | CPU (this will   |

|               |                     | upt request is l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                  | (index priority)  |                   |                  |

| bit 14        | Unimplemen          | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0'               |                  |                   |                   |                  |

| bit 13        | VHOLD: Vect         | or Hold bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |                  |                   |                   |                  |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  | rupt is Stored ir |                   |                  |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ntain the value  | e of the highe   | st priority pend  | ding interrupt, i | instead of the   |

|               | current in          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tain the value   | of the last Ac   | knowledged int    | orrupt (last into | vrupt that has   |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  | ther interrupts a |                   | nupt that has    |

| bit 12        | Unimplemen          | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0'               |                  |                   |                   |                  |

| bit 11-8      | ILR<3:0>: Ne        | w CPU Interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | pt Priority Leve | el bits          |                   |                   |                  |

|               | 1111 <b>= CPU</b>   | Interrupt Priorit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ty Level is 15   |                  |                   |                   |                  |