Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

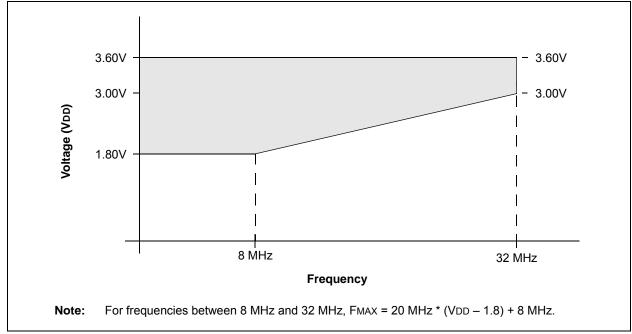

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

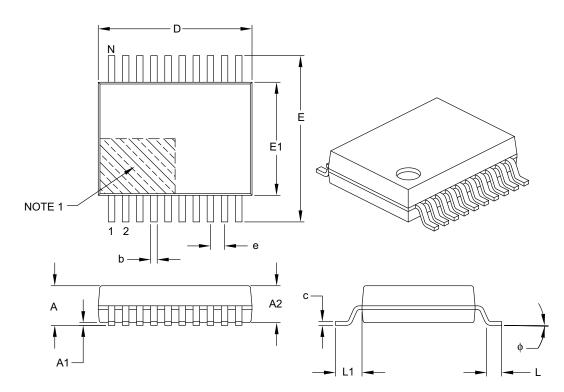

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km202-e-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Peripheral Features**

- High-Current Sink/Source, 18 mA/18 mA All Ports

- Independent Ultra Low-Power, 32 kHz Timer Oscillator

- Up to Two Master Synchronous Serial Ports (MSSPs) with SPI and I<sup>2</sup>C™ modes:

In SPI mode:

- User-configurable SCKx and SDOx pin outputs

- Daisy-chaining of SPI slave devices

#### In I<sup>2</sup>C mode:

- Serial clock synchronization (clock stretching)

- Bus collision detection and will arbitrate accordingly

- Support for 16-bit read/write interface

- Up to Two Enhanced Addressable UARTs:

- LIN/J2602 bus support (auto-wake-up, Auto-Baud Detect, Break character support)

- High and low speed (SCI)

- IrDA<sup>®</sup> mode (hardware encoder/decoder function)

- Two External Interrupt Pins

- Hardware Real-Time Clock and Calendar (RTCC)

- Configurable Reference Clock Output (REFO)

- Two Configurable Logic Cells (CLC)

- Up to Two Single Output Capture/Compare/PWM (SCCP) modules and up to Three Multiple Output Capture/Compare/PWM (MCCP) modules

### **Special Microcontroller Features**

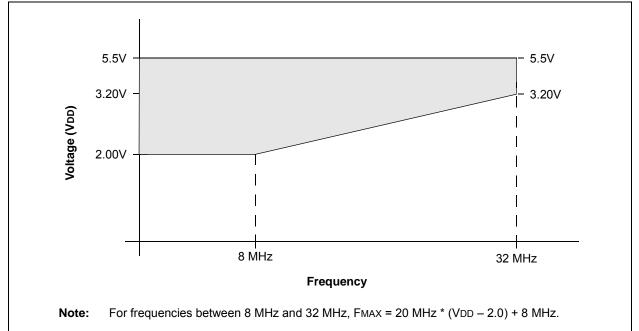

- Wide Operating Voltage Range Options:

- 1.8V to 3.6V (PIC24F devices)

- 2.0V to 5.0V (PIC24FV devices)

- Selectable Power Management modes:

- Idle: CPU shuts down, allowing for significant power reduction

- Sleep: CPU and peripherals shut down for substantial power reduction and fast wake-up

- Retention Sleep mode: PIC24FV devices can enter Sleep mode, employing the Retention Regulator, further reducing power consumption

- Doze: CPU can run at a lower frequency than peripherals, a user-programmable feature

- Alternate Clock modes allow on-the-fly switching to a lower clock speed for selective power reduction

- · Fail-Safe Clock Monitor:

- Detects clock failure and switches to on-chip, low-power RC Oscillator

- Ultra Low-Power Wake-up Pin Provides an External Trigger for Wake from Sleep

- 10,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- 100,000 Erase/Write Cycle Endurance Data EEPROM, Typical

- Flash and Data EEPROM Data Retention: 20 Years Minimum

- Self-Programmable under Software Control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

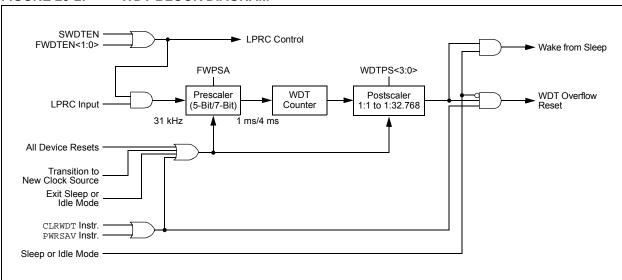

- Watchdog Timer (WDT) with its Own On-Chip RC Oscillator for Reliable Operation

- On-Chip Regulator for 5V Operation

- Selectable Windowed WDT Feature

- Selectable Oscillator Options including:

4x Phase Locked Loop (PLL)

- 8 MHz (FRC) Internal RC Oscillator:

- HS/EC, High-Speed Crystal/Resonator Oscillator or External Clock

- In-Circuit Serial Programming™ (ICSP™) and In-Circuit Emulation (ICE) via Two Pins

- In-Circuit Debugging

- Programmable High/Low-Voltage Detect (HLVD) module

- Programmable Brown-out Reset (BOR):

- Software enable feature

- Configurable shutdown in Sleep

- Auto-configures power mode and sensitivity based on device operating speed

- LPBOR available for re-arming of the POR

### Pin Diagrams (Continued)

|     | 20-Pin QFN<br>$\begin{array}{c ccccccccccccccccccccccccccccccccccc$              |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------|--|--|--|--|--|

| Dia | Pin Features                                                                     |  |  |  |  |  |

| Pin | PIC24F08KM101 PIC24FV08KM101                                                     |  |  |  |  |  |

| 1   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0                                         |  |  |  |  |  |

| 2   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                                                   |  |  |  |  |  |

| 3   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                                                    |  |  |  |  |  |

| 4   | OSCI/CLKI/AN13/C1INB/CN30/RA2                                                    |  |  |  |  |  |

| 5   | OSCO/CLKO/AN14/C1INA/CN29/RA3                                                    |  |  |  |  |  |

| 6   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4                                                  |  |  |  |  |  |

| 7   | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/RA4                                    |  |  |  |  |  |

| 8   | AN19/U1TX/CTED1/INT0/CN23/RB7 AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7             |  |  |  |  |  |

| 9   | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8                                             |  |  |  |  |  |

| 10  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4/CN21/RB9                             |  |  |  |  |  |

| 11  | IC1/OC1A/INT2/CN8/RA6 VCAP OR VDDCORE                                            |  |  |  |  |  |

| 12  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12 AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |  |

| 13  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13                                              |  |  |  |  |  |

| 14  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RB14                                  |  |  |  |  |  |

| 15  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15                                               |  |  |  |  |  |

| 16  | Vss/AVss                                                                         |  |  |  |  |  |

| 17  | Vdd/AVdd                                                                         |  |  |  |  |  |

| 18  | MCLR/Vpp/RA5                                                                     |  |  |  |  |  |

| 19  | PGEC2/CVREF+ /VREF+/AN0/CN2/RA0                                                  |  |  |  |  |  |

| 20  | PGED2/CVREF-/VREF-/AN1/CN3/RA1                                                   |  |  |  |  |  |

### **Table of Contents**

| 1.0   | Device Overview                                             |       |

|-------|-------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 29    |

| 3.0   | CPU                                                         | 35    |

| 4.0   | Memory Organization                                         | 41    |

| 5.0   | Flash Program Memory                                        | 67    |

| 6.0   | Data EEPROM Memory                                          | 73    |

| 7.0   | Resets                                                      | 79    |

| 8.0   | Interrupt Controller                                        | 85    |

| 9.0   | Oscillator Configuration                                    | . 121 |

| 10.0  | Power-Saving Features                                       | . 131 |

| 11.0  | I/O Ports                                                   | . 137 |

| 12.0  | Timer1                                                      |       |

| 13.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)           | . 143 |

| 14.0  | Master Synchronous Serial Port (MSSP)                       |       |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART)          | . 173 |

| 16.0  | Real-Time Clock and Calendar (RTCC)                         | . 181 |

| 17.0  | Configurable Logic Cell (CLC)                               | . 195 |

| 18.0  | High/Low-Voltage Detect (HLVD)                              | . 207 |

|       | 12-Bit A/D Converter with Threshold Detect                  |       |

| 20.0  | 8-Bit Digital-to-Analog Converter (DAC)                     | . 229 |

| 21.0  | Dual Operational Amplifier Module                           | . 233 |

| 22.0  | Comparator Module                                           |       |

| 23.0  | Comparator Voltage Reference                                | . 239 |

| 24.0  | Charge Time Measurement Unit (CTMU)                         | . 241 |

| 25.0  | Special Features                                            | . 249 |

| 26.0  | Development Support                                         | . 261 |

| 27.0  | Electrical Characteristics                                  | . 265 |

| 28.0  | Packaging Information                                       | . 297 |

| Appe  | ndix A: Revision History                                    | . 325 |

| Index | · · · · · · · · · · · · · · · · · · ·                       | 327   |

|       | /icrochip Web Site                                          |       |

| Custo | omer Change Notification Service                            | . 333 |

| Custo | omer Support                                                | . 333 |

| Produ | Jct Identification System                                   | . 335 |

### 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the Table Read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location, followed by a TBLRDL instruction.

A typical read sequence, using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and Table Read (builtin\_tblrd1) procedures from the C30 compiler library, is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

### EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

| <pre>intattribute ((space(eedata))) eeData = 0x1234;</pre> |                                       |

|------------------------------------------------------------|---------------------------------------|

| int data;                                                  | // Data read from EEPROM              |

| /*                                                         |                                       |

| The variable eeData must be a Global variable declared     | d outside of any method               |

| the code following this comment can be written inside      | the method that will execute the read |

| */                                                         |                                       |

| unsigned int offset;                                       |                                       |

| // Set up a pointer to the EEPROM location to be e         | erased                                |

| <pre>TBLPAG =builtin_tblpage(&amp;eeData);</pre>           | // Initialize EE Data page pointer    |

| offset =builtin_tbloffset(&eeData);                        | // Initizlize lower word of address   |

| <pre>data =builtin_tblrdl(offset);</pre>                   | // Write EEPROM data to write latch   |

|                                                            |                                       |

### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC Oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

### 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSCx bits in the Flash Configuration Word (FOSCSEL<2:0>); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

### 7.4 Brown-out Reset (BOR)

The PIC24FXXXXX family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the Power-up Timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the Brown-out Reset does not automatically enable the PWRT.

### 7.4.1 LOW-POWER BOR (LPBOR)

The Low-Power BOR is an alternate setting for the BOR, designed to consume minimal power. In LPBOR mode, BORV<1:0> (FPOR<6:5>) = 00. The BOR trip point is approximately 2.0V. Due to the low current consumption, the accuracy of the LPBOR mode can vary.

Unlike the other BOR modes, LPBOR mode will not cause a device Reset when VDD drops below the trip point. Instead, it re-arms the POR circuit to ensure that the device will reset properly in the event that VDD continues to drop below the minimum operating voltage.

The device will continue to execute code when VDD is below the level of the LPBOR trip point. A device that requires falling edge BOR protection to prevent code from improperly executing should use one of the other BOR voltage settings.

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0        | U-0 |

|--------------|-----|-----|-----|-----|-----|-----|-----|

| NSTDIS       | —   | —   | —   | —   | —   | —   | —   |

| bit 15 bit 8 |     |     |     |     |     |     |     |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| —     | —   | —   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | —     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:       |                                                                                                                          | HS = Hardware Settable bi                                                                                | t                                  |                    |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readabl   | e bit                                                                                                                    | W = Writable bit                                                                                         | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at | POR                                                                                                                      | '1' = Bit is set                                                                                         | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15        | 1 = Interru                                                                                                              | Interrupt Nesting Disable bit<br>Ipt nesting is disabled                                                 |                                    |                    |  |  |  |

| bit 14-5      |                                                                                                                          | ipt nesting is enabled<br>nented: Read as '0'                                                            |                                    |                    |  |  |  |

| bit 4         | <b>MATHERI</b><br>1 = Overfl                                                                                             | R: Arithmetic Error Trap Status t<br>ow trap has occurred<br>ow trap has not occurred                    | bit                                |                    |  |  |  |

| bit 3         | ADDRERR: Address Error Trap Status bit<br>1 = Address error trap has occurred<br>0 = Address error trap has not occurred |                                                                                                          |                                    |                    |  |  |  |

| bit 2         | 1 = Stack                                                                                                                | Stack Error Trap Status bit<br>error trap has occurred<br>error trap has not occurred                    |                                    |                    |  |  |  |

| bit 1         | 1 = Oscilla                                                                                                              | Oscillator Failure Trap Status t<br>ator failure trap has occurred<br>ator failure trap has not occurred |                                    |                    |  |  |  |

| bit 0         | Unimplen                                                                                                                 | nented: Read as '0'                                                                                      |                                    |                    |  |  |  |

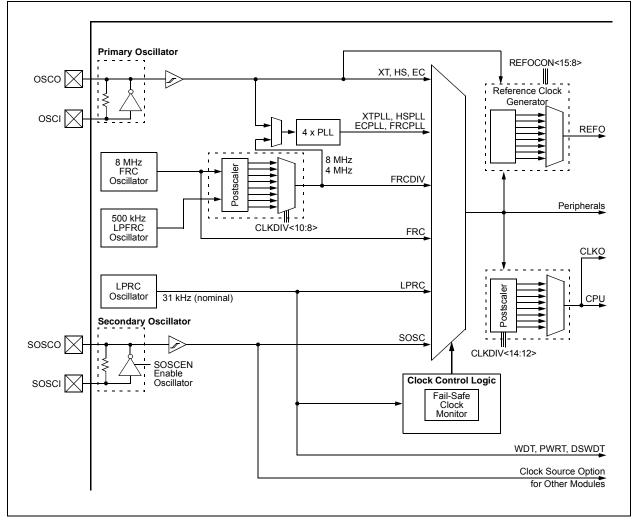

### 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on oscillator configuration, refer to the *"PIC24F Family Reference Manual"*, **"Oscillator with 500 kHz Low-Power FRC"** (DS39726).

The oscillator system for the PIC24FV16KM204 family of devices has the following features:

A total of five external and internal oscillator options as clock sources, providing 11 different clock modes.

- On-chip 4x Phase Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources.

- Software-controllable switching between various clock sources.

- Software-controllable postscaler for selective clocking of CPU for system power savings.

- System frequency range declaration bits for External Clock (EC) mode. When using an EC source, the current consumption is reduced by setting the declaration bits to the expected frequency range.

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown.

A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: PIC24FXXXXX FAMILY CLOCK DIAGRAM

#### REGISTER 11-2: ANSB: PORTB ANALOG SELECTION REGISTER

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | U-0 | U-0 | R/W-1 | R/W-1 |

|--------|--------|--------|--------|-----|-----|-------|-------|

| ANSB15 | ANSB14 | ANSB13 | ANSB12 | —   |     | ANSB9 | ANSB8 |

| bit 15 |        |        |        |     |     |       | bit 8 |

| R/W-1 | R/W-1                | R/W-1                | R/W-1 | R/W-1                | R/W-1 | R/W-1 | R/W-1 |

|-------|----------------------|----------------------|-------|----------------------|-------|-------|-------|

| ANSB7 | ANSB6 <sup>(1)</sup> | ANSB5 <sup>(1)</sup> | ANSB4 | ANSB3 <sup>(1)</sup> | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |                      |                      |       |                      |       |       | bit 0 |

### Legend

| Legena:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

bit 15-12 **ANSB<15:12>:** Analog Select Control bits 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

- bit 11-10 Unimplemented: Read as '0'

- bit 9-0 ANSB<9:0>: Analog Select Control bits<sup>(1)</sup>

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

- Note 1: The ANSB<6:5,3> bits are not available on 20-pin devices.

### REGISTER 11-3: ANSC: PORTC ANALOG SELECTION REGISTER

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0                    | U-0                    | U-0                    |

|---------|-----|-----|-----|-----|------------------------|------------------------|------------------------|

| —       | —   | —   | —   | —   | —                      | —                      | —                      |

| bit 15  |     |     |     |     |                        |                        | bit 8                  |

|         |     |     |     |     |                        |                        |                        |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1                  | R/W-1                  | R/W-1                  |

| —       | —   | —   | —   | —   | ANSC2 <sup>(1,2)</sup> | ANSC1 <sup>(1,2)</sup> | ANSC0 <sup>(1,2)</sup> |

| bit 7   |     |     |     |     |                        |                        | bit 0                  |

|         |     |     |     |     |                        |                        |                        |

| Legend: |     |     |     |     |                        |                        |                        |

| Logona.           |                                                                    |                      |                    |

|-------------------|--------------------------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      | , read as '0'      |

| -n = Value at POR | '1' = Bit is set                                                   | '0' = Bit is cleared | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 ANSC<2:0>: Analog Select Control bits<sup>(1,2)</sup>

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

#### REGISTER 13-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

| bit 15         U-0       R/W-0       R/W 0       R/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0         | R/W-0                                                                                                 | R/W-0            | R/W-0           | U-0            | R/W-0                | R/W-0                | R/W-0                  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------|------------------|-----------------|----------------|----------------------|----------------------|------------------------|--|--|--|--|

| U-0       U-0       R/W-0       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OETRIG        | OSCNT2                                                                                                | OSCNT1           | OSCNT0          |                | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup>   |  |  |  |  |

| -         POLACE         POLBOF <sup>(1)</sup> PSSACE1         PSSACE0         PSSBDF1 <sup>(1)</sup> PSSBDF1 <sup>(1)</sup> bit 7           Legend:           R = Readable bit         W = Writable bit         U = Unimplemented bit, read as '0'<br>-n = Value at POR         '1' = Bit is set         '0' = Bit is cleared         x = Bit is unknown           bit 15         OETRIG: CCPx Dead-Time Select bit<br>1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered<br>0 = Normal output pin operation           bit 14-12         OSCNT-2:0>: One-Shot Event Count bits           111 = Extend one-shot event by 7 time base periods (6 time base periods total)           100 = Extend one-shot event by 5 time base periods (6 time base periods total)           101 = Extend one-shot event by 2 time base periods (6 time base periods total)           011 = Extend one-shot event by 2 time base periods (6 time base periods total)           010 = Extend one-shot event by 2 time base periods (2 time base periods total)           011 = Extend one-shot event by 2 time base periods (2 time base periods total)           011 = Extend one-shot event by 2 time base periods (2 time base periods total)           010 = D textend one-shot event by 2 time base periods (2 time base periods total)           010 = D textend one-shot event by 2 time base periods (2 time base periods total)           011 = Extend one-shot event by 2 time base periods (2 time base periods total)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 15        |                                                                                                       |                  |                 |                |                      |                      | bit 8                  |  |  |  |  |

| -         POLACE         POLBOF <sup>(1)</sup> PSSACE1         PSSACE0         PSSBDF1 <sup>(1)</sup> PSSBDF1 <sup>(1)</sup> bit 7           Legend:           R = Readable bit         W = Writable bit         U = Unimplemented bit, read as '0'<br>-n = Value at POR         '1' = Bit is set         '0' = Bit is cleared         x = Bit is unknown           bit 15         OETRIG: CCPx Dead-Time Select bit<br>1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered<br>0 = Normal output pin operation           bit 14-12         OSCNT-2:0>: One-Shot Event Count bits           111 = Extend one-shot event by 7 time base periods (6 time base periods total)           100 = Extend one-shot event by 5 time base periods (6 time base periods total)           101 = Extend one-shot event by 2 time base periods (6 time base periods total)           011 = Extend one-shot event by 2 time base periods (6 time base periods total)           010 = Extend one-shot event by 2 time base periods (2 time base periods total)           011 = Extend one-shot event by 2 time base periods (2 time base periods total)           011 = Extend one-shot event by 2 time base periods (2 time base periods total)           010 = D textend one-shot event by 2 time base periods (2 time base periods total)           010 = D textend one-shot event by 2 time base periods (2 time base periods total)           011 = Extend one-shot event by 2 time base periods (2 time base periods total)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |                                                                                                       |                  |                 |                |                      |                      |                        |  |  |  |  |

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       OETRIG: CCPx Dead-Time Select bit       1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered         0 = Normal output pin operation       111 = Extend one-shot event by 7 time base periods (8 time base periods total)         101 = Extend one-shot event by 5 time base periods (6 time base periods total)       100 = Extend one-shot event by 4 time base periods (5 time base periods total)         101 = Extend one-shot event by 3 time base periods (6 time base periods total)       011 = Extend one-shot event by 4 time base periods (6 time base periods total)         010 = Extend one-shot event by 1 time base periods (2 time base periods total)       011 = Extend one-shot event by 1 time base periods (2 time base periods total)         010 = Extend one-shot event by 1 time base periods (2 time base periods total)       001 = Extend one-shot event by 1 time base periods (2 time base periods total)         010 = Extend one-shot event by 1 time base periods (2 time base periods total)       001 = Extend one-shot event by 1 time base periods (2 time base periods total)         010 = Extend one-shot event by 1 time base periods (2 time base periods total)       001 = Extend one-shot event by 1 time base periods (2 time base periods total)         010 = D totatend one-shot event by 1 time bas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0           | <u>U-0</u>                                                                                            | (                |                 |                | 1                    |                      | R/W-0                  |  |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 OETRIG: CCPx Dead-Time Select bit<br>1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered<br>0 = Normal output pin operation<br>bit 14-12 OSCNT-2:0>: One-Shot Event Count bits<br>111 = Extend one-shot event by 7 time base periods (8 time base periods total)<br>100 = Extend one-shot event by 7 time base periods (7 time base periods total)<br>101 = Extend one-shot event by 5 time base periods (7 time base periods total)<br>102 = Extend one-shot event by 5 time base periods (6 time base periods total)<br>103 = Extend one-shot event by 2 time base periods (4 time base periods total)<br>104 = Extend one-shot event by 2 time base periods (3 time base periods total)<br>105 = Extend one-shot event by 2 time base periods (3 time base periods total)<br>106 = Extend one-shot event by 1 time base periods (3 time base periods total)<br>107 = Extend one-shot event by 2 time base periods (3 time base periods total)<br>108 = Extend one-shot event by 1 time base period (2 time base periods total)<br>109 = Do not extend one-shot trigger event<br>111 Unimplemented: Read as '0'<br>112 = Reserved<br>113 = Reserved<br>114 = Reserved<br>115 = OULACE: CCPX Output mode, reverse<br>115 = POLACE: CCPX Output mode<br>116 = FUSh-Pull Output mode<br>117 = Reserved<br>118 = Reserved<br>119 = Output pin polarity is active-low<br>119 = Output pin polarity is active-low<br>119 = Output pin polarity is active-low<br>119 = Output pin polarity is active-low<br>120 = Output pin polarity is active-low<br>131 = DEBDF: CCPX Output Pins, OCXA, OCXC and OCXE, Polarity Control bit<br>132 = Pins are driven inactive when a shutdown event occurs<br>132 = Pins are driven inactive when a shutdown event occurs<br>133 = Pins are driven inactive when a shutdown event occurs<br>134 = Pins are driven inactive when a shutdown event occurs<br>135 = Pins are driven inactive when a shutdown event occurs<br>135 = Pins are driven inactive                                              |               |                                                                                                       | POLACE           | POLBDF          | PSSACE1        | PSSACE0              | PSSBDF1()            | PSSBDF0 <sup>(1)</sup> |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       OETRIG: CCPx Dead-Time Select bit       1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered         bit 14       OSCNT<2:0>: One-Shot Event Count bits       11 = Extend one-shot event by 7 time base periods (8 time base periods total)         100 = Extend one-shot event by 5 time base periods (6 time base periods total)       100 = Extend one-shot event by 5 time base periods (6 time base periods total)         010 = Extend one-shot event by 3 time base periods (6 time base periods total)       010 = Extend one-shot event by 3 time base periods (3 time base periods total)         010 = Extend one-shot event by 1 time base periods (3 time base periods total)       010 = Extend one-shot event by 1 time base periods (1 time base periods total)         010 = Extend one-shot event by 1 time base periods (1 time base periods total)       010 = Extend one-shot frigger event         bit 10-8       OUTM       OUTM       OUTM       OUTM       OUTM         010 = Dutput Scan mode       111 = Reserved       111 = Reserved<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7         |                                                                                                       |                  |                 |                |                      |                      | bit C                  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       OETRIG: CCPx Dead-Time Select bit       1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered         bit 14       OSCNT<2:0>: One-Shot Event Count bits       11 = Extend one-shot event by 7 time base periods (8 time base periods total)         100 = Extend one-shot event by 5 time base periods (6 time base periods total)       100 = Extend one-shot event by 5 time base periods (6 time base periods total)         010 = Extend one-shot event by 3 time base periods (6 time base periods total)       010 = Extend one-shot event by 3 time base periods (3 time base periods total)         010 = Extend one-shot event by 1 time base periods (3 time base periods total)       010 = Extend one-shot event by 1 time base periods (1 time base periods total)         010 = Extend one-shot event by 1 time base periods (1 time base periods total)       010 = Extend one-shot frigger event         bit 10-8       OUTM       OUTM       OUTM       OUTM       OUTM         010 = Dutput Scan mode       111 = Reserved       111 = Reserved<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Legend:       |                                                                                                       |                  |                 |                |                      |                      |                        |  |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       OETRIG: CCPx Dead-Time Select bit       1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered 0 = Normal output pin operation         bit 14-12       OSCNT-2:0>: One-Shot Event Count bits       111 = Extend one-shot event by 6 time base periods (8 time base periods total)         100 = Extend one-shot event by 5 time base periods (6 time base periods total)       101 = Extend one-shot event by 4 time base periods (5 time base periods total)         101 = Extend one-shot event by 3 time base periods (1 time base periods total)       000 = Extend one-shot event by 3 time base periods (2 time base periods total)         001 = Extend one-shot event by 3 time base periods (2 time base periods total)       001 = Extend one-shot event by 1 time base periods (2 time base periods total)         001 = Extend one-shot event by 1 time base periods (2 time base periods total)       001 = Extend one-shot event by 1 time base periods (2 time base periods total)         001 = Extend one-shot event by 2 time base periods (2 time base periods total)       001 = Extend one-shot event by 1 time base periods (2 time base periods total)         000 = Do not extend one-shot event by 6 time base periods (3 time base periods total)       001 = Extend one-shot event by 6 time base periods (2 time base periods total)         010 = Output Scan mode       101 = Output Scan mode       101 = Output Scan mode         101 = Noush DC Output mode, reverse       101 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -             | e bit                                                                                                 | W = Writable     | bit             | U = Unimpler   | nented bit, read     | d as '0'             |                        |  |  |  |  |

| <ul> <li>bit 15 OETRIG: CCPx Dead-Time Select bit</li> <li>1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered 0 = Normal output pin operation</li> <li>bit 14-12 OSCNT-2:0: One-Shot Event Count bits</li> <li>111 = Extend one-shot event by 6 time base periods (8 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>101 = Extend one-shot event by 3 time base periods (6 time base periods total)</li> <li>101 = Extend one-shot event by 3 time base periods (3 time base periods total)</li> <li>010 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>010 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>010 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>010 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>010 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>010 = Extend one-shot ovent by 1 time base periods (3 time base periods total)</li> <li>010 = Do not extend one-shot Trigger event</li> <li>011 = Reserved</li> <li>111 = Reserved</li> <li>112 = Reserved</li> <li>113 = Reserved</li> <li>114 = Reserved</li> <li>115 = Bush DC Output mode, forward</li> <li>100 = Bush DC Output mode</li> <li>011 = Push-Pull Output mode</li> <li>012 = Half-Bridge Output mode</li> <li>013 = Push-Pull Output mode</li> <li>014 = PolLACE: CCPX Output Pins, OCXA, OCXC and OCXE, Polarity Control bit</li> <li>1 = Output pin polarity is active-low</li> <li>0 =</li></ul>                                                                                                                | -n = Value at | POR                                                                                                   | '1' = Bit is set |                 | -              |                      |                      | iown                   |  |  |  |  |

| <ul> <li>1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered 0 = Normal output pin operation</li> <li>bit 14-12</li> <li>OSCNT&lt;2:0:: One-Shot Event Count bits</li> <li>111 = Extend one-shot event by 7 time base periods (8 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>102 = Extend one-shot event by 3 time base periods (6 time base periods total)</li> <li>103 = Extend one-shot event by 2 time base periods (5 time base periods total)</li> <li>104 = Extend one-shot event by 2 time base periods (2 time base periods total)</li> <li>105 = Extend one-shot event by 2 time base periods (2 time base periods total)</li> <li>106 = Extend one-shot Trigger event</li> <li>107 = Extend one-shot Trigger event</li> <li>108 OUTM</li> <li>109 = Do not extend one-shot Trigger event</li> <li>110 = Brush DC Output mode, forward</li> <li>101 = Brush DC Output mode, forward</li> <li>101 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, reverse</li> <li>101 = Reserved</li> <li>101 = Push-Pull Output mode</li> <li>101 = Push-Pull Output mode</li> <li>111 = Output pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Pins are driven inactive when a shutdown event occurs</li> <li>0 = Pins</li></ul>                                                                                                                                                                                                                                                         |               | -                                                                                                     |                  |                 |                |                      |                      | -                      |  |  |  |  |

| <ul> <li>1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered 0 = Normal output pin operation</li> <li>bit 14-12</li> <li>OSCNT&lt;2:0:: One-Shot Event Count bits</li> <li>111 = Extend one-shot event by 7 time base periods (8 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>102 = Extend one-shot event by 3 time base periods (6 time base periods total)</li> <li>103 = Extend one-shot event by 2 time base periods (5 time base periods total)</li> <li>104 = Extend one-shot event by 2 time base periods (2 time base periods total)</li> <li>105 = Extend one-shot event by 2 time base periods (2 time base periods total)</li> <li>106 = Extend one-shot Trigger event</li> <li>107 = Extend one-shot Trigger event</li> <li>108 OUTM</li> <li>109 = Do not extend one-shot Trigger event</li> <li>110 = Brush DC Output mode, forward</li> <li>101 = Brush DC Output mode, forward</li> <li>101 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, reverse</li> <li>101 = Reserved</li> <li>101 = Push-Pull Output mode</li> <li>101 = Push-Pull Output mode</li> <li>111 = Output pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Pins are driven inactive when a shutdown event occurs</li> <li>0 = Pins</li></ul>                                                                                                                                                                                                                                                         | bit 15        | OETRIG: CC                                                                                            | Px Dead-Time     | Select bit      |                |                      |                      |                        |  |  |  |  |

| <ul> <li>0 = Normal output pin operation</li> <li>0 = Normal output pin operation</li> <li>0 = SCNT &lt;2:0&gt;: One-Shot Event Count bits</li> <li>111 = Extend one-shot event by 7 time base periods (8 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>101 = Extend one-shot event by 3 time base periods (5 time base periods total)</li> <li>101 = Extend one-shot event by 2 time base periods (5 time base periods total)</li> <li>101 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>100 = D on to extend one-shot Trigger event</li> <li>001 = D on to extend one-shot Trigger event</li> <li>001 = D on to extend one-shot Trigger event</li> <li>001 = Brush DC Output Mode Control bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>100 = Output Scan mode</li> <li>101 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode</li> <li>101 = Push-Pull Output mode</li> <li>001 = Steerable Single Output mode</li> <li>001 = Output pin polarity is active-low</li> <li>0 = Pins are driven active w</li></ul>                                                                                                                                                                                                                                                     |               | 1 = For Trigg                                                                                         | ered mode (TF    | RIGEN = 1): Mo  | dule does not  | drive enabled        | output pins until    | l triggered            |  |  |  |  |

| <ul> <li>111 = Extend one-shot event by 7 time base periods (8 time base periods total)</li> <li>110 = Extend one-shot event by 6 time base periods (7 time base periods total)</li> <li>101 = Extend one-shot event by 4 time base periods (6 time base periods total)</li> <li>100 = Extend one-shot event by 4 time base periods (6 time base periods total)</li> <li>101 = Extend one-shot event by 4 time base periods (3 time base periods total)</li> <li>101 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>101 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>101 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>101 = Extend one-shot event by 1 time base period (2 time base periods total)</li> <li>101 = Extend one-shot event by 1 time base period (2 time base periods total)</li> <li>101 = Extend one-shot event by 1 time base period (2 time base periods total)</li> <li>101 = Extend one-shot event by 1 time base period (2 time base periods total)</li> <li>101 = Extend one-shot event by 1 time base period (2 time base periods total)</li> <li>111 = Reserved</li> <li>112 = Dutput pin polarity is active-low</li> <li>113 = Output Pins, OCXA, OCXC and OCXE, Polarity Control bit</li> <li>114 = Output pin polarity is active-low</li> <li>12 = Output pin polarity is active-low</li> <li>13 = Output pin polarity is active-low</li> <l< td=""><td></td><td colspan="10"></td></l<></ul>                                                                                                                                                                                                                                     |               |                                                                                                       |                  |                 |                |                      |                      |                        |  |  |  |  |

| <ul> <li>110 = Extend one-shot event by 6 time base periods (7 time base periods total)</li> <li>101 = Extend one-shot event by 5 time base periods (5 time base periods total)</li> <li>100 = Extend one-shot event by 4 time base periods (5 time base periods total)</li> <li>101 = Extend one-shot event by 2 time base periods (2 time base periods total)</li> <li>101 = Extend one-shot event by 1 time base periods (2 time base periods total)</li> <li>100 = Do not extend one-shot Trigger event</li> <li>111 Unimplemented: Read as '0'</li> <li>111 = Reserved</li> <li>111 = Reserved</li> <li>111 = Reserved</li> <li>110 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, forward</li> <li>100 = Steerable Single Output mode</li> <li>001 = Push-Puil Output mode</li> <li>001 = Exterd exterved</li> <li>002 = Steerable Single Output mode</li> <li>003 = Steerable Single Output mode</li> <li>004 = Output pin polarity is active-low</li> <li>0 = Output pin polarity is active-logh</li> <li>11 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>10 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 14-12     | OSCNT<2:0>                                                                                            | : One-Shot Ev    | ent Count bits  |                |                      |                      |                        |  |  |  |  |

| <ul> <li>101 = Extend one-shot event by 5 time base periods (6 time base periods total)</li> <li>100 = Extend one-shot event by 4 time base periods (5 time base periods total)</li> <li>011 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>010 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 1 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>011 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>011 = Dot ot extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>011 = Brush DC Output Mode Control bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>111 = Reserved</li> <li>110 = Output Scan mode</li> <li>101 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode</li> <li>010 = Half-Bridge Output mode</li> <li>010 = Half-Bridge Output mode</li> <li>011 = Push-Pull Output pins, OCXA, OCXC and OCXE, Polarity Control bit</li> <li>1 = Output pin polarity is active-low</li> <li>0 = Output pin polarity is active-low</li> <li>0 = Output pin polarity is active-low</li> <li>0 = Output pin polarity is active-logh</li> <li>0 = Output pin polarity is active-logh</li> <li>0 = Dins are driven active when a shutdown event occurs</li> <li>0 =</li></ul>                                                                                                                                                                                                                               |               |                                                                                                       |                  |                 |                |                      |                      |                        |  |  |  |  |

| <ul> <li>100 = Extend one-shot event by 4 time base periods (5 time base periods total)</li> <li>011 = Extend one-shot event by 3 time base periods (4 time base periods total)</li> <li>010 = Extend one-shot event by 1 time base periods (2 time base periods total)</li> <li>000 = Do not extend one-shot Trigger event</li> <li>bit 11</li> <li>Unimplemented: Read as '0'</li> <li>bit 10-8</li> <li>OUTM&lt;2:0&gt;: PWMx Output Mode Control bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>110 = Output Scan mode</li> <li>110 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, reverse</li> <li>011 = Reserved</li> <li>010 = Half-Bridge Output mode</li> <li>000 = Steerable Single Output mode</li> <li>000 = Steerable Single Output Pins, OCXA, OCXC and OCXE, Polarity Control bit</li> <li>1 = Output pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Output pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Output pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Dutput pin polarity is active-low</li> <li>0 = Dutput pin set active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven inactive when a shutdown event occurs</li> <li>0 = Pins</li></ul>                                                                                                                                                                                                                                                         |               | 110 = Extend one-shot event by 6 time base periods (7 time base periods total)                        |                  |                 |                |                      |                      |                        |  |  |  |  |

| <ul> <li>11 = Extend one-shot event by 3 time base periods (4 time base periods total)</li> <li>10 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>11 = Extend one-shot Trigger event</li> <li>bit 11 Unimplemented: Read as '0'</li> <li>bit 10-8 OUTM&lt;2:0&gt;: PWMx Output Mode Control bits<sup>(1)</sup></li> <li>11 = Reserved</li> <li>10 = Output Scan mode</li> <li>10 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, reverse</li> <li>011 = Reserved</li> <li>010 = Half-Bridge Output mode</li> <li>011 = Reserved</li> <li>010 = Steerable Single Output mode</li> <li>011 = Output pin polarity is active-low</li> <li>011 = Pins are driven active when a shutdown event occurs</li> <li>011 = Pins are driven active when a shutdown event occurs</li> <li>011 = Pins are driven active when a shutdown event occurs</li> <li>011 = Pins are driven active when a shutdown event occurs</li> <li>011 = Pins are driven active when a shutdown event occurs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                                                       |                  |                 |                |                      |                      |                        |  |  |  |  |

| <ul> <li>100 = Extend one-shot event by 2 time base periods (3 time base periods total)</li> <li>001 = Extend one-shot event by 1 time base period (2 time base periods total)</li> <li>000 = Do not extend one-shot Trigger event</li> <li>bit 11</li> <li>Unimplemented: Read as '0'</li> <li>DUTM-2:0&gt;: PWMx Output Mode Control bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>100 = Output Scan mode</li> <li>101 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, reverse</li> <li>011 = Reserved</li> <li>010 = Half-Bridge Output mode</li> <li>001 = Push-Pull Output mode</li> <li>000 = Steerable Single Output mode</li> <li>000 = Steerable Single Output mode</li> <li>011 = Output pins, OCXA, OCXC and OCXE, Polarity Control bit</li> <li>1 = Output pin polarity is active-low</li> <li>0 = Dins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 =</li></ul>                                                                                                                                                                                                                                                                     |               |                                                                                                       |                  |                 |                |                      |                      |                        |  |  |  |  |

| 001 = Extend one-shot event by 1 time base period (2 time base periods total)         000 = Do not extend one-shot Trigger event         bit 11       Unimplemented: Read as '0'         bit 10-8       OUTM<2:0>: PWMx Output Mode Control bits <sup>(1)</sup> 111 = Reserved       110 = Output Scan mode         101 = Dutput Scan mode       101 = Brush DC Output mode, forward         100 = Brush DC Output mode, forward       100 = Brush DC Output mode         011 = Reserved       010 = Half-Bridge Output mode         010 = Half-Bridge Output mode       000 = Steerable Single Output mode         001 = Push-Pull Output prins, OCXA, OCXC and OCXE, Polarity Control bit       1         1 = Output pin polarity is active-low       0         0 = Dins are driven ac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | 010 = Extend one-shot event by 2 time base periods (3 time base periods total)                        |                  |                 |                |                      |                      |                        |  |  |  |  |

| bit 11       Unimplemented: Read as '0'         bit 10-8       OUTM<2:0>: PWMx Output Mode Control bits <sup>(1)</sup> 111 = Reserved       110 = Output Scan mode         101 = Brush DC Output mode, forward       100 = Brush DC Output mode, reverse         011 = Reserved       010 = Half-Bridge Output mode         010 = Half-Bridge Output mode       001 = Push-Pull Output mode         000 = Steerable Single Output mode       000 = Steerable Single Output mode         000 = Steerable Single Output mode       000 = Steerable Single Output mode         bit 7-6       Unimplemented: Read as '0'         bit 5       POLACE: CCPx Output Pins, OCxA, OCxC and OCxE, Polarity Control bit         1 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Dins are driven active when a shutdown event occurs       0 = Pins are driven inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 001 = Extend one-shot event by 1 time base period (2 time base periods total)                         |                  |                 |                |                      |                      |                        |  |  |  |  |

| bit 10-8       OUTM-2:0>: PWMx Output Mode Control bits <sup>(1)</sup> 111 = Reserved       110 = Output Scan mode         101 = Brush DC Output mode, forward       100 = Brush DC Output mode, reverse         011 = Reserved       010 = Half-Bridge Output mode         010 = Half-Bridge Output mode       001 = Push-Pull Output mode         000 = Steerable Single Output mode       000 = Steerable Single Output mode         000 = Steerable Single Output mode       000 = Steerable Single Output mode         bit 7-6       Unimplemented: Read as '0'         bit 5       POLACE: CCPx Output Pins, OCXA, OCxC and OCxE, Polarity Control bit         1 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Output pin polarity is active-low       0 = Output pin polarity is active-low         0 = Pins are driven active when a shutdown event occurs       10 = Pins are driven active when a shutdown event occurs         0 = Pins are driven active when a shutdown event occurs       0 = Pins are driven active when a shutdown event occurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 000 <b>= Do no</b>                                                                                    | t extend one-sl  | not Trigger eve | nt             |                      |                      |                        |  |  |  |  |

| <ul> <li>111 = Reserved</li> <li>110 = Output Scan mode</li> <li>101 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, reverse</li> <li>011 = Reserved</li> <li>010 = Half-Bridge Output mode</li> <li>001 = Push-Pull Output mode</li> <li>000 = Steerable Single Output mode</li> <li>000 = Steerable Single Output mode</li> <li>000 = Steerable Single Output mode</li> <li>011 = Output pin polarity is active-low</li> <li>0 = Pins are driven a shutdown event occurs</li> <li>1 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven inactive when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             | bit 11        | •                                                                                                     |                  |                 |                |                      |                      |                        |  |  |  |  |

| <ul> <li>110 = Output Scan mode</li> <li>101 = Brush DC Output mode, forward</li> <li>100 = Brush DC Output mode, reverse</li> <li>011 = Reserved</li> <li>010 = Half-Bridge Output mode</li> <li>001 = Push-Pull Output mode</li> <li>000 = Steerable Single Output Pins, OCXA, OCXC and OCXE, Polarity Control bit</li> <li>1 = Output pin polarity is active-low</li> <li>0 = Output pin polarity is active-logic</li> <li>0 = Output pin polarity is active-logic</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>1 = Pins are driven inactive when a shutdown event occurs</li> <li>0 = Pins are tri-stated when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>1 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>1 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> <li>0 = Pins are driven active when a shutdown event occurs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 10-8      | OUTM<2:0>: PWMx Output Mode Control bits <sup>(1)</sup>                                               |                  |                 |                |                      |                      |                        |  |  |  |  |