#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

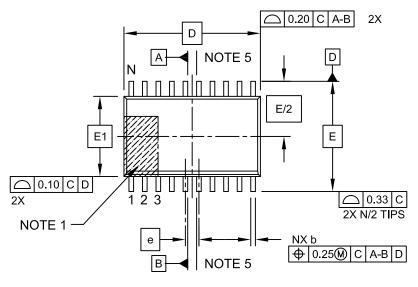

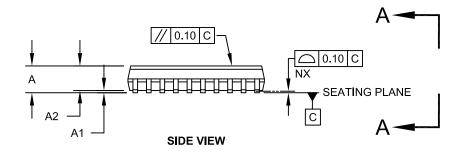

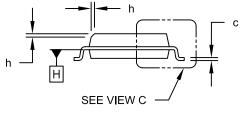

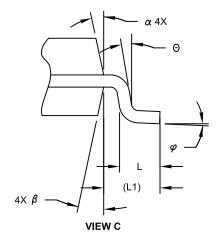

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km202-e-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                            |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  | I                                | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| CN13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I   | ST     | Interrupt-on-Change Inputs |

| CN14     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | Interrupt-on-Change Inputs |

| CN15     | —                                | 22                               | 19            | 9                      | 10             | —                                | 22                               | 19            | 9                      | 10             | I   | ST     | Interrupt-on-Change Inputs |

| CN16     | _                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I   | ST     | Interrupt-on-Change Inputs |

| CN17     | —                                | —                                |               | 3                      | 3              | —                                |                                  | —             | 3                      | 3              | I   | ST     | Interrupt-on-Change Inputs |

| CN18     | —                                | —                                |               | 2                      | 2              | —                                |                                  | —             | 2                      | 2              | I   | ST     | Interrupt-on-Change Inputs |

| CN19     | —                                | —                                |               | 5                      | 5              | —                                |                                  | —             | 5                      | 5              | I   | ST     | Interrupt-on-Change Inputs |

| CN20     | —                                | —                                |               | 4                      | 4              | —                                |                                  | —             | 4                      | 4              | I   | ST     | Interrupt-on-Change Inputs |

| CN21     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | Interrupt-on-Change Inputs |

| CN22     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ST     | Interrupt-on-Change Inputs |

| CN23     | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs |

| CN24     | —                                | 15                               | 12            | 42                     | 46             | —                                | 15                               | 12            | 42                     | 46             | I   | ST     | Interrupt-on-Change Inputs |

| CN25     | _                                | _                                |               | 37                     | 40             | _                                |                                  | _             | 37                     | 40             | I   | ST     | Interrupt-on-Change Inputs |

| CN26     | _                                | _                                |               | 38                     | 41             | _                                |                                  | _             | 38                     | 41             | I   | ST     | Interrupt-on-Change Inputs |

| CN27     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I   | ST     | Interrupt-on-Change Inputs |

| CN28     | —                                | —                                |               | 36                     | 39             | —                                |                                  | —             | 36                     | 39             | I   | ST     | Interrupt-on-Change Inputs |

| CN29     | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | I   | ST     | Interrupt-on-Change Inputs |

| CN30     | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I   | ST     | Interrupt-on-Change Inputs |

| CN31     | —                                | —                                |               | 26                     | 28             | —                                |                                  | —             | 26                     | 28             | I   | ST     | Interrupt-on-Change Inputs |

| CN32     | —                                | —                                |               | 25                     | 27             | —                                |                                  | —             | 25                     | 27             | I   | ST     | Interrupt-on-Change Inputs |

| CN33     | —                                | —                                |               | 32                     | 35             | —                                |                                  | —             | 32                     | 35             | I   | ST     | Interrupt-on-Change Inputs |

| CN34     | _                                | _                                | _             | 35                     | 38             | _                                |                                  | _             | 35                     | 38             | I   | ST     | Interrupt-on-Change Inputs |

| CN35     | _                                | _                                | _             | 12                     | 13             | _                                |                                  | _             | 12                     | 13             | I   | ST     | Interrupt-on-Change Inputs |

| CN36     | _                                | _                                | _             | 13                     | 14             | _                                |                                  | _             | 13                     | 14             | I   | ST     | Interrupt-on-Change Inputs |

| CTCMP    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input      |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

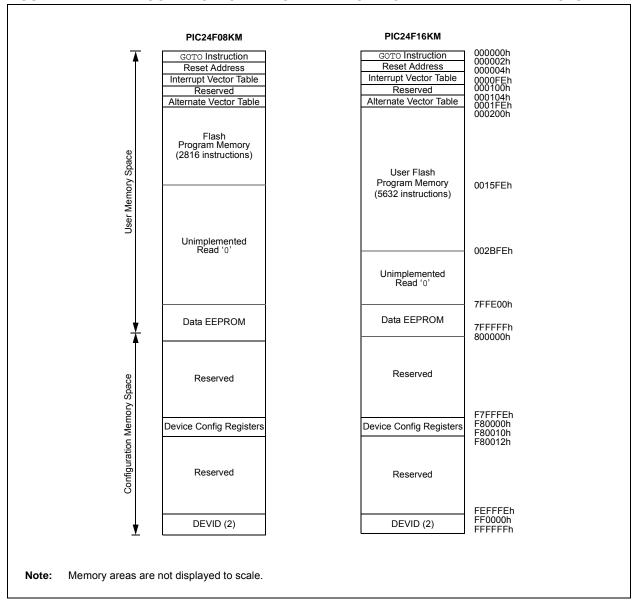

## 4.0 MEMORY ORGANIZATION

As with Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and busing. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 **Program Address Space**

The program address memory space of the PIC24F devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or Data Space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

The user access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FV16KM204 family of devices are displayed in Figure 4-1.

## FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FXXXXX FAMILY DEVICES

### TABLE 4-9: MCCP2 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13               | Bit 12               | Bit 11               | Bit 10               | Bit 9                | Bit 8                | Bit 7        | Bit 6        | Bit 5   | Bit 4                 | Bit 3   | Bit 2   | Bit 1                  | Bit 0      | All<br>Resets |

|-----------|-------|---------|--------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------------|--------------|---------|-----------------------|---------|---------|------------------------|------------|---------------|

| CCP2CON1L | 164h  | CCPON   | _      | CCPSIDL              | r                    | TMRSYNC              | CLKSEL2              | CLKSEL1              | CLKSEL0              | TMRPS1       | TMRPS0       | T32     | CCSEL                 | MOD3    | MOD2    | MOD1                   | MOD0       | 0000          |

| CCP2CON1H | 166h  | OPSSRC  | RTRGEN | _                    | _                    | IOPS3                | IOPS2                | IOPS1                | IOPS0                | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4                 | SYNC3   | SYNC2   | SYNC1                  | SYNC0      | 0000          |

| CCP2CON2L | 168h  | PWMRSEN | ASDGM  |                      | SSDG                 |                      |                      | _                    | _                    | ASDG7        | ASDG6        | ASDG5   | ASDG4                 | ASDG3   | ASDG2   | ASDG1                  | ASDG0      | 0000          |

| CCP2CON2H | 16Ah  | OENSYNC | -      | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN                | ICGSM1       | ICGSM0       | _       | AUXOUT1               | AUXOUT0 | ICSEL2  | ICSEL1                 | ICSEL0     | 0100          |

| CCP2CON3L | 16Ch  | _       | _      | _                    | _                    | _                    | _                    | _                    | _                    | _            |              | DT5     | DT4                   | DT3     | DT2     | DT1                    | DT0        | 0000          |

| CCP2CON3H | 16Eh  | OETRIG  | OSCNT2 | OSCNT1               | OSCNT0               | _                    | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> | _            | _            | POLACE  | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0(1) | 0000          |

| CCP2STATL | 170h  | _       | -      |                      | _                    |                      |                      | _                    | _                    | CCPTRIG      | TRSET        | TRCLR   | ASEVT                 | SCEVT   | ICDIS   | ICOV                   | ICBNE      | 0000          |

| CCP2TMRL  | 174h  |         |        |                      |                      |                      |                      | MCC                  | P2 Time Ba           | ase Register | r Low Word   |         |                       |         |         |                        |            | 0000          |

| CCP2TMRH  | 176h  |         |        |                      |                      |                      |                      | MCC                  | P2 Time Ba           | se Register  | High Word    |         |                       |         |         |                        |            | 0000          |

| CCP2PRL   | 178h  |         |        |                      |                      |                      |                      | MCCP2                | Time Base            | Period Regi  | ister Low Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2PRH   | 17Ah  |         |        |                      |                      |                      |                      | MCCP2                | Time Base I          | Period Regi  | ster High Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2RAL   | 17Ch  |         |        |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word A       |         |                       |         |         |                        |            | 0000          |

| CCP2RBL   | 180h  |         |        |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word B       |         |                       |         |         |                        |            | 0000          |

| CCP2BUFL  | 184h  |         |        |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | Low Word     |         |                       |         |         |                        |            | 0000          |

| CCP2BUFH  | 186h  |         |        |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | High Word    |         |                       |         |         |                        |            | 0000          |

PIC24FV16KM204 FAMILY

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

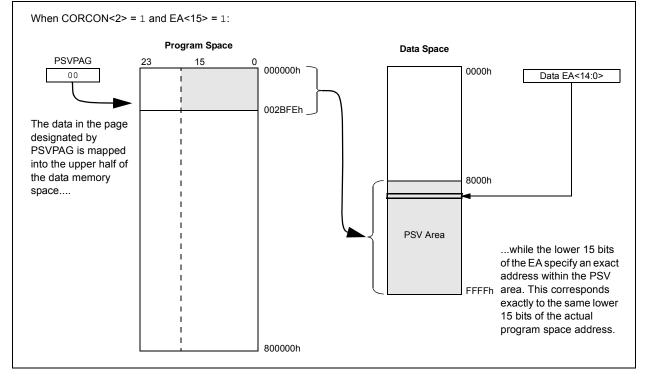

### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of Data Space may optionally be mapped into a 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs if the MSb of the Data Space, EA, is '1' and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the Data Space is determined by the Program Space Visibility Page Address register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of Data Space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each Data Space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | Table Reads/Writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

## FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| ; | Set up NVMCO  | N for row programming operation | ns  |                                       |

|---|---------------|---------------------------------|-----|---------------------------------------|

|   | MOV           | #0x4004, W0                     | ;   |                                       |

|   | MOV           | W0, NVMCON                      | ;   | Initialize NVMCON                     |

| ; | Set up a poir | nter to the first program memor | ry  | location to be written                |

| ; | program memo: | ry selected, and writes enabled | b   |                                       |

|   | MOV           | #0x0000, W0                     | ;   |                                       |

|   | MOV           | W0, TBLPAG                      | ;   | Initialize PM Page Boundary SFR       |

|   | MOV           | #0x1500, W0                     | ;   | An example program memory address     |

| ; | Perform the   | TBLWT instructions to write the | e . | latches                               |

| ; | 0th_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_0, W2                 | ;   |                                       |

|   | MOV           | <pre>#HIGH_BYTE_0, W3</pre>     | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | lst_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_1, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_1, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | 2nd_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_2, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_2, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

| ; | 32nd_program  | —                               |     |                                       |

|   |               | #LOW_WORD_31, W2                | ;   |                                       |

|   |               | #HIGH_BYTE_31, W3               | ;   |                                       |

|   |               | W2, [W0]                        |     | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0]                        | ;   | Write PM high byte into program latch |

| 1 |               |                                 |     |                                       |

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234 // Variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

// Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

// Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

// Write to address low word

__builtin_tblwtl(offset, progData[i++]);

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

## 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the Table Read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location, followed by a TBLRDL instruction.

A typical read sequence, using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and Table Read (builtin\_tblrd1) procedures from the C30 compiler library, is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

## EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

| <pre>intattribute ((space(eedata))) eeData = 0x1234;</pre> |                                       |

|------------------------------------------------------------|---------------------------------------|

| int data;                                                  | // Data read from EEPROM              |

| /*                                                         |                                       |

| The variable eeData must be a Global variable declared     | d outside of any method               |

| the code following this comment can be written inside      | the method that will execute the read |

| */                                                         |                                       |

| unsigned int offset;                                       |                                       |

| // Set up a pointer to the EEPROM location to be e         | erased                                |

| <pre>TBLPAG =builtin_tblpage(&amp;eeData);</pre>           | // Initialize EE Data page pointer    |

| offset =builtin_tbloffset(&eeData);                        | // Initizlize lower word of address   |

| <pre>data =builtin_tblrdl(offset);</pre>                   | // Write EEPROM data to write latch   |

|                                                            |                                       |

#### U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 CNIP2 CNIP1 CNIP0 CMIP2 CMIP1 CMIP0 bit 15 bit 8 U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 BCL1IP2 BCL1IP1 BCL1IP0 SSP1IP2 SSP1IP1 SSP1IP0 \_\_\_\_ \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 Unimplemented: Read as '0' bit 14-12 CNIP<2:0>: Input Change Notification Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 11 Unimplemented: Read as '0' bit 10-8 CMIP<2:0>: Comparator Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled Unimplemented: Read as '0' bit 7 BCL1IP<2:0>: MSSP1 I<sup>2</sup>C<sup>™</sup> Bus Collision Interrupt Priority bits bit 6-4 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 3 Unimplemented: Read as '0' bit 2-0 **SSP1IP<2:0>:** MSSP1 SPI/I<sup>2</sup>C Event Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled

## REGISTER 8-23: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

|                       | R/W-1                                                                                     | R/W-0                                                                                                                                          | R/W-0                                                                 | U-0                                         | R/W-1            | R/W-0           | R/W-0   |

|-----------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------|------------------|-----------------|---------|

| —                     | U2TXIP2                                                                                   | U2TXIP1                                                                                                                                        | U2TXIP0                                                               |                                             | U2RXIP2          | U2RXIP1         | U2RXIP0 |

| bit 15                |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 | bit     |

| U-0                   | R/W-1                                                                                     | R/W-0                                                                                                                                          | R/W-0                                                                 | U-0                                         | R/W-1            | R/W-0           | R/W-0   |

|                       | INT2IP2                                                                                   | INT2IP1                                                                                                                                        | INT2IP0                                                               | _                                           | CCT4IP2          | CCT4IP1         | CCT4IP0 |

| bit 7                 |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 | bit     |

|                       |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

| Legend:<br>R = Readat | ole hit                                                                                   | W = Writable                                                                                                                                   | hit                                                                   | II = Unimple                                | mented bit, read | 1 as '0'        |         |

| -n = Value a          |                                                                                           | '1' = Bit is set                                                                                                                               |                                                                       | '0' = Bit is cle                            |                  | x = Bit is unkr | iown    |

|                       |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

| bit 15                | Unimplemen                                                                                | ted: Read as 'o                                                                                                                                | )'                                                                    |                                             |                  |                 |         |

| bit 14-12             |                                                                                           | : UART2 Trans                                                                                                                                  |                                                                       |                                             |                  |                 |         |

|                       | 111 = Interru                                                                             | pt is Priority 7(                                                                                                                              | highest priority                                                      | interrupt)                                  |                  |                 |         |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

|                       | 001 = Interru                                                                             | pt is Priority 1<br>pt source is dis                                                                                                           | abled                                                                 |                                             |                  |                 |         |

| bit 11                |                                                                                           | ted: Read as '                                                                                                                                 |                                                                       |                                             |                  |                 |         |

| bit 10-8              | -                                                                                         | : UART2 Rece                                                                                                                                   |                                                                       | Priority bits                               |                  |                 |         |

|                       |                                                                                           | pt is Priority 7 (                                                                                                                             |                                                                       |                                             |                  |                 |         |

|                       | •                                                                                         | · · · ·                                                                                                                                        | • • •                                                                 |                                             |                  |                 |         |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

|                       | 001 = Interru                                                                             | pt is Priority 1                                                                                                                               |                                                                       |                                             |                  |                 |         |

|                       | 000 = Interru                                                                             | pt source is dis                                                                                                                               | abled                                                                 |                                             |                  |                 |         |

| bit 7                 | Unimplemen                                                                                | ted: Read as 'o                                                                                                                                |                                                                       |                                             |                  |                 |         |

|                       |                                                                                           |                                                                                                                                                | )'                                                                    |                                             |                  |                 |         |

| bit 6-4               |                                                                                           | External Interr                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |

|                       | 111 = Interru                                                                             |                                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |

|                       |                                                                                           | External Interr                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |

|                       | 111 = Interru<br>•<br>•                                                                   | External Interr<br>pt is Priority 7(                                                                                                           | upt 2 Priority b                                                      |                                             |                  |                 |         |

|                       | 111 = Interru<br>•<br>•<br>001 = Interru                                                  | External Interr<br>pt is Priority 7(<br>pt is Priority 1                                                                                       | upt 2 Priority t<br>highest priority                                  |                                             |                  |                 |         |

| bit 6-4               | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru                                 | External Interr<br>pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                                                                   | upt 2 Priority b<br>highest priority<br>abled                         |                                             |                  |                 |         |

| bit 6-4<br>bit 3      | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                   | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                        | upt 2 Priority b<br>highest priority<br>abled<br>)'                   | v interrupt)                                | av hits          |                 |         |

|                       | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>-: Capture/Com                      | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                        | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>-: Capture/Com                      | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Capture/Com<br>pt is Priority 7 ( | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | ty bits          |                 |         |

## REGISTER 8-26: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

### REGISTER 13-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

| R/W-0         | R/W-0                 | R/W-0                                  | R/W-0                                | U-0                 | R/W-0                | R/W-0                  | R/W-0                  |

|---------------|-----------------------|----------------------------------------|--------------------------------------|---------------------|----------------------|------------------------|------------------------|

| OETRIG        | OSCNT2                | OSCNT1                                 | OSCNT0                               | _                   | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup>   | OUTM0 <sup>(1)</sup>   |

| bit 15        |                       |                                        |                                      |                     |                      |                        | bit 8                  |

|               |                       |                                        |                                      |                     |                      |                        |                        |

| U-0           | U-0                   | R/W-0                                  | R/W-0                                | R/W-0               | R/W-0                | R/W-0                  | R/W-0                  |

|               |                       | POLACE                                 | POLBDF <sup>(1)</sup>                | PSSACE1             | PSSACE0              | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> |

| bit 7         |                       |                                        |                                      |                     |                      |                        | bit C                  |

| Legend:       |                       |                                        |                                      |                     |                      |                        |                        |

| R = Readabl   | le bit                | W = Writable                           | bit                                  | U = Unimplen        | nented bit, read     | d as '0'               |                        |

| -n = Value at | POR                   | '1' = Bit is set                       |                                      | '0' = Bit is cle    |                      | x = Bit is unkn        | own                    |

|               |                       |                                        |                                      |                     |                      |                        | -                      |

| bit 15        | OETRIG: CC            | Px Dead-Time                           | Select bit                           |                     |                      |                        |                        |

|               | 1 = For Trigg         | ered mode (TF                          | RIGEN = 1): Mo                       | dule does not       | drive enabled o      | output pins until      | triggered              |

|               |                       | output pin opera                       |                                      |                     |                      |                        |                        |

| bit 14-12     | OSCNT<2:0>            | : One-Shot Ev                          | ent Count bits                       |                     |                      |                        |                        |

|               |                       |                                        | nt by 7 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 6 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 5 time bas<br>nt by 4 time bas |                     |                      |                        |                        |

|               |                       |                                        | nt by 3 time bas                     |                     |                      |                        |                        |

|               |                       |                                        | nt by 2 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 1 time ba                      |                     |                      |                        |                        |

|               | 000 <b>= Do no</b>    | t extend one-sl                        | not Trigger ever                     | nt                  |                      |                        |                        |

| bit 11        | -                     | ted: Read as '                         |                                      |                     |                      |                        |                        |

| bit 10-8      | OUTM<2:0>:            | PWMx Output                            | Mode Control I                       | oits <sup>(1)</sup> |                      |                        |                        |

|               | 111 = Reserv          |                                        |                                      |                     |                      |                        |                        |

|               | 110 = Output          |                                        | 1. f                                 |                     |                      |                        |                        |

|               |                       | DC Output mod<br>DC Output mod         |                                      |                     |                      |                        |                        |

|               | 011 = Reserv          | •                                      |                                      |                     |                      |                        |                        |

|               | 010 = Half-Br         | idge Output me                         | ode                                  |                     |                      |                        |                        |

|               |                       | Pull Output mod                        |                                      |                     |                      |                        |                        |

|               | 000 <b>= Steera</b> l | ble Single Outp                        | out mode                             |                     |                      |                        |                        |

| bit 7-6       | -                     | ted: Read as '                         |                                      |                     |                      |                        |                        |

| bit 5         |                       | -                                      | s, OCxA, OCxC                        | and OCxE, P         | olarity Control      | bit                    |                        |

|               |                       | in polarity is ac<br>in polarity is ac |                                      |                     |                      |                        |                        |

| bit 4         |                       |                                        | s, OCxB, OCxE                        | and OCxF Po         | plarity Control b    | <sub>Dit</sub> (1)     |                        |

|               |                       | in polarity is ac                      |                                      |                     |                      |                        |                        |

|               |                       | in polarity is ac                      |                                      |                     |                      |                        |                        |

| bit 3-2       | PSSACE<1:0            | >: PWMx Outp                           | out Pins, OCxA                       | , OCxC and O        | CxE, Shutdowr        | State Control b        | oits                   |

|               | 11 = Pins are         | driven active v                        | vhen a shutdow                       | n event occur       | S                    |                        |                        |

|               |                       |                                        | when a shutdo                        |                     | urs                  |                        |                        |

|               |                       |                                        | n a shutdown e                       |                     |                      |                        | (4)                    |

| bit 1-0       |                       |                                        |                                      |                     |                      | State Control b        | oits <sup>(1)</sup>    |

|               |                       |                                        | vhen a shutdov                       |                     |                      |                        |                        |

|               |                       |                                        | when a shutdo                        |                     |                      |                        |                        |

|               | ux = Pins are         | па пуп-тпре                            | dance state wh                       | ien a shuluowi      | i eveni occurs       |                        |                        |

**Note 1:** These bits are implemented in MCCPx modules only.

## REGISTER 14-7: SSPxCON3: MSSPx CONTROL REGISTER 3 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0                                                                                                                                       | U-0                                                                                                                              | U-0                                   | U-0            | U-0                            | U-0              | U-0              | U-0             |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|--------------------------------|------------------|------------------|-----------------|--|--|--|--|

|                                                                                                                                           | _                                                                                                                                | —                                     |                | —                              | —                |                  | —               |  |  |  |  |

| bit 15                                                                                                                                    |                                                                                                                                  |                                       |                |                                |                  |                  | bit             |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  |                                       |                |                                |                  |                  |                 |  |  |  |  |

| R-0                                                                                                                                       | R/W-0                                                                                                                            | R/W-0                                 | R/W-0          | R/W-0                          | R/W-0            | R/W-0            | R/W-0           |  |  |  |  |

| ACKTIM <sup>(1)</sup>                                                                                                                     | PCIE                                                                                                                             | SCIE                                  | BOEN           | SDAHT                          | SBCDE            | AHEN             | DHEN            |  |  |  |  |

| bit 7                                                                                                                                     |                                                                                                                                  |                                       |                |                                |                  |                  | bit (           |  |  |  |  |

| 1                                                                                                                                         |                                                                                                                                  |                                       |                |                                |                  |                  |                 |  |  |  |  |

| Legend:                                                                                                                                   | , hit                                                                                                                            | M = Mritable k                        |                |                                | opted bit read   |                  |                 |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |                                                                                                                                  |                                       |                |                                |                  |                  |                 |  |  |  |  |

|                                                                                                                                           | FUR                                                                                                                              | '1' = Bit is set                      |                |                                | areu             | X - DILISUIK     | nown            |  |  |  |  |

| bit 15-8                                                                                                                                  | Unimplemen                                                                                                                       | ted: Read as '0                       | 3              |                                |                  |                  |                 |  |  |  |  |

| bit 7                                                                                                                                     | -                                                                                                                                | knowledge Time                        |                |                                |                  |                  |                 |  |  |  |  |

|                                                                                                                                           | 1 = Indicates                                                                                                                    | the I <sup>2</sup> C bus is ir        | an Acknowlee   |                                |                  |                  | the SCLx cloc   |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | knowledge seq                         |                | d on the 9 <sup>th</sup> risii | ng edge of the   | SCLx clock       |                 |  |  |  |  |

| bit 6                                                                                                                                     |                                                                                                                                  | ondition Interrup                     |                |                                |                  |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | nterrupt on dete                      |                |                                |                  |                  |                 |  |  |  |  |

| bit 5                                                                                                                                     | <ul> <li>0 = Stop detection interrupts are disabled<sup>(2)</sup></li> <li>SCIE: Start Condition Interrupt Enable bit</li> </ul> |                                       |                |                                |                  |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | nterrupt on dete                      |                | t or Restart cor               | dition           |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | ction interrupts                      |                |                                |                  |                  |                 |  |  |  |  |

| bit 4                                                                                                                                     | BOEN: Buffer                                                                                                                     | r Overwrite Ena                       | ble bit        |                                |                  |                  |                 |  |  |  |  |

|                                                                                                                                           | I <sup>2</sup> C Master m                                                                                                        |                                       |                |                                |                  |                  |                 |  |  |  |  |

|                                                                                                                                           | This bit is igno<br>I <sup>2</sup> C Slave mo                                                                                    |                                       |                |                                |                  |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | F is updated and                      | d an ACK is ge | enerated for a re              | eceived addres   | s/data byte, igr | noring the stat |  |  |  |  |

|                                                                                                                                           | of the SS                                                                                                                        | SPOV bit only if                      | the BF bit = 0 |                                |                  |                  | •               |  |  |  |  |

| L:1 0                                                                                                                                     |                                                                                                                                  | F is only update                      |                | IV is clear                    |                  |                  |                 |  |  |  |  |

| bit 3                                                                                                                                     |                                                                                                                                  | x Hold Time Se<br>of 300 ns hold t    |                | ofter the folling              |                  |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | of 100 ns hold t                      |                |                                |                  |                  |                 |  |  |  |  |

| bit 2                                                                                                                                     |                                                                                                                                  | ve Mode Bus Co                        |                | -                              | -                |                  |                 |  |  |  |  |

|                                                                                                                                           | 1 = Enables s                                                                                                                    | ave bus collision                     | on interrupts  |                                |                  |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | s collision interru                   | •              |                                |                  |                  |                 |  |  |  |  |

| bit 1                                                                                                                                     |                                                                                                                                  | ess Hold Enable                       | -              | • •                            |                  |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | g the 8th falling<br>N1 register will |                |                                |                  | ddress byte;     | CKP bit of the  |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | holding is disab                      |                |                                |                  |                  |                 |  |  |  |  |

| bit 0                                                                                                                                     | DHEN: Data                                                                                                                       | Hold Enable bit                       | (Slave mode of | only)                          |                  |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | g the 8th falling                     | -              |                                | lata byte; slave | hardware clea    | ars the CKP bi  |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  | SPxCON1 regist<br>ding is disabled    | er and SCLx is | s held low                     |                  |                  |                 |  |  |  |  |

|                                                                                                                                           |                                                                                                                                  |                                       |                |                                |                  |                  |                 |  |  |  |  |

| Note 1: Th                                                                                                                                |                                                                                                                                  | fect in Slave mo                      |                |                                |                  |                  |                 |  |  |  |  |

2: The ACKTIM status bit is active only when the AHEN bit or DHEN bit is set.

'1' = Bit is set

## REGISTER 14-8: SSPxADD: MSSPx SLAVE ADDRESS/BAUD RATE GENERATOR REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0                                | U-0   | U-0   | U-0   |  |  |  |

|--------------|-------|--------------|-------|------------------------------------|-------|-------|-------|--|--|--|

| —            | —     | —            |       | —                                  | _     | —     | _     |  |  |  |

| bit 15       |       |              |       |                                    |       |       | bit 8 |  |  |  |

|              |       |              |       |                                    |       |       |       |  |  |  |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |  |

| ADD7         | ADD6  | ADD5         | ADD4  | ADD3                               | ADD2  | ADD1  | ADD0  |  |  |  |

| bit 7        |       |              |       |                                    |       |       | bit 0 |  |  |  |

|              |       |              |       |                                    |       |       |       |  |  |  |

| Legend:      |       |              |       |                                    |       |       |       |  |  |  |

| R = Readable | e bit | W = Writable | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |  |  |

'0' = Bit is cleared

x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0

ADD<7:0>: Slave Address/Baud Rate Generator Value bits

SPI Master and I<sup>2</sup>C™ Master modes:

Reload value for the Baud Rate Generator. Clock period is (([SPxADD] + 1) \* 2)/Fosc.

I<sup>2</sup>C Slave modes:

Represents 7 or 8 bits of the slave address, depending on the addressing mode used:

7-Bit mode:

Address is ADD<7:1>; ADD<0> is ignored.

10-Bit LSb mode:

ADD<7:0> are the Least Significant bits of the address.

10-Bit MSb mode:

ADD<2:1> are the two Most Significant bits of the address; ADD<7:3> are always '11110' as a specification requirement; ADD<0> is ignored.

## REGISTER 14-9: SSPxMSK: I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(1)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-8 | Unimplemented: Read as '0'                              |

|----------|---------------------------------------------------------|

| bit 7-0  | MSK<7:0>: Slave Address Mask Select bits <sup>(1)</sup> |

|          | 1 = Masking of corresponding bit of SSPxADD is enabled  |

|          | 0 = Masking of corresponding bit of SSPxADD is disabled |

Note 1: MSK0 is not used as a mask bit in 7-bit addressing.

## REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER

| R/W-0                   | R/W-0        | R/W-0                             | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|-------------------------|--------------|-----------------------------------|------------------|------------------|------------------|-----------------|-------|

| G4D4T                   | G4D4N        | G4D3T                             | G4D3N            | G4D2T            | G4D2N            | G4D1T           | G4D1N |

| bit 15                  |              |                                   |                  |                  |                  |                 | bit 8 |

|                         |              |                                   |                  |                  |                  |                 |       |

| R/W-0                   | R/W-0        | R/W-0                             | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| G3D4T                   | G3D4N        | G3D3T                             | G3D3N            | G3D2T            | G3D2N            | G3D1T           | G3D1N |