#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-><F

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

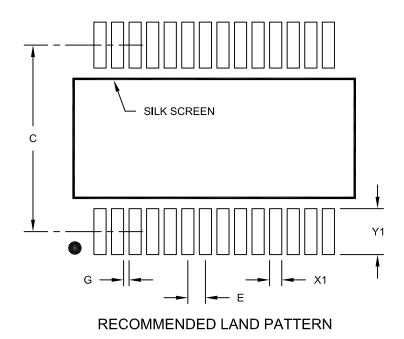

| Mounting Type              | Surface Mount                                                                |

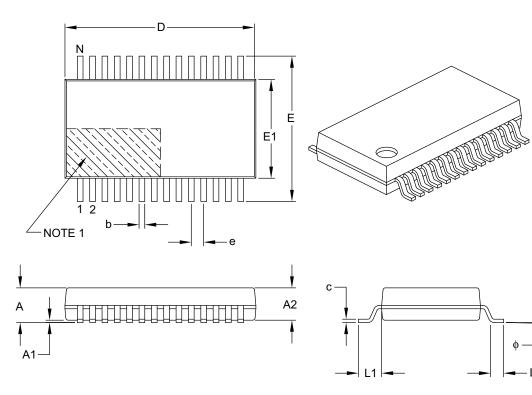

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km202-e-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                |      | N                     | lemory       | 1               |                   |              |                  |      |      | Pe                  | riphe     | rals   |             |      |      |     |           |

|----------------|------|-----------------------|--------------|-----------------|-------------------|--------------|------------------|------|------|---------------------|-----------|--------|-------------|------|------|-----|-----------|

| Device         | Pins | Flash Program (bytes) | SRAM (bytes) | EE Data (bytes) | Voltage Range (V) | 16-Bit Timer | 16-Bit MCCP/SCCP | MSSP | UART | 12-Bit A/D Channels | 8-Bit DAC | Op Amp | Comparators | CTMU | RTCC | CLC | ICD BRKPT |

|                |      |                       |              |                 |                   | 5V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24FV16KM204 | 44   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM202 | 28   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM204 | 44   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM202 | 28   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM104 | 44   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 22                  | —         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV16KM102 | 28   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM102 | 28   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM101 | 20   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 16                  | _         | -      | 1           | Yes  | _    | 1   | 3         |

|                |      |                       |              |                 |                   | 3V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24F16KM204  | 44   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM202  | 28   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM204  | 44   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM202  | 28   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM104  | 44   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 22                  | _         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F16KM102  | 28   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24F08KM102  | 28   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | —         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F08KM101  | 20   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 16                  |           |        | 1           | Yes  | _    | 1   | 3         |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                            |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  | I                                | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| CN13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I   | ST     | Interrupt-on-Change Inputs |

| CN14     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | Interrupt-on-Change Inputs |

| CN15     | —                                | 22                               | 19            | 9                      | 10             | —                                | 22                               | 19            | 9                      | 10             | I   | ST     | Interrupt-on-Change Inputs |

| CN16     | _                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I   | ST     | Interrupt-on-Change Inputs |

| CN17     | —                                | —                                |               | 3                      | 3              | —                                |                                  | —             | 3                      | 3              | I   | ST     | Interrupt-on-Change Inputs |

| CN18     | —                                | —                                |               | 2                      | 2              | —                                |                                  | —             | 2                      | 2              | I   | ST     | Interrupt-on-Change Inputs |

| CN19     | —                                | —                                |               | 5                      | 5              | —                                |                                  | —             | 5                      | 5              | I   | ST     | Interrupt-on-Change Inputs |

| CN20     | —                                | —                                |               | 4                      | 4              | —                                |                                  | —             | 4                      | 4              | I   | ST     | Interrupt-on-Change Inputs |

| CN21     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | Interrupt-on-Change Inputs |

| CN22     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ST     | Interrupt-on-Change Inputs |

| CN23     | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs |

| CN24     | —                                | 15                               | 12            | 42                     | 46             | —                                | 15                               | 12            | 42                     | 46             | I   | ST     | Interrupt-on-Change Inputs |

| CN25     | _                                | _                                |               | 37                     | 40             | _                                |                                  | _             | 37                     | 40             | I   | ST     | Interrupt-on-Change Inputs |

| CN26     | _                                | _                                |               | 38                     | 41             | _                                |                                  | _             | 38                     | 41             | I   | ST     | Interrupt-on-Change Inputs |

| CN27     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I   | ST     | Interrupt-on-Change Inputs |

| CN28     | —                                | —                                |               | 36                     | 39             | —                                |                                  | —             | 36                     | 39             | I   | ST     | Interrupt-on-Change Inputs |

| CN29     | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | I   | ST     | Interrupt-on-Change Inputs |

| CN30     | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I   | ST     | Interrupt-on-Change Inputs |

| CN31     | —                                | —                                |               | 26                     | 28             | —                                |                                  | —             | 26                     | 28             | I   | ST     | Interrupt-on-Change Inputs |

| CN32     | —                                | —                                |               | 25                     | 27             | —                                |                                  | —             | 25                     | 27             | I   | ST     | Interrupt-on-Change Inputs |

| CN33     | —                                | —                                |               | 32                     | 35             | —                                |                                  | —             | 32                     | 35             | I   | ST     | Interrupt-on-Change Inputs |

| CN34     | _                                | _                                | _             | 35                     | 38             | _                                |                                  | _             | 35                     | 38             | I   | ST     | Interrupt-on-Change Inputs |

| CN35     | _                                | _                                | _             | 12                     | 13             | _                                |                                  | _             | 12                     | 13             | I   | ST     | Interrupt-on-Change Inputs |

| CN36     | _                                | _                                | _             | 13                     | 14             | _                                |                                  | _             | 13                     | 14             | I   | ST     | Interrupt-on-Change Inputs |

| CTCMP    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input      |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with Data Memory Space Addressing and makes it possible to access data in the program memory space.

### 4.1.2 HARD MEMORY VECTORS

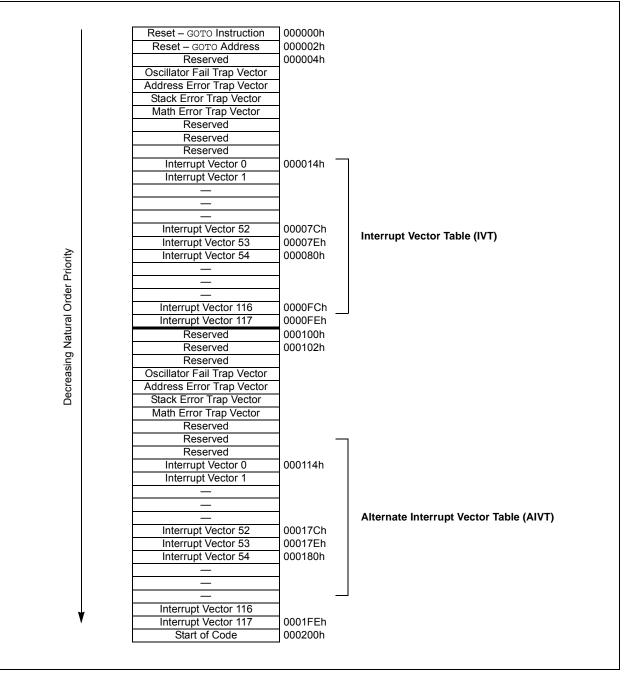

All PIC24F devices reserve the addresses between 00000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables, located from 000004h to 0000FFh, and 000104h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. **Section 8.1 "Interrupt Vector Table (IVT)**" discusses the Interrupt Vector Tables in more detail.

# 4.1.3 DATA EEPROM

In the PIC24FV16KM204 family, the data EEPROM is mapped to the top of the user program memory space, starting at address, 7FFE00, and expanding up to address, 7FFFF.

The data EEPROM is organized as 16-bit-wide memory and 256 words deep. This memory is accessed using Table Read and Write operations similar to the user code memory.

# 4.1.4 DEVICE CONFIGURATION WORDS

Table 4-1 provides the addresses of the device Configuration Words for the PIC24FV16KM204 family. Their location in the memory map is displayed in Figure 4-1.

Refer to **Section 25.1** "**Configuration Bits**" for more information on device Configuration Words.

# TABLE 4-1: DEVICE CONFIGURATION WORDS FOR PIC24FXXXXX FAMILY DEVICES

| Configuration Word | Configuration Word<br>Addresses |

|--------------------|---------------------------------|

| FBS                | F80000                          |

| FGS                | F80004                          |

| FOSCSEL            | F80006                          |

| FOSC               | F80008                          |

| FWDT               | F8000A                          |

| FPOR               | F8000C                          |

| FICD               | F8000E                          |

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION msw most significant word least significant word PC Address (Isw Address) Address 16 8 Λ 23 000000h 000001h 00000000 0000000 000002h 000003h 000004h 00000000 000005h 0000000 000006h 000007h Instruction Width Program Memory Phantom' Byte (read as '0')

### TABLE 4-21: PORTA REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 <sup>(4,5)</sup> | Bit 10 <sup>(4,5)</sup> | Bit 9 <sup>(4,5)</sup> | Bit 8 <sup>(4,5)</sup> | Bit 7 <sup>(4)</sup> | Bit 6 <sup>(3)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|--------|--------|--------|--------|-------------------------|-------------------------|------------------------|------------------------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|---------------------|

| TRISA     | 2C0h  |        | _      | _      | _      | TRISA11                 | TRISA10                 | TRISA9                 | TRISA8                 | TRISA7               | TRISA6               | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 0FDF <sup>(1)</sup> |

| PORTA     | 2C2h  | -      | —      | —      |        | RA11                    | RA10                    | RA9                    | RA8                    | RA7                  | RA6                  | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx                |

| LATA      | 2C4h  | -      | —      | —      |        | LATA11                  | LATA10                  | LATA9                  | LATA8                  | LATA7                | LATA6                | _                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx                |

| ODCA      | 2C6h  | _      | —      | _      | _      | ODA11                   | ODA10                   | ODA9                   | ODA8                   | ODA7                 | ODA6                 | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are only available when MCLRE (FPOR<7>) = 0.

3: These bits are not implemented in FV devices.

4: These bits are not implemented in 20-pin devices.

5: These bits are not implemented in 28-pin devices.

## TABLE 4-22: PORTB REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7  | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|--------|----------------------|----------------------|--------|----------------------|--------|--------|--------|---------------------|

| TRISB     | 2C8h  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7 | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2 | TRISB1 | TRISB0 | <sub>FFFF</sub> (1) |

| PORTB     | 2CAh  | RB15    | RB14    | RB13    | RB12    | RB11                  | RB10                  | RB9    | RB8    | RB7    | RB6                  | RB5                  | RB4    | RB3                  | RB2    | RB1    | RB0    | xxxx                |

| LATB      | 2CCh  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11                | LATB10                | LATB9  | LATB8  | LATB7  | LATB6                | LATB5                | LATB4  | LATB3                | LATB2  | LATB1  | LATB0  | xxxx                |

| ODCB      | 2CEh  | ODB15   | ODB14   | ODB13   | ODB12   | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7   | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2   | ODB1   | ODB0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

### TABLE 4-23: PORTC REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 <sup>(2,3)</sup> | Bit 8 <sup>(2,3)</sup> | Bit 7 <sup>(2,3)</sup> | Bit 6 <sup>(2,3)</sup> | Bit 5 <sup>(2,3)</sup> | Bit 4 <sup>(2,3)</sup> | Bit 3 <sup>(2,3)</sup> | Bit 2 <sup>(2,3)</sup> | Bit 1 <sup>(2,3)</sup> | Bit 0 <sup>(2,3)</sup> | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------|

| TRISC        | 2D0h  |        | _      |        | _      | —      | _      | TRISC9                 | TRISC8                 | TRISC7                 | TRISC6                 | TRISC5                 | TRISC4                 | TRISC3                 | TRISC2                 | TRISC1                 | TRISC0                 | 03FF <sup>(1)</sup> |

| PORTC        | 2D2h  | —      | _      | _      | -      | —      | _      | RC9                    | RC8                    | RC7                    | RC6                    | RC5                    | RC4                    | RC3                    | RC2                    | RC1                    | RC0                    | xxxx                |

| LATTC        | 2D4h  | —      | _      | _      | -      | —      | _      | LATC9                  | LATC8                  | LATC7                  | LATC6                  | LATC5                  | LATC4                  | LATC3                  | LATC2                  | LATC1                  | LATC0                  | xxxx                |

| ODCC         | 2D6h  | _      | _      | —      | -      | —      | _      | ODC9                   | ODC8                   | ODC7                   | ODC6                   | ODC5                   | ODC4                   | ODC3                   | ODC2                   | ODC1                   | ODC0                   | 0000                |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

**2:** These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

# REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | —   | —   | —   | —     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

|            |       |       |                        |     |     |     |       |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearable b  | it               |

|----------------------|------------------------|----------------------------|------------------|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit           | W = Writable bit |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit, rea | d as '0'         |

| bit 15   | WR: Write Control bit                                                                                                                                                                                                        |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Initiates a Flash memory program or erase operation; the operation is self-timed and the bit is                                                                                                                          |

|          | cleared by hardware once the operation is complete                                                                                                                                                                           |

|          | <ul><li>0 = Program or erase operation is complete and inactive</li></ul>                                                                                                                                                    |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                       |

|          | 1 = Enables Flash program/erase operations                                                                                                                                                                                   |

|          | 0 = Inhibits Flash program/erase operations                                                                                                                                                                                  |

| bit 13   | WRERR: Write Sequence Error Flag bit                                                                                                                                                                                         |

|          | 1 = An improper program or erase sequence attempt, or termination has occurred (bit is set automatically                                                                                                                     |

|          | on any set attempt of the WR bit)                                                                                                                                                                                            |

|          | 0 = The program or erase operation completed normally                                                                                                                                                                        |

| bit 12   | PGMONLY: Program Only Enable bit <sup>(4)</sup>                                                                                                                                                                              |

| bit 11-7 | Unimplemented: Read as '0'                                                                                                                                                                                                   |

| bit 6    | ERASE: Erase/Program Enable bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Performs the erase operation specified by the NVMOP&lt;5:0&gt; bits on the next WR command</li> <li>0 = Performs the program operation specified by the NVMOP&lt;5:0&gt; bits on the next WR command</li> </ul> |

| bit 5-0  | NVMOP<5:0>: Programming Operation Command Byte bits <sup>(1)</sup>                                                                                                                                                           |

|          | Erase Operations (when ERASE bit is '1'):                                                                                                                                                                                    |

|          | 1010xx = Erase entire boot block (including code-protected boot block) <sup>(2)</sup>                                                                                                                                        |

|          | 1001xx = Erase entire memory (including boot block, configuration block, general block) <sup>(2)</sup>                                                                                                                       |

|          | 011010 = Erase 4 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                         |

|          | 011001 = Erase 2 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                         |

|          | 011000 = Erase 1 row of Flash memory <sup>(3)</sup>                                                                                                                                                                          |

|          | 0101xx = Erase entire configuration block (except code protection bits)                                                                                                                                                      |

|          | 0100xx = Erase entire data EEPROM <sup>(4)</sup>                                                                                                                                                                             |

|          | 0011xx = Erase entire general memory block programming operations                                                                                                                                                            |

|          | 0001xx = Write 1 row of Flash memory (when ERASE bit is '0') <sup>(3)</sup>                                                                                                                                                  |

| Note 1:  | All other combinations of NVMOP<5:0> are no operation.                                                                                                                                                                       |

| 2:       | Available in ICSP™ mode only. Refer to the device programming specification.                                                                                                                                                 |

| 2.       | The address in the Table Deinter decides which rows will be created                                                                                                                                                          |

- 3: The address in the Table Pointer decides which rows will be erased.

- 4: This bit is used only while accessing data EEPROM.

FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE

| U-0         U-0         U-0         U-0         U-0         U-0         U-0           -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <t< th=""><th>REGISTER</th><th>9-2: CLKL</th><th>DIV: CLOCK L</th><th></th><th>6151EK</th><th></th><th></th><th></th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | REGISTER | 9-2: CLKL                                                                                                                                                                                                                                                        | DIV: CLOCK L                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | 6151EK               |                  |                  |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------|

| bit 15       bit 1         U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -         bit 7       bit 10       U-0       U-0       U-0       U-0         Egend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       RO: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE       DOZE       2:0: CPU and Peripheral Clock Ratio Select bits       111 = 1:28         110 = 1:4       101 = 1:28       100 = 1:16       112       100 = 1:16         011 = 1:1       DOZE       2:0: CPU and peripheral clock ratio are set to 1:1       111 = 13:25 kHz (divide-by-26)         110 = 125 kHz (divide-by-32)       100 = 2:0: CPU and peripheral clock ratio are set to 1:1       111 = 31:25 kHz (divide-by-32)         101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)         101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)         101 = 156 kHz (d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0    | R/W-0                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                          | R/W-1                                                                                                            |                      | R/W-0            | R/W-0            | R/W-1  |

| U-0         U-0         U-0         U-0         U-0         U-0         U-0           -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ROI      | DOZE2                                                                                                                                                                                                                                                            | DOZE1                                                                                                                                                                                                                                                                                                                          | DOZE0                                                                                                            | DOZEN <sup>(1)</sup> | RCDIV2           | RCDIV1           | RCDIV0 |

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 15   |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  | bit 8  |

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11.0     | 11.0                                                                                                                                                                                                                                                             | 11.0                                                                                                                                                                                                                                                                                                                           | 11.0                                                                                                             | 11.0                 | 11.0             | 11.0             | 11.0   |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>bit 14-12 DOZE-2:0-: CPU and Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>110 = 1:132<br>100 = 1:16<br>011 = 1:3<br>100 = 1:16<br>011 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE-2:0-> bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10-8 RCDIV-2:0->: FRC Postscaler Select bits<br>When COSC-2:0-> (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-2)<br>100 = 500 kHz (divide-by-2)<br>100 = 2 MHz (divide-by-2) - default<br>001 = 4 MHz (divide-by-2) - default<br>001 = 4 MHz (divide-by-2)<br>100 = 8 MHz (divide-by-2)<br>100 = 15 kHz (divide-by-2)<br>100 = 15 kHz (divide-by-2)<br>100 = 125 kHz (divide-by-   | 0-0      | 0-0                                                                                                                                                                                                                                                              | 0-0                                                                                                                                                                                                                                                                                                                            | 0-0                                                                                                              | 0-0                  | 0-0              | 0-0              | 0-0    |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE-2:0>: CPU and Peripheral Clock Ratio Select bits       111 = 1:128         101 = 1:64       101 = 1:32       100 = 1:16         001 = 1:1       000 = 1:11       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE<2:0>: Dits specify the CPU and peripheral clock ratio       0 = CPU and peripheral clock ratio are set to 1:1         bit 10       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE         1 = 1:2       000 = 1:1       111 = 31.25 kHz (divide-by-256)         1 = 250 kHz (divide-by-256)       111 = 31.25 kHz (divide-by-256)         1 = 255 kHz (divide-by-32)       100 = 500 kHz (divide-by-32)         1 = 1 = 255 kHz (divide-by-32)       100 = 2 MHz (divide-by-41)         1 = 1 = 152 kHz (divide-by-32)       100 = 2 MHz (divide-by-32)         1 = 1 = 15 kHz (divide-by-32)       110 = 15.62 kHz (divide-by-256)         1 = 1 = 12 + 12 (divide-by-41)       111 = 1.5 kHz (divide-by-42)         1 = 1 = 1 = 1.5 kHz (divide-by-22) - default       100 = 8 MHz (divide-by-42) = 110: </td <td>bit 7</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>bit 0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  | bit 0  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE-2:0>: CPU and Peripheral Clock Ratio Select bits       111 = 1:128         101 = 1:64       101 = 1:32       100 = 1:16         001 = 1:1       000 = 1:11       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE<2:0>: Dits specify the CPU and peripheral clock ratio       0 = CPU and peripheral clock ratio are set to 1:1         bit 10       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE         1 = 1:2       000 = 1:1       111 = 31.25 kHz (divide-by-256)         1 = 250 kHz (divide-by-256)       111 = 31.25 kHz (divide-by-256)         1 = 255 kHz (divide-by-32)       100 = 500 kHz (divide-by-32)         1 = 1 = 255 kHz (divide-by-32)       100 = 2 MHz (divide-by-41)         1 = 1 = 152 kHz (divide-by-32)       100 = 2 MHz (divide-by-32)         1 = 1 = 15 kHz (divide-by-32)       110 = 15.62 kHz (divide-by-256)         1 = 1 = 12 + 12 (divide-by-41)       111 = 1.5 kHz (divide-by-42)         1 = 1 = 1 = 1.5 kHz (divide-by-22) - default       100 = 8 MHz (divide-by-42) = 110: </td <td>Logondu</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Logondu  |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  |        |

| <pre>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 ROI: Recover on Interrupt bit 1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1 0 = Interrupts have no effect on the DOZEN bit bit 14-12 DOZE-2:0&gt;: CPU and Peripheral Clock Ratio Select bits 111 = 1:128 110 = 1:64 101 = 1:32 100 = 1:1 001 = 1:4 001 = 1:2 000 = 1:1 bit 11 DOZEN: Doze Enable bit<sup>(1)</sup> 1 = DOZE-2:0&gt; bits specify the CPU and peripheral clock ratio 0 = CPU and peripheral clock ratio are set to 1:1 bit 10-8 RCDIVe2:0&gt;: FRC Postscaler Select bits When COSC&lt;2:0&gt; (OSCCON(14:12&gt;) = 111: 111 = 31.25 kHz (divide-by-266) 110 = 125 kHz (divide-by-4) 011 = 150 kHz (divide-by-4) 011 = 150 kHz (divide-by-4) 011 = 15.8 kHz (divide-by-4) 011 = 15.8 kHz (divide-by-4) 101 = 15.62 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-4) 011 = 62.5 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 02.5 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 02.5 kHz (divide-by-4) 011 = 1.5 kHz (divide-by-4) 011 = 0.5 kHz (divide</pre>                                                                                                            | -        | le bit                                                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                                   | bit                                                                                                              | U = Unimplem         | nented bit, read | d as '0'         |        |

| bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>DOZE-2:00: CPU and Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE-2:00: bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10-8 RCDV-2:00: FRC Postscaler Select bits<br>When COSC-2:00: (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-29)<br>011 = 1 MHz (divide-by-2) - default<br>000 = 8 MHz (divide-by-2) - default<br>101 = 25 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 7.81 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-2) - default<br>001 = 125 kHz (divide-by-2) - default<br>001 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 7.81 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-4)<br>011 = 62.5 kHz (divide-by-4)<br>011 = 50.5 kHz (divide-by-4)<br>011 = 15.5 kHz (divide-by-4)<br>011 = 15.5 kHz (divide-by-4)<br>011 = 62.5 kHz (divide-by-4)<br>011 = 6 |          |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  | -                    |                  |                  | nown   |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 1 = Interrupts<br>0 = Interrupts                                                                                                                                                                                                                                 | s clear the DOZ<br>s have no effect                                                                                                                                                                                                                                                                                            | EN bit, and re<br>t on the DOZE                                                                                  | N bit                | d peripheral cl  | ock ratio to 1:1 |        |

| 1 = DOZE<2:0> bits specify the CPU and peripheral clock ratio 0 = CPU and peripheral clock ratio are set to 1:1 bit 10-8 $RCDIV<2:0>: FRC Postscaler Select bits When COSC<2:0> (OSCCON<14:12>) = 111: 111 = 31.25 kHz (divide-by-256) 110 = 125 kHz (divide-by-264) 101 = 250 kHz (divide-by-32) 100 = 500 kHz (divide-by-32) 100 = 500 kHz (divide-by-4) 011 = 1 MHz (divide-by-4) 010 = 2 MHz (divide-by-2) - default 000 = 8 MHz (divide-by-2) 100 = 8 MHz (divide-by-2) = 110: 111 = 1.95 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-32) 100 = 31.25 kHz (divide-by-3) 100 = 31.25 kHz (divide-by-4) 011 = 125 kHz (divide-by-4) 010 = 125 kHz (divide-by-4) 010 = 125 kHz (divide-by-2) - default 000 = 500 kHz (divide-by-1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  |        |

| bit 10-8 <b>RCDIV-2:0&gt;:</b> FRC Postscaler Select bits<br>When COSC<2:0> (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-64)<br>101 = 250 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-16)<br>011 = 1 MHz (divide-by-8)<br>010 = 2 MHz (divide-by-8)<br>010 = 2 MHz (divide-by-2) – default<br>000 = 8 MHz (divide-by-2) – default<br>000 = 8 MHz (divide-by-1)<br>When COSC<2:0> (OSCCON<14:12>) = 110:<br>111 = 1.95 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 31.25 kHz (divide-by-32)<br>100 = 31.25 kHz (divide-by-8)<br>011 = 62.5 kHz (divide-by-8)<br>010 = 125 kHz (divide-by-4)<br>011 = 250 kHz (divide-by-2) – default<br>000 = 500 kHz (divide-by-1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 11   | 1 = DOZE<2                                                                                                                                                                                                                                                       | :0> bits specify                                                                                                                                                                                                                                                                                                               |                                                                                                                  |                      | ratio            |                  |        |