#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-><F

| Detuils                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km202-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Pin Diagrams (Continued)

|     | 20-Pin QFN<br>$\begin{array}{c ccccccccccccccccccccccccccccccccccc$              |

|-----|----------------------------------------------------------------------------------|

| Dia | Pin Features                                                                     |

| Pin | PIC24F08KM101 PIC24FV08KM101                                                     |

| 1   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0                                         |

| 2   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                                                   |

| 3   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                                                    |

| 4   | OSCI/CLKI/AN13/C1INB/CN30/RA2                                                    |

| 5   | OSCO/CLKO/AN14/C1INA/CN29/RA3                                                    |

| 6   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4                                                  |

| 7   | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/RA4                                    |

| 8   | AN19/U1TX/CTED1/INT0/CN23/RB7 AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7             |

| 9   | AN20/SCL1/UICTS/OC1B/CTED10/CN22/RB8                                             |

| 10  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4/CN21/RB9                             |

| 11  | IC1/OC1A/INT2/CN8/RA6 VCAP OR VDDCORE                                            |

| 12  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12 AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |

| 13  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13                                              |

| 14  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RB14                                  |

| 15  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15                                               |

| 16  | Vss/AVss                                                                         |

| 17  | Vdd/AVdd                                                                         |

| 18  | MCLR/Vpp/RA5                                                                     |

| 19  | PGEC2/CVREF+ /VREF+/AN0/CN2/RA0                                                  |

| 20  | PGED2/CVReF-/VReF-/AN1/CN3/RA1                                                   |

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                 |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------|

|          |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                                 |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                     |

| RB9      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | ST     | PORTB Pins                      |

| RB10     | —                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I/O | ST     | PORTB Pins                      |

| RB11     | —                                | 22                               | 19            | 9                      | 10             | _                                | 22                               | 19            | 9                      | 10             | I/O | ST     | PORTB Pins                      |

| RB12     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I/O | ST     | PORTB Pins                      |

| RB13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I/O | ST     | PORTB Pins                      |

| RB14     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I/O | ST     | PORTB Pins                      |

| RB15     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I/O | ST     | PORTB Pins                      |

| RC0      | —                                | _                                |               | 25                     | 27             | _                                |                                  |               | 25                     | 27             | I/O | ST     | PORTC Pins                      |

| RC1      | —                                | _                                | _             | 26                     | 28             | _                                | _                                | _             | 26                     | 28             | I/O | ST     | PORTC Pins                      |

| RC2      | —                                | _                                | _             | 27                     | 29             | _                                | _                                | _             | 27                     | 29             | I/O | ST     | PORTC Pins                      |

| RC3      | —                                | _                                | _             | 36                     | 39             | _                                | _                                | _             | 36                     | 39             | I/O | ST     | PORTC Pins                      |

| RC4      | —                                | _                                | _             | 37                     | 40             | _                                | _                                | _             | 37                     | 40             | I/O | ST     | PORTC Pins                      |

| RC5      | —                                | _                                | _             | 38                     | 41             | _                                | _                                | _             | 38                     | 41             | I/O | ST     | PORTC Pins                      |

| RC6      | —                                | _                                | _             | 2                      | 2              | _                                | _                                | _             | 2                      | 2              | I/O | ST     | PORTC Pins                      |

| RC7      | —                                | _                                | _             | 3                      | 3              | _                                | _                                | _             | 3                      | 3              | I/O | ST     | PORTC Pins                      |

| RC8      | —                                | _                                | _             | 4                      | 4              | _                                | _                                | _             | 4                      | 4              | I/O | ST     | PORTC Pins                      |

| RC9      | —                                | _                                | _             | 5                      | 5              | _                                | _                                | _             | 5                      | 5              | I/O | ST     | PORTC Pins                      |

| REFO     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | 0   | _      | Reference Clock Output          |

| RTCC     | —                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | _      | Real-Time Clock/Calendar Output |

| SCK1     | 15                               | 22                               | 19            | 9                      | 10             | 15                               | 22                               | 19            | 9                      | 10             | I/O | ST     | MSSP1 SPI Clock                 |

| SDI1     | 17                               | 21                               | 18            | 8                      | 9              | 17                               | 21                               | 18            | 8                      | 9              | Ι   | ST     | MSSP1 SPI Data Input            |

| SDO1     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   |        | MSSP1 SPI Data Output           |

| SS1      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | MSSP1 SPI Slave Select Input    |

| SCK2     | —                                | 14                               | 11            | 38                     | 41             | _                                | 14                               | 11            | 38                     | 41             | I/O | ST     | MSSP2 SPI Clock                 |

| SDI2     | —                                | 19                               | 16            | 36                     | 39             | _                                | 19                               | 16            | 36                     | 39             | Ι   | ST     | MSSP2 SPI Data Input            |

| SDO2     | —                                | 15                               | 12            | 37                     | 40             | —                                | 15                               | 12            | 37                     | 40             | 0   |        | MSSP2 SPI Data Output           |

| SS2      | —                                | 23                               | 20            | 35                     | 38             | _                                | 23                               | 20            | 35                     | 38             | Ι   | ST     | MSSP2 SPI Slave Select Input    |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART2 16x Baud Rate Clock Output               |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> devices and improve Data Space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all EA calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word, which contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, the data memory and the registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register, which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed, but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow the users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

#### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the Data Space is addressable indirectly. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing (MDA) with a 16-bit address field. For PIC24FV16KM204 family devices, the entire implemented data memory lies in Near Data Space (NDS).

#### 4.2.4 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by that module. Much of the SFR space contains unused addresses; these are read as '0'. The SFR space, where the SFRs are actually implemented, is provided in Table 4-2. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete listing of implemented SFRs, including their addresses, is provided in Table 4-3 through Table 4-26.

|      |                          |           |                 | SFR Space A | ddress |            |      |       |  |  |

|------|--------------------------|-----------|-----------------|-------------|--------|------------|------|-------|--|--|

|      | xx00                     | xx20      | xx40            | xx60        | xx80   | xxA0       | xxC0 | xxE0  |  |  |

| 000h |                          | Core      |                 | ICN         |        | Interrupts |      | _     |  |  |

| 100h | Timers                   | CLC       |                 |             | MCCP   | /SCCP      |      |       |  |  |

| 200h | h MSSP UART Op Amp DAC — |           |                 |             |        |            | I/O  |       |  |  |

| 300h |                          | A/D/C     | CMTU            |             | —      | —          | —    | —     |  |  |

| 400h | —                        | —         | —               | —           | —      | —          | —    | ANSEL |  |  |

| 500h | —                        | —         | —               | —           | —      | —          | —    | —     |  |  |

| 600h | —                        | RTCC/Comp | —               | Band Gap    |        | -          | _    |       |  |  |

| 700h | _                        | —         | System/<br>HLVD | NVM/PMD     | —      | —          | _    | —     |  |  |

#### TABLE 4-2: IMPLEMENTED REGIONS OF SFR DATA SPACE

**Legend:** — = No implemented SFRs in this block.

### TABLE 4-13: MSSP1 (I<sup>2</sup>C<sup>™</sup>/SPI) REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                                                                                                    | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-------|-------|-------|-------|---------------|

| SSP1BUF   | 200h  | —      | _      | _      | —      | —      | —      | _     | —     | MSSP1 Receive Buffer/Transmit Register                                                                                   |         |       |       |       |       |       |       | 00xx          |

| SSP1CON1  | 202h  | _      | _      | _      | _      | _      | _      | _     | _     | WCOL                                                                                                                     | SSPOV   | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | 0000          |

| SSP1CON2  | 204h  | _      | _      | _      | _      | _      | _      | _     | _     | GCEN                                                                                                                     | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 0000          |

| SSP1CON3  | 206h  | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM                                                                                                                   | PCIE    | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  | 0000          |

| SSP1STAT  | 208h  | _      | _      | _      | _      | _      | _      | —     | _     | SMP                                                                                                                      | CKE     | D/A   | Р     | S     | R/W   | UA    | BF    | 0000          |

| SSP1ADD   | 20Ah  | —      | _      | _      | —      | _      | —      |       |       | MSSP1 Address Register in I <sup>2</sup> C Slave Mode<br>MSSP1 Baud Rate Reload Register in I <sup>2</sup> C Master Mode |         |       |       |       |       |       |       | 0000          |

| SSP1MSK   | 20Ch  | _      | _      | _      | _      | _      | _      |       | _     | MSK7                                                                                                                     | MSK6    | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  | OOFF          |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-14: MSSP2 (I<sup>2</sup>C<sup>™</sup>/SPI) REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                                                                                                    | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-------|-------|-------|-------|---------------|

| SSP2BUF <sup>(1)</sup>  | 210h  | —      | _      | —      | —      |        | _      |       | _     | MSSP2 Receive Buffer/Transmit Register                                                                                   |         |       |       |       |       |       | 00xx  |               |

| SSP2CON1 <sup>(1)</sup> | 212h  | _      | _      | _      | _      | _      | _      | _     | _     | WCOL                                                                                                                     | SSPOV   | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | 0000          |

| SSP2CON2 <sup>(1)</sup> | 214h  | _      | _      | _      | _      | _      | _      | _     | _     | GCEN                                                                                                                     | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 0000          |

| SSP2CON3 <sup>(1)</sup> | 216h  | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM                                                                                                                   | PCIE    | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  | 0000          |

| SSP2STAT <sup>(1)</sup> | 218h  | _      | _      | _      | _      | _      | _      | _     | _     | SMP                                                                                                                      | CKE     | D/A   | Р     | S     | R/W   | UA    | BF    | 0000          |

| SSP2ADD <sup>(1)</sup>  | 21Ah  | —      | _      | —      | —      | _      | —      | _     | _     | MSSP2 Address Register in I <sup>2</sup> C Slave Mode<br>MSSP2 Baud Rate Reload Register in I <sup>2</sup> C Master Mode |         |       |       |       |       |       | 0000  |               |

| SSP2MSK <sup>(1)</sup>  | 21Ch  | —      | _      | _      | _      |        | _      | _     | _     | MSK7                                                                                                                     | MSK6    | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  | 00FF          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

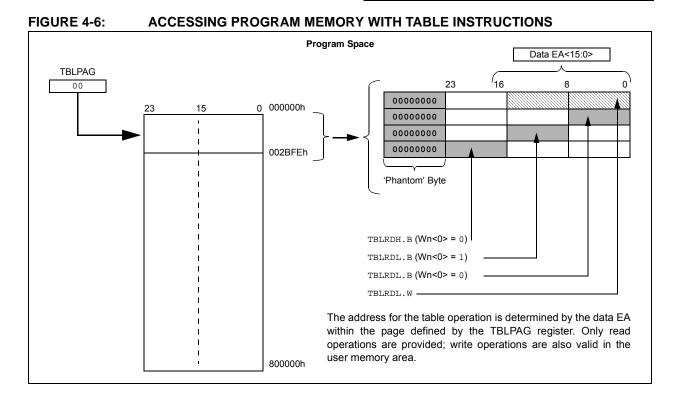

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through Data Space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

Note: The TBLRDH and TBLWTH instructions are not used while accessing data EEPROM memory.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit, word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table Write operations are not allowed.

© 2013 Microchip Technology Inc.

| U-0                 | R/W-1                                    | R/W-0                                                                       | R/W-0            | U-0                                | U-0              | U-0             | U-0     |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------|------------------|------------------------------------|------------------|-----------------|---------|

| 0-0                 | NVMIP2                                   | NVMIP1                                                                      | NVMIP0           | 0-0                                | 0-0              | 0-0             | 0-0     |

| <br>bit 15          |                                          |                                                                             |                  | —                                  | _                | _               | <br>bit |

|                     |                                          |                                                                             |                  |                                    |                  |                 | bit     |

| U-0                 | R/W-1                                    | R/W-0                                                                       | R/W-0            | U-0                                | R/W-1            | R/W-0           | R/W-0   |

| _                   | AD1IP2                                   | AD1IP1                                                                      | AD1IP0           |                                    | U1TXIP2          | U1TXIP1         | U1TXIP0 |

| bit 7               |                                          |                                                                             |                  |                                    |                  |                 | bit     |

| Legend:             |                                          |                                                                             |                  |                                    |                  |                 |         |

| R = Readab          | ole bit                                  | W = Writable                                                                | bit              | U = Unimplem                       | nented bit, read | 1 as '0'        |         |

| -n = Value a        | at POR                                   | '1' = Bit is set                                                            |                  | '0' = Bit is clea                  | ared             | x = Bit is unkr | nown    |

| =                   |                                          |                                                                             |                  |                                    |                  |                 |         |

| bit 15<br>bit 14-12 | -                                        | ited: Read as '<br>: NVM Interrup                                           |                  |                                    |                  |                 |         |

|                     | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                   | abled            | .,                                 |                  |                 |         |

| bit 11-7            | -                                        | ted: Read as '                                                              |                  |                                    |                  |                 |         |

| bit 6-4             | 111 = Interru<br>•<br>•<br>001 = Interru | A/D Conversic<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis | highest priority | terrupt Priority I<br>/ interrupt) | bits             |                 |         |

| bit 3               | Unimplemen                               | ted: Read as '                                                              | 0'               |                                    |                  |                 |         |

| bit 2-0             |                                          | ➤: UART1 Trans<br>pt is Priority 7 (                                        |                  |                                    |                  |                 |         |

|                     |                                          | pt is Priority 1<br>pt source is dis                                        | abled            |                                    |                  |                 |         |

#### REGISTER 8-22: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

### **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, "Power-Saving Features with VBAT" (DS30622).

This FRM describes some features which

are not implemented in this device. Sections related to the VBAT pin and Deep Sleep do not apply to the PIC24FV16KM204 family.

The PIC24FV16KM204 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

#### 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

#### 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The 'C' syntax of the  $\ensuremath{\mathtt{PWRSAV}}$  instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as the clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification on the I/O ports or peripherals that use an External Clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: 'C' POWER-SAVING ENTRY

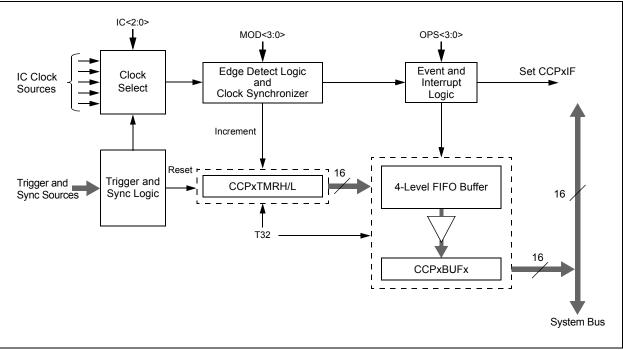

#### 13.4 Input Capture Mode

Input Capture mode is used to capture a timer value from an independent timer base upon an event on an input pin or other internal Trigger source. The input capture features are useful in applications requiring frequency (time period) and pulse measurement. Figure 13-6 depicts a simplified block diagram of Input Capture mode. Input Capture mode uses a dedicated 16/32-bit, synchronous, up counting timer for the capture function. The timer value is written to the FIFO when a capture event occurs. The internal value may be read (with a synchronization delay) using the CCPxTMRH/L register.

To use Input Capture mode, the CCSEL bit (CCPxCON1L<4>) must be set. The T32 and the MOD<3:0> bits are used to select the proper Capture mode, as shown in Table 13-4.

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                     |  |  |  |  |  |

|------------------------------|-----------------------|------------------------------------|--|--|--|--|--|

| 0000                         | 0                     | Edge Detect (16-bit capture)       |  |  |  |  |  |

| 0000                         | 1                     | Edge Detect (32-bit capture)       |  |  |  |  |  |

| 0001                         | 0                     | Every Rising (16-bit capture)      |  |  |  |  |  |

| 0001                         | 1                     | Every Rising (32-bit capture)      |  |  |  |  |  |

| 0010                         | 0                     | Every Falling (16-bit capture)     |  |  |  |  |  |

| 0010                         | 1                     | Every Falling (32-bit capture)     |  |  |  |  |  |

| 0011                         | 0                     | Every Rise/Fall (16-bit capture)   |  |  |  |  |  |

| 0011                         | 1                     | Every Rise/Fall (32-bit capture)   |  |  |  |  |  |

| 0100                         | 0                     | Every 4th Rising (16-bit capture)  |  |  |  |  |  |

| 0100                         | 1                     | Every 4th Rising (32-bit capture)  |  |  |  |  |  |

| 0101                         | 0                     | Every 16th Rising (16-bit capture) |  |  |  |  |  |

| 0101                         | 1                     | Every 16th Rising (32-bit capture) |  |  |  |  |  |

#### TABLE 13-4: INPUT CAPTURE MODES

#### REGISTER 15-3: UXTXREG: UARTX TRANSMIT REGISTER

| U-x    | U-x | U-x | U-x | U-x | U-x | U-x | W-x   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | _   | —   | UTX8  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-x   | W-x  | W-x  | W-x  | W-x  | W-x  | W-x  | W-x   |

|-------|------|------|------|------|------|------|-------|

| UTX7  | UTX6 | UTX5 | UTX4 | UTX3 | UTX2 | UTX1 | UTX0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

bit 8 **UTX8:** Data of the Transmitted Character bit (in 9-bit mode)

bit 7-0 UTX<7:0>: Data of the Transmitted Character bits

#### REGISTER 15-4: UxRXREG: UARTx RECEIVE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC |

|--------|-----|-----|-----|-----|-----|-----|----------|

| —      | —   | —   | —   | —   | —   | _   | URX8     |

| bit 15 |     |     |     |     |     |     | bit 8    |

| R-0, HSC |

|----------|----------|----------|----------|----------|----------|----------|----------|

| URX7     | URX6     | URX5     | URX4     | URX3     | URX2     | URX1     | URX0     |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/ | HSC = Hardware Settable/Clearable bit   |  |  |  |  |  |

|-------------------|--------------------------|-----------------------------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0'      |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |  |

bit 15-9 Unimplemented: Read as '0'

bit 8 URX8: Data of the Received Character bit (in 9-bit mode)

bit 7-0 URX<7:0>: Data of the Received Character bits

#### REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit                  |

|-------|--------------------------------------------------------------|

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit               |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                  |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit               |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

| R/W-0              | R-0                                                             | r-0                                                                                                                                                                                                                  | R/W-0  | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

|--------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|------------------|-----------------|-------|--|--|

| ADRC               | EXTSAM                                                          | r                                                                                                                                                                                                                    | SAMC4  | SAMC3             | SAMC2            | SAMC1           | SAMC0 |  |  |

| bit 15             |                                                                 |                                                                                                                                                                                                                      |        |                   |                  |                 | bit   |  |  |

| R/W-0              | R/W-0                                                           | R/W-0                                                                                                                                                                                                                | R/W-0  | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

| ADCS7              | ADCS6                                                           | ADCS5                                                                                                                                                                                                                | ADCS4  | ADCS3             | ADCS2            | ADCS1           | ADCS0 |  |  |

| bit 7              |                                                                 |                                                                                                                                                                                                                      | 1      |                   |                  |                 | bit   |  |  |

| Legend:            |                                                                 | r = Reserved                                                                                                                                                                                                         | bit    |                   |                  |                 |       |  |  |

| R = Readab         | le bit                                                          | W = Writable                                                                                                                                                                                                         | bit    | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |

| -n = Value a       | t POR                                                           | '1' = Bit is set                                                                                                                                                                                                     |        | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |

| bit 13<br>bit 12-8 | 0 = A/D is fir<br><b>Reserved:</b> M<br><b>SAMC&lt;4:0&gt;:</b> | <ul> <li>1 = A/D is still sampling after SAMP = 0</li> <li>0 = A/D is finished sampling</li> <li>Reserved: Maintain as '0'</li> <li>SAMC&lt;4:0&gt;: Auto-Sample Time Select bits</li> <li>11111 = 31 TAD</li> </ul> |        |                   |                  |                 |       |  |  |

|                    | •<br>•<br>00001 = 1 T.<br>00000 = 0 T.                          |                                                                                                                                                                                                                      |        |                   |                  |                 |       |  |  |

| bit 7-0            | 11111111-0                                                      | A/D Conversio<br>1000000 = Re<br>64 * TCY = TAC                                                                                                                                                                      | served | : bits            |                  |                 |       |  |  |

|                    | •<br>00000001 =<br>00000000 =                                   | 2 * TCY = TAD                                                                                                                                                                                                        |        |                   |                  |                 |       |  |  |

#### REGISTER 19-3: AD1CON3: A/D CONTROL REGISTER 3

| R/W-0         | R/W-0                                                                                                              | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|

| CH0NB2        | CH0NB1                                                                                                             | CH0NB0                               | CH0SB4         | CH0SB3            | CH0SB2           | CH0SB1          | CH0SB0 |  |  |  |  |  |

| bit 15        |                                                                                                                    |                                      |                |                   |                  |                 | bit    |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                              | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

| CH0NA2        | CH0NA1                                                                                                             | CHONAO                               | CH0SA4         | CH0SA3            | CH0SA2           | CH0SA1          | CH0SA0 |  |  |  |  |  |

| bit 7         |                                                                                                                    |                                      |                |                   |                  |                 | bit    |  |  |  |  |  |

| Legend:       |                                                                                                                    |                                      |                |                   |                  |                 |        |  |  |  |  |  |

| R = Readabl   | le bit                                                                                                             | W = Writable                         | bit            | U = Unimplem      | nented bit, read | d as '0'        |        |  |  |  |  |  |

| -n = Value at | POR                                                                                                                | '1' = Bit is set                     |                | '0' = Bit is clea |                  | x = Bit is unkr | iown   |  |  |  |  |  |

| L: 45 40      |                                                                                                                    | · Comple D Ch                        | annal O Nagati | ve less to Celest | h:to             |                 |        |  |  |  |  |  |

| bit 15-13     | 111 = AN6 <sup>(1)</sup>                                                                                           | •                                    | annei 0 Negati | ve Input Select   | DIIS             |                 |        |  |  |  |  |  |

|               | $111 = AN6^{(1)}$<br>$110 = AN5^{(2)}$                                                                             |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 101 = AN3                                                                                                          |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 101 - AN4<br>100 = AN3                                                                                             |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 011 = AN2                                                                                                          |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 010 = AN1                                                                                                          |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 001 = ANO                                                                                                          |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 000 = AVss                                                                                                         |                                      |                |                   |                  |                 |        |  |  |  |  |  |

| bit 12-8      | CH0SB<4:0>: S/H Amplifier Positive Input Select for MUX B Multiplexer Setting bits                                 |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 11111 = Unimplemented, do not use                                                                                  |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 11110 = $AVDD^{(3)}$                                                                                               |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 11101 = AVss <sup>(3)</sup>                                                                                        |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 11100 = Upper guardband rail (0.785 * VDD)                                                                         |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 11011 = Lower guardband rail (0.215 * VDD)                                                                         |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 11010 = Internal Band Gap Reference (VвG) <sup>(3)</sup>                                                           |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    | 1 = Unimpleme                        |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    |                                      |                | puts are floating |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    |                                      |                | puts are floating |                  |                 |        |  |  |  |  |  |

|               | 10110 = No channels are connected, all inputs are floating (used for CTMU temperature sensor input);               |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | does not require the corresponding CTMEN22 (AD1CTMENH<6>) bit)                                                     |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 10101 = Channel 0 positive input is AN21                                                                           |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 10100 = Channel 0 positive input is AN20                                                                           |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 10011 = Channel 0 positive input is AN19<br>10010 = Channel 0 positive input is AN18 <sup>(2)</sup>                |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 10010 = Channel 0 positive input is AN17 <sup>(2)</sup><br>10001 = Channel 0 positive input is AN17 <sup>(2)</sup> |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | •                                                                                                                  |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | •                                                                                                                  |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 01001 <b>= Ch</b> a                                                                                                | annel 0 positive                     | input is AN9   |                   |                  |                 |        |  |  |  |  |  |

|               | 01000 = Channel 0 positive input is $AN8^{(1)}$                                                                    |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 00111 = Channel 0 positive input is AN7 <sup>(1)</sup>                                                             |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               | 00110 = Channel 0 positive input is AN6 <sup>(1)</sup>                                                             |                                      |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                | )                 |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                    | annel 0 positive<br>annel 0 positive |                |                   |                  |                 |        |  |  |  |  |  |

| Note 4- T     |                                                                                                                    | ·                                    | •              |                   |                  |                 |        |  |  |  |  |  |

|               | his is implement                                                                                                   | -                                    | -              |                   |                  |                 |        |  |  |  |  |  |

| <b>Z</b> : 1  | his is implement                                                                                                   | teu un zo-pin a                      |                | CS UNIY.          |                  |                 |        |  |  |  |  |  |

3: The band gap value used for this input is 2x or 4x the internal VBG, which is selected when PVCFG<1:0> = 1x.

#### REGISTER 19-5: AD1CHS: A/D SAMPLE SELECT REGISTER

DS30003030B-page 218

#### REGISTER 20-1: DACxCON: DACx CONTROL REGISTER (CONTINUED)

- bit 6-2 DACTSEL<4:0>: DACx Trigger Source Select bits

- 11101-11111 = Unused 11100 = CTMU 11011 = A/D 11010 = Comparator 3 11001 = Comparator 2 11000 = Comparator 1 10011 to 10111 = Unused 10010 = CLC2 output 10001 = CLC1 output 01100 to 10000 = Unused 01011 = Timer1 Sync output 01010 = External Interrupt 2 01001 = External Interrupt 1 01000 = External Interrupt 0 0011x = Unused 00101 = MCCP5 or SCCP5 Sync output 00100 = MCCP4 or SCCP4 Sync output 00011 = MCCP3 or SCCP3 Sync output 00010 = MCCP2 or SCCP2 Sync output 00001 = MCCP1 or SCCP1 Sync output 00000 = Unused DACREF<1:0>: DACx Reference Source Select bits 11 = Internal Band Gap Buffer 1 (BGBUF1)<sup>(1)</sup>

- 10 = AVDD

bit 1-0

- 01 = DVREF+

- 00 = Reference is not connected (lowest power but no DAC functionality)

- **Note 1:** BGBUF1 voltage is configured by BUFREF<1:0> (BUFCON0<1:0>).

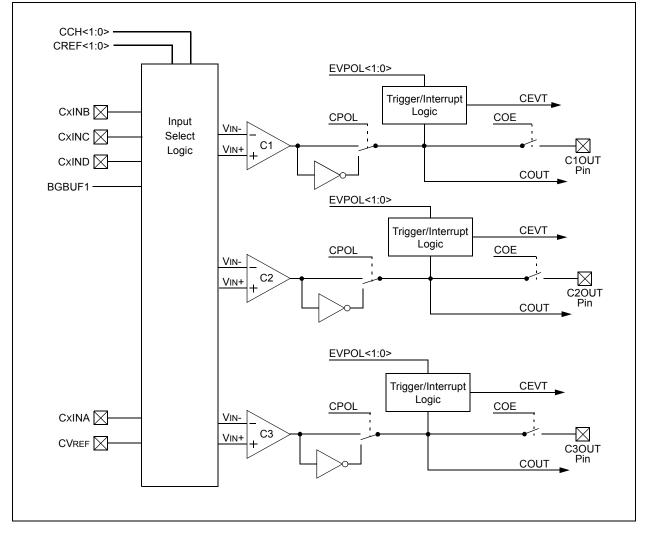

### 22.0 COMPARATOR MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator module, refer to the "PIC24F Family Reference Manual", "Scalable Comparator Module" (DS39734).

The comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs, as well as a voltage reference input from either the Internal Band Gap Buffer 1 (BGBUF1) or the comparator voltage reference generator. The comparator outputs may be directly connected to the CxOUT pins. When the respective COE bit equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is shown in Figure 22-1. Diagrams of the possible individual comparator configurations are shown in Figure 22-2.

Each comparator has its own control register, CMxCON (Register 22-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 22-2).

#### FIGURE 22-1: COMPARATOR x MODULE BLOCK DIAGRAM

| R/W-0         | U-0                                                                                                       | R/W-0                                                   | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------|------------------|------------------|-----------------|--------|--|--|--|

| CTMUEN        |                                                                                                           | CTMUSIDL                                                | TGEN            | EDGEN            | EDGSEQEN         | IDISSEN         | CTTRIG |  |  |  |

| bit 15        |                                                                                                           |                                                         |                 |                  |                  |                 | bit 8  |  |  |  |

|               |                                                                                                           |                                                         |                 |                  |                  |                 |        |  |  |  |

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                   | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| ITRIM5        | ITRIM4                                                                                                    | ITRIM3                                                  | ITRIM2          | ITRIM1           | ITRIM0           | IRNG1           | IRNG0  |  |  |  |

| bit 7         |                                                                                                           |                                                         |                 |                  |                  |                 | bit (  |  |  |  |

| Legend:       |                                                                                                           |                                                         |                 |                  |                  |                 |        |  |  |  |

| R = Readable  | e bit                                                                                                     | W = Writable b                                          | bit             | U = Unimpler     | mented bit, read | as '0'          |        |  |  |  |