#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km202t-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FV08KM101 PIC24F08KM101

- PIC24FV08KM102

- PIC24F08KM102

PIC24F16KM102

- PIC24FV16KM102

- PIC24FV16KM104 PIC24F16KM104

- PIC24FV08KM202 PIC24F08KM202

- PIC24FV08KM204 PIC24F08KM204

- PIC24FV16KM202

- PIC24F16KM202

- PIC24FV16KM204 PIC24F16KM204

The PIC24FV16KM204 family introduces many new analog features to the extreme low-power Microchip devices. This is a 16-bit microcontroller family with a broad peripheral feature set and enhanced computational performance. This family also offers a new migration option for those high-performance applications which may be outgrowing their 8-bit platforms, but do not require the numerical processing power of a Digital Signal Processor (DSC).

## 1.1 Core Features

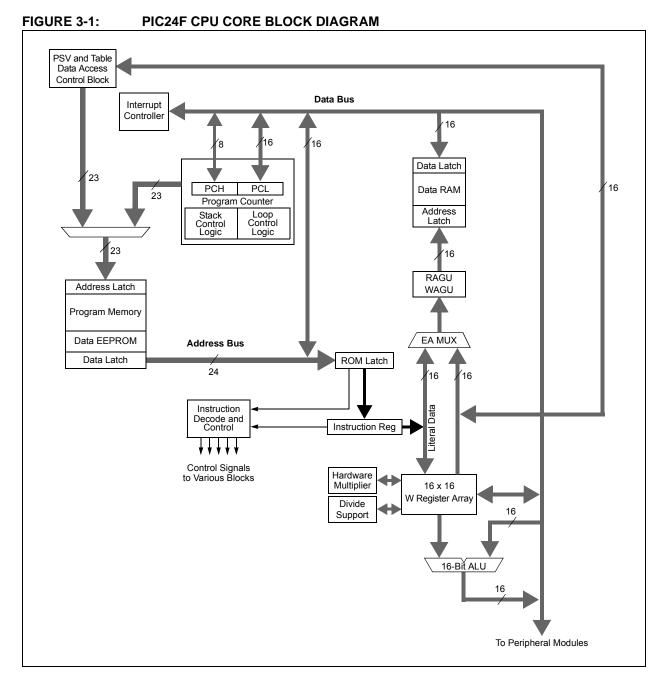

## 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's  $dsPIC^{\textcircled{B}}$  Digital Signal Controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear Addressing of up to 16 Mbytes (program space) and 16 Kbytes (data)

- A 16-element working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32-bit by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as C

- Operational performance up to 16 MIPS

## 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24FV16KM204 family incorporate a range of features that can significantly reduce power consumption during operation. Key features include:

- On-the-Fly Clock Switching, to allow the device clock to be changed under software control to the Timer1 source or the internal, low-power RC Oscillator during operation, allowing users to incorporate power-saving ideas into their software designs.

- Doze Mode Operation, when timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes, to allow the microcontroller to suspend all operations or selectively shut down its core while leaving its peripherals active with a single instruction in software.

## 1.1.3 OSCILLATOR OPTIONS AND FEATURES

The PIC24FV16KM204 family offers five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock (EC) modes offering the option of a divide-by-2 clock output.

- Two Fast Internal Oscillators (FRCs), one with a nominal 8 MHz output and the other with a nominal 500 kHz output. These outputs can also be divided under software control to provide clock speed as low as 31 kHz or 2 kHz.

- A Phase Locked Loop (PLL) frequency multiplier, available to the external oscillator modes and the 8 MHz FRC Oscillator, which allows clock speeds of up to 32 MHz.

- A separate internal RC Oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

NOTES:

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

| TABLE 4-29: | COMPARATOR REGISTER MAP |

|-------------|-------------------------|

|             |                         |

| File Name             | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10               | Bit 9                | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4                | Bit 3 | Bit 2                | Bit 1                | Bit 0 | All<br>Resets |

|-----------------------|-------|--------|--------|--------|--------|--------|----------------------|----------------------|-------|--------|--------|-------|----------------------|-------|----------------------|----------------------|-------|---------------|

| CMSTAT                | 630h  | CMIDL  | _      | —      | —      |        | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT | —      | _      | _     | —                    | —     | C3OUT <sup>(1)</sup> | C2OUT <sup>(1)</sup> | C1OUT | 0000          |

| CVRCON                | 632h  | —      | _      | _      | _      | _      | _                    | _                    | _     | CVREN  | CVROE  | CVRSS | CVR4                 | CVR3  | CVR2                 | CVR1                 | CVR0  | 0000          |

| CM1CON                | 634h  | CON    | COE    | CPOL   | CLPWR  |        | _                    | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF1                | CREF0 | —                    | CCH1                 | CCH0  | 0000          |

| CM2CON <sup>(1)</sup> | 636h  | CON    | COE    | CPOL   | CLPWR  |        | —                    | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF1 <sup>(1)</sup> | CREF0 | —                    | CCH1                 | CCH0  | 0000          |

| CM3CON <sup>(1)</sup> | 638h  | CON    | COE    | CPOL   | CLPWR  |        | —                    | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF1 <sup>(1)</sup> | CREF0 | —                    | CCH1                 | CCH0  | 0000          |

$\label{eq:legend: second condition, u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.$

Note 1: These registers and bits are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-30: BAND GAP BUFFER CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------|---------|---------------|

| BUFCON0   | 670h  |        | _      |        | _      |        | _      | _     |       | _     |       |       |       |       | _     | BUFREF1 | BUFREF0 | 0001          |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

## 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on data EEPROM, refer to the *"PIC24F Family Reference Manual"*, **"Data EEPROM"** (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFh. The size of the data EEPROM is 256 words in PIC24FXXXXX devices.

The data EEPROM is organized as 16-bit-wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

## 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

## 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

|                | rrupts For 5 instruc | ctions |

|----------------|----------------------|--------|

| asm volatile   | ("disi #5");         |        |

| //Issue Unlock | Sequence             |        |

| asm volatile   | ("mov #0x55, W0      | \n"    |

|                | "mov W0, NVMKEY      | \n"    |

|                | "mov #0xAA, W1       | \n"    |

|                | "mov W1, NVMKEY      | \n");  |

| // Perform Wri | te/Erase operations  |        |

| asm volatile   | ("bset NVMCON, #WR   | \n"    |

|                | "nop                 | \n"    |

|                | "nop                 | \n");  |

|                |                      |        |

#### 6.4.1.1 Data EEPROM Bulk Erase

To erase the entire data EEPROM (bulk erase), the address registers do not need to be configured because this operation affects the entire data EEPROM. The following sequence helps in performing a bulk erase:

- 1. Configure NVMCON to Bulk Erase mode.

- 2. Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 3. Write the key sequence to NVMKEY.

- 4. Set the WR bit to begin the erase cycle.

- 5. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical bulk erase sequence is provided in Example 6-3.

#### 6.4.2 SINGLE-WORD WRITE

To write a single word in the data EEPROM, the following sequence must be followed:

- Erase one data EEPROM word (as mentioned in the previous section) if the PGMONLY bit (NVMCON<12>) is set to '1'.

- 2. Write the data word into the data EEPROM latch.

- Program the data word into the EEPROM:

Configure the NVMCON register to

- program one EEPROM word (NVMCON<5:0> = 0001xx).

- Clear the NVMIF status bit and enable the NVM interrupt (optional).

- Write the key sequence to NVMKEY.

- Set the WR bit to begin the erase cycle.

- Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

- To get cleared, wait until NVMIF is set.

A typical single-word write sequence is provided in Example 6-4.

## EXAMPLE 6-3: DATA EEPROM BULK ERASE

// Set up NVMCON to bulk erase the data EEPROM NVMCON =  $0 \times 4050$ ;

// Disable Interrupts For 5 Instructions

asm volatile ("disi #5");

// Issue Unlock Sequence and Start Erase Cycle

\_\_builtin\_write\_NVM();

## EXAMPLE 6-4: SINGLE-WORD WRITE TO DATA EEPROM

```

int __attribute__ ((space(eedata))) eeData = 0x1234;

// New data to write to EEPROM

int newData;

_____

/*_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the write

_ _ _ _ _

* /

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0 \times 4004;

// Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData); // Initialize EE Data page pointer

// Initizlize lower word of address

offset = __builtin_tbloffset(&eeData);

__builtin_tblwtl(offset, newData);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

__builtin_write_NVM();

// Issue Unlock Sequence & Start Write Cycle

while(NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

| R/W-0        | R-0, HSC                              | U-0               | U-0             | U-0               | U-0              | U-0                | U-0    |  |

|--------------|---------------------------------------|-------------------|-----------------|-------------------|------------------|--------------------|--------|--|

| ALTIVT       | DISI                                  | —                 | —               | —                 | —                | —                  | —      |  |

| bit 15       |                                       |                   |                 |                   |                  |                    | bit 8  |  |

|              |                                       |                   |                 |                   |                  |                    |        |  |

| U-0          | U-0                                   | U-0               | U-0             | U-0               | R/W-0            | R/W-0              | R/W-0  |  |

| —            | —                                     | —                 | —               | —                 | INT2EP           | INT1EP             | INT0EP |  |

| bit 7        |                                       |                   |                 |                   |                  |                    | bit 0  |  |

|              |                                       |                   |                 |                   |                  |                    |        |  |

| Legend:      |                                       | HSC = Hardw       | are Settable/C  | learable bit      |                  |                    |        |  |

| R = Readab   | le bit                                | W = Writable b    | oit             | U = Unimplem      | nented bit, read | d as '0'           |        |  |

| -n = Value a | t POR                                 | '1' = Bit is set  |                 | '0' = Bit is clea | ared             | x = Bit is unknown |        |  |

|              |                                       |                   |                 |                   |                  |                    |        |  |

| bit 15       | ALTIVT: Enat                          | ole Alternate Int | errupt Vector 7 | Table bit         |                  |                    |        |  |

|              |                                       | rnate Interrupt   | •               | ,                 |                  |                    |        |  |

|              |                                       | ndard (default) I | •               | r Table (IVT)     |                  |                    |        |  |

| bit 14       | 21011 2101                            | struction Status  |                 |                   |                  |                    |        |  |

|              |                                       | ruction is active |                 |                   |                  |                    |        |  |

| bit 13-3     |                                       | ted: Read as '0   |                 |                   |                  |                    |        |  |

| bit 2        | •                                     | ernal Interrupt 2 |                 | Polarity Solact k | ait              |                    |        |  |

|              |                                       | s on the negativ  | -               |                   | JIL              |                    |        |  |

|              | •                                     | s on the positive | •               |                   |                  |                    |        |  |

| bit 1        |                                       | ernal Interrupt 1 | •               | Polarity Select b | oit              |                    |        |  |

|              | 1 = Interrupt i                       | s on the negativ  | ve edge         | -                 |                  |                    |        |  |

|              | 0 = Interrupt is on the positive edge |                   |                 |                   |                  |                    |        |  |

| bit 0        | INTOEP: Exte                          | ernal Interrupt 0 | Edge Detect F   | Polarity Select b | oit              |                    |        |  |

|              |                                       | s on the negativ  | U U             |                   |                  |                    |        |  |

|              | 0 = Interrupt i                       | s on the positive | e edge          |                   |                  |                    |        |  |

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER 2

## 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC Oscillator by a fixed amount.

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                    | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit |                        |                    |  |  |

|----------------------------|---------------------------------------|------------------------|--------------------|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit               | SO = Settable Only bit |                    |  |  |

| R = Readable bit           | W = Writable bit                      | U = Unimplemented bit  | , read as '0'      |  |  |

| -n = Value at POR          | '1' = Bit is set                      | '0' = Bit is cleared   | x = Bit is unknown |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| Note 1:   | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:        | This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                |

**3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

## 10.2.2 IDLE MODE

Idle mode includes these features:

- · The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.6 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

#### 10.2.3.1 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. When a true POR occurs, the entire device is reset.

### 10.3 Ultra Low-Power Wake-up

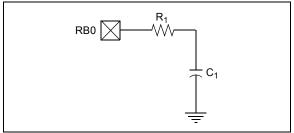

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

#### EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//********

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//2. Stop Charging the capacitor

on RBO

11

//*******************************

TRISBbits.TRISB0 = 1;

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

IEC5bits.ULPWUIE = 1;

IPC21bits.ULPWUIP = 0x7;

//*********************************

//4. Enable the Ultra Low Power

11

Wakeup module and allow

11

capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbit.ULPSINK = 1;

//5. Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RB0 and the external capacitor provides overcurrent protection for the AN2/ULPWU/RB0 pin and enables software calibration of the time-out (see Figure 10-1).

#### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

| R/W-0         | U-0                                                                                                 | R/W-0                       | U-0                                | U-0                    | U-0              | R/W-0                | R/W-0                |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------|------------------------|------------------|----------------------|----------------------|--|--|--|--|

| TON           | —                                                                                                   | TSIDL                       | —                                  | —                      | _                | TECS1 <sup>(1)</sup> | TECS0 <sup>(1)</sup> |  |  |  |  |

| bit 15        |                                                                                                     | •                           | -                                  |                        | •                |                      | bit                  |  |  |  |  |

|               |                                                                                                     |                             |                                    |                        |                  |                      |                      |  |  |  |  |

| U-0           | R/W-0                                                                                               | R/W-0                       | R/W-0                              | U-0                    | R/W-0            | R/W-0                | U-0                  |  |  |  |  |

| —             | TGATE                                                                                               | TCKPS1                      | TCKPS0                             | —                      | TSYNC            | TCS                  |                      |  |  |  |  |

| bit 7         |                                                                                                     |                             |                                    |                        |                  |                      | bit                  |  |  |  |  |

| Legend:       |                                                                                                     |                             |                                    |                        |                  |                      |                      |  |  |  |  |

| R = Readabl   | e bit                                                                                               | W = Writable                | bit                                | U = Unimpler           | nented bit, read | d as '0'             |                      |  |  |  |  |

| -n = Value at | POR                                                                                                 | '1' = Bit is set            |                                    | '0' = Bit is cleared   |                  | x = Bit is unknown   |                      |  |  |  |  |

|               |                                                                                                     |                             |                                    |                        |                  |                      |                      |  |  |  |  |

| bit 15        | TON: Timer1                                                                                         | On bit                      |                                    |                        |                  |                      |                      |  |  |  |  |

|               | 1 = Starts 16-<br>0 = Stops 16-                                                                     |                             |                                    |                        |                  |                      |                      |  |  |  |  |

| bit 14        | •                                                                                                   | ted: Read as '              | 0'                                 |                        |                  |                      |                      |  |  |  |  |

| bit 13        | TSIDL: Timer                                                                                        | 1 Stop in Idle I            | Mode bit                           |                        |                  |                      |                      |  |  |  |  |

|               |                                                                                                     |                             | eration when c<br>ation in Idle mo | levice enters Ic<br>de | lle mode         |                      |                      |  |  |  |  |

| bit 12-10     |                                                                                                     | ted: Read as '              |                                    |                        |                  |                      |                      |  |  |  |  |

| bit 9-8       | TECS<1:0>:                                                                                          | Timer1 Extend               | ed Clock Seled                     | ct bits <sup>(1)</sup> |                  |                      |                      |  |  |  |  |

|               | 11 = Reserved; do not use                                                                           |                             |                                    |                        |                  |                      |                      |  |  |  |  |

|               | 10 = Timer1 uses the LPRC as the clock source<br>01 = Timer1 uses the External Clock (EC) from T1CK |                             |                                    |                        |                  |                      |                      |  |  |  |  |

|               |                                                                                                     |                             |                                    | r (SOSC) as the        | e clock source   |                      |                      |  |  |  |  |

| bit 7         | Unimplemen                                                                                          | ted: Read as '              | 0'                                 |                        |                  |                      |                      |  |  |  |  |

| bit 6         |                                                                                                     |                             | Accumulation                       | Enable bit             |                  |                      |                      |  |  |  |  |

|               | When TCS =                                                                                          |                             |                                    |                        |                  |                      |                      |  |  |  |  |

|               | When TCS = $\frac{1}{2}$                                                                            |                             |                                    |                        |                  |                      |                      |  |  |  |  |

|               |                                                                                                     | <u></u><br>ne accumulatio   | n is enabled                       |                        |                  |                      |                      |  |  |  |  |

|               |                                                                                                     | ne accumulatio              |                                    |                        |                  |                      |                      |  |  |  |  |

| bit 5-4       |                                                                                                     | : Timer1 Input              | Clock Prescale                     | e Select bits          |                  |                      |                      |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                                                                             |                             |                                    |                        |                  |                      |                      |  |  |  |  |

|               | 01 = 1:8                                                                                            |                             |                                    |                        |                  |                      |                      |  |  |  |  |

|               | 00 = 1:1                                                                                            |                             |                                    |                        |                  |                      |                      |  |  |  |  |

| bit 3         | -                                                                                                   | ted: Read as '              |                                    |                        |                  |                      |                      |  |  |  |  |

| bit 2         |                                                                                                     |                             | ock Input Sync                     | hronization Sel        | ect bit          |                      |                      |  |  |  |  |

|               | When TCS =<br>1 = Synchron                                                                          | <u>1:</u><br>nizes External | Clock input                        |                        |                  |                      |                      |  |  |  |  |

|               | 0 = Does no                                                                                         | t synchronize I             | External Clock                     | input                  |                  |                      |                      |  |  |  |  |

|               | When TCS =                                                                                          |                             |                                    |                        |                  |                      |                      |  |  |  |  |

|               | -                                                                                                   | Clock Source                | Select bit                         |                        |                  |                      |                      |  |  |  |  |

| bit 1         |                                                                                                     |                             |                                    |                        |                  |                      |                      |  |  |  |  |

| bit 1         | 1 = Timer1 cl<br>0 = Internal c                                                                     |                             | selected by TE                     | CS<1:0>                |                  |                      |                      |  |  |  |  |

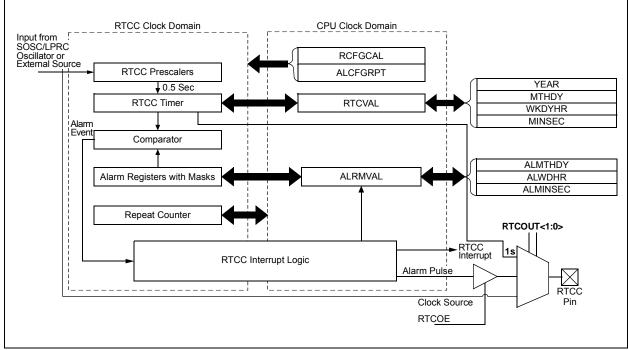

## 16.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Sleep and Retention Sleep modes

- · Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

## 16.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

## FIGURE 16-1: RTCC BLOCK DIAGRAM

## REGISTER 19-1: AD1CON1: A/DA/D CONTROL REGISTER 1 (CONTINUED)

- bit 3

Unimplemented: Read as '0'

bit 2

ASAM: A/D Sample Auto-Start bit

1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set

0 = Sampling begins when the SAMP bit is manually set

bit 1

SAMP: A/D Sample Enable bit

1 = A/D Sample-and-Hold amplifiers are sampling

0 = A/D Sample-and-Hold amplifiers are holding

- bit 0 DONE: A/D Conversion Status bit

- 1 = A/D conversion cycle has completed

- 0 = A/D conversion cycle has not started or is in progress

- **Note 1:** This version of the TMR1 Trigger allows A/D conversions to be triggered from TMR1 while the device is operating in Sleep mode. The SSRC<3:0> = 0101 option allows conversions to be triggered in Run or Idle modes only.

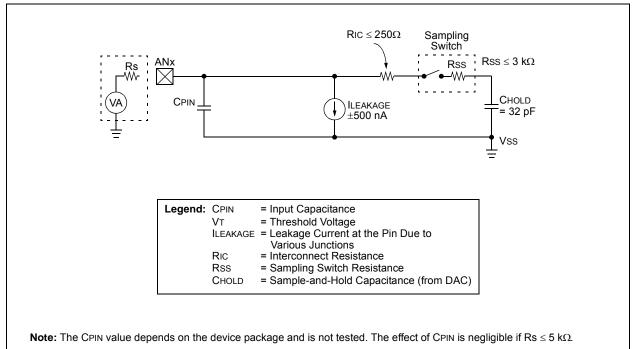

## 19.2 A/D Sampling Requirements

The analog input model of the 12-bit A/D Converter is shown in Figure 19-2. The total sampling time for the A/D is a function of the holding capacitor charge time.

For the A/D Converter to meet its specified accuracy, the Charge Holding Capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The Source Impedance (Rs), the Interconnect Impedance (Rsc) and the Internal Sampling Switch Impedance (Rss) combine to directly affect the time required to charge CHOLD. The combined impedance of the analog sources must, therefore, be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the A/D Converter, the maximum recommended source impedance, Rs, is  $2.5 \text{ k}\Omega$ . After the analog input channel is selected (changed), this sampling function

must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

At least 1 TAD time period should be allowed between conversions for the sample time. For more details, see **Section 27.0 "Electrical Characteristics"**.

# EQUATION 19-1: A/D CONVERSION CLOCK PERIOD

$$TAD = TCY (ADCS + 1)$$

$ADCS = \frac{TAD}{TCY} - 1$

**Note:** Based on Tcy = 2/Fosc; Doze mode and PLL are disabled.

#### FIGURE 19-2: 12-BIT A/D CONVERTER ANALOG INPUT MODEL

#### REGISTER 24-2: CTMUCON1H: CTMU CONTROL 1 HIGH REGISTER (CONTINUED)

- bit 6 EDG2POL: Edge 2 Polarity Select bit 1 = Edge 2 is programmed for a positive edge 0 = Edge 2 is programmed for a negative edge bit 5-2 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = Edge 2 source is the Comparator 3 output 1110 = Edge 2 source is the Comparator 2 output 1101 = Edge 2 source is the Comparator 1 output 1100 = Unimplemented; do not use 1011 = Edge 2 source is CLC1 1010 = Edge 2 source is the MCCP2 Compare Event (CCP2IF) 1001 = Unimplemented; do not use 1000 = Edge 2 source is CTED13 0111 = Edge 2 source is CTED12 0110 = Edge 2 source is CTED11<sup>(2)</sup> 0101 = Edge 2 source is CTED10 0100 = Edge 2 source is CTED9<sup>(2)</sup> 0011 = Edge 2 source is CTED1 0010 = Edge 2 source is CTED2 0001 = Edge 2 source is the MCCP1 Compare Event (CCP1IF) 0000 = Edge 2 source is Timer1

- bit 1-0 Unimplemented: Read as '0'

- Note 1: Edge sources, CTED7 and CTED8, are not available on 28-pin and 20-pin devices.

- 2: Edge sources, CTED3, CTED9 and CTED11, are not available on 20-pin devices.

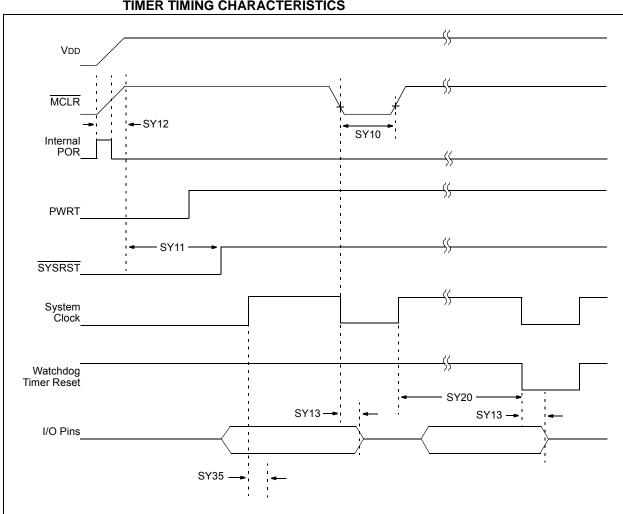

## FIGURE 27-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

| Param.<br>No. | Symbol  | Characteris                | tic          | Min     | Max  | Units                                      | Conditions                           |

|---------------|---------|----------------------------|--------------|---------|------|--------------------------------------------|--------------------------------------|

| 100           | Тнідн   | Clock High Time            | 100 kHz mode | 4.0     | -    | μS                                         | Must operate at a minimum of 1.5 MHz |

|               |         |                            | 400 kHz mode | 0.6     | -    | μS                                         | Must operate at a minimum of 10 MHz  |

|               |         |                            | MSSPx module | 1.5 TCY |      | _                                          |                                      |

| 101           | TLOW    | Clock Low Time             | 100 kHz mode | 4.7     | —    | μS                                         | Must operate at a minimum of 1.5 MHz |

|               |         |                            | 400 kHz mode | 1.3     | —    | μS                                         | Must operate at a minimum of 10 MHz  |

|               |         |                            | MSSPx module | 1.5 TCY | —    | _                                          |                                      |

| 102           | TR      | SDAx and SCLx Rise Time    | 100 kHz mode | —       | 1000 | ns                                         |                                      |

|               |         | 400 kHz mode               | 20 + 0.1 CB  | 300     | ns   | CB is specified to be from<br>10 to 400 pF |                                      |

| 103 TF        | TF      | SDAx and SCLx Fall Time    | 100 kHz mode | —       | 300  | ns                                         |                                      |

|               |         | 400 kHz mode               | 20 + 0.1 CB  | 300     | ns   | CB is specified to be from<br>10 to 400 pF |                                      |

| 90 Tsu:sta    | TSU:STA | Start Condition Setup Time | 100 kHz mode | 4.7     |      | μS                                         | Only relevant for Repeated           |

|               |         |                            | 400 kHz mode | 0.6     | _    | μS                                         | Start condition                      |

| 91 TH         | THD:STA | Start Condition Hold Time  | 100 kHz mode | 4.0     | —    | μS                                         | After this period, the first clock   |

|               |         |                            | 400 kHz mode | 0.6     | —    | μS                                         | pulse is generated                   |

| 106           | THD:DAT | Data Input Hold Time       | 100 kHz mode | 0       | —    | ns                                         |                                      |

|               |         |                            | 400 kHz mode | 0       | 0.9  | μS                                         |                                      |

| 107 TSU:DAT   | TSU:DAT | Data Input Setup Time      | 100 kHz mode | 250     | —    | ns                                         | (Note 2)                             |

|               |         |                            | 400 kHz mode | 100     | —    | ns                                         |                                      |

| 92 Tsu:sto    | Tsu:sto | Stop Condition Setup Time  | 100 kHz mode | 4.7     | —    | μS                                         |                                      |

|               |         |                            | 400 kHz mode | 0.6     | —    | μS                                         |                                      |

| 109 TA        | ΤΑΑ     | Output Valid from Clock    | 100 kHz mode | —       | 3500 | ns                                         | (Note 1)                             |

|               |         |                            | 400 kHz mode | —       | —    | ns                                         |                                      |

| 110           | TBUF    | Bus Free Time              | 100 kHz mode | 4.7     | —    | μS                                         | Time the bus must be free before     |

|               |         |                            | 400 kHz mode | 1.3     | —    | μS                                         | a new transmission can start         |

| D102          | Св      | Bus Capacitive Loading     |              | —       | 400  | pF                                         |                                      |

## TABLE 27-34: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS (SLAVE MODE)

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCLx to avoid unintended generation of Start or Stop conditions.

2: A Fast mode I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement, TSU:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCLx line is released.

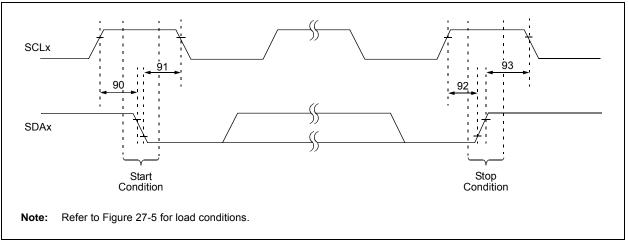

## FIGURE 27-17: MSSPx I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING WAVEFORMS

| TABLE 27-35: | I <sup>2</sup> C <sup>™</sup> BUS START/STOP BITS REQUIREMENTS (MASTER MODE) |

|--------------|------------------------------------------------------------------------------|

|--------------|------------------------------------------------------------------------------|

| Param.<br>No. | Symbol       | Characteristic        |                  | Min              | Max | Units                          | Conditions             |

|---------------|--------------|-----------------------|------------------|------------------|-----|--------------------------------|------------------------|

| 90            | TSU:STA Star | Start Condition       | 100 kHz mode     | 2(Tosc)(BRG + 1) |     | ns                             | Only relevant for      |

| Set           | Setup Time   | 400 kHz mode          | 2(Tosc)(BRG + 1) |                  |     | Repeated Start<br>condition    |                        |

| 91            | THD:STA      | Start Condition       | 100 kHz mode     | 2(Tosc)(BRG + 1) | _   | ns                             | After this period, the |

|               | Hold Time    | 400 kHz mode          | 2(Tosc)(BRG + 1) | _                |     | first clock pulse is generated |                        |

| 92            | Tsu:sto      | SU:STO Stop Condition | 100 kHz mode     | 2(Tosc)(BRG + 1) | _   | ns                             |                        |

|               | Setup Time   | 400 kHz mode          | 2(Tosc)(BRG + 1) | —                |     |                                |                        |

| 93            | THD:STO      | Stop Condition        | 100 kHz mode     | 2(Tosc)(BRG + 1) | —   | ns                             |                        |

| Но            | Hold Time    | 400 kHz mode          | 2(Tosc)(BRG + 1) | _                |     |                                |                        |

## Μ

| Master Synchronous Serial Port (MSSP)     | 159 |

|-------------------------------------------|-----|

| Microchip Internet Web Site               | 332 |

| MPLAB Assembler, Linker, Librarian        | 262 |

| MPLAB ICD 3 In-Circuit Debugger           | 263 |

| MPLAB PM3 Device Programmer               | 263 |

| MPLAB REAL ICE In-Circuit Emulator System | 263 |

| MPLAB X Integrated Development            |     |

| Environment Software                      | 261 |

| MPLAB X SIM Software Simulator            | 263 |

| MPLIB Object Librarian                    | 262 |

| MPLINK Object Linker                      | 262 |

| N                                         |     |

| Near Data Space                           |     |

## 0

| 127 |

|-----|

| 127 |

| 122 |

| 123 |

| 122 |

| 122 |

| 128 |

|     |

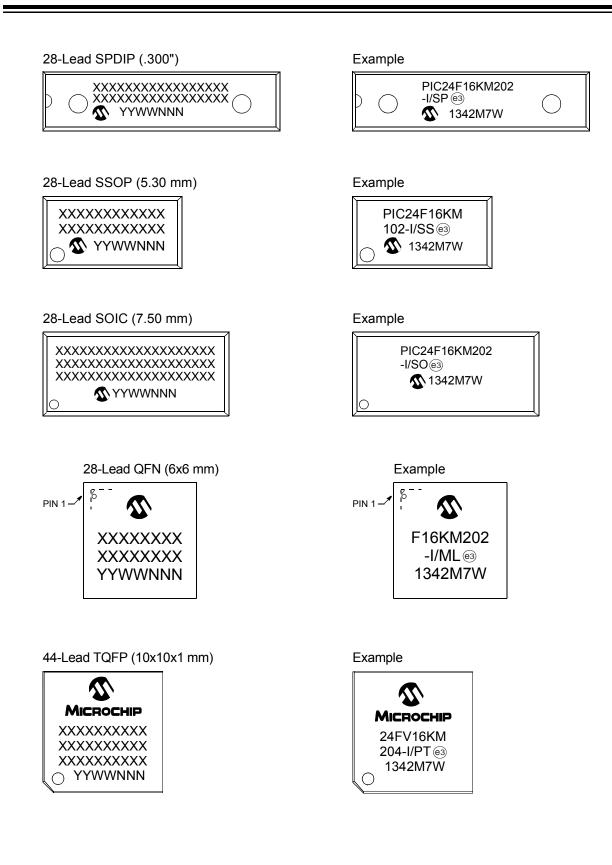

#### **P** Packagir

| Packaging                               |     |

|-----------------------------------------|-----|

| Details                                 | 300 |

| Marking                                 |     |

| PICkit 3 In-Circuit Debugger/Programmer |     |

| Power-Saving                            | 135 |

| Power-Saving Features                   |     |

| Clock Frequency, Clock Switching        | 131 |

| Coincident Interrupts                   | 132 |

| Instruction-Based Modes                 | 131 |

| Idle                                    | 132 |

| Sleep                                   | 131 |

| Retention Regulator (RETREG)            | 134 |

| Selective Peripheral Control            |     |

| Ultra Low-Power Wake-up (ULPWU)         |     |

| Voltage Regulator-Based                 | 134 |

| Retention Sleep Mode                    | 134 |

| Run Mode                                | 134 |

| Sleep Mode                              | 134 |

| Product Identification System           |     |

| Program and Data Memory                 |     |

| Access Using Table Instructions         | 65  |

| Program Space Visibility                | 66  |

| Program and Data Memory Spaces          |     |

| Interfacing, Addressing                 | 63  |

| Program Memory                          |     |

| Address Space                           | 41  |

| Configuration Word Addresses            |     |

| Program Space                           |     |

| Memory Map                              | 41  |

| Program Verification                    |     |

| R                                       |     |

| Real-Time Clock and Calendar (RTCC)     | 181 |

| Register Maps                           |     |

| A/D                                     | 59  |

| ANSEL                                   |     |

| Band Gap Buffer Control                 |     |

| CLC1-2                                  |     |

|                                         |     |

| Clock Control                                                  |     |

|----------------------------------------------------------------|-----|

| Comparator                                                     |     |

| CPU Core                                                       |     |

| CTMU                                                           |     |

| DAC1                                                           |     |

| DAC2                                                           |     |

| ICN                                                            |     |

| Interrupt Controller                                           |     |

| MCCP1                                                          |     |

| MCCP2                                                          |     |

| MCCP3<br>MSSP1 (I <sup>2</sup> C/SPI)                          | 51  |

| MSSP1 (I <sup>-</sup> C/SPI)<br>MSSP2 (I <sup>2</sup> C/SPI)   |     |

| NVM                                                            |     |

| Op Amp 1                                                       |     |

| Op Amp 2                                                       |     |

| Pad Configuration                                              |     |

| PMD                                                            |     |

| PORTA                                                          |     |

| PORTB                                                          |     |

| PORTC                                                          |     |

| Real-Time Clock and Calendar                                   |     |

| SCCP4                                                          |     |

| SCCP5                                                          |     |

| Timer1                                                         |     |

| UART1                                                          | 55  |

| UART2                                                          |     |

| Ultra Low-Power Wake-up                                        | 62  |

| Registers                                                      |     |

| AD1CHITH (A/D Scan Compare Hit,                                |     |

| High Word)                                                     | 219 |

| AD1CHITL (A/D Scan Compare Hit,                                |     |

| Low Word)                                                      |     |

| AD1CHS (A/D Sample Select)                                     |     |

| AD1CON1 (A/D Control 1)                                        |     |

| AD1CON2 (A/D Control 2)                                        |     |

| AD1CON3 (A/D Control 3)                                        |     |

| AD1CON5 (A/D Control 5)                                        | 217 |

| AD1CSSH (A/D Input Scan Select, High Word)                     |     |

| AD1CSSL (A/D Input Scan Select, Low Word)                      |     |

| AD1CTMENH (CTMU Enable, High Word)                             |     |

| AD1CTMENL (CTMU Enable, Low Word)                              |     |

| ALCFGRPT (Alarm Configuration)                                 | 186 |

| ALMINSEC (Alarm Minutes and                                    | 400 |

| Seconds Value)                                                 |     |

| ALMTHDY (Alarm Month and Day Value)                            |     |

| ALWDHR (Alarm Weekday and Hours Value)                         |     |

| AMPxCON (Op Amp x Control)                                     |     |

| ANSA (PORTA Analog Selection)<br>ANSB (PORTB Analog Selection) |     |

| ANSE (PORTE Analog Selection)                                  |     |

| BUFCON0 (Internal Voltage Reference                            | 155 |

| Control 0)                                                     | 232 |

| CCPxCON1H (CCPx Control 1 High)                                |     |

| CCPxCON1L (CCPx Control 1 Low)                                 |     |

| CCPxCON2H (CCPx Control 2 High)                                |     |

| CCPxCON2L (CCPx Control 2 Low)                                 |     |

| CCPxCON3H (CCPx Control 3 High)                                |     |

| CCPxCON3L (CCPx Control 3 Low)                                 |     |

| CCPxSTATL (CCPx Status)                                        |     |

| CLCxCONH (CLCx Control High)                                   |     |

| CLCxCONL (CLCx Control Low)                                    |     |

| CLCxGLSH (CLCx Gate Logic Input Select High)                   |     |

| CLCxGLSL (CLCx Gate Logic Input Select Low)                    | 202 |

| CLCxSEL (CLCx Input MUX Select)                                |     |

| CLKDIV (Clock Divider)                                         | 125 |

NOTES: