Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km202t-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-3: DEVICE FEATURES FOR                      | R THE PIC24FV1         |                                                                            |                        |                                         |  |  |  |  |  |

|-----------------------------------------------------|------------------------|----------------------------------------------------------------------------|------------------------|-----------------------------------------|--|--|--|--|--|

| Features                                            | PIC24FV16KM204         | PIC24FV08KM204                                                             | PIC24FV16KM202         | PIC24FV08KM202                          |  |  |  |  |  |

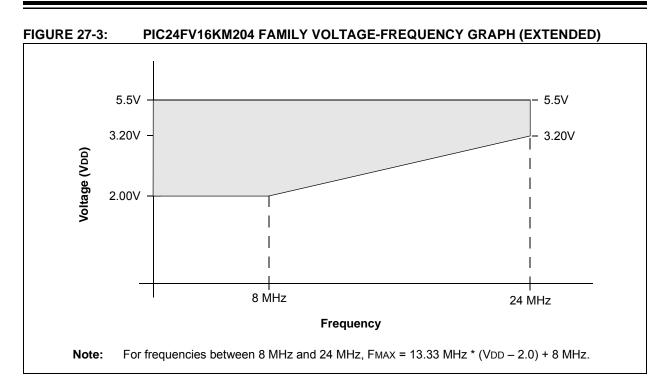

| Operating Frequency                                 |                        | DC-3                                                                       | 2 MHz                  |                                         |  |  |  |  |  |

| Program Memory (bytes)                              | 16K                    | 8K                                                                         | 16K                    | 8K                                      |  |  |  |  |  |

| Program Memory (instructions)                       | 5632                   | 2816                                                                       | 5632                   | 2816                                    |  |  |  |  |  |

| Data Memory (bytes)                                 |                        | 20                                                                         | )48                    | I                                       |  |  |  |  |  |

| Data EEPROM Memory (bytes)                          |                        | 5                                                                          | 12                     |                                         |  |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)          |                        | 40 (                                                                       | 36/4)                  |                                         |  |  |  |  |  |

| Voltage Range                                       |                        | 2.0-                                                                       | -5.5V                  |                                         |  |  |  |  |  |

| I/O Ports                                           | PORTB<                 | PORTA<11:7,5:0><br>PORTB<15:0><br>PORTB<15:0><br>PORTC<9:0><br>PORTB<15:0> |                        |                                         |  |  |  |  |  |

| Total I/O Pins                                      | 37                     |                                                                            |                        | 23                                      |  |  |  |  |  |

| Timers                                              | (One 16-bit timer, f   |                                                                            | 11<br>Ps with up to tv | vo 16/32 timers each)                   |  |  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                        |                                                                            | 3<br>2                 |                                         |  |  |  |  |  |

| Serial Communications<br>MSSP<br>UART               |                        |                                                                            | 2<br>2                 |                                         |  |  |  |  |  |

| Input Change Notification Interrupt                 | 36                     |                                                                            |                        | 22                                      |  |  |  |  |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                     |                                                                            |                        | 19                                      |  |  |  |  |  |

| Analog Comparators                                  |                        |                                                                            | 3                      |                                         |  |  |  |  |  |

| 8-Bit Digital-to-Analog Converters                  |                        |                                                                            | 2                      |                                         |  |  |  |  |  |

| Operational Amplifiers                              |                        |                                                                            | 2                      |                                         |  |  |  |  |  |

| Charge Time Measurement Unit (CTMU)                 |                        | Y                                                                          | íes 🛛                  |                                         |  |  |  |  |  |

| Real-Time Clock and Calendar (RTCC)                 |                        | Y                                                                          | 'es                    |                                         |  |  |  |  |  |

| Configurable Logic Cell (CLC)                       |                        |                                                                            | 2                      |                                         |  |  |  |  |  |

| Resets (and delays)                                 |                        | on, Hardware Tra                                                           |                        | , Illegal Opcode,<br>tion Word Mismatch |  |  |  |  |  |

| Instruction Set                                     | 76 Base Inst           | ructions, Multiple                                                         | e Addressing N         | Iode Variations                         |  |  |  |  |  |

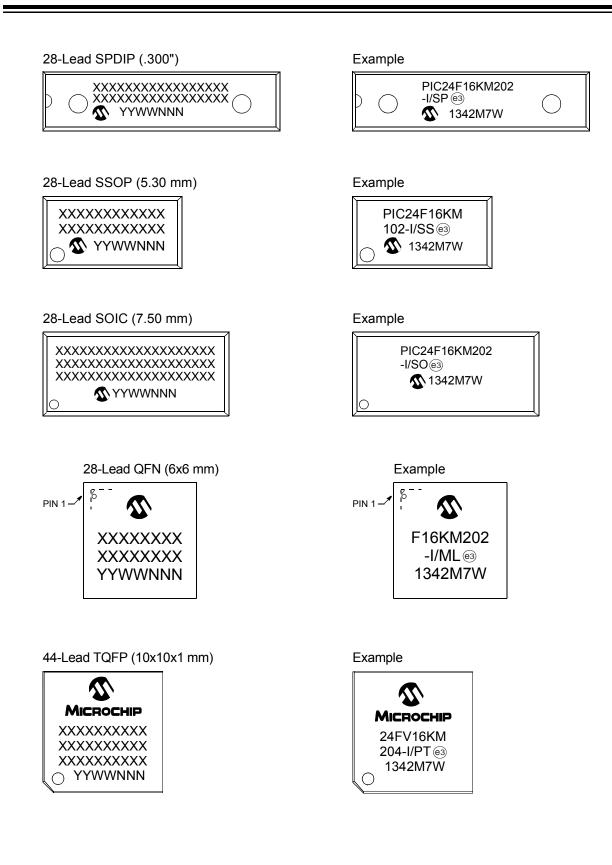

| Packages                                            | 44-Pin QFI<br>48-Pin U |                                                                            | SPDIP/S                | 28-Pin<br>SOP/SOIC/QFN                  |  |  |  |  |  |

#### TABLE 1-3: DEVICE FEATURES FOR THE PIC24FV16KM204 FAMILY

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          | F<br>Pin Number                  |                                  |               |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART2 16x Baud Rate Clock Output               |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | _                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | _                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |

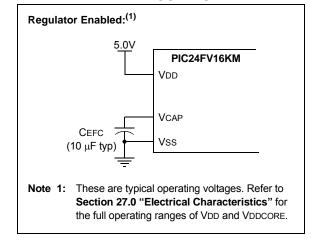

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

### TABLE 4-17: OP AMP 1 REGISTER MAP

| File Name              | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|------------------------|-------|--------|--------|---------|--------|--------|--------|-------|-------|--------|-------|---------|---------|---------|---------|---------|---------|---------------|

|                        |       |        |        |         |        |        |        |       |       |        |       |         |         |         |         |         |         |               |

| AMP1CON <sup>(1)</sup> | 24Ah  | AMPEN  | _      | AMPSIDL | AMPSLP | _      | _      | _     | —     | SPDSEL | _     | NINSEL2 | NINSEL1 | NINSEL0 | PINSEL2 | PINSEL1 | PINSEL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: This registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-18: OP AMP 2 REGISTER MAP

| File Name              | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|------------------------|-------|--------|--------|---------|--------|--------|--------|-------|-------|--------|-------|---------|---------|---------|---------|---------|---------|---------------|

| AMP2CON <sup>(1)</sup> | 24Ch  | AMPEN  | _      | AMPSIDL | AMPSLP | _      | _      | _     | _     | SPDSEL | —     | NINSEL2 | NINSEL1 | NINSEL0 | PINSEL2 | PINSEL1 | PINSEL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: This registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-19: DAC1 REGISTER MAP

| File Name            | Addr.   | Bit 15                  | Bit 14                  | Bit 13      | Bit 12      | Bit 11      | Bit 10      | Bit 9      | Bit 8      | Bit 7                  | Bit 6      | Bit 5      | Bit 4                  | Bit 3      | Bit 2      | Bit 1      | Bit 0      | All<br>Resets |

|----------------------|---------|-------------------------|-------------------------|-------------|-------------|-------------|-------------|------------|------------|------------------------|------------|------------|------------------------|------------|------------|------------|------------|---------------|

| DAC1CON              | 1) 274h | DACEN                   | -                       | DACSIDL     | DACSLP      | DACFM       | -           | SRDIS      | DACTRIG    | DACOE                  | DACTSEL4   | DACTSEL3   | DACTSEL2               | DACTSEL1   | DACTSEL0   | DACREF1    | DACREF0    | 0000          |

| DAC1DAT <sup>(</sup> | ) 276h  | DACDAT15 <sup>(2)</sup> | DACDAT14 <sup>(2)</sup> | DACDAT13(2) | DACDAT12(2) | DACDAT11(2) | DACDAT10(2) | DACDAT9(2) | DACDAT8(2) | DACDAT7 <sup>(2)</sup> | DACDAT6(2) | DACDAT5(2) | DACDAT4 <sup>(2)</sup> | DACDAT3(2) | DACDAT2(2) | DACDAT1(2) | DACDATO(2) | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM1XX devices.

2: The 8-bit result format depends on the value of the DACFM control bit.

#### TABLE 4-20: DAC2 REGISTER MAP

| File Name              | Addr. | Bit 15      | Bit 14      | Bit 13      | Bit 12      | Bit 11      | Bit 10      | Bit 9      | Bit 8      | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | All<br>Resets |

|------------------------|-------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|---------------|

| DAC2CON <sup>(1)</sup> | 278h  | DACEN       | -           | DACSIDL     | DACSLP      | DACFM       | -           | SRDIS      | DACTRIG    | DACOE      | DACTSEL4   | DACTSEL3   | DACTSEL2   | DACTSEL1   | DACTSEL0   | DACREF1    | DACREF0    | 0000          |

| DAC2DAT <sup>(1)</sup> | 27Ah  | DACDAT15(2) | DACDAT14(2) | DACDAT13(2) | DACDAT12(2) | DACDAT11(2) | DACDAT10(2) | DACDAT9(2) | DACDAT8(2) | DACDAT7(2) | DACDAT6(2) | DACDAT5(2) | DACDAT4(2) | DACDAT3(2) | DACDAT2(2) | DACDAT1(2) | DACDATO(2) | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

2: The 8-bit result format depends on the value of the DACFM control bit.

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| ; | Set up NVMCO  | N for row programming operation | ns  |                                       |

|---|---------------|---------------------------------|-----|---------------------------------------|

|   | MOV           | #0x4004, W0                     | ;   |                                       |

|   | MOV           | W0, NVMCON                      | ;   | Initialize NVMCON                     |

| ; | Set up a poir | nter to the first program memor | ry  | location to be written                |

| ; | program memo: | ry selected, and writes enabled | b   |                                       |

|   | MOV           | #0x0000, W0                     | ;   |                                       |

|   | MOV           | W0, TBLPAG                      | ;   | Initialize PM Page Boundary SFR       |

|   | MOV           | #0x1500, W0                     | ;   | An example program memory address     |

| ; | Perform the   | TBLWT instructions to write the | e . | latches                               |

| ; | 0th_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_0, W2                 | ;   |                                       |

|   | MOV           | <pre>#HIGH_BYTE_0, W3</pre>     | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | lst_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_1, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_1, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | 2nd_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_2, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_2, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

| ; | 32nd_program  | —                               |     |                                       |

|   |               | #LOW_WORD_31, W2                | ;   |                                       |

|   |               | #HIGH_BYTE_31, W3               | ;   |                                       |

|   |               | W2, [W0]                        |     | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0]                        | ;   | Write PM high byte into program latch |

| 1 |               |                                 |     |                                       |

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234 // Variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

// Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

// Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

// Write to address low word

__builtin_tblwtl(offset, progData[i++]);

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

| REGISTER      |                            |                                        |                         | KI CONTRO        | LREGISTE       | ĸ              |             |

|---------------|----------------------------|----------------------------------------|-------------------------|------------------|----------------|----------------|-------------|

| R/SO-0, HC    | R/W-0                      | R/W-0                                  | R/W-0                   | U-0              | U-0            | U-0            | U-0         |

| WR            | WREN                       | WRERR                                  | PGMONLY                 | _                | _              | _              | _           |

| bit 15        | •                          |                                        |                         | ·                |                |                | bit 8       |

|               |                            |                                        |                         |                  |                |                |             |

| U-0           | R/W-0                      | R/W-0                                  | R/W-0                   | R/W-0            | R/W-0          | R/W-0          | R/W-0       |

| _             | ERASE                      | NVMOP5                                 | NVMOP4                  | NVMOP3           | NVMOP2         | NVMOP1         | NVMOP0      |

| bit 7         |                            |                                        |                         |                  |                |                | bit 0       |

|               |                            |                                        |                         |                  |                |                |             |

| Legend:       |                            | HC = Hardware                          | Clearable bit           | U = Unimple      | mented bit, re | ead as '0'     |             |

| R = Readable  | bit                        | W = Writable bit                       |                         | S = Settable     | Only bit       |                |             |

| -n = Value at | POR                        | '1' = Bit is set                       |                         | '0' = Bit is cle | eared          | x = Bit is unk | nown        |

| bit 15        |                            | ontrol bit (program<br>a data EEPROM e |                         | cle (can be set  | . but not clea | red in softwar | e)          |

|               |                            | le is complete (cle                    |                         |                  |                |                | - /         |

| bit 14        | WREN: Write                | Enable bit (erase                      | or program)             |                  |                |                |             |

|               | 1 = Enables a              | an erase or progra                     | m operation             |                  |                |                |             |

|               | 0 = No operat              | tion allowed (devic                    | ce clears this bit      | on completion    | of the write/e | erase operatio | on)         |

| bit 13        |                            | sh Error Flag bit                      |                         |                  |                |                |             |

|               |                            | operation is prem                      | aturely terminat        | ted (any MCL     | R or WDT F     | Reset during   | programming |

|               | operation<br>0 = The write | )<br>operation comple                  | eted successfully       | /                |                |                |             |

| bit 12        |                            | Program Only Enal                      | ,                       | ,                |                |                |             |

| 511 12        |                            | eration is executed                    |                         | a target addres  | s(es) first    |                |             |

|               |                            | c erase-before-wr                      | -                       | ,                | -()            |                |             |

|               | Write operation            | ons are preceded                       | automatically by        | an erase of th   | e target addr  | ess(es).       |             |

| bit 11-7      | Unimplemen                 | ted: Read as '0'                       |                         |                  |                |                |             |

| bit 6         |                            | e Operation Selec                      |                         |                  |                |                |             |

|               |                            | an erase operation                     |                         |                  |                |                |             |

|               |                            | a write operation                      |                         |                  |                |                |             |

| bit 5-0       |                            | Programming C<br>ions (when ERAS)      | -                       | and byte bits    |                |                |             |

|               | 011010 = Era               | •                                      | $\perp$ DIUS $\perp$ ). |                  |                |                |             |

|               | 011001 = Era               |                                        |                         |                  |                |                |             |

|               | 011000 = Era               |                                        |                         |                  |                |                |             |

|               |                            | ase entire data EE                     | -                       |                  |                |                |             |

|               | • •                        | Operations (when                       | n ERASE bit is '        | <u>0'):</u>      |                |                |             |

|               | 0001xx = Wr                | ite 1 word                             |                         |                  |                |                |             |

|               |                            |                                        |                         |                  |                |                |             |

#### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

#### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC Oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

### 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSCx bits in the Flash Configuration Word (FOSCSEL<2:0>); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

### 7.4 Brown-out Reset (BOR)

The PIC24FXXXXX family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the Power-up Timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the Brown-out Reset does not automatically enable the PWRT.

### 7.4.1 LOW-POWER BOR (LPBOR)

The Low-Power BOR is an alternate setting for the BOR, designed to consume minimal power. In LPBOR mode, BORV<1:0> (FPOR<6:5>) = 00. The BOR trip point is approximately 2.0V. Due to the low current consumption, the accuracy of the LPBOR mode can vary.

Unlike the other BOR modes, LPBOR mode will not cause a device Reset when VDD drops below the trip point. Instead, it re-arms the POR circuit to ensure that the device will reset properly in the event that VDD continues to drop below the minimum operating voltage.

The device will continue to execute code when VDD is below the level of the LPBOR trip point. A device that requires falling edge BOR protection to prevent code from improperly executing should use one of the other BOR voltage settings.

#### 8.3 Interrupt Control and Status Registers

The PIC24FV16KM204 family of devices implements a total of 33 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS6

- · IEC0 through IEC6

- IPC0 through IPC7, IPC10, IPC12, IPC15, IPC16, IPC18 through IPC20 and IPC24

- INTTREG

Global Interrupt Enable (GIE) control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIVT.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU Interrupt Priority Level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All Interrupt registers are described in Register 8-1 through Register 8-35, in the following sections.

### REGISTER 8-21: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0                 | R/W-1      | R/W-0                            | R/W-0   | U-0               | U-0              | U-0             | U-0     |

|---------------------|------------|----------------------------------|---------|-------------------|------------------|-----------------|---------|

|                     | U1RXIP2    | U1RXIP1                          | U1RXIP0 | _                 | —                | —               | _       |

| bit 15              |            |                                  |         |                   |                  |                 | bit 8   |

| U-0                 | U-0        | U-0                              | U-0     | U-0               | R/W-1            | R/W-0           | R/W-0   |

| _                   | _          | _                                | _       | _                 | CCT2IP2          | CCT2IP1         | CCT2IP0 |

| bit 7               |            |                                  |         | •                 |                  |                 | bit 0   |

|                     |            |                                  |         |                   |                  |                 |         |

| Legend:             |            |                                  |         |                   |                  |                 |         |

| R = Readab          | le bit     | W = Writable                     | bit     | U = Unimplem      | nented bit, read | l as '0'        |         |

| -n = Value a        | t POR      | '1' = Bit is set                 |         | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|                     |            |                                  |         |                   |                  |                 |         |

|                     |            |                                  |         |                   |                  |                 |         |

| bit 15              | Unimplemen | ted: Read as 'd                  | כ'      |                   |                  |                 |         |

| bit 15<br>bit 14-12 | •          | ted: Read as 'd<br>•: UART1 Rece |         | Priority bits     |                  |                 |         |

- bit 11-3

bit 2-0

CCT2IP<2:0>: Capture/Compare 2 Timer Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt)

- ٠

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 8-31: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

| _       | —   | —   | —   | —   | —       | —       | —       |

| bit 15  |     | •   |     |     | •       |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _       | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Logondi |     |     |     |     |         |         |         |

| Legend: |  |

|---------|--|

|---------|--|

bit 2-0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 8-33: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0                                | U-0        | U-0              | U-0               | U-0               | U-0              | U-0      | U-0      |

|------------------------------------|------------|------------------|-------------------|-------------------|------------------|----------|----------|

| —                                  | —          | —                | —                 | —                 | —                | —        | —        |

| bit 15                             |            |                  |                   |                   |                  |          | bit 8    |

|                                    |            |                  |                   |                   |                  |          |          |

| U-0                                | U-0        | U-0              | U-0               | U-0               | R/W-1            | R/W-0    | R/W-0    |

| _                                  | _          | _                | _                 | —                 | ULPWUIP2         | ULPWUIP1 | ULPWUIP0 |

| bit 7                              |            |                  |                   |                   |                  |          | bit 0    |

| Legend:                            |            |                  |                   |                   |                  |          |          |

| R = Readable                       | e bit      | W = Writable     | bit               | U = Unimplem      | nented bit, read | l as '0' |          |

| -n = Value at POR '1' = Bit is set |            |                  | '0' = Bit is clea | ared              | x = Bit is unkr  | iown     |          |

|                                    |            |                  |                   |                   |                  |          |          |

| bit 15-3                           | Unimplemer | ted: Read as '0  | )'                |                   |                  |          |          |

| bit 2-0                            | ULPWUIP<2  | :0>: Ultra Low-F | Power Wake-u      | p Interrupt Prior | rity bits        |          |          |

111 = Interrupt is Priority 7 (highest priority interrupt)

- •

- 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

## REGISTER 8-34: IPC24: INTERRUPT PRIORITY CONTROL REGISTER 24

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | CLC2IP2 | CLC2IP1 | CLC2IP0 | —   | CLC1IP2 | CLC1IP1 | CLC1IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 6-4  | CLC2IP<2:0>: CLC2 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

| bit 3    | Unimplemented: Read as '0'                                 |

| bit 2-0  | CLC1IP<2:0>: CLC1 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

|          |                                                            |

## REGISTER 14-2: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE) (CONTINUED)

- BF: Buffer Full Status bit

- In Transmit mode:

bit 0

- 1 = Transmit is in progress, SSPxBUF is full

- 0 = Transmit is complete, SSPxBUF is empty

- In Receive mode:

- 1 = SSPxBUF is full (does not include the  $\overline{ACK}$  and Stop bits)

- 0 = SSPxBUF is empty (does not include the  $\overline{ACK}$  and Stop bits)

- **Note 1:** This bit is cleared on Reset and when SSPEN is cleared.

- 2: This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit or not ACK bit.

- 3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

| U-0                              | U-0                                                                                                           | U-0                                                                                                        | U-0                                                                                                                      | U-0                                                    | U-0              | U-0              | U-0       |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|------------------|-----------|

| _                                | —                                                                                                             | —                                                                                                          | —                                                                                                                        | —                                                      | —                | —                | —         |

| bit 15                           |                                                                                                               |                                                                                                            |                                                                                                                          | •                                                      | •                | •                | bit       |

| R-0                              | R/W-0                                                                                                         | R/W-0                                                                                                      | R/W-0                                                                                                                    | R/W-0                                                  | R/W-0            | R/W-0            | R/W-0     |

| ACKTIM                           | PCIE                                                                                                          | SCIE                                                                                                       | BOEN <sup>(1)</sup>                                                                                                      | SDAHT                                                  | SBCDE            | AHEN             | DHEN      |

| bit 7                            |                                                                                                               |                                                                                                            |                                                                                                                          |                                                        |                  |                  | bit       |

| Legend:                          |                                                                                                               |                                                                                                            |                                                                                                                          |                                                        |                  |                  |           |

| R = Readab                       | le bit                                                                                                        | W = Writable                                                                                               | bit                                                                                                                      | U = Unimplem                                           | nented bit, read | l as '0'         |           |

| -n = Value a                     | t POR                                                                                                         | '1' = Bit is set                                                                                           | :                                                                                                                        | '0' = Bit is clea                                      | ared             | x = Bit is unkn  | iown      |

| bit 7<br>bit 6<br>bit 5<br>bit 4 | Unused in SF<br>PCIE: Stop C<br>Unused in SF<br>SCIE: Start C<br>Unused in SF<br>BOEN: Buffer<br>In SPI Slave | PI mode.<br>ondition Interru<br>PI mode.<br>ondition Interru<br>PI mode.<br>r Overwrite En<br><u>mode:</u> | e Status bit (I <sup>2</sup> C<br>ıpt Enable bit (I<br>ıpt Enable bit (I<br>able bit <sup>(1)</sup><br>ry time that a ne | <sup>2</sup> C mode only)<br><sup>2</sup> C mode only) |                  | vring the BE bit |           |

| hit 2                            | 0 = If a new<br>the SSP>                                                                                      | byte is receive<br>cCON1 registe                                                                           | d with the BF b<br>r is set and the<br>election bit (I <sup>2</sup> C                                                    | it of the SSPxS<br>buffer is not up                    | STAT register a  |                  | SSPOV bit |

| bit 3                            | Unused in SF                                                                                                  |                                                                                                            |                                                                                                                          | mode only)                                             |                  |                  |           |

| bit 2                            | SBCDE: Slav                                                                                                   | ve Mode Bus C                                                                                              | ollision Detect                                                                                                          | Enable bit (I <sup>2</sup> C                           | Slave mode or    | nly)             |           |

|                                  | Unused in SPI mode.                                                                                           |                                                                                                            |                                                                                                                          |                                                        |                  |                  |           |

| bit 1                            | AHEN: Address Hold Enable bit (I <sup>2</sup> C Slave mode only)<br>Unused in SPI mode.                       |                                                                                                            |                                                                                                                          |                                                        |                  |                  |           |

| bit 0                            | <b>DHEN:</b> Data Hold Enable bit (Slave mode only)<br>Unused in SPI mode.                                    |                                                                                                            |                                                                                                                          |                                                        |                  |                  |           |

| Note 1: F                        | for Daisy-Chained SPI Operation: Allows the user to ignore all but the last received byte. SSPOV is s         |                                                                                                            |                                                                                                                          |                                                        |                  |                  |           |

#### REGISTER 14-6: SSPxCON3: MSSPx CONTROL REGISTER 3 (SPI MODE)

**Note 1:** For Daisy-Chained SPI Operation: Allows the user to ignore all but the last received byte. SSPOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSPxBUF.

| R/W-0         | R/W-0                                                                                                              | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0        |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|--------------|--|--|--|--|

| CH0NB2        | CH0NB1                                                                                                             | CH0NB0                               | CH0SB4         | CH0SB3            | CH0SB2           | CH0SB1          | CH0SB0       |  |  |  |  |

| bit 15        |                                                                                                                    |                                      |                |                   |                  |                 | bit          |  |  |  |  |

| R/W-0         | R/W-0                                                                                                              | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0        |  |  |  |  |

| CH0NA2        | CH0NA1                                                                                                             | CHONAO                               | CH0SA4         | CH0SA3            | CH0SA2           | CH0SA1          | CH0SA0       |  |  |  |  |

| bit 7         |                                                                                                                    |                                      |                |                   |                  |                 | bit          |  |  |  |  |

| Legend:       |                                                                                                                    |                                      |                |                   |                  |                 |              |  |  |  |  |

| R = Readabl   | le bit                                                                                                             | W = Writable                         | bit            | U = Unimplem      | nented bit, read | d as '0'        |              |  |  |  |  |

| -n = Value at | POR                                                                                                                | '1' = Bit is set                     |                | '0' = Bit is clea |                  | x = Bit is unkr | nown         |  |  |  |  |

| L: 45 40      |                                                                                                                    | · Comple D Ch                        | annal O Nagati | ve less to Celest | h:to             |                 |              |  |  |  |  |

| bit 15-13     | 111 = AN6 <sup>(1)</sup>                                                                                           | •                                    | annei 0 Negati | ve Input Select   | DIIS             |                 |              |  |  |  |  |

|               | $111 = AN6^{(1)}$<br>$110 = AN5^{(2)}$                                                                             |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 101 = AN3                                                                                                          |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 101 - AN4<br>100 = AN3                                                                                             |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 011 = AN2                                                                                                          |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 010 = AN1                                                                                                          |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 001 = ANO                                                                                                          |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 000 = AVss                                                                                                         |                                      |                |                   |                  |                 |              |  |  |  |  |

| bit 12-8      | CH0SB<4:0>: S/H Amplifier Positive Input Select for MUX B Multiplexer Setting bits                                 |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 11111 = Unimplemented, do not use                                                                                  |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 11110 = $AVDD^{(3)}$                                                                                               |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 11101 = AVss <sup>(3)</sup>                                                                                        |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 11100 = Upper guardband rail (0.785 * VDD)                                                                         |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 11011 = Lower guardband rail (0.215 * VDD)                                                                         |                                      |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | rnal Band Gap                        |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | 1 = Unimpleme                        |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    |                                      |                | puts are floating |                  |                 |              |  |  |  |  |

|               |                                                                                                                    |                                      |                | puts are floatin  |                  |                 |              |  |  |  |  |

|               |                                                                                                                    |                                      |                |                   |                  | /U temperature  | sensor input |  |  |  |  |

|               | does not require the corresponding CTMEN22 (AD1CTMENH<6>) bit)                                                     |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 10101 = Channel 0 positive input is AN20                                                                           |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 10100 = Channel 0 positive input is AN20<br>10011 = Channel 0 positive input is AN19                               |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 10011 = Channel 0 positive input is AN19<br>10010 = Channel 0 positive input is AN18 <sup>(2)</sup>                |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | 10010 = Channel 0 positive input is AN18 <sup>(2)</sup><br>10001 = Channel 0 positive input is AN17 <sup>(2)</sup> |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | •                                                                                                                  |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | •                                                                                                                  |                                      |                |                   |                  |                 |              |  |  |  |  |

|               | •                                                                                                                  |                                      |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |              |  |  |  |  |

|               | 00110 = Channel 0 positive input is AN6 <sup>(1)</sup><br>00101 = Channel 0 positive input is AN5 <sup>(2)</sup>   |                                      |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    |                                      |                | ,                 |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | annel 0 positive<br>annel 0 positive |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |              |  |  |  |  |

|               |                                                                                                                    | annel 0 positive                     |                |                   |                  |                 |              |  |  |  |  |

| Note 1: T     | his is implement                                                                                                   |                                      | •              |                   |                  |                 |              |  |  |  |  |

|               | his is implement                                                                                                   | -                                    | -              | es only           |                  |                 |              |  |  |  |  |

| <b>Z</b> . 1  |                                                                                                                    |                                      |                | So only.          |                  |                 |              |  |  |  |  |

3: The band gap value used for this input is 2x or 4x the internal VBG, which is selected when PVCFG<1:0> = 1x.

#### REGISTER 19-5: AD1CHS: A/D SAMPLE SELECT REGISTER

DS30003030B-page 218

#### REGISTER 22-1: CMxCON: COMPARATOR x CONTROL REGISTERS (CONTINUED)

- bit 2 Unimplemented: Read as '0'

- bit 1-0 **CCH<1:0>:** Comparator x Channel Select bits

- 11 = Inverting input of the comparator connects to BGBUF1<sup>(1)</sup>

- 10 = Inverting input of the comparator connects to the CxIND pin

- 01 = Inverting input of the comparator connects to the CxINC pin

- 00 = Inverting input of the comparator connects to the CxINB pin

- **Note 1:** BGBUF1 voltage is configured by BUFREF1<1:0> (BUFCON0<1:0>).

- 2: If the EVPOL<1:0> bits are set to a value other than '00', the first interrupt generated will occur on any transition of COUT. Subsequent interrupts will occur based on the EVPOLx bits setting.

#### REGISTER 22-2: CMSTAT: COMPARATOR MODULE STATUS REGISTER

| R/W-0  | U-0 | U-0 | U-0 | U-0 | R-0, HSC             | R-0, HSC             | R-0, HSC |

|--------|-----|-----|-----|-----|----------------------|----------------------|----------|

| CMIDL  | —   | —   | —   | —   | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT    |

| bit 15 |     |     |     |     |                      |                      | bit 8    |

|        |     |     |     |     |                      |                      |          |

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0, HSC             | R-0, HSC             | R-0, HSC |

|-------|-----|-----|-----|-----|----------------------|----------------------|----------|

| —     | —   | —   | —   | —   | C3OUT <sup>(1)</sup> | C2OUT <sup>(1)</sup> | C1OUT    |

| bit 7 |     |     |     |     |                      |                      | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                             |                    |  |

|-------------------|---------------------------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15    | CMIDL: Comparator x Stop in Idle Mode bit                                                                                                                                                |