#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km202t-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Diagrams**

| 20-Pin PDIP/SSOP/SOIC | RA5       1       20       VDD         RA0       2       19       VSs         RA1       3       18       RB15         RB0       4       17       RB14         RB1       5       RB12         RA2       6       9       16         RA3       8       00       VDC         RA4       10       11       RB9 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dia | Pin Features                                  |                                            |  |  |  |  |  |

|-----|-----------------------------------------------|--------------------------------------------|--|--|--|--|--|

| Pin | PIC24F08KM101                                 | PIC24FVKM08KM101                           |  |  |  |  |  |

| 1   | MCLR/Vpp/RA5                                  |                                            |  |  |  |  |  |

| 2   | PGEC2/CVREF+/VREF+/AN0/CN2/RA0                |                                            |  |  |  |  |  |

| 3   | PGED2/CVREF-/VREF-/AN1/CN3/RA1                |                                            |  |  |  |  |  |

| 4   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0      |                                            |  |  |  |  |  |

| 5   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                |                                            |  |  |  |  |  |

| 6   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                 |                                            |  |  |  |  |  |

| 7   | OSCI/CLKI/AN13/C1INB/CN30/RA2                 |                                            |  |  |  |  |  |

| 8   | OSCO/CLKO/AN14/C1INA/CN29/RA3                 |                                            |  |  |  |  |  |

| 9   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4               |                                            |  |  |  |  |  |

| 10  | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/    | RA4                                        |  |  |  |  |  |

| 11  | AN19/U1TX/CTED1/INT0/CN23/RB7                 | AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7     |  |  |  |  |  |

| 12  | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8          |                                            |  |  |  |  |  |

| 13  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4   | /CN21/RB9                                  |  |  |  |  |  |

| 14  | IC1/OC1A/INT2/CN8/RA6                         | VCAP OR VDDCORE                            |  |  |  |  |  |

| 15  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12         | AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |  |

| 16  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13           |                                            |  |  |  |  |  |

| 17  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RE | 814                                        |  |  |  |  |  |

| 18  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15            |                                            |  |  |  |  |  |

| 19  | Vss/AVss                                      |                                            |  |  |  |  |  |

| 20  | Vdd/AVdd                                      |                                            |  |  |  |  |  |

## **Pin Diagrams (Continued)**

|                                                                                                                                                                                                      | Pin      | Pin Features                        |                                         |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------|-----------------------------------------|--|--|

| 48-Pin UQFN <sup>(1)</sup>                                                                                                                                                                           | FIII     | PIC24FXXKMX04                       | PIC24FVXXKMX04                          |  |  |

| RBS<br>VCDD<br>VCDD<br>VCDD<br>VCDD<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3                                                                                            | 1        | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/    | /CLC10/CTED4/CN21/RB9                   |  |  |

| $\overline{x} \overline{x} \overline{x} \overline{x} \overline{z} \overline{z} \overline{z} \overline{z} \overline{z} \overline{x} \overline{x} \overline{x} \overline{x} \overline{x} \overline{x}$ | 2        | U1RX/ /CN18/RC6                     |                                         |  |  |

| RB9 1 8 4 8 4 7 7 7 7 7 7 8 8 8 8 8 8 8 8 8 8                                                                                                                                                        | 3        | U1TX/ /CN17/RC7                     |                                         |  |  |

| RB9 1 36 RB4<br>RC6 2 35 RA8                                                                                                                                                                         |          | OC2/CN20/RC8                        |                                         |  |  |

| RC7 3 34 RA3<br>RC8 4 33 RA2                                                                                                                                                                         |          | IC4/OC2F/CTED7/CN19/RC9             |                                         |  |  |

| RC9 5 32 n/c                                                                                                                                                                                         | 6        | IC1/ / /CTED3/CN9/RA7               | 1                                       |  |  |

| RA7         6         PIC24FXXKMX04         31         Vss           RA6         7         PIC24FVXXKMX04         30         Vbb                                                                     |          | /OC1A/CTED1/INT2/CN8/RA6            | VDDCORE OF VCAP                         |  |  |

| n/c 8 29 RC2                                                                                                                                                                                         | 2 0      | n/c                                 | n/c                                     |  |  |

| RB10 9 28 RC <sup>2</sup><br>RB11 10 27 RC                                                                                                                                                           | <u> </u> | PGED2/SDI1/OC1C/CTED11/CN16/RB10    |                                         |  |  |

| RB12 11 26 RB3                                                                                                                                                                                       | 3 10     | PGEC2/SCK1/OC2A/CTED9/CN15/RB11     |                                         |  |  |

| RB13 12 25 RB2 25 RB2 25 RB2                                                                                                                                                                         | 2 11     | /AN12/HLVDIN/ /CTED2/<br>CN14/RB12  | /AN12/HLVDIN/ /CTED2/<br>INT2/CN14/RB12 |  |  |

|                                                                                                                                                                                                      | 12       | / /AN11/SDO1/OC1D/CTPLS             |                                         |  |  |

| RA10<br>RA11<br>RB14<br>RB14<br>Vss/AVsp<br>NCLR/RA5<br>N/C<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10                                                                    | 13       | / /CN35/RA10                        |                                         |  |  |

| R R SSS/ANDI                                                                                                                                                                                         | 14       | / /CTED8/CN36/RA11                  |                                         |  |  |

| > >                                                                                                                                                                                                  | 15       | /CVREF/ / /AN10/                    | / /C1OUT/OCFA/CTED5/INT1/               |  |  |

|                                                                                                                                                                                                      |          | CN12/RB14                           |                                         |  |  |

|                                                                                                                                                                                                      | 16       |                                     | I/TCKIA/CTED6/CN11/RB15                 |  |  |

|                                                                                                                                                                                                      | 17       | Vss/AVss                            |                                         |  |  |

|                                                                                                                                                                                                      | 18       | VDD/AVDD                            |                                         |  |  |

|                                                                                                                                                                                                      | 19       | MCLR/VPP/RA5                        |                                         |  |  |

|                                                                                                                                                                                                      | 20<br>21 | n/c<br>CVREF+/VREF+/ +/AN0/ /       | CVREF+/VREF+/ +/AN0/ /                  |  |  |

|                                                                                                                                                                                                      | 21       | CN2/RA0                             | CTED1/CN2/RA0                           |  |  |

|                                                                                                                                                                                                      | 22       | CVREF-/VREF-/AN1/CN3/RA1            |                                         |  |  |

|                                                                                                                                                                                                      | 23       | PGED1/AN2/CTCMP/ULPWU/C1IND/        | / /CN4/RB0                              |  |  |

|                                                                                                                                                                                                      | 24       | PGEC1/ / /AN3/C1INC/                | / /CTED12/CN5/RB1                       |  |  |

|                                                                                                                                                                                                      | 25       | / /AN4/C1INB/ / /T                  | CKIB/CTED13/CN6/RB2                     |  |  |

|                                                                                                                                                                                                      | 26       | /AN5/C1INA/ / /CN7/RB3              |                                         |  |  |

|                                                                                                                                                                                                      | 27       | AN6/CN32/RC0                        |                                         |  |  |

|                                                                                                                                                                                                      | 28       |                                     |                                         |  |  |

|                                                                                                                                                                                                      | 29<br>30 | AN8/CN10/RC2<br>Vdd                 |                                         |  |  |

|                                                                                                                                                                                                      | 30       | Vss                                 |                                         |  |  |

|                                                                                                                                                                                                      | 32       | n/c                                 |                                         |  |  |

|                                                                                                                                                                                                      | 33       | OSCI/AN13/CLKI/CN30/RA2             |                                         |  |  |

|                                                                                                                                                                                                      | 34       | OSCO/CLKO/AN14/CN29/RA3             |                                         |  |  |

|                                                                                                                                                                                                      | 35       | OCFB/CN33/RA8                       |                                         |  |  |

|                                                                                                                                                                                                      | 36       | SOSCI/AN15/ / /CN1/RB4              |                                         |  |  |

|                                                                                                                                                                                                      | 37       | SOSCO/SCLKI/AN16/PWRLCLK/ /CN       | 0/RA4                                   |  |  |

|                                                                                                                                                                                                      | 38       | /CN34/RA9                           |                                         |  |  |

|                                                                                                                                                                                                      | 39       | /CN28/RC3                           |                                         |  |  |

|                                                                                                                                                                                                      | 40       | /CN25/RC4                           |                                         |  |  |

|                                                                                                                                                                                                      | 41       | /CN26/RC5                           |                                         |  |  |

| Legend: Values in indicate pin                                                                                                                                                                       | 42       | Vss                                 |                                         |  |  |

| Legend: Values in indicate pin<br>function differences between                                                                                                                                       | 43       | VDD                                 |                                         |  |  |

| PIC24F(V)XXKM202 and                                                                                                                                                                                 | 44       | n/c                                 |                                         |  |  |

| PIC24F(V)XXKM102 devices.                                                                                                                                                                            | 45       | PGED3/AN17/ASDA1/OC1E/CLCINA/CN27/F |                                         |  |  |

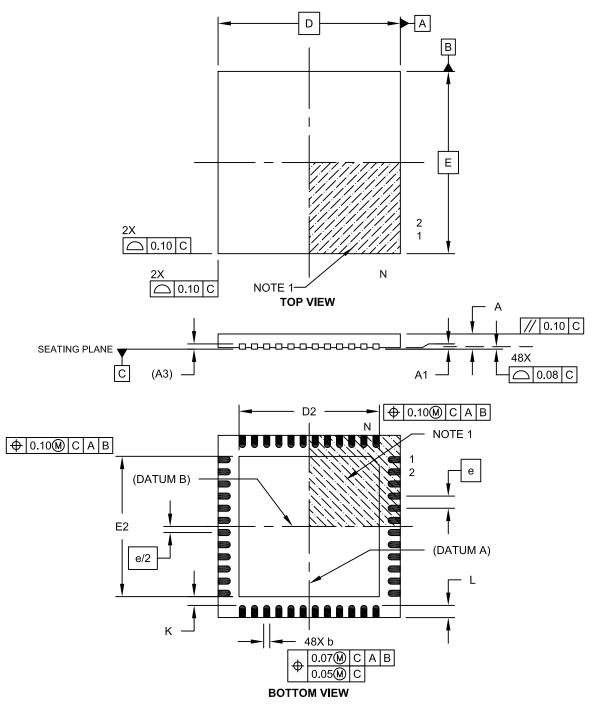

| Note 1: Exposed pad on underside of                                                                                                                                                                  | 46       | PGEC3/AN18/ASCL1/OC1F/CLCINB/CN24/F |                                         |  |  |

| device is connected to Vss.                                                                                                                                                                          | 47       | AN19/INT0/CN23/RB7                  | AN19/ /OC1A/INT0/CN23/RB7               |  |  |

|                                                                                                                                                                                                      | 48       | AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/  | CN22/RB8                                |  |  |

| TABLE 1-3:       DEVICE FEATURES FOR THE PIC24FV16KM204 FAMILY |                                                                       |                    |                             |                                         |  |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|-----------------------------|-----------------------------------------|--|--|--|--|

| Features                                                       | PIC24FV16KM204                                                        | PIC24FV08KM204     | PIC24FV16KM202              | PIC24FV08KM202                          |  |  |  |  |

| Operating Frequency                                            |                                                                       | DC-3               | 2 MHz                       |                                         |  |  |  |  |

| Program Memory (bytes)                                         | 16K                                                                   | 8K                 | 16K                         | 8K                                      |  |  |  |  |

| Program Memory (instructions)                                  | 5632                                                                  | 2816               | 5632                        | 2816                                    |  |  |  |  |

| Data Memory (bytes)                                            |                                                                       | 20                 | )48                         | I                                       |  |  |  |  |

| Data EEPROM Memory (bytes)                                     |                                                                       | 5                  | 12                          |                                         |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)                     |                                                                       | 40 (               | 36/4)                       |                                         |  |  |  |  |

| Voltage Range                                                  |                                                                       | 2.0-               | -5.5V                       |                                         |  |  |  |  |

| I/O Ports                                                      | PORTA<1<br>PORTB<<br>PORTC                                            | :15:0>             | PORTA<7,5:0><br>PORTB<15:0> |                                         |  |  |  |  |

| Total I/O Pins                                                 | 37                                                                    |                    |                             | 23                                      |  |  |  |  |

| Timers                                                         | 11<br>(One 16-bit timer, five MCCPs/SCCPs with up to two 16/32 timers |                    |                             |                                         |  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP                    |                                                                       |                    | 3<br>2                      |                                         |  |  |  |  |

| Serial Communications<br>MSSP<br>UART                          |                                                                       |                    | 2<br>2                      |                                         |  |  |  |  |

| Input Change Notification Interrupt                            | 36                                                                    |                    |                             | 22                                      |  |  |  |  |

| 12-Bit Analog-to-Digital Module<br>(input channels)            | 22                                                                    |                    | 19                          |                                         |  |  |  |  |

| Analog Comparators                                             |                                                                       |                    | 3                           |                                         |  |  |  |  |

| 8-Bit Digital-to-Analog Converters                             |                                                                       |                    | 2                           |                                         |  |  |  |  |

| Operational Amplifiers                                         |                                                                       |                    | 2                           |                                         |  |  |  |  |

| Charge Time Measurement Unit (CTMU)                            | Yes                                                                   |                    |                             |                                         |  |  |  |  |

| Real-Time Clock and Calendar (RTCC)                            | Yes                                                                   |                    |                             |                                         |  |  |  |  |

| Configurable Logic Cell (CLC)                                  |                                                                       |                    | 2                           |                                         |  |  |  |  |

| Resets (and delays)                                            |                                                                       | on, Hardware Tra   |                             | , Illegal Opcode,<br>tion Word Mismatch |  |  |  |  |

| Instruction Set                                                | 76 Base Inst                                                          | ructions, Multiple | e Addressing N              | Iode Variations                         |  |  |  |  |

| Packages                                                       | 44-Pin QFI<br>48-Pin U                                                |                    | SPDIP/S                     | 28-Pin<br>SOP/SOIC/QFN                  |  |  |  |  |

#### TABLE 1-3: DEVICE FEATURES FOR THE PIC24FV16KM204 FAMILY

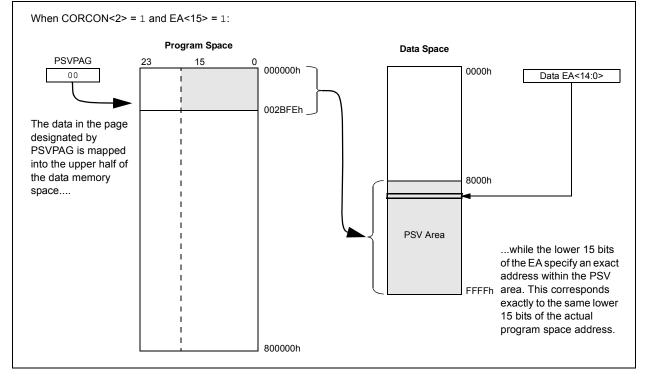

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of Data Space may optionally be mapped into a 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs if the MSb of the Data Space, EA, is '1' and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the Data Space is determined by the Program Space Visibility Page Address register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of Data Space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each Data Space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | Table Reads/Writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

#### FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| ; | Set up NVMCO  | N for row programming operation | ns  |                                       |

|---|---------------|---------------------------------|-----|---------------------------------------|

|   | MOV           | #0x4004, W0                     | ;   |                                       |

|   | MOV           | W0, NVMCON                      | ;   | Initialize NVMCON                     |

| ; | Set up a poir | nter to the first program memor | ry  | location to be written                |

| ; | program memo: | ry selected, and writes enabled | b   |                                       |

|   | MOV           | #0x0000, W0                     | ;   |                                       |

|   | MOV           | W0, TBLPAG                      | ;   | Initialize PM Page Boundary SFR       |

|   | MOV           | #0x1500, W0                     | ;   | An example program memory address     |

| ; | Perform the   | TBLWT instructions to write the | e . | latches                               |

| ; | 0th_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_0, W2                 | ;   |                                       |

|   | MOV           | <pre>#HIGH_BYTE_0, W3</pre>     | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | lst_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_1, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_1, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | 2nd_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_2, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_2, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

| ; | 32nd_program  | —                               |     |                                       |

|   |               | #LOW_WORD_31, W2                | ;   |                                       |

|   |               | #HIGH_BYTE_31, W3               | ;   |                                       |

|   |               | W2, [W0]                        |     | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0]                        | ;   | Write PM high byte into program latch |

| 1 |               |                                 |     |                                       |

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234 // Variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

// Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

// Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

// Write to address low word

__builtin_tblwtl(offset, progData[i++]);

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

## 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on data EEPROM, refer to the *"PIC24F Family Reference Manual"*, **"Data EEPROM"** (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFh. The size of the data EEPROM is 256 words in PIC24FXXXXX devices.

The data EEPROM is organized as 16-bit-wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

## 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

|                | rrupts For 5 instruc | ctions |

|----------------|----------------------|--------|

| asm volatile   | ("disi #5");         |        |

| //Issue Unlock | Sequence             |        |

| asm volatile   | ("mov #0x55, W0      | \n"    |

|                | "mov W0, NVMKEY      | \n"    |

|                | "mov #0xAA, W1       | \n"    |

|                | "mov W1, NVMKEY      | \n");  |

| // Perform Wri | te/Erase operations  |        |

| asm volatile   | ("bset NVMCON, #WR   | \n"    |

|                | "nop                 | \n"    |

|                | "nop                 | \n");  |

|                |                      |        |

### 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the Table Read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location, followed by a TBLRDL instruction.

A typical read sequence, using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and Table Read (builtin\_tblrd1) procedures from the C30 compiler library, is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

### EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

| <pre>intattribute ((space(eedata))) eeData = 0x1234;</pre> |                                       |

|------------------------------------------------------------|---------------------------------------|

| int data;                                                  | // Data read from EEPROM              |

| /*                                                         |                                       |

| The variable eeData must be a Global variable declared     | d outside of any method               |

| the code following this comment can be written inside      | the method that will execute the read |

| */                                                         |                                       |

| unsigned int offset;                                       |                                       |

| // Set up a pointer to the EEPROM location to be e         | erased                                |

| <pre>TBLPAG =builtin_tblpage(&amp;eeData);</pre>           | // Initialize EE Data page pointer    |

| offset =builtin_tbloffset(&eeData);                        | // Initizlize lower word of address   |

| <pre>data =builtin_tblrdl(offset);</pre>                   | // Write EEPROM data to write latch   |

|                                                            |                                       |

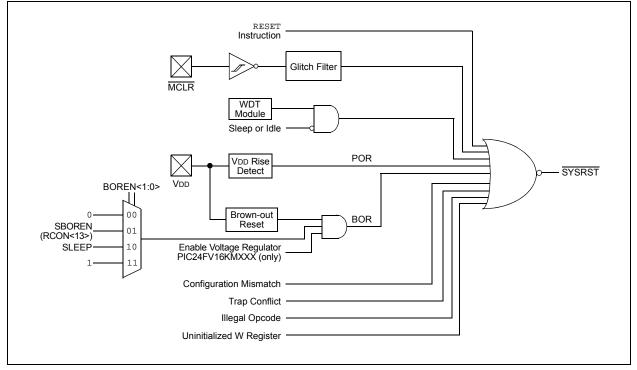

## 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "PIC24F Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- LPBOR: Low-Power BOR

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on Power-on Reset (POR) and unchanged by all other Resets.

Note: Refer to the specific peripheral or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A Power-on Reset will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

## FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

| R/W-0         | U-0                                                                                    | R/W-0                                  | R/W-0                     | R/W-0             | U-0              | U-0             | R/W-0  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------|----------------------------------------|---------------------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| NVMIE         |                                                                                        | AD1IE                                  | U1TXIE                    | U1RXIE            |                  | _               | CCT2IE |  |  |  |  |

| bit 15        | +                                                                                      |                                        |                           | •                 | •                |                 | bit    |  |  |  |  |

| R/W-0         | R/W-0                                                                                  | R/W-0                                  | U-0                       | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| CCT1IE        | CCP4IE                                                                                 | CCP3IE                                 | <u> </u>                  | T1IE              | CCP2IE           | CCP1IE          | INTOIE |  |  |  |  |

| bit 7         |                                                                                        |                                        |                           | 1.112             |                  |                 | bit    |  |  |  |  |

|               |                                                                                        |                                        |                           |                   |                  |                 |        |  |  |  |  |

| Legend:       |                                                                                        |                                        |                           |                   |                  |                 |        |  |  |  |  |

| R = Readabl   |                                                                                        | W = Writable                           |                           | •                 | nented bit, read |                 |        |  |  |  |  |

| -n = Value at | POR                                                                                    | '1' = Bit is set                       |                           | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |  |  |  |  |

| bit 15        | NVMIE: NVM                                                                             | Interrupt Enat                         | ole bit                   |                   |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt r                                                                        | equest is enab                         | oled                      |                   |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt r                                                                        | request is not e                       | enabled                   |                   |                  |                 |        |  |  |  |  |

| bit 14        | Unimplemen                                                                             | ted: Read as '                         | 0'                        |                   |                  |                 |        |  |  |  |  |

| bit 13        | AD1IE: A/D C                                                                           | Conversion Cor                         | nplete Interrup           | t Enable bit      |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enat                        |                           |                   |                  |                 |        |  |  |  |  |

|               | -                                                                                      | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 12        |                                                                                        |                                        | r Interrupt Ena           | ble bit           |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enab                        |                           |                   |                  |                 |        |  |  |  |  |

| L:1 44        | -                                                                                      | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 11        | <b>U1RXIE:</b> UART1 Receiver Interrupt Enable bit<br>1 = Interrupt request is enabled |                                        |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enaction of equest is not e |                           |                   |                  |                 |        |  |  |  |  |

| bit 10-9      | •                                                                                      | ted: Read as '                         |                           |                   |                  |                 |        |  |  |  |  |

| bit 8         | CCT2IE: Capture/Compare 2 Timer Interrupt Enable bit                                   |                                        |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enab                        |                           |                   |                  |                 |        |  |  |  |  |

| bit 7         | •                                                                                      | request is not e<br>ture/Compare       | nabled<br>1 Timer Interru | nt Enable bit     |                  |                 |        |  |  |  |  |

|               | •                                                                                      | request is enat                        |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 6         | CCP4IE: Cap                                                                            | ture/Compare                           | 4 Event Interru           | ipt Enable bit    |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt request is enabled                                                       |                                        |                           |                   |                  |                 |        |  |  |  |  |

|               | -                                                                                      | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 5         | CCP3IE: Cap                                                                            | ture/Compare                           | 3 Event Interru           | ipt Enable bit    |                  |                 |        |  |  |  |  |

|               |                                                                                        | equest is enab                         |                           |                   |                  |                 |        |  |  |  |  |

|               | -                                                                                      | equest is not e                        |                           |                   |                  |                 |        |  |  |  |  |

| bit 4         | -                                                                                      | ted: Read as '                         |                           |                   |                  |                 |        |  |  |  |  |

| bit 3         |                                                                                        | Interrupt Enab                         |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enat<br>request is not e    |                           |                   |                  |                 |        |  |  |  |  |

| bit 2         | -                                                                                      | -                                      | 2 Event Interru           | unt Enchlo hit    |                  |                 |        |  |  |  |  |

| DIL Z         | •                                                                                      | •                                      |                           | ipt Enable bit    |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enat<br>request is not e    |                           |                   |                  |                 |        |  |  |  |  |

| bit 1         | -                                                                                      | -                                      | 1 Event Interru           | ipt Enable bit    |                  |                 |        |  |  |  |  |

|               | -                                                                                      | equest is enab                         |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 0         | INT0IE: Exter                                                                          | nal Interrupt 0                        | Enable bit                |                   |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt r                                                                        | equest is enab                         | oled                      |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | equest is not e                        | mahlad                    |                   |                  |                 |        |  |  |  |  |

## REGISTER 8-12: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| U-0          | R/W-1                                                                                                                                   | R/W-0                                | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

| —            | CCT1IP2                                                                                                                                 | CCT1IP1                              | CCT1IP0          | —                 | CCP4IP2          | CCP4IP1         | CCP4IP0 |  |  |  |  |  |

| bit 15       |                                                                                                                                         |                                      |                  |                   |                  |                 | bit 8   |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                                   | R/W-0                                | R/W-0            | U-0               | U-0              | U-0             | U-0     |  |  |  |  |  |

|              | CCP3IP2                                                                                                                                 | CCP3IP1                              | CCP3IP0          |                   |                  |                 |         |  |  |  |  |  |

| bit 7        | 0010112                                                                                                                                 |                                      |                  |                   |                  |                 | bit 0   |  |  |  |  |  |

|              |                                                                                                                                         |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

| Legend:      |                                                                                                                                         |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

| R = Readab   | ole bit                                                                                                                                 | W = Writable                         | bit              | U = Unimplen      | nented bit, read | l as '0'        |         |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                                  | '1' = Bit is set                     |                  | '0' = Bit is cle  | ared             | x = Bit is unkn | iown    |  |  |  |  |  |

|              |                                                                                                                                         |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 15       | -                                                                                                                                       | ted: Read as '                       |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 14-12    | CCT1IP<2:0>                                                                                                                             | : Capture/Com                        | pare 1 Timer I   | nterrupt Priority | / bits           |                 |         |  |  |  |  |  |

|              | <pre>111 = Interrupt is Priority 7 (highest priority interrupt)</pre>                                                                   |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interru                                                                                                                           |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       | pt source is dis                     |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 11       | -                                                                                                                                       | ted: Read as '                       |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 10-8     | CCP4IP<2:0>: Capture/Compare 4 Event Interrupt Priority bits                                                                            |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                              |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interru                                                                                                                           |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | -                                                                                                                                       | pt source is dis                     |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 7        | -                                                                                                                                       | ted: Read as '                       |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 6-4      | <b>CCP3IP&lt;2:0&gt;:</b> Capture/Compare 3 Event Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 111 = Interru                                                                                                                           | pt is Priority 7 (                   | nignest priority | (interrupt)       |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interru                                                                                                                           | pt is Priority 1<br>pt source is dis | ablad            |                   |                  |                 |         |  |  |  |  |  |

| bit 3-0      | •                                                                                                                                       | ted: Read as '                       |                  |                   |                  |                 |         |  |  |  |  |  |

| DIL 3-0      | Unimplemen                                                                                                                              | ieu: Reau as                         | J                |                   |                  |                 |         |  |  |  |  |  |

### REGISTER 8-20: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| R/W-0         | U-0                                                              | R/W-0                                  | r-0            | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |  |  |  |

|---------------|------------------------------------------------------------------|----------------------------------------|----------------|--------------------------------------|------------------------|------------------------|------------------------|--|--|--|

| CCPON         |                                                                  | CCPSIDL                                | r              | TMRSYNC                              | CLKSEL2 <sup>(1)</sup> | CLKSEL1 <sup>(1)</sup> | CLKSEL0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                  |                                        |                |                                      | •                      | •                      | bit 8                  |  |  |  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |  |  |  |

| R/W-0         | R/W-0                                                            | R/W-0                                  | R/W-0          | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |  |  |  |

| TMRPS1        | TMRPS0                                                           | T32                                    | CCSEL          | MOD3                                 | MOD2                   | MOD1                   | MOD0                   |  |  |  |

| bit 7         |                                                                  |                                        |                |                                      |                        |                        | bit (                  |  |  |  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |  |  |  |

| Legend:       |                                                                  | r = Reserved I                         |                |                                      |                        |                        |                        |  |  |  |

| R = Readable  |                                                                  | W = Writable I                         | oit            |                                      | nented bit, read       |                        |                        |  |  |  |

| -n = Value at | POR                                                              | '1' = Bit is set                       |                | '0' = Bit is clea                    | ared                   | x = Bit is unkn        | own                    |  |  |  |

| bit 15        | CCPON: CCF                                                       | x Module Enat                          | ole bit        |                                      |                        |                        |                        |  |  |  |

|               | 1 = Module is<br>0 = Module is                                   |                                        | an operating r | node specified b                     | by the MOD<3:          | 0> control bits        |                        |  |  |  |

| bit 14        | Unimplemen                                                       | ted: Read as 'd                        | )'             |                                      |                        |                        |                        |  |  |  |

| bit 13        | CCPSIDL: CO                                                      | CPx Stop in Idle                       | Mode Bit       |                                      |                        |                        |                        |  |  |  |

|               |                                                                  | ues module op<br>s module opera        |                | device enters lo<br>ode              | lle mode               |                        |                        |  |  |  |

| bit 12        | Reserved: Ma                                                     |                                        |                |                                      |                        |                        |                        |  |  |  |

| bit 11        | TMRSYNC: Time Base Clock Synchronization bit                     |                                        |                |                                      |                        |                        |                        |  |  |  |

|               | (CLKSEL<br>0 = Synchron                                          | <b>&lt;2:0&gt;</b> ≠ 000)              |                | k is selected and<br>lock is selecte | -                      |                        | -                      |  |  |  |

| bit 10-8      | CLKSEL<2:0>: CCPx Time Base Clock Select bits <sup>(1)</sup>     |                                        |                |                                      |                        |                        |                        |  |  |  |

|               | 110 = Externa<br>101 = CLC1<br>100 = Reserv<br>011 = LPRC (      | 31 kHz source<br>dary Oscillator<br>ed | t              |                                      |                        |                        |                        |  |  |  |

| bit 7-6       | TMRPS<1:0>                                                       | : Time Base Pr                         | escale Select  | t bits                               |                        |                        |                        |  |  |  |

|               | 11 = 1:64 Pre<br>10 = 1:16 Pre<br>01 = 1:4 Pres<br>00 = 1:1 Pres | scaler<br>caler                        |                |                                      |                        |                        |                        |  |  |  |

| bit 5         | T32: 32-Bit Ti                                                   | me Base Selec                          | t bit          |                                      |                        |                        |                        |  |  |  |

|               |                                                                  |                                        |                | e edge output co<br>e edge output co |                        |                        |                        |  |  |  |

| bit 4         |                                                                  | ure/Compare N                          |                |                                      |                        |                        |                        |  |  |  |

|               | 1 = Input Cap                                                    | -                                      |                |                                      |                        |                        |                        |  |  |  |

### REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

| -                     |                                                                                                                                                      |                                       |                                                 |                                                                                      |                                    |                     | ,                   |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------|---------------------|---------------------|

| R/W-0                 | R/W-0                                                                                                                                                | U-0                                   | U-0                                             | R/W-0                                                                                | R/W-0                              | R/W-0               | R/W-0               |

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup>                                                                                                                                |                                       | —                                               | OPS3 <sup>(3)</sup>                                                                  | OPS2 <sup>(3)</sup>                | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |

| bit 15                |                                                                                                                                                      |                                       |                                                 |                                                                                      |                                    |                     | bit 8               |

|                       |                                                                                                                                                      |                                       |                                                 |                                                                                      |                                    |                     |                     |

| R/W-0                 | R/W-0                                                                                                                                                | R/W-0                                 | R/W-0                                           | R/W-0                                                                                | R/W-0                              | R/W-0               | R/W-0               |

| TRIGEN <sup>(4)</sup> | ONESHOT                                                                                                                                              | ALTSYNC                               | SYNC4                                           | SYNC3                                                                                | SYNC2                              | SYNC1               | SYNC0               |

| bit 7                 |                                                                                                                                                      |                                       |                                                 |                                                                                      |                                    |                     | bit 0               |

|                       |                                                                                                                                                      |                                       |                                                 |                                                                                      |                                    |                     |                     |

| Legend:               |                                                                                                                                                      |                                       |                                                 |                                                                                      |                                    |                     |                     |

| R = Readable          |                                                                                                                                                      | W = Writable I                        | oit                                             | -                                                                                    | nented bit, read                   | l as '0'            |                     |