Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

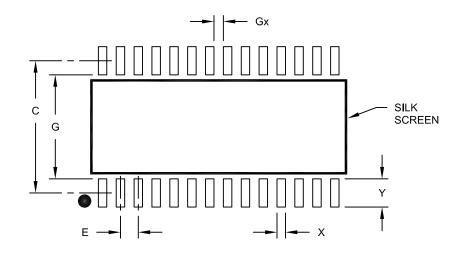

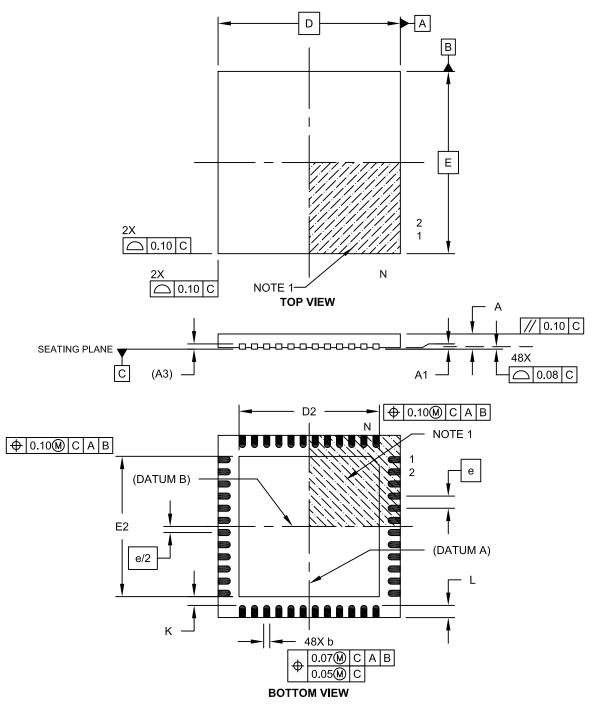

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km204-e-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-21: PORTA REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 <sup>(4,5)</sup> | Bit 10 <sup>(4,5)</sup> | Bit 9 <sup>(4,5)</sup> | Bit 8 <sup>(4,5)</sup> | Bit 7 <sup>(4)</sup> | Bit 6 <sup>(3)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|--------|--------|--------|--------|-------------------------|-------------------------|------------------------|------------------------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|---------------------|

| TRISA     | 2C0h  |        | _      | _      | _      | TRISA11                 | TRISA10                 | TRISA9                 | TRISA8                 | TRISA7               | TRISA6               | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 0FDF <sup>(1)</sup> |

| PORTA     | 2C2h  | -      | —      | —      |        | RA11                    | RA10                    | RA9                    | RA8                    | RA7                  | RA6                  | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx                |

| LATA      | 2C4h  | -      | —      | —      |        | LATA11                  | LATA10                  | LATA9                  | LATA8                  | LATA7                | LATA6                | _                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx                |

| ODCA      | 2C6h  | _      | _      | _      | _      | ODA11                   | ODA10                   | ODA9                   | ODA8                   | ODA7                 | ODA6                 | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are only available when MCLRE (FPOR<7>) = 0.

3: These bits are not implemented in FV devices.

4: These bits are not implemented in 20-pin devices.

5: These bits are not implemented in 28-pin devices.

### TABLE 4-22: PORTB REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7  | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|--------|----------------------|----------------------|--------|----------------------|--------|--------|--------|---------------------|

| TRISB     | 2C8h  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7 | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2 | TRISB1 | TRISB0 | <sub>FFFF</sub> (1) |

| PORTB     | 2CAh  | RB15    | RB14    | RB13    | RB12    | RB11                  | RB10                  | RB9    | RB8    | RB7    | RB6                  | RB5                  | RB4    | RB3                  | RB2    | RB1    | RB0    | xxxx                |

| LATB      | 2CCh  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11                | LATB10                | LATB9  | LATB8  | LATB7  | LATB6                | LATB5                | LATB4  | LATB3                | LATB2  | LATB1  | LATB0  | xxxx                |

| ODCB      | 2CEh  | ODB15   | ODB14   | ODB13   | ODB12   | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7   | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2   | ODB1   | ODB0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

### TABLE 4-23: PORTC REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 <sup>(2,3)</sup> | Bit 8 <sup>(2,3)</sup> | Bit 7 <sup>(2,3)</sup> | Bit 6 <sup>(2,3)</sup> | Bit 5 <sup>(2,3)</sup> | Bit 4 <sup>(2,3)</sup> | Bit 3 <sup>(2,3)</sup> | Bit 2 <sup>(2,3)</sup> | Bit 1 <sup>(2,3)</sup> | Bit 0 <sup>(2,3)</sup> | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------|

| TRISC        | 2D0h  | _      | _      |        | _      | —      | _      | TRISC9                 | TRISC8                 | TRISC7                 | TRISC6                 | TRISC5                 | TRISC4                 | TRISC3                 | TRISC2                 | TRISC1                 | TRISC0                 | 03FF <sup>(1)</sup> |

| PORTC        | 2D2h  | —      | _      | _      | -      | —      | _      | RC9                    | RC8                    | RC7                    | RC6                    | RC5                    | RC4                    | RC3                    | RC2                    | RC1                    | RC0                    | xxxx                |

| LATTC        | 2D4h  | —      | _      | _      | -      | —      | _      | LATC9                  | LATC8                  | LATC7                  | LATC6                  | LATC5                  | LATC4                  | LATC3                  | LATC2                  | LATC1                  | LATC0                  | xxxx                |

| ODCC         | 2D6h  | _      | _      | —      | -      | —      | _      | ODC9                   | ODC8                   | ODC7                   | ODC6                   | ODC5                   | ODC4                   | ODC3                   | ODC2                   | ODC1                   | ODC0                   | 0000                |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

**2:** These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

### TABLE 4-25: A/D REGISTER MAP

| File Name | -25:<br>Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11   | Bit 10       | Bit 9      | Bit 8                 | Bit 7                 | Bit 6                 | Bit 5               | Bit 4                  | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | All    |

|-----------|---------------|---------|---------|---------|---------|----------|--------------|------------|-----------------------|-----------------------|-----------------------|---------------------|------------------------|------------------------|---------|---------|---------|--------|

|           |               | 2.1.10  |         | 2       | 2.4.12  | 2        | 20.10        | 2          | 2                     |                       | 2                     | 2                   |                        | 2                      |         |         | 2.10    | Resets |

| ADC1BUF0  | 300h          |         |         |         |         | A/D Da   | ata Buffer 0 | /Threshold | for Channel 0/        | Threshold for         | Channel 0 & 1         | 2 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF1  | 302h          |         |         |         |         | A/D Da   | ata Buffer 1 | /Threshold | for Channel 1/        | Threshold for         | Channel 1 & 1         | 3 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF2  | 304h          |         |         |         |         | A/D Da   | ata Buffer 2 | /Threshold | for Channel 2/        | Threshold for         | Channel 2 & 1         | 4 in Window         | Compare                |                        |         |         |         | XXXX   |

| ADC1BUF3  | 306h          |         |         |         |         | A/D Da   | ata Buffer 3 | /Threshold | for Channel 3/        | Threshold for         | Channel 3 & 1         | 5 in Window         | Compare                |                        |         |         |         | XXXX   |

| ADC1BUF4  | 308h          |         |         |         |         | A/D Da   | ata Buffer 4 | /Threshold | for Channel 4/        | Threshold for         | Channel 4 & 1         | 6 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF5  | 30Ah          |         |         |         |         | A/D Da   | ata Buffer 5 | /Threshold | for Channel 5/        | Threshold for         | Channel 5 & 1         | 7 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF6  | 30Ch          |         |         |         |         | A/D Da   | ata Buffer 6 | /Threshold | for Channel 6/        | Threshold for         | Channel 6 & 1         | 8 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF7  | 30Eh          |         |         |         |         | A/D Da   | ata Buffer 7 | /Threshold | for Channel 7/        | Threshold for         | Channel 7 & 1         | 9 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF8  | 310h          |         |         |         |         | A/D Da   | ata Buffer 8 | /Threshold | for Channel 8/        | Threshold for         | Channel 8 & 2         | 0 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF9  | 312h          |         |         |         |         | A/D Da   | ata Buffer 9 | /Threshold | for Channel 9/        | Threshold for         | Channel 9 & 2         | 1 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF10 | 314h          |         |         |         |         | A/D Data | a Buffer 10/ | Threshold  | for Channel 10        | /Threshold for        | r Channel 10 &        | 22 in Window        | w Compare              |                        |         |         |         | xxxx   |

| ADC1BUF11 | 316h          |         |         |         |         | A/D Dat  | a Buffer 11/ | Threshold  | for Channel 11        | /Threshold for        | Channel 11 &          | 23 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF12 | 318h          |         |         |         |         | A/D Dat  | a Buffer 12  | /Threshold | for Channel 12        | 2/Threshold fo        | r Channel 0 &         | 12 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF13 | 31Ah          |         |         |         |         | A/D Dat  | a Buffer 13  | /Threshold | for Channel 13        | 3/Threshold fo        | r Channel 1 &         | 13 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF14 | 31Ch          |         |         |         |         | A/D Dat  | a Buffer 14  | /Threshold | for Channel 14        | 4/Threshold fo        | r Channel 2 &         | 14 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF15 | 31Eh          |         |         |         |         | A/D Dat  | a Buffer 15  | /Threshold | for Channel 1         | 5/Threshold fo        | r Channel 3 &         | 15 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF16 | 320h          |         |         |         |         | A/D Dat  | a Buffer 16  | /Threshold | for Channel 1         | 6/Threshold fo        | r Channel 4 &         | 16 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF17 | 322h          |         |         |         |         | A/D Dat  | a Buffer 17  | /Threshold | for Channel 1         | 7/Threshold fo        | r Channel 5 &         | 17 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF18 | 324h          |         |         |         |         | A/D Dat  | a Buffer 18  | /Threshold | for Channel 18        | 8/Threshold fo        | r Channel 6 &         | 18 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF19 | 326h          |         |         |         |         | A/D Dat  | a Buffer 19  | /Threshold | for Channel 19        | 9/Threshold fo        | r Channel 7 &         | 19 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF20 | 328h          |         |         |         |         | A/D Dat  | a Buffer 20  | /Threshold | for Channel 20        | 0/Threshold fo        | r Channel 8 &         | 20 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF21 | 32Ah          |         |         |         |         | A/D Dat  | a Buffer 21  | /Threshold | for Channel 2         | 1/Threshold fo        | r Channel 9 &         | 21 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF22 | 32Ch          |         |         |         |         | A/D Data | a Buffer 22/ | Threshold  | for Channel 22        | 2/Threshold for       | r Channel 10 &        | 22 in Window        | w Compare              |                        |         |         |         | xxxx   |

| ADC1BUF23 | 32Eh          |         |         |         |         | A/D Data | a Buffer 23/ | Threshold  | for Channel 23        | 3/Threshold for       | r Channel 11 &        | 23 in Window        | w Compare              |                        |         |         |         | xxxx   |

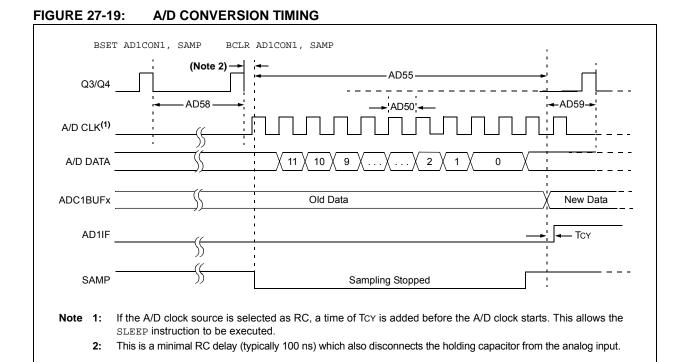

| AD1CON1   | 340h          | ADON    | _       | ADSIDL  | _       | _        | MODE12       | FORM1      | FORM0                 | SSRC3                 | SSRC2                 | SSRC1               | SSRC0                  | _                      | ASAM    | SAMP    | DONE    | 0000   |

| AD1CON2   | 342h          | PVCFG1  | PVCFG0  | NVCFG0  | _       | BUFREGEN | CSCNA        | _          | _                     | BUFS                  | SMPI4                 | SMPI3               | SMPI2                  | SMPI1                  | SMPI0   | BUFM    | ALTS    | 0000   |

| AD1CON3   | 344h          | ADRC    | EXTSAM  |         | SAMC4   | SAMC3    | SAMC2        | SAMC1      | SAMC0                 | ADCS7                 | ADCS6                 | ADCS5               | ADCS4                  | ADCS3                  | ADCS2   | ADCS1   | ADCS0   | 0000   |

| AD1CHS    | 348h          | CH0NB2  | CH0NB1  | CH0NB0  | CH0SB4  | CH0SB3   | CH0SB2       | CH0SB1     | CH0SB0                | CH0NA2                | CH0NA1                | CH0NA0              | CH0SA4                 | CH0SA3                 | CH0SA2  | CH0SA1  | CH0SA0  | 0000   |

| AD1CSSH   | 34Eh          | _       | CSS30   | CSS29   | CSS28   | CSS27    | CSS26        | _          | _                     | CSS23                 | CSS22                 | CSS21               | CSS20 <sup>(1)</sup>   | CSS19 <sup>(1)</sup>   | CSS18   | CSS17   | CSS16   | 0000   |

| AD1CSSL   | 350h          | CSS15   | CSS14   | CSS13   | CSS12   | CSS11    | CSS10        | CSS9       | CSS8 <sup>(1,2)</sup> | CSS7 <sup>(1,2)</sup> | CSS6 <sup>(1,2)</sup> | CSS5 <sup>(1)</sup> | CSS4                   | CSS3                   | CSS2    | CSS1    | CSS0    | 0000   |

| AD1CON5   | 354h          | ASEN    | LPEN    | CTMREQ  | BGREQ   | r        | _            | ASINT1     | ASINT0                | _                     | _                     | —                   | _                      | WM1                    | WM0     | CM1     | CM0     | 0000   |

| AD1CHITH  | 356h          | _       | —       | —       | —       | _        | _            | —          | —                     | CHH23                 | CHH22                 | CHH21               | CHH20 <sup>(1)</sup>   | CHH19 <sup>(1)</sup>   | CHH18   | CHH17   | CHH16   | 0000   |

| AD1CHITL  | 358h          | CHH15   | CHH14   | CHH13   | CHH12   | CHH11    | CHH10        | CHH9       | CHH8 <sup>(1,2)</sup> | CHH7 <sup>(1,2)</sup> | CHH6 <sup>(1,2)</sup> | CHH5 <sup>(1)</sup> | CHH4                   | CHH3                   | CHH2    | CHH1    | CHH0    | 0000   |

| AD1CTMENH | 360h          | _       | —       | —       | _       | _        | _            | —          | —                     | CTMEN23               | CTMEN22               | CTMEN21             | CTMEN20 <sup>(1)</sup> | CTMEN19 <sup>(1)</sup> | CTMEN18 | CTMEN17 | CTMEN16 | 0000   |

| AD1CTMENL | 362h          | CTMEN15 | CTMEN14 | CTMEN13 | CTMEN12 | CTMEN11  | CTMEN10      | CTMEN9     | CTMEN8((1,2)          | CTMEN7(1,2)           | CTMEN6(1,2)           | CTMEN5(1)           | CTMEN4                 | CTMEN3                 | CTMEN2  | CTMEN1  | CTMEN0  | 0000   |

$\label{eq:Legend: Legend: Legend: u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.$

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as displayed in Example 5-5.

| EXAMPLE 5-1: | ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE |

|--------------|-------------------------------------------------------|

|              |                                                       |

| ; Set up NVMCON fo | or row erase operation               |                                     |

|--------------------|--------------------------------------|-------------------------------------|

| MOV #0x            | x4058, WO ;                          |                                     |

| MOV W0,            | , NVMCON ;                           | Initialize NVMCON                   |

| ; Init pointer to  | row to be ERASED                     |                                     |

| MOV #tk            | <pre>blpage(PROG_ADDR), W0 ;</pre>   |                                     |

| MOV W0,            | , TBLPAG ;                           | Initialize PM Page Boundary SFR     |

| MOV #tk            | <pre>bloffset(PROG_ADDR), W0 ;</pre> | Initialize in-page EA[15:0] pointer |

| TBLWTL W0,         | , [WO] ;                             | Set base address of erase block     |

| DISI #5            | ;                                    | Block all interrupts                |

|                    |                                      | for next 5 instructions             |

| MOV #0×            | x55, WO                              |                                     |

| MOV W0,            | , NVMKEY ;                           | Write the 55 key                    |

| MOV #0×            | xAA, W1 ;                            |                                     |

| MOV W1,            | , NVMKEY ;                           | Write the AA key                    |

| BSET NVM           | MCON, #WR ;                          | Start the erase sequence            |

| NOP                | ;                                    | Insert two NOPs after the erase     |

| NOP                | ;                                    | command is asserted                 |

|                    |                                      |                                     |

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

// Variable located in Pgm Memory, declared as a

int __attribute__ ((space(auto_psv))) progAddr = 0x1234;

// global variable

unsigned int offset;

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

__builtin_tblwtl(offset, 0x0000);

// Set base address of erase block

// with dummy latch write

NVMCON = 0 \times 4058;

// Initialize NVMCON

asm("DISI #5");

// Block all interrupts for next 5 instructions

_builtin_write_NVM();

\ensuremath{{//}} C30 function to perform unlock

// sequence and set WR

```

### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC          |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| —      | —   | —   | —   | —   | —   |     | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0, HSC            | R/W-0, HSC            | R/W-0, HSC            | R-0, HSC          | R/W-0, HSC       | R/W-0, HSC        | R/W-0, HSC       | R/W-0, HSC       |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           | HSC = Hardware Settable/0 | Clearable bit                      |                    |  |  |  |  |

|-------------------|---------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 15-9 Unimplemented: Read as '0'

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

|         |                                                                            |

Note 1: See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

- 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- 3: The IPLx Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

| R/W-0         | U-0             | R/W-0                               | R/W-0                     | R/W-0             | U-0              | U-0             | R/W-0  |

|---------------|-----------------|-------------------------------------|---------------------------|-------------------|------------------|-----------------|--------|

| NVMIE         |                 | AD1IE                               | U1TXIE                    | U1RXIE            |                  | _               | CCT2IE |

| bit 15        | +               |                                     |                           | •                 | •                |                 | bit    |

| R/W-0         | R/W-0           | R/W-0                               | U-0                       | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| CCT1IE        | CCP4IE          | CCP3IE                              | <u> </u>                  | T1IE              | CCP2IE           | CCP1IE          | INTOIE |

| bit 7         |                 |                                     |                           | 1.112             |                  |                 | bit    |

|               |                 |                                     |                           |                   |                  |                 |        |

| Legend:       |                 |                                     |                           |                   |                  |                 |        |

| R = Readabl   |                 | W = Writable                        |                           | •                 | nented bit, read |                 |        |

| -n = Value at | POR             | '1' = Bit is set                    |                           | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |

| bit 15        | NVMIE: NVM      | Interrupt Enat                      | ole bit                   |                   |                  |                 |        |

|               | 1 = Interrupt r | equest is enab                      | oled                      |                   |                  |                 |        |

|               | 0 = Interrupt r | request is not e                    | enabled                   |                   |                  |                 |        |

| bit 14        | Unimplemen      | ted: Read as '                      | 0'                        |                   |                  |                 |        |

| bit 13        | AD1IE: A/D C    | Conversion Cor                      | nplete Interrup           | t Enable bit      |                  |                 |        |

|               |                 | request is enat                     |                           |                   |                  |                 |        |

|               | -               | request is not e                    |                           |                   |                  |                 |        |

| bit 12        |                 |                                     | r Interrupt Ena           | ble bit           |                  |                 |        |

|               |                 | request is enab                     |                           |                   |                  |                 |        |

| L:1 44        | -               | request is not e                    |                           |                   |                  |                 |        |

| bit 11        |                 |                                     | nterrupt Enable           | e dit             |                  |                 |        |

|               |                 | request is enat<br>request is not e |                           |                   |                  |                 |        |

| bit 10-9      | •               | ted: Read as '                      |                           |                   |                  |                 |        |

| bit 8         | CCT2IE: Cap     | ture/Compare                        | 2 Timer Interru           | pt Enable bit     |                  |                 |        |

|               |                 | request is enab                     |                           |                   |                  |                 |        |

| bit 7         | •               | request is not e<br>ture/Compare    | nabled<br>1 Timer Interru | nt Enable bit     |                  |                 |        |

|               | •               | request is enat                     |                           |                   |                  |                 |        |

|               |                 | request is not e                    |                           |                   |                  |                 |        |

| bit 6         | CCP4IE: Cap     | ture/Compare                        | 4 Event Interru           | ipt Enable bit    |                  |                 |        |

|               |                 | equest is enab                      |                           |                   |                  |                 |        |

|               | -               | request is not e                    |                           |                   |                  |                 |        |

| bit 5         | CCP3IE: Cap     | ture/Compare                        | 3 Event Interru           | ipt Enable bit    |                  |                 |        |

|               |                 | equest is enab                      |                           |                   |                  |                 |        |

|               | -               | equest is not e                     |                           |                   |                  |                 |        |

| bit 4         | -               | ted: Read as '                      |                           |                   |                  |                 |        |

| bit 3         |                 | Interrupt Enab                      |                           |                   |                  |                 |        |

|               |                 | request is enat<br>request is not e |                           |                   |                  |                 |        |

| bit 2         | -               | -                                   | 2 Event Interru           | unt Enchlo hit    |                  |                 |        |

| DIL Z         | •               | •                                   |                           | ipt Enable bit    |                  |                 |        |

|               |                 | request is enat<br>request is not e |                           |                   |                  |                 |        |

| bit 1         | -               | -                                   | 1 Event Interru           | ipt Enable bit    |                  |                 |        |

|               | -               | equest is enab                      |                           |                   |                  |                 |        |

|               |                 | equest is not e                     |                           |                   |                  |                 |        |

| bit 0         | INT0IE: Exter   | nal Interrupt 0                     | Enable bit                |                   |                  |                 |        |

|               | 1 = Interrupt r | equest is enab                      | oled                      |                   |                  |                 |        |

|               |                 | equest is not e                     | mahlad                    |                   |                  |                 |        |

### REGISTER 8-12: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| U-0                                | U-0           | U-0                  | U-0              | U-0               | R/W-1            | R/W-0           | R/W-0   |

|------------------------------------|---------------|----------------------|------------------|-------------------|------------------|-----------------|---------|

| —                                  | —             | —                    | _                | —                 | CCP5IP2          | CCP5IP1         | CCP5IP0 |

| bit 15                             |               |                      |                  |                   |                  | -<br>-          | bit 8   |

|                                    |               |                      |                  |                   |                  |                 |         |

| U-0                                | U-0           | U-0                  | U-0              | U-0               | R/W-1            | R/W-0           | R/W-0   |

| _                                  | —             | —                    |                  | —                 | INT1IP2          | INT1IP1         | INT1IP0 |

| bit 7                              |               |                      |                  |                   |                  |                 | bit 0   |

| Legend:                            |               |                      |                  |                   |                  |                 |         |

| R = Readat                         | ole hit       | W = Writable b       | hit              | II = Unimpler     | nented bit, read | 1 as '0'        |         |

| -n = Value at POR '1' = Bit is set |               |                      |                  | '0' = Bit is cle  |                  | x = Bit is unkr | own     |

|                                    |               |                      |                  |                   |                  |                 |         |

| bit 15-11                          | Unimplemer    | nted: Read as '0     | '                |                   |                  |                 |         |

| bit 10-8                           | CCP5IP<2:0    | >: Capture/Com       | pare 5 Event     | Interrupt Priorit | y bits           |                 |         |

|                                    | 111 = Interru | ipt is Priority 7 (ł | nighest priority | y interrupt)      |                  |                 |         |

|                                    | •             |                      |                  |                   |                  |                 |         |

|                                    | •             |                      |                  |                   |                  |                 |         |

|                                    |               | pt is Priority 1     |                  |                   |                  |                 |         |

|                                    |               | pt source is disa    |                  |                   |                  |                 |         |

| bit 7-3                            | Unimplemer    | nted: Read as '0     | '                |                   |                  |                 |         |

| bit 2-0                            |               | : External Interru   |                  |                   |                  |                 |         |

|                                    | 111 = Interru | ipt is Priority 7 (h | nighest priority | y interrupt)      |                  |                 |         |

|                                    | •             |                      |                  |                   |                  |                 |         |

|                                    | •             |                      |                  |                   |                  |                 |         |

|                                    |               | pt is Priority 1     | - la la al       |                   |                  |                 |         |

|                                    | 000 = interru | pt source is disa    | adied            |                   |                  |                 |         |

### REGISTER 8-24: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

### REGISTER 8-27: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | CCT5IP2 | CCT5IP1 | CCT5IP0 |     | _   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

| Legend:                               |            |                                 |                              |                    |

|---------------------------------------|------------|---------------------------------|------------------------------|--------------------|

| R = Readable bit<br>-n = Value at POR |            | W = Writable bit                | U = Unimplemented bit        | , read as '0'      |

|                                       |            | '1' = Bit is set                | '0' = Bit is cleared         | x = Bit is unknown |

|                                       |            |                                 |                              |                    |

| bit 15-7                              | Unimpler   | mented: Read as '0'             |                              |                    |

| bit 6-4                               | CCT5IP<    | 2:0>: Capture/Compare 5 Ti      | imer Interrupt Priority bits |                    |

|                                       | 111 = Inte | errupt is Priority 7 (highest p | riority interrupt)           |                    |

|                                       | •          |                                 |                              |                    |

|                                       | •          |                                 |                              |                    |

|                                       | •          |                                 |                              |                    |

|                                       | 001 = Inte | errupt is Priority 1            |                              |                    |

- 000 = Interrupt source is disabled

- bit 3-0 Unimplemented: Read as '0'

### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC Oscillator by a fixed amount.

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                    | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit                    |                                                |               |  |  |

|----------------------------|----------------------------------------------------------|------------------------------------------------|---------------|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit                                  | CO = Clearable Only bit SO = Settable Only bit |               |  |  |

| R = Readable bit           | W = Writable bit                                         | U = Unimplemented bit                          | , read as '0' |  |  |

| -n = Value at POR          | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                |               |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| Note 1:   | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:        | This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                |

**3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

| U-0             | U-0                | U-0                 | U-0                       | U-0                 | U-0                 | U-0                 | U-0                 |

|-----------------|--------------------|---------------------|---------------------------|---------------------|---------------------|---------------------|---------------------|

|                 | —                  | —                   | —                         | —                   | —                   | —                   | —                   |

| bit 15          |                    |                     |                           |                     |                     |                     | bit 8               |

|                 |                    |                     |                           |                     |                     |                     |                     |

| U-0             | U-0                | R/W-0               | R/W-0                     | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

| —               | —                  | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>       | TUN3 <sup>(1)</sup> | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| bit 7           |                    |                     |                           |                     |                     |                     | bit 0               |

|                 |                    |                     |                           |                     |                     |                     |                     |

| Legend:         |                    |                     |                           |                     |                     |                     |                     |

| R = Readable    | bit                | W = Writable        | bit                       | U = Unimplem        | nented bit, read    | l as '0'            |                     |

| -n = Value at I | POR                | '1' = Bit is set    |                           | '0' = Bit is clea   | ared                | x = Bit is unkn     | nown                |

|                 |                    |                     |                           |                     |                     |                     |                     |

| bit 15-6        | Unimplement        | ted: Read as 'd     | )'                        |                     |                     |                     |                     |

| bit 5-0         | TUN<5:0>: FI       | RC Oscillator T     | uning bits <sup>(1)</sup> |                     |                     |                     |                     |

|                 |                    | ximum frequen       | cy deviation              |                     |                     |                     |                     |

|                 | 011110             |                     |                           |                     |                     |                     |                     |

|                 | •                  |                     |                           |                     |                     |                     |                     |

|                 | •                  |                     |                           |                     |                     |                     |                     |

|                 | 000001             |                     |                           |                     |                     |                     |                     |

|                 | 000000 <b>= Ce</b> | nter frequency,     | oscillator is ru          | nning at factory    | calibrated free     | quency              |                     |

|                 | 111111             |                     |                           |                     |                     |                     |                     |

|                 | •                  |                     |                           |                     |                     |                     |                     |

|                 | •                  |                     |                           |                     |                     |                     |                     |

|                 | 100001             |                     |                           |                     |                     |                     |                     |

|                 |                    | nimum frequen       | cv deviation              |                     |                     |                     |                     |

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

### 13.1 Time Base Generator

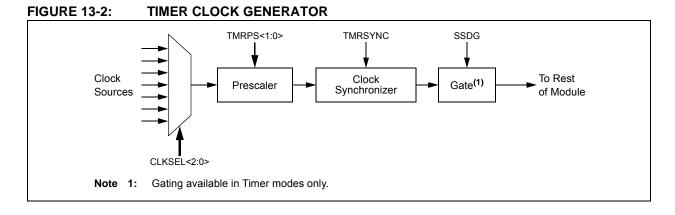

The Timer Clock Generator (TCG) generates a clock for the module's internal time base, using one of the clock signals already available on the microcontroller. This is used as the time reference for the module in its three major modes. The internal time base is shown in Figure 13-2.

There are eight inputs available to the clock generator, which are selected using the CLKSEL<2:0> bits (CCPxCON1L<10:8>). Available sources include the FRC and LPRC, the Secondary Oscillator, and the TCLKI External Clock inputs. The system clock is the default source (CLKSEL<2:0> = 000). On PIC24FV16KM204 family devices, clock sources to the MCCPx module must be synchronized with the system clock; as a result, when clock sources are selected, clock input timing restrictions or module operating restrictions may exist. Table 13-1 describes which time base sources are valid for the various operating modes.

### TABLE 13-1: VALID TIMER OPTIONS FOR MCCPx/SCCPx MODES

| CLKSEL               | Tir                                      | ner | Input   | Output  |

|----------------------|------------------------------------------|-----|---------|---------|

| <2:0> <sup>(1)</sup> | Sync <sup>(2)</sup> Async <sup>(3)</sup> |     | Capture | Compare |

| 111                  | Х                                        | _   | _       | _       |

| 110                  | Х                                        |     |         | —       |

| 101                  | Х                                        | _   | -       | —       |

| 011                  | Х                                        | _   | -       | —       |

| 010                  | Х                                        |     |         | —       |

| 001                  | Х                                        | _   | —       | _       |

| <sub>000</sub> (4)   | —                                        | Х   | Х       | Х       |

**Note 1:** See Register 13-1 for the description of the time base sources.

- 2: Synchronous Operation: TMRSYNC (CCPxCON1L<11>) = 1 and TRIGEN (CCPxCON1H<7>) = 0.

- Asynchronous Operation: (TMRSYNC = 0) or Triggered mode (TRIGEN = 1).

- 4: When CLKSEL<2:0> = 000, the TMRSYNC bit must be cleared.

DS30003030B-page 144

### 13.4 Input Capture Mode

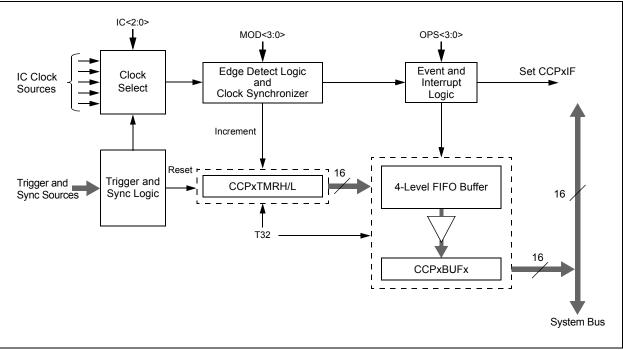

Input Capture mode is used to capture a timer value from an independent timer base upon an event on an input pin or other internal Trigger source. The input capture features are useful in applications requiring frequency (time period) and pulse measurement. Figure 13-6 depicts a simplified block diagram of Input Capture mode. Input Capture mode uses a dedicated 16/32-bit, synchronous, up counting timer for the capture function. The timer value is written to the FIFO when a capture event occurs. The internal value may be read (with a synchronization delay) using the CCPxTMRH/L register.

To use Input Capture mode, the CCSEL bit (CCPxCON1L<4>) must be set. The T32 and the MOD<3:0> bits are used to select the proper Capture mode, as shown in Table 13-4.

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                     |  |  |  |

|------------------------------|-----------------------|------------------------------------|--|--|--|

| 0000                         | 0                     | Edge Detect (16-bit capture)       |  |  |  |

| 0000                         | 1                     | Edge Detect (32-bit capture)       |  |  |  |

| 0001                         | 0                     | Every Rising (16-bit capture)      |  |  |  |

| 0001                         | 1                     | Every Rising (32-bit capture)      |  |  |  |

| 0010                         | 0                     | Every Falling (16-bit capture)     |  |  |  |

| 0010                         | 1                     | Every Falling (32-bit capture)     |  |  |  |

| 0011                         | 0                     | Every Rise/Fall (16-bit capture)   |  |  |  |

| 0011                         | 1                     | Every Rise/Fall (32-bit capture)   |  |  |  |

| 0100                         | 0                     | Every 4th Rising (16-bit capture)  |  |  |  |

| 0100                         | 1                     | Every 4th Rising (32-bit capture)  |  |  |  |

| 0101                         | 0                     | Every 16th Rising (16-bit capture) |  |  |  |

| 0101                         | 1                     | Every 16th Rising (32-bit capture) |  |  |  |

### TABLE 13-4: INPUT CAPTURE MODES

| R/W-0         | U-0                                                                                              | R/W-0                                                         | R/W-0                            | R/W-0                             | R/W-0                | R/W-0                                                  | R/W-0    |

|---------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|-----------------------------------|----------------------|--------------------------------------------------------|----------|

| OENSYNC       |                                                                                                  | OCFEN <sup>(1)</sup>                                          | OCEEN <sup>(1)</sup>             | OCDEN <sup>(1)</sup>              | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup>                                   | OCAEN    |

| bit 15        |                                                                                                  |                                                               |                                  |                                   |                      |                                                        | bit      |

| R/W-0         | R/W-0                                                                                            | U-0                                                           | R/W-0                            | R/W-0                             | R/W-0                | R/W-0                                                  | R/W-0    |

| ICGSM1        | ICGSM0                                                                                           | _                                                             | AUXOUT1                          | AUXOUT0                           | ICS2                 | ICS1                                                   | ICS0     |

| bit 7         |                                                                                                  |                                                               |                                  |                                   |                      | 1                                                      | bit      |

| Legend:       |                                                                                                  |                                                               |                                  |                                   |                      |                                                        |          |

| R = Readable  | e bit                                                                                            | W = Writable                                                  | bit                              | U = Unimplem                      | nented bit, read     | 1 as '0'                                               |          |

| -n = Value at | POR                                                                                              | '1' = Bit is set                                              |                                  | '0' = Bit is clea                 | ared                 | x = Bit is unkn                                        | own      |

| bit 15        | 1 = Update b                                                                                     | Dutput Enable S<br>by output enable<br>by output enable       | e bits occurs or                 | n the next Time                   | Base Reset or        | rollover                                               |          |

| bit 14        | Unimplemen                                                                                       | ted: Read as '                                                | )'                               |                                   |                      |                                                        |          |

| bit 13-8      | 1 = OCx pin<br>0 = OCx pin                                                                       |                                                               | the CCPx moded by the CCP        | dule and produc                   |                      | compare or PWI<br>e to the port log                    |          |

| bit 7-6       | ICGSM<1:0>                                                                                       | : Input Capture                                               | Gating Source                    | Mode Control                      | bits                 |                                                        |          |

|               | 01 = One-Sh<br>00 = Level-Se                                                                     | ot mode: Falling<br>ot mode: Rising                           | edge from gat<br>A high level fr | ting source ena<br>om gating sour | bles future cap      | pture events (IC<br>oture events (IC<br>future capture | DIS = 0) |

| bit 5         | Unimplemen                                                                                       | ted: Read as '                                                | )'                               |                                   |                      |                                                        |          |

| bit 4-3       | AUXOUT<1:0                                                                                       | <b>0&gt;:</b> Auxiliary Oເ                                    | tput Signal on                   | Event Selectio                    | n bits               |                                                        |          |

|               | 10 = Signal c                                                                                    | pture or output<br>output is defined<br>ise rollover eve<br>d | l by module op                   |                                   |                      | )                                                      |          |

| bit 2-0       | 111 = Unuse<br>110 = CLC2<br>101 = CLC1<br>100 = Unuse<br>011 = Comp<br>010 = Comp<br>001 = Comp | output<br>output                                              |                                  | 3                                 |                      |                                                        |          |

### REGISTER 13-4: CCPxCON2H: CCPx CONTROL 2 HIGH REGISTERS

### **Note 1:** OCFEN through OCBEN (bits<13:9>) are implemented in MCCPx modules only.

### REGISTER 14-3: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     |     | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:   |                   |                                                                                                                                                                                |                                                                                    |                                                 |  |  |  |  |  |

|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|--|

| R = Read  | lable bit         | W = Writable bit                                                                                                                                                               | U = Unimplemented bit                                                              | , read as '0'                                   |  |  |  |  |  |

| -n = Valu | e at POR          | '1' = Bit is set                                                                                                                                                               | '0' = Bit is cleared                                                               | x = Bit is unknown                              |  |  |  |  |  |

|           |                   |                                                                                                                                                                                |                                                                                    |                                                 |  |  |  |  |  |

| bit 15-8  | Unimple           | mented: Read as '0'                                                                                                                                                            |                                                                                    |                                                 |  |  |  |  |  |

| bit 7     | WCOL: \           | Nrite Collision Detect bit                                                                                                                                                     |                                                                                    |                                                 |  |  |  |  |  |

|           |                   | C C                                                                                                                                                                            | while it is still transmitting the                                                 | previous word (must be cleared in               |  |  |  |  |  |

|           | softw<br>0 = No c | ,                                                                                                                                                                              |                                                                                    |                                                 |  |  |  |  |  |

| bit 6     |                   |                                                                                                                                                                                | Port Receive Overflow Indicate                                                     | or hit(1)                                       |  |  |  |  |  |

| Sit 0     |                   |                                                                                                                                                                                |                                                                                    |                                                 |  |  |  |  |  |

|           |                   | <u>SPI Slave mode:</u><br>1 = A new byte is received while the SSPxBUF register is still holding the previous data. In case of over-                                           |                                                                                    |                                                 |  |  |  |  |  |

|           |                   | flow, the data in SSPxSR is lost. Overflow can only occur in Slave mode. The user must read the                                                                                |                                                                                    |                                                 |  |  |  |  |  |

|           | 0 = No c          |                                                                                                                                                                                | g data, to avoid setting overflo                                                   | w (must be cleared in software).                |  |  |  |  |  |

| bit 5     |                   |                                                                                                                                                                                | Port Enable bit(2)                                                                 |                                                 |  |  |  |  |  |

| DIL 5     |                   | <b>SSPEN:</b> Master Synchronous Serial Port Enable bit <sup>(2)</sup><br>1 = Enables the serial port and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins |                                                                                    |                                                 |  |  |  |  |  |

|           |                   |                                                                                                                                                                                | jures these pins as I/O port pi                                                    | · ·                                             |  |  |  |  |  |

| bit 4     | CKP: Clo          | ock Polarity Select bit                                                                                                                                                        |                                                                                    |                                                 |  |  |  |  |  |

|           | 1 = Idle s        | state for clock is a high level                                                                                                                                                |                                                                                    |                                                 |  |  |  |  |  |

|           |                   | state for clock is a low level                                                                                                                                                 |                                                                                    |                                                 |  |  |  |  |  |

| bit 3-0   | SSPM<3            | :0>: Master Synchronous Se                                                                                                                                                     | rial Port Mode Select bits <sup>(3)</sup>                                          |                                                 |  |  |  |  |  |

|           |                   | SPI Master mode, Clock = Fo                                                                                                                                                    |                                                                                    | $\frac{1}{2}$                                   |  |  |  |  |  |

|           |                   |                                                                                                                                                                                | x pin; <u>SSx</u> pin control is disable<br>(x pin; <u>SSx</u> pin control is enab | led, $\overline{SSx}$ can be used as an I/O pin |  |  |  |  |  |

|           |                   | SPI Master mode, Clock = TM                                                                                                                                                    |                                                                                    |                                                 |  |  |  |  |  |

|           |                   | SPI Master mode, Clock = Fo                                                                                                                                                    |                                                                                    |                                                 |  |  |  |  |  |

|           |                   | 0001 = SPI Master mode, Clock = Fosc/8                                                                                                                                         |                                                                                    |                                                 |  |  |  |  |  |

|           | 0000 = 5          | SPI Master mode, Clock = Fo                                                                                                                                                    | SC/Z                                                                               |                                                 |  |  |  |  |  |