Welcome to E-XFL.COM

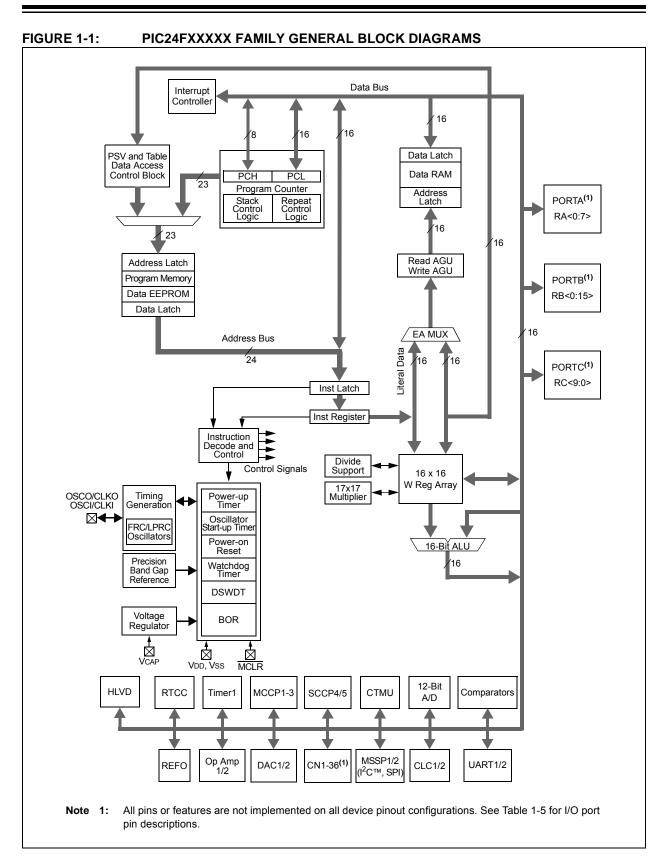

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 48-UQFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km204-e-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

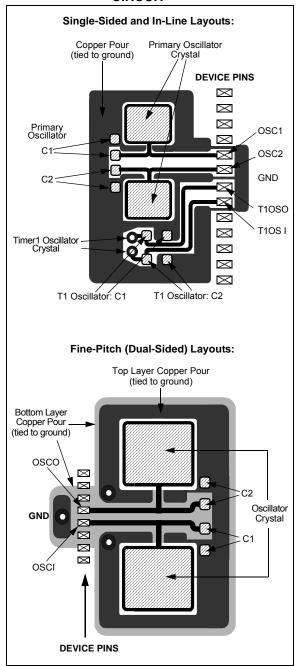

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to for **Section 9.0 "Oscillator Configuration**" details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals, in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

## FIGURE 2-5: SU

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

|              |               |                            | -                          |                   |                  |                 |         |

|--------------|---------------|----------------------------|----------------------------|-------------------|------------------|-----------------|---------|

| U-0          | U-0           | U-0                        | U-0                        | U-0               | R/W-1            | R/W-0           | R/W-0   |

| _            | _             | _                          | _                          | _                 | BCL2IP2          | BCL2IP1         | BCL2IP0 |

| oit 15       |               | ·                          |                            |                   |                  |                 | bit 8   |

|              |               |                            |                            |                   |                  |                 |         |

| U-0          | R/W-1         | R/W-0                      | R/W-0                      | U-0               | U-0              | U-0             | U-0     |

| —            | SSP2IP2       | SSP2IP1                    | SSP2IP0                    |                   | —                | —               | —       |

| bit 7        |               |                            |                            |                   |                  |                 | bit 0   |

|              |               |                            |                            |                   |                  |                 |         |

| Legend:      |               |                            |                            |                   |                  |                 |         |

| R = Readab   | ole bit       | W = Writable               | bit                        | U = Unimplei      | mented bit, read | d as '0'        |         |

| -n = Value a | at POR        | '1' = Bit is set           |                            | '0' = Bit is cle  | eared            | x = Bit is unkr | nown    |

|              |               |                            |                            |                   |                  |                 |         |

| bit 15-11    | -             | nted: Read as '            |                            |                   |                  |                 |         |

| bit 10-8     | BCL2IP<2:0    | >: MSSP2 I <sup>2</sup> C™ | Bus Collision              | Interrupt Prior   | rity bits        |                 |         |

|              | 111 = Interru | pt is Priority 7(          | highest priority           | / interrupt)      |                  |                 |         |

|              | •             |                            |                            |                   |                  |                 |         |

|              | •             |                            |                            |                   |                  |                 |         |

|              |               | pt is Priority 1           |                            |                   |                  |                 |         |

|              | 000 = Interru | pt source is dis           | abled                      |                   |                  |                 |         |

| bit 7        | Unimplemen    | nted: Read as '            | o'                         |                   |                  |                 |         |

| bit 6-4      | SSP2IP<2:0>   | SPI/I SPI/I                | <sup>2</sup> C Event Inter | rupt Priority bit | ts               |                 |         |

|              | 111 = Interru | pt is Priority 7 (         | highest priority           | / interrupt)      |                  |                 |         |

|              | •             |                            |                            |                   |                  |                 |         |

|              | •             |                            |                            |                   |                  |                 |         |

|              | 001 = Interru | pt is Priority 1           |                            |                   |                  |                 |         |

|              | 000 = Interru | pt source is dis           | abled                      |                   |                  |                 |         |

| bit 3-0      | Unimplemen    | ted: Read as '             | כ'                         |                   |                  |                 |         |

|              |               |                            |                            |                   |                  |                 |         |

#### REGISTER 8-28: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

## 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24FXXXXX family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator:

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The Primary Oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 25.1 "Configuration Bits"). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

## 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                      | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|------------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler<br>(LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                       | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)                 | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)      | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)      | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                              | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                              | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                              | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

NOTES:

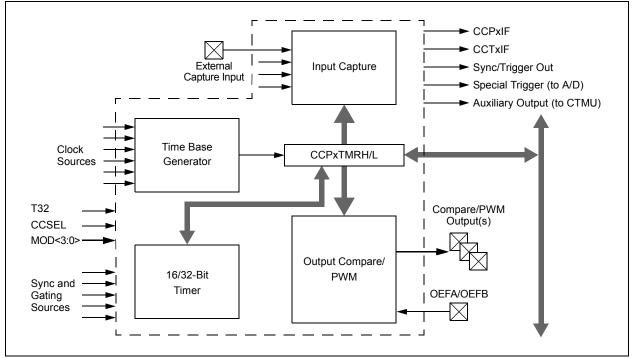

## 13.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive refer-      |

|       | ence source. For more information on the   |

|       | MCCP/SCCP modules, refer to the            |

|       | "PIC24F Family Reference Manual".          |

PIC24FV16KM204 family devices include several Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals of earlier PIC24F devices. The module can operate in one of three major modes:

- General Purpose Timer

- Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single output modules (SCCPs) provide only one PWM output. Multiple output modules (MCCPs) can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical.

The SCCP and MCCP modules can be operated only in one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode. A conceptual block diagram for the module is shown in Figure 13-1. All three modes share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of seven control and status registers:

- CCPxCON1L (Register 13-1)

- CCPxCON1H (Register 13-2)

- CCPxCON2L (Register 13-3)

- CCPxCON2H (Register 13-4)

- CCPxCON3L (Register 13-5)

- CCPxCON3H (Register 13-6)

- CCPxSTATL (Register 13-7)

Each module also includes eight buffer/counter registers that serve as Timer Value registers or data holding buffers:

- CCPxTMRH/CCPxTMRL (Timer High/Low Counters)

- CCPxPRH/CCPxPRL (Timer Period High/Low)

- CCPxRA (Primary Output Compare Data Buffer)

- CCPxRB (Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (Input Capture High/Low Buffers)

#### FIGURE 13-1: MCCPx/SCCPx CONCEPTUAL BLOCK DIAGRAM

### 13.1 Time Base Generator

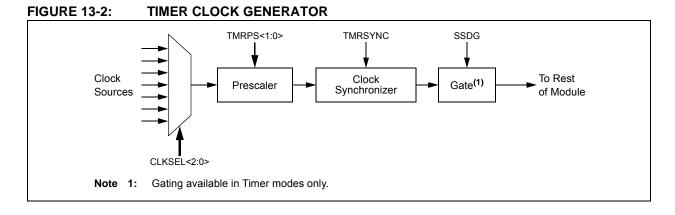

The Timer Clock Generator (TCG) generates a clock for the module's internal time base, using one of the clock signals already available on the microcontroller. This is used as the time reference for the module in its three major modes. The internal time base is shown in Figure 13-2.

There are eight inputs available to the clock generator, which are selected using the CLKSEL<2:0> bits (CCPxCON1L<10:8>). Available sources include the FRC and LPRC, the Secondary Oscillator, and the TCLKI External Clock inputs. The system clock is the default source (CLKSEL<2:0> = 000). On PIC24FV16KM204 family devices, clock sources to the MCCPx module must be synchronized with the system clock; as a result, when clock sources are selected, clock input timing restrictions or module operating restrictions may exist. Table 13-1 describes which time base sources are valid for the various operating modes.

#### TABLE 13-1: VALID TIMER OPTIONS FOR MCCPx/SCCPx MODES

| CLKSEL               | Timer I             |                      | Input   | Output  |

|----------------------|---------------------|----------------------|---------|---------|

| <2:0> <sup>(1)</sup> | Sync <sup>(2)</sup> | Async <sup>(3)</sup> | Capture | Compare |

| 111                  | Х                   | _                    | _       | _       |

| 110                  | Х                   |                      |         | —       |

| 101                  | Х                   | _                    | -       | —       |

| 011                  | Х                   | _                    | -       | —       |

| 010                  | Х                   |                      |         | —       |

| 001                  | Х                   | _                    | _       | _       |

| <sub>000</sub> (4)   | —                   | Х                    | Х       | Х       |

**Note 1:** See Register 13-1 for the description of the time base sources.

- 2: Synchronous Operation: TMRSYNC (CCPxCON1L<11>) = 1 and TRIGEN (CCPxCON1H<7>) = 0.

- Asynchronous Operation: (TMRSYNC = 0) or Triggered mode (TRIGEN = 1).

- 4: When CLKSEL<2:0> = 000, the TMRSYNC bit must be cleared.

DS30003030B-page 144

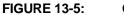

## 13.3 Output Compare Mode

Output Compare mode compares the Timer register value with the value of one or two Compare registers, depending on its mode of operation. The Output Compare x module on compare match events has the ability to generate a single output transition or a train of output

pulses. Like most PIC<sup>®</sup> MCU peripherals, the Output Compare x module can also generate interrupts on a compare match event.

Table 13-3 shows the various modes available in Output Compare modes.

| TABLE 13-3: | OUTPUT COMPARE/PWM MODES |

|-------------|--------------------------|

|-------------|--------------------------|

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) |                                        |                  |  |

|------------------------------|-----------------------|----------------------------------------|------------------|--|

| 0001                         | 0                     | Output High on Compare (16-bit)        |                  |  |

| 0001                         | 1                     | Output High on Compare (32-bit)        |                  |  |

| 0010                         | 0                     | Output Low on Compare (16-bit)         | Single Edge Mede |  |

| 0010                         | 1                     | Output Low on Compare (32-bit)         | Single Edge Mode |  |

| 0011                         | 0                     | Output Toggle on Compare (16-bit)      |                  |  |

| 0011                         | 1                     | Output Toggle on Compare (32-bit)      |                  |  |

| 0100                         | 0                     | Dual Edge Compare (16-bit)             | Dual Edge Mode   |  |

| 0101                         | 0                     | Dual Edge Compare (16-bit buffered)    | PWM Mode         |  |

| 0110                         | 0                     | Center-Aligned Pulse (16-bit buffered) | Center PWM       |  |

| 0111                         | 0                     | Variable Frequency Pulse (16-bit)      |                  |  |

| 0111                         | 1                     | Variable Frequency Pulse (32-bit)      |                  |  |

#### OUTPUT COMPARE x BLOCK DIAGRAM

#### 16.2.4 RTCC CONTROL REGISTERS

## REGISTER 16-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                  | R-0, HSC                                                                                                                                                                         | R-0, HSC                                                                                                                              | R/W-0                                                                                     | R/W-0                                                                  | R/W-0                                               |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------|

| RTCEN <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                        | RTCWREN                                                                                                                                                                                                                                                                                                                                                | RTCSYNC                                                                                                                                                                          | HALFSEC <sup>(3)</sup>                                                                                                                | RTCOE                                                                                     | RTCPTR1                                                                | RTCPTR0                                             |

| bit 15               |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  | 1                                                                                                                                     |                                                                                           |                                                                        | bit 8                                               |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

| R/W-0                | R/W-0                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                            | R/W-0                                                                                                                                 | R/W-0                                                                                     | R/W-0                                                                  | R/W-0                                               |

| CAL7                 | CAL6                                                                                                                                                                                                                                                                                                                                   | CAL5                                                                                                                                                                                                                                                                                                                                                   | CAL4                                                                                                                                                                             | CAL3                                                                                                                                  | CAL2                                                                                      | CAL1                                                                   | CAL0                                                |

| bit 7                |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        | bit (                                               |

| Legend:              |                                                                                                                                                                                                                                                                                                                                        | HSC = Hardw                                                                                                                                                                                                                                                                                                                                            | are Settable/C                                                                                                                                                                   | learable bit                                                                                                                          |                                                                                           |                                                                        |                                                     |

| R = Readable         | e bit                                                                                                                                                                                                                                                                                                                                  | W = Writable I                                                                                                                                                                                                                                                                                                                                         | oit                                                                                                                                                                              | U = Unimplem                                                                                                                          | ented bit, rea                                                                            | d as '0'                                                               |                                                     |

| -n = Value at        | POR                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  | '0' = Bit is clea                                                                                                                     |                                                                                           | x = Bit is unkr                                                        | iown                                                |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

| bit 15               | RTCEN: RT                                                                                                                                                                                                                                                                                                                              | CC Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                        | nodule is enable                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                        | nodule is disable                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

| bit 14               | •                                                                                                                                                                                                                                                                                                                                      | nted: Read as '0                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

| bit 13               |                                                                                                                                                                                                                                                                                                                                        | RTCC Value Re                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                |                                                                                                                                       | u the upor                                                                                |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                        | _H and RTCVAL<br>_H and RTCVAL                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           | n to by the user                                                       |                                                     |

| bit 12               | 0 = RTCVAL                                                                                                                                                                                                                                                                                                                             | H and RTCVAL                                                                                                                                                                                                                                                                                                                                           | L registers are                                                                                                                                                                  | locked out from                                                                                                                       | n being writter                                                                           | n to by the user                                                       |                                                     |

| bit 12               | 0 = RTCVAL<br>RTCSYNC:                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                        | L registers are<br>gisters Read S                                                                                                                                                | locked out from                                                                                                                       | h being writter<br>bit                                                                    |                                                                        | rollover ripple                                     |

| bit 12               | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting                                                                                                                                                                                                                                                                                      | ∟H and RTCVAL<br>RTCC Value Reo<br>∟H, RTCVALL ar<br>g in an invalid da                                                                                                                                                                                                                                                                                | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the                                                                                                              | locked out from<br>ynchronization<br>registers can c                                                                                  | n being writter<br>bit<br>hange while r                                                   | eading due to a                                                        |                                                     |

| bit 12               | 0 = RTCVAI<br>RTCSYNC:<br>1 = RTCVAI<br>resulting<br>can be a                                                                                                                                                                                                                                                                          | ₋H and RTCVAL<br>RTCC Value Reg<br>∟H, RTCVALL ar<br>g in an invalid da<br>assumed to be va                                                                                                                                                                                                                                                            | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the<br>alid.                                                                                                     | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

|                      | 0 = RTCVAL<br><b>RTCSYNC:</b><br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL                                                                                                                                                                                                                                                     | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or                                                                                                                                                                                                                                               | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r                                                                                       | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

| bit 12<br>bit 11     | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H                                                                                                                                                                                                                                              | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or<br>Half Second Stat                                                                                                                                                                                                                           | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>tus bit <sup>(3)</sup>                                                             | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

|                      | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC:<br>1 = Second                                                                                                                                                                                                                                  | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or                                                                                                                                                                                                                                               | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>sus bit <sup>(3)</sup><br>second                                                   | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

|                      | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal                                                                                                                                                                                                               | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a s                                                                                                                                                                                                | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>sus bit <sup>(3)</sup><br>second<br>ond                                            | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

| bit 11               | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: 1<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o                                                                                                                                                                                 | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled                                                                                                                                                        | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>tus bit <sup>(3)</sup><br>second<br>ond<br>le bit                                  | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o                                                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled                                                                                                                                 | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>second<br>ond<br>le bit                                                            | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be                                         | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without                 | eading due to a<br>ults in the same                                    | data, the data                                      |

| bit 11               | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:                                                                                                                                                      | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0-:</b> RTCC Value                                                                                                              | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind                  | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be                                         | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without                 | eading due to a<br>ults in the same<br>concern over a                  | data, the data                                      |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled                                                                                                                                 | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>LH, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>LH, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec                                                                | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT                                                                                  | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>: <u>8&gt;:</u><br>ES                                       | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKI                                                                    | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>: <u>8&gt;:</u><br>ES<br>DAY                              | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT                                                                                  | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>:8>:<br>ES<br>DAY<br>H                                      | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKE<br>10 = MONTH                                                      | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enabled<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>: <u>8&gt;:</u><br>ES<br>DAY<br>H<br>ed                    | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKI<br>10 = MONTH<br>11 = Reserv<br><u>RTCVAL&lt;7:(</u><br>00 = SECON | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va-<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br><u>:8&gt;:</u><br>ES<br>DAY<br>H<br>ed<br><u>)&gt;:</u><br>NDS | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKI<br>10 = MONTH<br>11 = Reserv<br><u>RTCVAL&lt;7:0</u>               | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va-<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br><u>:8&gt;:</u><br>ES<br>DAY<br>H<br>ed<br><u>)&gt;:</u><br>NDS | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

Note 1: The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

## REGISTER 16-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

- **Note 1:** The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

| REGISTER 16-2: | RTCPWC: RTCC CONFIGURATION REGISTER 2 <sup>(1)</sup> |

|----------------|------------------------------------------------------|

|                |                                                      |

| R/W-0      | R/W-0       | R/W-0                                | R/W-0                        | R/W-0                         | R/W-0                  | R/W-0           | R/W-0         |

|------------|-------------|--------------------------------------|------------------------------|-------------------------------|------------------------|-----------------|---------------|

| PWCEN      | PWCPOL      | PWCCPRE                              | PWCSPRE                      | RTCCLK1 <sup>(2)</sup>        | RTCCLK0 <sup>(2)</sup> | RTCOUT1         | RTCOUT0       |

| bit 15     |             |                                      |                              |                               |                        |                 | bit 8         |

|            |             |                                      |                              |                               |                        |                 |               |

| U-0        | U-0         | U-0                                  | U-0                          | U-0                           | U-0                    | U-0             | U-0           |

|            | —           |                                      |                              | _                             | —                      |                 |               |

| bit 7      |             |                                      |                              |                               |                        |                 | bit (         |

| Legend:    |             |                                      |                              |                               |                        |                 |               |

| R = Reada  | able bit    | W = Writable                         | bit                          | U = Unimpleme                 | nted bit, read as      | '0'             |               |

| -n = Value | at POR      | '1' = Bit is set                     |                              | '0' = Bit is cleare           | ed                     | x = Bit is unkr | nown          |

|            |             |                                      |                              |                               |                        |                 |               |

| bit 15     | PWCEN: Po   | wer Control Er                       | able bit                     |                               |                        |                 |               |

|            |             | ontrol is enable                     |                              |                               |                        |                 |               |

|            |             | ontrol is disable                    |                              |                               |                        |                 |               |

| bit 14     |             | ower Control F                       | •                            |                               |                        |                 |               |

|            |             | ontrol output is<br>ontrol output is | •                            |                               |                        |                 |               |

| bit 13     |             | Power Control                        |                              | caler hits                    |                        |                 |               |

|            |             |                                      | •                            | by-2 of source R <sup>-</sup> | TCC clock              |                 |               |

|            |             |                                      |                              | by-1 of source R              |                        |                 |               |

| bit 12     | PWCSPRE:    | Power Control                        | Sample Pres                  | caler bits                    |                        |                 |               |

|            |             |                                      |                              | by-2 of source RT             |                        |                 |               |

| bit 11-10  | RTCCLK<1:   | 0>: RTCC Clo                         | ck Select bits <sup>(2</sup> | 2)                            |                        |                 |               |

|            |             |                                      |                              | CC clock, which i             | s used for all RT      | CC timer opera  | ations.       |

|            |             | al Secondary O<br>I LPRC Oscillat    |                              | C)                            |                        |                 |               |

|            |             | al power line sc                     |                              |                               |                        |                 |               |

|            |             | al power line so                     |                              |                               |                        |                 |               |

| bit 9-8    | RTCOUT<1:   | : <b>0&gt;:</b> RTCC Out             | put Select bits              | 5                             |                        |                 |               |

|            |             | the source of th                     | ne RTCC pin c                | output.                       |                        |                 |               |

|            | 00 = RTCC a | •                                    |                              |                               |                        |                 |               |

|            | 01 = RTCC   | seconds clock                        |                              |                               |                        |                 |               |

|            | 11 = Power  |                                      |                              |                               |                        |                 |               |

| bit 7-0    | Unimpleme   | nted: Read as                        | '0'                          |                               |                        |                 |               |

| Note 1:    | The RTCPWC  | register is only                     | affected by a                | POR                           |                        |                 |               |

|            |             |                                      | -                            | r bits the Secon              | da Valua ragistar      | should also be  | o urritton to |

2: When a new value is written to these register bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

| R/W-0         | R/W-0                                                                                                                               | R/W-0                                                                                                                                              | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|---------------|

| ALRMEN        | CHIME                                                                                                                               | AMASK3                                                                                                                                             | AMASK2          | AMASK1            | AMASK0           | ALRMPTR1        | ALRMPTR0      |

| bit 15        |                                                                                                                                     |                                                                                                                                                    |                 |                   |                  |                 | bit 8         |

| R/W-0         | R/W-0                                                                                                                               | R/W-0                                                                                                                                              | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

| ARPT7         | ARPT6                                                                                                                               | ARPT5                                                                                                                                              | ARPT4           | ARPT3             | ARPT2            | ARPT1           | ARPT0         |