Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km204-e-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

| TADLE 1-5. |                                  |                                  | F FV          |                        |                |                                  |                                  |               |                        |                |     |        |                                             |  |

|------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|--|

|            |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                | -   |        |                                             |  |

| Function   | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |  |

| CTED1      | 11                               | 20                               | 17            | 7                      | 7              | 11                               | 2                                | 27            | 19                     | 21             | Ι   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED2      | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED3      | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED4      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED5      | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED6      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED7      | _                                |                                  | _             | 5                      | 5              |                                  |                                  | _             | 5                      | 5              | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED8      | —                                |                                  | _             | 13                     | 14             |                                  |                                  | —             | 13                     | 14             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED9      | _                                | 22                               | 19            | 9                      | 10             |                                  | 22                               | 19            | 9                      | 10             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED10     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED11     | —                                | 21                               | 18            | 8                      | 9              |                                  | 21                               | 18            | 8                      | 9              | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED12     | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED13     | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTPLS      | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   | _      | CTMU Pulse Output                           |  |

| CVREF      | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | 0   | ANA    | Comparator Voltage Reference Output         |  |

| CVREF+     | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | Ι   | ANA    | Comparator Voltage Reference Positive Input |  |

| CVREF-     | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | Comparator Voltage Reference Negative Input |  |

| DAC1OUT    | —                                | 23                               | 20            | 10                     | 11             |                                  | 23                               | 20            | 10                     | 11             | 0   | ANA    | DAC1 Output                                 |  |

| DAC1REF+   | _                                | 2                                | 27            | 19                     | 21             |                                  | 2                                | 27            | 19                     | 21             | I   | ANA    | DAC1 Positive Voltage Reference Input       |  |

| DAC2OUT    | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | ANA    | DAC2 Output                                 |  |

| DAC2REF+   | _                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | Ι   | ANA    | DAC2 Positive Voltage Reference Input       |  |

| HLVDIN     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | Ι   | ANA    | External High/Low-Voltage Detect Input      |  |

| IC1        | 14                               | 19                               | 16            | 6                      | 6              | 11                               | 19                               | 16            | 6                      | 6              | Ι   | ST     | MCCP1 Input Capture Input                   |  |

| IC2        | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | MCCP2 Input Capture Input                   |  |

| IC3        | _                                | 23                               | 20            | 13                     | 14             | _                                | 23                               | 20            | 13                     | 14             | Ι   | ST     | MCCP3 Input Capture Input                   |  |

| IC4        | _                                | 14                               | 11            | 5                      | 5              | _                                | 14                               | 11            | 5                      | 5              | I   | ST     | SCCP4 Input Capture Input                   |  |

| IC5        | _                                | 15                               | 12            | 12                     | 13             |                                  | 15                               | 12            | 12                     | 13             | Ι   | ST     | SCCP5 Input Capture Input                   |  |

| INT0       | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ST     | External Interrupt 0 Input                  |  |

| INT1       | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | External Interrupt 1 Input                  |  |

| INT2       | 14                               | 20                               | 17            | 7                      | 7              | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | External Interrupt 2 Input                  |  |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

FIGURE 2-1:

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

## 2.1 Basic Connection Requirements

Getting started with the PIC24FV16KM204 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pins (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

#### **MINIMUM CONNECTIONS** C2<sup>(2)</sup> Vdd Vss ₹R1 VDD R2 MCLR VCAP (1) C1 PIC24FV16KM204 Vdd Vss C6<sup>(2)</sup> C3(2) VDD Vss AVDD AVSS /SS 20/

RECOMMENDED

#### Key (all values are recommendations):

C5<sup>(2)</sup>

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic

C7: 10 µF, 16V tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for an explanation of VCAP pin connections.

- 2: The example shown is for a PIC24F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

C4(2)

### 2.4 Voltage Regulator Pin (VCAP)

| Note: | This    | section  | appli   | ies  | or | to  |      |

|-------|---------|----------|---------|------|----|-----|------|

|       | PIC24F  | V16KM    | devices | with | an | on- | chip |

|       | voltage | regulato | or.     |      |    |     |      |

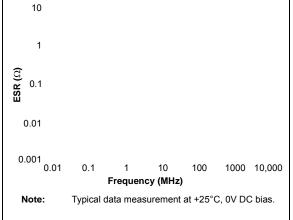

Some of the PIC24FV16KM devices have an internal voltage regulator. These devices have the voltage regulator output brought out on the VCAP pin. On the PIC24F K devices with regulators, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the voltage regulator output. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 27.0** "**Electrical Characteristics**" for additional information. Refer to **Section 27.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

# FIGURE 2-3: FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

### TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range   |

|-----------|--------------------|------------------------|----------------|---------------|---------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

### TABLE 4-15: UART1 REGISTER MAP

|                                          |       | •                      |        |          |        |        |        |       |       |          |          |           |             |       |        |        |       |               |

|------------------------------------------|-------|------------------------|--------|----------|--------|--------|--------|-------|-------|----------|----------|-----------|-------------|-------|--------|--------|-------|---------------|

| File Name                                | Addr. | Bit 15                 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE                                   | 220h  | UARTEN                 | —      | USIDL    | IREN   | RTSMD  | -      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD     | URXINV      | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA                                    | 222h  | UTXISEL1               | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN     | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG                                  | 224h  | _                      | _      | _        | _      | _      | _      | _     |       |          |          | UART1 Tra | ansmit Regi | ster  |        |        |       | xxxx          |

| U1RXREG                                  | 226h  | UART1 Receive Register |        |          |        |        |        |       |       |          |          |           | 0000        |       |        |        |       |               |

| U1BRG 228h Baud Rate Generator Prescaler |       |                        |        |          |        |        |        |       |       |          |          | 0000      |             |       |        |        |       |               |

|                                          |       |                        |        |          |        |        |        |       |       |          |          |           |             |       |        |        |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-16: UART2 REGISTER MAP

| File Name              | Addr. | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|------------------------|-------|----------|-------------------------------|----------|--------|--------|--------|-------|------------------------|----------|----------|-----------|-------------|-------|--------|--------|-------|---------------|

| U2MODE <sup>(1)</sup>  | 230h  | UARTEN   | —                             | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD     | URXINV      | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA <sup>(1)</sup>   | 232h  | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN     | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG <sup>(1)</sup> | 234h  | _        | _                             | _        | —      | _      | _      | _     |                        |          |          | UART2 Tra | nsmit Regis | ster  |        |        |       | xxxx          |

| U2RXREG <sup>(1)</sup> | 236h  | _        | _                             | _        | —      | _      | _      | _     | UART2 Receive Register |          |          |           |             |       | 0000   |        |       |               |

| U2BRG <sup>(1)</sup>   | 238h  |          | Baud Rate Generator Prescaler |          |        |        |        |       |                        |          |          |           |             | 0000  |        |        |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

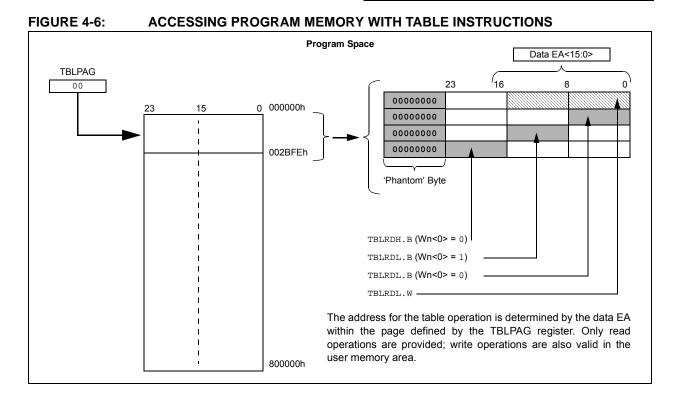

### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through Data Space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

Note: The TBLRDH and TBLWTH instructions are not used while accessing data EEPROM memory.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit, word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table Write operations are not allowed.

© 2013 Microchip Technology Inc.

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time. It is also possible to program single words.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks, and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

| Note: | Writing | to a |      | location     | multiple | times, |

|-------|---------|------|------|--------------|----------|--------|

|       | without | eras | sing | it, is not i | ecommer  | nded.  |

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.5 "Programming Operations"** for further details.

## 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | U-0   |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| —      | —   | —   | —   | —   | —   | CCT5IF    | —     |

| bit 15 |     |     |     |     |     |           | bit 8 |

|        |     |     |     |     |     |           |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0       | U-0   |

|        |     | _   | _   |     | _   |           | _     |

| bit 7  |     |     |     |     |     |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | CCT5IF: Capture/Compare 5 Timer Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

|           |                                                           |

bit 8-0 Unimplemented: Read as '0'

### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | BCL2IF    | SSP2IF    | —     |

| bit 7 |     |     |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                          |

|----------|-------------------------------------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit                       |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 13-3 | Unimplemented: Read as '0'                                                          |

| bit 2    | BCL2IF: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 1    | SSP2IF: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Flag Status bit                  |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 0    | Unimplemented: Read as '0'                                                          |

|          |                                                                                     |

### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----|-----------|

| —     | —   | —   | _   | —   | _   | —   | ULPWUIF   |

| bit 7 |     |     |     |     |     |     | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

### REGISTER 8-11: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----------|-----------|

| —     | —   | —   | —   | —   | —   | CLC2IF    | CLC1IF    |

| bit 7 |     |     |     |     |     |           | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IF: Configurable Logic Cell 2 Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

bit 0 CLC1IF: Configurable Logic Cell 1 Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

| U-0                   | R/W-1                                                                                                                | R/W-0                                | R/W-0            | U-0              | R/W-1             | R/W-0           | R/W-0   |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|------------------|-------------------|-----------------|---------|--|--|--|--|

| _                     | DAC2IP2                                                                                                              | DAC2IP1                              | DAC2IP0          |                  | DAC1IP2           | DAC1IP1         | DAC1IP0 |  |  |  |  |

| bit 15                |                                                                                                                      |                                      |                  |                  |                   |                 | bit 8   |  |  |  |  |

| U-0                   | R/W-1                                                                                                                | R/W-0                                | R/W-0            | U-0              | U-0               | U-0             | U-0     |  |  |  |  |

| _                     | CTMUIP2                                                                                                              | CTMUIP1                              | CTMUIP0          | _                |                   | _               | _       |  |  |  |  |

| bit 7                 |                                                                                                                      |                                      |                  |                  |                   |                 | bit (   |  |  |  |  |

| Legend:               |                                                                                                                      |                                      |                  |                  |                   |                 |         |  |  |  |  |

| Legena.<br>R = Readab | le hit                                                                                                               | W = Writable                         | hit              | II = Unimple     | mented bit, read  | las 'O'         |         |  |  |  |  |

| -n = Value a          |                                                                                                                      | '1' = Bit is set                     | on               | '0' = Bit is cle |                   | x = Bit is unkr |         |  |  |  |  |

|                       |                                                                                                                      |                                      |                  |                  | aleu              |                 |         |  |  |  |  |

| bit 15                | Unimplemen                                                                                                           | ted: Read as '                       | )'               |                  |                   |                 |         |  |  |  |  |

| bit 14-12             | -                                                                                                                    |                                      |                  | 2 Event Interr   | upt Priority bits |                 |         |  |  |  |  |

|                       |                                                                                                                      | •                                    | •                |                  | upt i nonty bits  |                 |         |  |  |  |  |

|                       | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li>•</li> </ul>                            |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | •                                                                                                                    |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | •                                                                                                                    |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | 001 = Interru<br>000 = Interru                                                                                       | pt is Priority 1<br>pt source is dis | abled            |                  |                   |                 |         |  |  |  |  |

| bit 11                | Unimplemen                                                                                                           | ted: Read as '                       | )'               |                  |                   |                 |         |  |  |  |  |

| bit 10-8              | DAC1IP<2:0>                                                                                                          | -: Digital-to-Ana                    | alog Converter   | 1 Event Interr   | upt Priority bits |                 |         |  |  |  |  |

|                       | 111 = Interru                                                                                                        | pt is Priority 7(                    | highest priority | / interrupt)     |                   |                 |         |  |  |  |  |

|                       | •                                                                                                                    |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | •                                                                                                                    |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | •<br>001 = Interru                                                                                                   | nt is Priority 1                     |                  |                  |                   |                 |         |  |  |  |  |

|                       |                                                                                                                      | pt is Fridity 1                      | abled            |                  |                   |                 |         |  |  |  |  |

| bit 7                 | -                                                                                                                    | ted: Read as '                       |                  |                  |                   |                 |         |  |  |  |  |

| bit 6-4               | -                                                                                                                    |                                      |                  | s                |                   |                 |         |  |  |  |  |

|                       | <b>CTMUIP&lt;2:0&gt;:</b> CTMU Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | •                                                                                                                    |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | •                                                                                                                    |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | •                                                                                                                    |                                      |                  |                  |                   |                 |         |  |  |  |  |

|                       | 001 = Interru                                                                                                        | pt is Priority 1<br>pt source is dis | ahlad            |                  |                   |                 |         |  |  |  |  |

| hit 2 0               |                                                                                                                      |                                      |                  |                  |                   |                 |         |  |  |  |  |

| bit 3-0               | Unimplemented: Read as '0'                                                                                           |                                      |                  |                  |                   |                 |         |  |  |  |  |

### REGISTER 8-32: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

| R/W-0        | U-0                                                                                                 | R/W-0                       | U-0                                | U-0                     | U-0              | R/W-0                | R/W-0                |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------|-------------------------|------------------|----------------------|----------------------|--|--|--|

| TON          |                                                                                                     | TSIDL                       | —                                  | _                       | —                | TECS1 <sup>(1)</sup> | TECS0 <sup>(1)</sup> |  |  |  |

| bit 15       |                                                                                                     | •                           | -                                  |                         |                  |                      | bit                  |  |  |  |

|              |                                                                                                     |                             |                                    |                         |                  |                      |                      |  |  |  |

| U-0          | R/W-0                                                                                               | R/W-0                       | R/W-0                              | U-0                     | R/W-0            | R/W-0                | U-0                  |  |  |  |

| —            | TGATE                                                                                               | TCKPS1                      | TCKPS0                             | —                       | TSYNC            | TCS                  | —                    |  |  |  |

| bit 7        |                                                                                                     |                             |                                    |                         |                  |                      | bit                  |  |  |  |

| Legend:      |                                                                                                     |                             |                                    |                         |                  |                      |                      |  |  |  |

| R = Readab   | ole bit                                                                                             | W = Writable                | bit                                | U = Unimpler            | mented bit, read | d as '0'             |                      |  |  |  |

| -n = Value a | It POR                                                                                              | '1' = Bit is set            |                                    | '0' = Bit is cle        | ared             | x = Bit is unkr      | iown                 |  |  |  |

|              |                                                                                                     |                             |                                    |                         |                  |                      |                      |  |  |  |

| bit 15       | TON: Timer1                                                                                         | On bit                      |                                    |                         |                  |                      |                      |  |  |  |

|              | 1 = Starts 16-<br>0 = Stops 16-                                                                     |                             |                                    |                         |                  |                      |                      |  |  |  |

| bit 14       | Unimplemen                                                                                          | ted: Read as '              | 0'                                 |                         |                  |                      |                      |  |  |  |

| bit 13       | TSIDL: Timer                                                                                        | 1 Stop in Idle I            | Node bit                           |                         |                  |                      |                      |  |  |  |

|              |                                                                                                     |                             | eration when o<br>ation in Idle mo | device enters lo<br>ode | lle mode         |                      |                      |  |  |  |

| bit 12-10    | Unimplemen                                                                                          | ted: Read as '              | 0'                                 |                         |                  |                      |                      |  |  |  |

| bit 9-8      |                                                                                                     |                             | ed Clock Seled                     | ct bits <sup>(1)</sup>  |                  |                      |                      |  |  |  |

|              | 11 = Reserve                                                                                        | •                           | as the sleek s                     | 0.1700                  |                  |                      |                      |  |  |  |

|              | 10 = Timer1 uses the LPRC as the clock source<br>01 = Timer1 uses the External Clock (EC) from T1CK |                             |                                    |                         |                  |                      |                      |  |  |  |

|              |                                                                                                     |                             |                                    | r (SOSC) as th          | e clock source   |                      |                      |  |  |  |

| bit 7        | Unimplemen                                                                                          | ted: Read as '              | 0'                                 |                         |                  |                      |                      |  |  |  |

| bit 6        |                                                                                                     |                             | Accumulation                       | Enable bit              |                  |                      |                      |  |  |  |

|              | When TCS =                                                                                          |                             |                                    |                         |                  |                      |                      |  |  |  |

|              | When TCS = $\frac{1}{2}$                                                                            |                             |                                    |                         |                  |                      |                      |  |  |  |

|              |                                                                                                     | <u>o.</u><br>ne accumulatio | n is enabled                       |                         |                  |                      |                      |  |  |  |

|              | 0 = Gated tim                                                                                       | ne accumulatio              | n is disabled                      |                         |                  |                      |                      |  |  |  |

| bit 5-4      | TCKPS<1:0>                                                                                          | : Timer1 Input              | Clock Prescale                     | e Select bits           |                  |                      |                      |  |  |  |

|              | 11 = 1:256                                                                                          |                             |                                    |                         |                  |                      |                      |  |  |  |

|              | 10 = 1:64<br>01 = 1:8                                                                               |                             |                                    |                         |                  |                      |                      |  |  |  |

|              | 00 = 1:1                                                                                            |                             |                                    |                         |                  |                      |                      |  |  |  |

| bit 3        | Unimplemen                                                                                          | ted: Read as '              | 0'                                 |                         |                  |                      |                      |  |  |  |

| bit 2        | TSYNC: Time                                                                                         | er1 External Cl             | ock Input Sync                     | hronization Se          | lect bit         |                      |                      |  |  |  |

|              | <u>When TCS =</u>                                                                                   | <u>1:</u><br>nizes External | Clock input                        |                         |                  |                      |                      |  |  |  |

|              |                                                                                                     |                             | External Clock                     | input                   |                  |                      |                      |  |  |  |

|              | When TCS =                                                                                          | -                           |                                    |                         |                  |                      |                      |  |  |  |

|              | This bit is igno                                                                                    | ored.                       |                                    |                         |                  |                      |                      |  |  |  |

| bit 1        |                                                                                                     | Clock Source                |                                    |                         |                  |                      |                      |  |  |  |

|              |                                                                                                     |                             | selected by TE                     | CS<1:0>                 |                  |                      |                      |  |  |  |

|              | 0 = Internal c                                                                                      |                             |                                    |                         |                  |                      |                      |  |  |  |

| bit 0        | Unimplemen                                                                                          | tod. Dood oo .              | Ω'                                 |                         |                  |                      |                      |  |  |  |

## 13.5 Auxiliary Output

The MCCPx and SCCPx modules have an auxiliary (secondary) output that provides other peripherals access to internal module signals. The auxiliary output is intended to connect to other MCCP or SCCP modules, or other digital peripherals, to provide these types of functions:

- Time Base Synchronization

- Peripheral Trigger and Clock Inputs

- Signal Gating

The type of output signal is selected using the AUXOUT<1:0> control bits (CCPxCON2H<4:3>). The type of output signal is also dependent on the module operating mode.

On the PIC24FV16KM204 family of devices, only the CTMU discharge trigger has access to the auxiliary output signal.

| AUXOUT<1:0> | CCSEL | MOD<3:0> | Comments                  | Signal Description                  |

|-------------|-------|----------|---------------------------|-------------------------------------|

| 00          | x     | xxxx     | Auxiliary output disabled | No Output                           |

| 01          | 0     | 0000     | Time Base modes           | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Special Event Trigger Output        |

| 11          |       |          |                           | No Output                           |

| 01          | 0     | 0001     | Output Compare modes      | Time Base Period Reset or Rollover  |

| 10          |       | through  |                           | Output Compare Event Signal         |

| 11          |       | 1111     |                           | Output Compare Signal               |

| 01          | 1     | xxxx     | Input Capture modes       | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Reflects the Value of the ICDIS bit |

| 11          |       |          |                           | Input Capture Event Signal          |

### TABLE 13-5: AUXILIARY OUTPUT

To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs and/or select band gap reference inputs (ANSx registers).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- e) Configure the MODE12 bit to select A/D resolution (AD1CON1<10>).

- f) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- g) Select the interrupt rate (AD1CON2<6:2>).

- h) Turn on the A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

To perform an A/D sample and conversion using Threshold Detect scanning:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs (ANSx registers).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- e) Configure the MODE12 bit to select A/D resolution (AD1CON1<10>).

- f) Select how the conversion results are presented in the buffer (AD1CON1<9:8>).

- g) Select the interrupt rate (AD1CON2<6:2>).

- 2. Configure the threshold compare channels:

- a) Enable auto-scan; set the ASEN bit (AD1CON5<15>).

- b) Select the Compare mode, "Greater Than, Less Than or Windowed"; set the CMx bits (AD1CON5<1:0>).

- c) Select the threshold compare channels to be scanned (AD1CSSH, AD1CSSL).

- d) If the CTMU is required as a current source for a threshold compare channel, enable the corresponding CTMU channel (AD1CTMENH, AD1CTMENL).

- e) Write the threshold values into the corresponding ADC1BUFx registers.

- f) Turn on the A/D module (AD1CON1<15>).

- Note: If performing an A/D sample and conversion, using Threshold Detect in Sleep Mode, the RC A/D clock source must be selected before entering into Sleep mode.

- 3. Configure the A/D interrupt (OPTIONAL):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

### REGISTER 20-1: DACxCON: DACx CONTROL REGISTER (CONTINUED)

- bit 6-2 DACTSEL<4:0>: DACx Trigger Source Select bits

- 11101-11111 = Unused 11100 = CTMU 11011 = A/D 11010 = Comparator 3 11001 = Comparator 2 11000 = Comparator 1 10011 to 10111 = Unused 10010 = CLC2 output 10001 = CLC1 output 01100 to 10000 = Unused 01011 = Timer1 Sync output 01010 = External Interrupt 2 01001 = External Interrupt 1 01000 = External Interrupt 0 0011x = Unused 00101 = MCCP5 or SCCP5 Sync output 00100 = MCCP4 or SCCP4 Sync output 00011 = MCCP3 or SCCP3 Sync output 00010 = MCCP2 or SCCP2 Sync output 00001 = MCCP1 or SCCP1 Sync output 00000 = Unused DACREF<1:0>: DACx Reference Source Select bits 11 = Internal Band Gap Buffer 1 (BGBUF1)<sup>(1)</sup>

- 10 = AVDD

bit 1-0

- 01 = DVREF+

- 00 = Reference is not connected (lowest power but no DAC functionality)

- **Note 1:** BGBUF1 voltage is configured by BUFREF<1:0> (BUFCON0<1:0>).

### REGISTER 23-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0          | U-0          | U-0                                  | U-0            | U-0                  | U-0             | U-0             | U-0   |  |  |  |

|--------------|--------------|--------------------------------------|----------------|----------------------|-----------------|-----------------|-------|--|--|--|

| _            | —            |                                      |                |                      |                 | —               | —     |  |  |  |

| bit 15       |              |                                      |                |                      |                 |                 | bit 8 |  |  |  |

|              |              |                                      |                |                      |                 |                 |       |  |  |  |

| R/W-0        | R/W-0        | R/W-0                                | R/W-0          | R/W-0                | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| CVREN        | CVROE        | CVRSS                                | CVR4           | CVR3                 | CVR2            | CVR1            | CVR0  |  |  |  |

| bit 7        |              |                                      |                |                      |                 |                 | bit ( |  |  |  |

|              |              |                                      |                |                      |                 |                 |       |  |  |  |

| Legend:      |              |                                      |                |                      |                 |                 |       |  |  |  |

| R = Readab   |              | W = Writable                         | bit            | •                    | nented bit, rea |                 |       |  |  |  |

| -n = Value a | t POR        | '1' = Bit is set                     |                | '0' = Bit is clea    | ared            | x = Bit is unkr | nown  |  |  |  |

| bit 15-8     | Unimplomon   | ted: Read as '                       | <b>)</b> '     |                      |                 |                 |       |  |  |  |

| bit 7        | •            |                                      |                | achla bit            |                 |                 |       |  |  |  |

| DIT 7        |              | parator Voltage                      |                | nable bit            |                 |                 |       |  |  |  |

|              |              | rcuit is powered<br>rcuit is powered |                |                      |                 |                 |       |  |  |  |

| bit 6        |              | parator VREF (                       |                | bit                  |                 |                 |       |  |  |  |

|              |              | oltage level is o                    | •              |                      |                 |                 |       |  |  |  |

|              |              | 0                                    |                | rom the CVREF        | pin             |                 |       |  |  |  |

| bit 5        | CVRSS: Com   | parator VREF S                       | ource Selecti  | on bit               |                 |                 |       |  |  |  |

|              | 1 = Compara  | tor reference s                      | ource, CVRSR   | c = Vref+ – Vr       | EF-             |                 |       |  |  |  |

|              | 0 = Compara  | tor reference s                      | ource, CVRSR   | c = AVDD – AVS       | S               |                 |       |  |  |  |

| bit 4-0      | CVR<4:0>: C  | omparator VRE                        | F Value Selec  | tion $0 \le CVR < 4$ | :0> ≤ 31 bits   |                 |       |  |  |  |

|              |              | When CVRSS = 1:                      |                |                      |                 |                 |       |  |  |  |

|              | ,            | EF-) + (CVR<4:(                      | )>/32) • (VREF | + – VREF-)           |                 |                 |       |  |  |  |

|              | When CVRSS   |                                      |                |                      |                 |                 |       |  |  |  |

|              | OVREF = (AVS | ss) + (CVR<4:0                       | ~132) • (AVDD  | – AVSS)              |                 |                 |       |  |  |  |

### REGISTER 24-3: CTMUCON2L: CTMU CONTROL 2 LOW REGISTER

| U-0          | U-0                                                                | U-0                               | U-0              | U-0          | U-0             | U-0               | U-0         |  |  |  |

|--------------|--------------------------------------------------------------------|-----------------------------------|------------------|--------------|-----------------|-------------------|-------------|--|--|--|

| _            | —                                                                  | —                                 | —                | —            | —               | —                 | —           |  |  |  |

| bit 15       |                                                                    |                                   |                  |              |                 |                   | bit 8       |  |  |  |

|              |                                                                    |                                   |                  |              |                 |                   |             |  |  |  |

| U-0          | U-0                                                                | U-0                               | R/W-0            | U-0          | R/W-0           | R/W-0             | R/W-0       |  |  |  |

|              | —                                                                  | —                                 | IRSTEN           | —            | DISCHS2         | DISCHS1           | DISCHS0     |  |  |  |

| bit 7 bit 0  |                                                                    |                                   |                  |              |                 |                   |             |  |  |  |

|              |                                                                    |                                   |                  |              |                 |                   |             |  |  |  |

| Legend:      |                                                                    |                                   |                  |              |                 |                   |             |  |  |  |

| R = Readab   | ole bit                                                            | W = Writable                      | bit              | U = Unimpler | mented bit, rea | d as '0'          |             |  |  |  |

| -n = Value a | -n = Value at POR '1' = Bit is set                                 |                                   |                  |              | ared            | x = Bit is unkn   | own         |  |  |  |

|              |                                                                    |                                   |                  |              |                 |                   |             |  |  |  |

| bit 15-5     | Unimplement                                                        | ted: Read as '                    | 0'               |              |                 |                   |             |  |  |  |

| bit 4        | IRSTEN: CTM                                                        | IU Current Sou                    | urce Reset Ena   | able bit     |                 |                   |             |  |  |  |

|              | detect log                                                         | gic                               |                  |              | SSEN control    | bit will reset th | e CTMU edge |  |  |  |

|              |                                                                    |                                   | c will not occur |              |                 |                   |             |  |  |  |

| bit 3        | Unimplement                                                        | ted: Read as '                    | 0'               |              |                 |                   |             |  |  |  |

| bit 2-0      | DISCHS<2:0>                                                        | Discharge S                       | ource Select bi  | its          |                 |                   |             |  |  |  |

|              |                                                                    | 111 = CLC2 output                 |                  |              |                 |                   |             |  |  |  |

|              | 110 = CLC1 c                                                       |                                   |                  |              |                 |                   |             |  |  |  |

|              |                                                                    | ed; do not use<br>d of conversion |                  |              |                 |                   |             |  |  |  |

|              | 100 = A/D end of conversion signal<br>011 = SCCP5 auxiliary output |                                   |                  |              |                 |                   |             |  |  |  |

- 110 = MCCP2 auxiliary output 001 = MCCP1 auxiliary output

- 000 = No discharge source selected, use the IDISSEN bit

| R/P-1                | R/P-1                               | R/P-1                | R/P-1                         | R/P-1                | R/P-1                 | R/P-1           | R/P-1            |

|----------------------|-------------------------------------|----------------------|-------------------------------|----------------------|-----------------------|-----------------|------------------|

| MCLRE <sup>(2)</sup> | BORV1 <sup>(3)</sup>                | BORV0 <sup>(3)</sup> | I2C1SEL <sup>(1)</sup>        | PWRTEN               | RETCFG <sup>(1)</sup> | BOREN1          | BOREN0           |

| bit 7                |                                     |                      |                               |                      |                       | •               | bit (            |

| Legend:              |                                     |                      |                               |                      |                       |                 |                  |

| R = Reada            | ble bit                             | P = Programr         | nable bit                     | U = Unimplen         | nented bit, read      | as '0'          |                  |

| -n = Value           | at POR                              | '1' = Bit is set     |                               | '0' = Bit is clea    |                       | x = Bit is unkr | nown             |

| bit 7                | MCLRE: MCL                          | R Pin Enable b       | <sub>it</sub> (2)             |                      |                       |                 |                  |

|                      |                                     |                      | 5 input pin is di             | sabled               |                       |                 |                  |

|                      |                                     |                      | MCLR is disab                 |                      |                       |                 |                  |

| bit 6-5              | BORV<1:0>: [                        | Brown-out Rese       | et Enable bits <sup>(3)</sup> | )                    |                       |                 |                  |

|                      | 11 = Brown-ou                       | it Reset is set t    | o the lowest vo               | ltage                |                       |                 |                  |

|                      |                                     |                      | o the middle vo               | 0                    |                       |                 |                  |

|                      |                                     |                      | o the highest ve              |                      |                       |                 |                  |

|                      |                                     | -                    |                               | a – Low-Power        | BOR (LPBOR)           | is selected     |                  |

| bit 4                | I2C1SEL: Alte                       |                      |                               |                      |                       |                 |                  |

|                      | 1 = Default loc<br>0 = Alternate lo |                      |                               |                      |                       |                 |                  |

| bit 3                | PWRTEN: Pov                         | ver-up Timer E       | nable bit                     |                      |                       |                 |                  |

|                      | 1 = PWRT is e                       | nabled               |                               |                      |                       |                 |                  |

|                      | 0 = PWRT is d                       | isabled              |                               |                      |                       |                 |                  |

| bit 2                | RETCFG: Ret                         | ention Regulate      | or Configuratior              | n bit <sup>(1)</sup> |                       |                 |                  |

|                      | 1 = Low-voltag<br>0 = Low-voltag    |                      |                               | ontrolled by the     | RETEN bit (RC         | ON<12>) durin   | g Sleep          |

| bit 1-0              | BOREN<1:0>:                         | Brown-out Re         | set Enable bits               |                      |                       |                 |                  |

|                      | 11 = Brown-ou                       | it Reset is enal     | oled in hardwar               | e; SBOREN bit        | is disabled           |                 |                  |

|                      |                                     |                      | •                             |                      | and disabled in S     | leep; SBOREN    | l bit is disable |

|                      |                                     |                      | rolled with the               |                      |                       |                 |                  |

|                      | 00 = Brown-ol                       | It Reset is disa     | bled in hardwar               | re; SBOREN DI        | t is disabled         |                 |                  |

| Note 1:              | This setting only devices.          | applies to the       | "FV" devices. T               | his bit is reserv    | ved and should I      | be maintained a | as '1' on "F"    |

| 2:                   | The MCLRE fus                       | e can only be c      | hanged when ι                 | using the VPP-b      | ased ICSP™ m          | ode entry. This | prevents a       |