#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km204-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

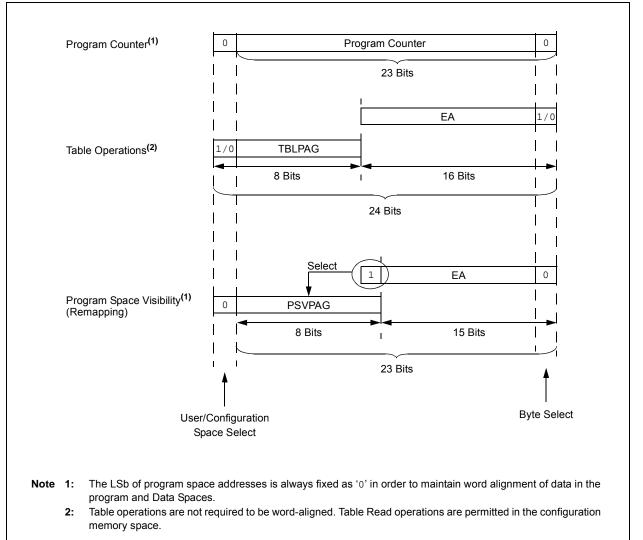

## TABLE 4-35: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        | Program Space Address        |                |                     |                    |        |  |

|--------------------------|---------------|------------------------------|----------------|---------------------|--------------------|--------|--|

| Access Type              | Space         | <23>                         | <22:16>        | <15>                | <14:1>             | <0>    |  |

| Instruction Access       | User          | 0                            |                | PC<22:1>            |                    | 0      |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |                |                     |                    |        |  |

| TBLRD/TBLWT              | User          | TBLPAG<7:0>                  |                | Data EA<15:0>       |                    |        |  |

| (Byte/Word Read/Write)   |               | 0xxx xxxx x:                 |                |                     | xxx xxxx xxxx xxxx |        |  |

|                          | Configuration | TBLPAG<7:0>                  |                | Data EA<15:0>       |                    |        |  |

|                          | 1xxx xxxx     |                              | xxx xxxx       | xxxx xxxx xxxx xxxx |                    |        |  |

| Program Space Visibility | User          | 0                            | PSVPAG<7:0>(2) |                     | Data EA<14:0>(1)   |        |  |

| (Block Remap/Read)       |               | 0 xxxx xxx                   |                | κx                  | xxx xxxx xxx       | x xxxx |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on the PIC24F16KM family.

## FIGURE 4-5: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts<br>for next 5 instructions |

|------|-------------|---|-------------------------------------------------|

| MOV  | #0x55, W0   |   |                                                 |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                                |

| MOV  | #0xAA, W1   | ; |                                                 |

| MOV  | W1, NVMKEY  | ; | Write the AA key                                |

| BSET | NVMCON, #WR | ; | Start the erase sequence                        |

| NOP  |             | ; | 2 NOPs required after setting WR                |

| NOP  |             | ; |                                                 |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed           |

| BRA  | \$-2        | ; |                                                 |

|      |             |   |                                                 |

## EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

## 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on data EEPROM, refer to the *"PIC24F Family Reference Manual"*, **"Data EEPROM"** (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFh. The size of the data EEPROM is 256 words in PIC24FXXXXX devices.

The data EEPROM is organized as 16-bit-wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

## 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

## 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

|                | rrupts For 5 instruc | ctions |

|----------------|----------------------|--------|

| asm volatile   | ("disi #5");         |        |

| //Issue Unlock | Sequence             |        |

| asm volatile   | ("mov #0x55, W0      | \n"    |

|                | "mov W0, NVMKEY      | \n"    |

|                | "mov #0xAA, W1       | \n"    |

|                | "mov W1, NVMKEY      | \n");  |

| // Perform Wri | te/Erase operations  |        |

| asm volatile   | ("bset NVMCON, #WR   | \n"    |

|                | "nop                 | \n"    |

|                | "nop                 | \n");  |

|                |                      |        |

**REGISTER 7-1:**

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0, H   | S R/W-0, HS                    | R/W-0                                      | R/W-0                | U-0                  | U-0                                 | R/W-0             | R/W-0          |  |  |

|------------|--------------------------------|--------------------------------------------|----------------------|----------------------|-------------------------------------|-------------------|----------------|--|--|

| TRAPR      |                                | SBOREN                                     | RETEN <sup>(3)</sup> | _                    | _                                   | СМ                | PMSLP          |  |  |

| bit 15     |                                |                                            |                      |                      |                                     |                   | bit 8          |  |  |

|            |                                |                                            |                      |                      |                                     |                   |                |  |  |

| R/W-0, H   | S R/W-0, HS                    | R/W-0, HS                                  | R/W-0, HS            | R/W-0, HS            | R/W-0, HS                           | R/W-1, HS         | R/W-1, HS      |  |  |

| EXTR       | SWR                            | SWDTEN <sup>(2)</sup>                      | WDTO                 | SLEEP                | IDLE                                | BOR               | POR            |  |  |

| bit 7      |                                |                                            |                      |                      |                                     |                   | bit C          |  |  |

|            |                                |                                            |                      |                      |                                     |                   |                |  |  |

| Legend:    |                                | HS = Hardwar                               | e Settable bit       |                      |                                     |                   |                |  |  |

| R = Read   | able bit                       | W = Writable t                             | pit                  | U = Unimplen         | nented bit, read                    | as '0'            |                |  |  |

| -n = Value | e at POR                       | '1' = Bit is set                           |                      | '0' = Bit is cle     | ared                                | x = Bit is unkn   | own            |  |  |

|            |                                |                                            |                      |                      |                                     |                   |                |  |  |

| bit 15     | -                              | Reset Flag bit                             |                      |                      |                                     |                   |                |  |  |

|            | •                              | onflict Reset has                          |                      |                      |                                     |                   |                |  |  |

| 1.11.4.4   |                                | onflict Reset has                          |                      |                      | <b>E</b> 1                          |                   |                |  |  |

| bit 14     |                                | gal Opcode or l                            |                      |                      | r Flag bit<br>or Uninitialized V    | / register used   | aa an Addraaa  |  |  |

|            |                                | aused a Reset                              | on, an illegal a     | duress mode c        |                                     | v register used   | as an Address  |  |  |

|            |                                | opcode or Unir                             | nitialized W Re      | set has not oc       | curred                              |                   |                |  |  |

| bit 13     | SBOREN: So                     | oftware Enable/D                           | Disable of BOF       | R bit                |                                     |                   |                |  |  |

|            | 1 = BOR is tu                  | rned on in softw                           | are                  |                      |                                     |                   |                |  |  |

|            |                                | rned off in softw                          |                      |                      |                                     |                   |                |  |  |

| bit 12     |                                | RETEN: Retention Sleep Mode <sup>(3)</sup> |                      |                      |                                     |                   |                |  |  |

|            |                                |                                            |                      |                      | Regulator (RETR<br>ge Regulator (VF |                   |                |  |  |

| bit 11-10  | -                              | ted: Read as '0                            |                      |                      |                                     |                   |                |  |  |

| bit 9      | -                              | ation Word Misr                            |                      | lag bit              |                                     |                   |                |  |  |

|            | -                              | Iration Word Mis                           |                      | -                    |                                     |                   |                |  |  |

|            | 0 = A Configu                  | ration Word Mis                            | match Reset          | has not occurre      | ed                                  |                   |                |  |  |

| bit 8      | PMSLP: Prog                    | gram Memory Po                             | ower During S        | leep bit             |                                     |                   |                |  |  |

|            |                                | memory bias vo                             |                      |                      |                                     |                   |                |  |  |

|            | 0 = Program<br>Standby         |                                            | oltage is pow        | ered down du         | iring Sleep and                     | the voltage re    | gulator enters |  |  |

| bit 7      | •                              | nal Reset (MCLF                            | R) Pin hit           |                      |                                     |                   |                |  |  |

| bit i      |                                | Clear (pin) Rese                           |                      | d                    |                                     |                   |                |  |  |

|            |                                | Clear (pin) Rese                           |                      |                      |                                     |                   |                |  |  |

| bit 6      | SWR: Softwa                    | re reset (Instru                           | uction) Flag bit     | t                    |                                     |                   |                |  |  |

|            |                                | instruction has t                          |                      |                      |                                     |                   |                |  |  |

|            |                                | instruction has r                          |                      |                      |                                     |                   |                |  |  |

| bit 5      |                                | oftware Enable/[                           | Disable of WD        | l bit <sup>(2)</sup> |                                     |                   |                |  |  |

|            | 1 = WDT is ei<br>0 = WDT is di |                                            |                      |                      |                                     |                   |                |  |  |

|            |                                |                                            |                      |                      | <b>-</b>                            |                   |                |  |  |

| Note 1:    | All of the Reset               | •                                          | be set or clear      | ed in software.      | Setting one of the                  | nese bits in soft | ware does not  |  |  |

| 2:         | If the FWDTEN                  |                                            | tion bits are '1     | 1' (upprogram        | med) the WDT i                      | is alwavs enabl   | ed renardless  |  |  |

| <b>_</b> . | of the SWDTEN                  |                                            |                      |                      |                                     | ie amayo chabi    |                |  |  |

| -          |                                |                                            |                      |                      |                                     |                   |                |  |  |

## 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

## REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS |  |

|-------------|-----|-----|-----|-----|-----|-----|-----------|--|

| —           | —   | —   | _   | —   | _   | —   | ULPWUIF   |  |

| bit 7 bit 0 |     |     |     |     |     |     |           |  |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

## REGISTER 8-11: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | —   | —   | —   | —   | —   | —   | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |  |

|-------------|-----|-----|-----|-----|-----|-----------|-----------|--|

| —           | —   | —   | —   | —   | —   | CLC2IF    | CLC1IF    |  |

| bit 7 bit 0 |     |     |     |     |     |           |           |  |

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IF: Configurable Logic Cell 2 Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

bit 0 CLC1IF: Configurable Logic Cell 1 Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

## REGISTER 8-31: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

| _       | —   | —   | —   | —   | —       | —       | —       |

| bit 15  | ·   | •   |     |     | •       |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _       | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Logondi |     |     |     |     |         |         |         |

| Legend: |  |

|---------|--|

|---------|--|

bit 2-0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| R-0           | U-0                                                                                                                                                                 | R/W-0             | U-0            | R-0              | R-0               | R-0             | R-0              |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|------------------|-------------------|-----------------|------------------|--|--|--|

| CPUIRQ        |                                                                                                                                                                     | VHOLD             |                | ILR3             | ILR2              | ILR1            | ILR0             |  |  |  |

| bit 15        |                                                                                                                                                                     |                   |                |                  |                   |                 | bit 8            |  |  |  |

|               |                                                                                                                                                                     |                   |                |                  |                   |                 |                  |  |  |  |

| U-0           |                                                                                                                                                                     |                   |                |                  |                   | R-0             |                  |  |  |  |

| <br>bit 7     | VECNUM6                                                                                                                                                             | VECNUM5           | VECNUM4        | VECNUM3          | VECNUM2           | VECNUM1         | VECNUM0<br>bit 0 |  |  |  |

|               |                                                                                                                                                                     |                   |                |                  |                   |                 | 511 0            |  |  |  |

| Legend:       |                                                                                                                                                                     |                   |                |                  |                   |                 |                  |  |  |  |

| R = Readable  | e bit                                                                                                                                                               | W = Writable      | bit            | U = Unimpler     | nented bit, read  | l as '0'        |                  |  |  |  |

| -n = Value at | POR                                                                                                                                                                 | '1' = Bit is set  |                | '0' = Bit is cle | ared              | x = Bit is unkr | nown             |  |  |  |

|               |                                                                                                                                                                     |                   |                |                  |                   |                 |                  |  |  |  |

| bit 15        | <b>CPUIRQ:</b> Interrupt Request from Interrupt Controller CPU bit<br>1 = An interrupt request has occurred but has not yet been Acknowledged by the CPU (this will |                   |                |                  |                   |                 |                  |  |  |  |

|               |                                                                                                                                                                     |                   |                |                  |                   | eagea by the    | CPU (this will   |  |  |  |

|               | happen when the CPU priority is higher than the interrupt priority)<br>0 = No interrupt request is left unacknowledged                                              |                   |                |                  |                   |                 |                  |  |  |  |

| bit 14        | Unimplemented: Read as '0'                                                                                                                                          |                   |                |                  |                   |                 |                  |  |  |  |

| bit 13        | VHOLD: Vector Hold bit                                                                                                                                              |                   |                |                  |                   |                 |                  |  |  |  |

|               | Allows Vector Number Capture and Changes which Interrupt is Stored in the VECNUM<6:0> bits:                                                                         |                   |                |                  |                   |                 |                  |  |  |  |

|               | 1 = VECNUM<6:0> will contain the value of the highest priority pending interrupt, instead of the                                                                    |                   |                |                  |                   |                 |                  |  |  |  |

|               | current interrupt<br>0 = VECNUM<6:0> will contain the value of the last Acknowledged interrupt (last interrupt that has                                             |                   |                |                  |                   |                 |                  |  |  |  |

|               |                                                                                                                                                                     |                   |                |                  | ther interrupts a |                 | nupt that has    |  |  |  |

| bit 12        | Unimplemen                                                                                                                                                          | ted: Read as '    | 0'             |                  |                   |                 |                  |  |  |  |

| bit 11-8      | ILR<3:0>: New CPU Interrupt Priority Level bits                                                                                                                     |                   |                |                  |                   |                 |                  |  |  |  |

|               | 1111 = CPU Interrupt Priority Level is 15                                                                                                                           |                   |                |                  |                   |                 |                  |  |  |  |

|               | •                                                                                                                                                                   |                   |                |                  |                   |                 |                  |  |  |  |

|               | •                                                                                                                                                                   |                   |                |                  |                   |                 |                  |  |  |  |

|               | 0001 <b>= CPU</b>                                                                                                                                                   | Interrupt Priorit | ty Level is 1  |                  |                   |                 |                  |  |  |  |

|               | 0000 <b>= CPU</b>                                                                                                                                                   | Interrupt Priori  | ty Level is 0  |                  |                   |                 |                  |  |  |  |

| bit 7         | Unimplemen                                                                                                                                                          | ted: Read as '    | 0'             |                  |                   |                 |                  |  |  |  |

| bit 6-0       | VECNUM<6:0                                                                                                                                                          | 0>: Vector Nun    | nber of Pendin | g Interrupt bits | i                 |                 |                  |  |  |  |

|               | 0111111 <b>= In</b>                                                                                                                                                 | terrupt vector    | pending is Nur | mber 135         |                   |                 |                  |  |  |  |

|               | •                                                                                                                                                                   |                   |                |                  |                   |                 |                  |  |  |  |

|               | •                                                                                                                                                                   |                   |                |                  |                   |                 |                  |  |  |  |

|               |                                                                                                                                                                     | terrupt vector    |                |                  |                   |                 |                  |  |  |  |

|               | 0000000 = In                                                                                                                                                        |                   |                |                  |                   |                 |                  |  |  |  |

## REGISTER 8-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- 2. Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON 4. low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- Set the OSWEN bit in the instruction immediately 5 following the unlock sequence.

- Continue to execute code that is not 6. clock-sensitive (optional).

- Invoke an appropriate amount of software delay 7. (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1 and Example 9-2.

#### EXAMPLE 9-1: ASSEMBLY CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON,#0                            |

#### EXAMPLE 9-2: BASIC 'C' CODE SEQUENCE FOR CLOCK SWITCHING

//Use compiler built-in function to write new clock setting \_\_builtin\_write\_OSCCONH(0x01); //0x01

```

switches to FRCPLL

```

//Use compiler built-in function to set the OSWEN bit. \_\_builtin\_write\_OSCCONL(OSCCONL | 0x01);

//Optional: Wait for clock switch sequence to complete while(OSCCONbits.OSWEN == 1);

#### 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FXXXXX family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIV<3:0> bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the ROSEL bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

| R/W-0         | U-0                                                                                                 | R/W-0                                                         | R/W-0                            | R/W-0                             | R/W-0                | R/W-0                                                  | R/W-0    |  |  |

|---------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|-----------------------------------|----------------------|--------------------------------------------------------|----------|--|--|

| OENSYNC       |                                                                                                     | OCFEN <sup>(1)</sup>                                          | OCEEN <sup>(1)</sup>             | OCDEN <sup>(1)</sup>              | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup>                                   | OCAEN    |  |  |

| bit 15        |                                                                                                     |                                                               |                                  |                                   |                      |                                                        | bit      |  |  |

| R/W-0         | R/W-0                                                                                               | U-0                                                           | R/W-0                            | R/W-0                             | R/W-0                | R/W-0                                                  | R/W-0    |  |  |

| ICGSM1        | ICGSM0                                                                                              | _                                                             | AUXOUT1                          | AUXOUT0                           | ICS2                 | ICS1                                                   | ICS0     |  |  |

| bit 7         |                                                                                                     |                                                               |                                  |                                   |                      | 1                                                      | bit      |  |  |

| Legend:       |                                                                                                     |                                                               |                                  |                                   |                      |                                                        |          |  |  |

| R = Readable  | e bit                                                                                               | W = Writable                                                  | bit                              | U = Unimplem                      | nented bit, read     | 1 as '0'                                               |          |  |  |

| -n = Value at | POR                                                                                                 | '1' = Bit is set                                              |                                  | '0' = Bit is clea                 | ared                 | x = Bit is unkn                                        | own      |  |  |

| bit 15        | 1 = Update b                                                                                        | Dutput Enable S<br>by output enable<br>by output enable       | e bits occurs or                 | n the next Time                   | Base Reset or        | rollover                                               |          |  |  |

| bit 14        | Unimplemen                                                                                          | ted: Read as '                                                | )'                               |                                   |                      |                                                        |          |  |  |

| bit 13-8      | 1 = OCx pin<br>0 = OCx pin                                                                          |                                                               | the CCPx moded by the CCP        | dule and produc                   |                      | compare or PWI<br>e to the port log                    |          |  |  |

| bit 7-6       | ICGSM<1:0>: Input Capture Gating Source Mode Control bits                                           |                                                               |                                  |                                   |                      |                                                        |          |  |  |

|               | 01 = One-Sh<br>00 = Level-Se                                                                        | ot mode: Falling<br>ot mode: Rising                           | edge from gat<br>A high level fr | ting source ena<br>om gating sour | bles future cap      | pture events (IC<br>oture events (IC<br>future capture | DIS = 0) |  |  |

| bit 5         | Unimplemen                                                                                          | ted: Read as '                                                | )'                               |                                   |                      |                                                        |          |  |  |

| bit 4-3       | AUXOUT<1:0                                                                                          | <b>0&gt;:</b> Auxiliary Oເ                                    | tput Signal on                   | Event Selectio                    | n bits               |                                                        |          |  |  |

|               | 10 = Signal c                                                                                       | pture or output<br>output is defined<br>ise rollover eve<br>d | l by module op                   |                                   |                      | )                                                      |          |  |  |

| bit 2-0       | 111 = Unuse<br>110 = CLC2<br>101 = CLC1<br>100 = Unuse<br>011 = Compa<br>010 = Compa<br>001 = Compa | output<br>output                                              |                                  | 3                                 |                      |                                                        |          |  |  |

## REGISTER 13-4: CCPxCON2H: CCPx CONTROL 2 HIGH REGISTERS

## **Note 1:** OCFEN through OCBEN (bits<13:9>) are implemented in MCCPx modules only.

| U-0           | U-0                                                                           | U-0                               | U-0              | U-0                | U-0            | U-0             | U-0              |  |  |  |

|---------------|-------------------------------------------------------------------------------|-----------------------------------|------------------|--------------------|----------------|-----------------|------------------|--|--|--|

|               | —                                                                             | —                                 |                  | —                  |                | _               |                  |  |  |  |

| bit 15        |                                                                               |                                   |                  |                    |                |                 | bit 8            |  |  |  |

|               |                                                                               |                                   |                  |                    |                |                 |                  |  |  |  |

| R/W-0         | R/W-0                                                                         | R-0                               | R-0              | R-0                | R-0            | R-0             | R-0              |  |  |  |

| SMP           | CKE <sup>(1)</sup>                                                            | D/Ā                               | Р                | S                  | R/W            | UA              | BF               |  |  |  |

| bit 7         |                                                                               |                                   |                  |                    |                |                 | bit (            |  |  |  |

| Legend:       |                                                                               |                                   |                  |                    |                |                 |                  |  |  |  |

| R = Readable  | e bit                                                                         | W = Writable I                    | oit              | U = Unimplem       | ented bit. rea | d as '0'        |                  |  |  |  |

| -n = Value at |                                                                               | '1' = Bit is set                  |                  | '0' = Bit is clea  |                | x = Bit is unkr | nown             |  |  |  |

|               |                                                                               |                                   |                  |                    |                |                 |                  |  |  |  |

| bit 15-8      | Unimplemen                                                                    | ted: Read as '0                   | )'               |                    |                |                 |                  |  |  |  |

| bit 7         | SMP: Sample                                                                   | e bit                             |                  |                    |                |                 |                  |  |  |  |

|               | SPI Master mode:                                                              |                                   |                  |                    |                |                 |                  |  |  |  |

|               | 1 = Input data is sampled at the end of data output time                      |                                   |                  |                    |                |                 |                  |  |  |  |

|               | 0 = Input data is sampled at the middle of data output time                   |                                   |                  |                    |                |                 |                  |  |  |  |

|               | <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode. |                                   |                  |                    |                |                 |                  |  |  |  |

| bit 6         | CKE: SPI Clock Select bit <sup>(1)</sup>                                      |                                   |                  |                    |                |                 |                  |  |  |  |

|               | 1 = Transmit o                                                                | occurs on trans                   | ition from acti  | ve to Idle clock s | state          |                 |                  |  |  |  |

|               | 0 = Transmit                                                                  | occurs on trans                   | ition from Idle  | to active clock s  | state          |                 |                  |  |  |  |

| bit 5         | D/A: Data/Ad                                                                  |                                   |                  |                    |                |                 |                  |  |  |  |

|               | Used in I <sup>2</sup> C™                                                     | mode only.                        |                  |                    |                |                 |                  |  |  |  |

| bit 4         | P: Stop bit                                                                   |                                   |                  |                    |                |                 |                  |  |  |  |

|               |                                                                               | node only. This                   | bit is cleared v | when the MSSP:     | x module is di | sabled; SSPEN   | l bit is cleared |  |  |  |

| bit 3         | S: Start bit                                                                  |                                   |                  |                    |                |                 |                  |  |  |  |

|               | Used in I <sup>2</sup> C m                                                    | •                                 |                  |                    |                |                 |                  |  |  |  |

| bit 2         |                                                                               | rite Information                  | bit              |                    |                |                 |                  |  |  |  |

|               | Used in I <sup>2</sup> C m                                                    |                                   |                  |                    |                |                 |                  |  |  |  |

| bit 1         | UA: Update A                                                                  |                                   |                  |                    |                |                 |                  |  |  |  |

|               | Used in I <sup>2</sup> C m                                                    | ,                                 |                  |                    |                |                 |                  |  |  |  |

| bit 0         | BF: Buffer Fu                                                                 |                                   |                  |                    |                |                 |                  |  |  |  |

|               |                                                                               | s complete, SS<br>s not complete, |                  | emntv              |                |                 |                  |  |  |  |

|               |                                                                               | -                                 |                  |                    |                |                 |                  |  |  |  |

|               | plarity of clock s                                                            | tata ia aat by th                 |                  | DUCONIA (A)        |                |                 |                  |  |  |  |

## REGISTER 14-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

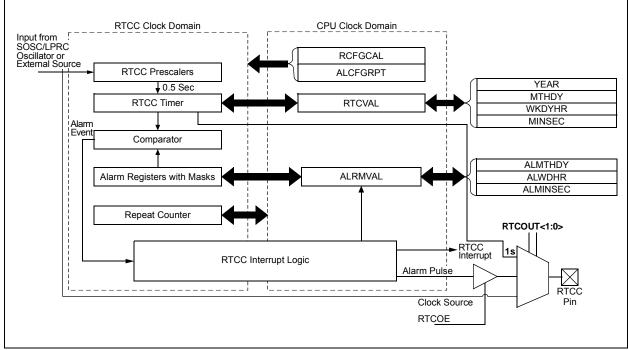

## 16.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Sleep and Retention Sleep modes

- · Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

## 16.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

## FIGURE 16-1: RTCC BLOCK DIAGRAM

| U-0    | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | U-0   | U-0   |

|--------|-------|-------|----------------------|----------------------|-------|-------|-------|

| _      | CSS30 | CSS29 | CSS28                | CSS27                | CSS26 | —     | —     |

| bit 15 |       |       |                      |                      |       |       | bit 8 |

|        |       |       |                      |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| CSS23  | CSS22 | CSS21 | CSS20 <sup>(2)</sup> | CSS19 <sup>(2)</sup> | CSS18 | CSS17 | CSS16 |

| bit 7  |       |       |                      |                      |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

- bit 14-10CSS<30:26>: A/D Input Scan Selection bits1 = Includes the corresponding channel for input scan0 = Skips the channel for input scanbit 9-8Unimplemented: Read as '0'bit 7-0CSS<23:16>: A/D Input Scan Selection bits<sup>(2)</sup>1 = Includes the corresponding channel for input scan0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<20:19> bits are not implemented in 20-pin devices.

## REGISTER 19-9: AD1CSSL: A/D INPUT SCAN SELECT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                 | R/W-0               | R/W-0                      | R/W-0                                  | R/W-0                                             | R/W-0                                                         | R/W-0                                                              |

|-----------------------|---------------------|----------------------------|----------------------------------------|---------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|

| CSS14                 | CSS13               | CSS12                      | CSS11                                  | CSS10                                             | CSS9                                                          | CSS8 <sup>(2,3)</sup>                                              |

|                       |                     |                            |                                        |                                                   |                                                               | bit 8                                                              |

|                       |                     |                            |                                        |                                                   |                                                               |                                                                    |

| R/W-0                 | R/W-0               | R/W-0                      | R/W-0                                  | R/W-0                                             | R/W-0                                                         | R/W-0                                                              |

| CSS6 <sup>(2,3)</sup> | CSS5 <sup>(2)</sup> | CSS4                       | CSS3                                   | CSS2                                              | CSS1                                                          | CSS0                                                               |

|                       |                     |                            |                                        |                                                   |                                                               | bit 0                                                              |

|                       | R/W-0               | CSS14 CSS13<br>R/W-0 R/W-0 | CSS14 CSS13 CSS12<br>R/W-0 R/W-0 R/W-0 | CSS14 CSS13 CSS12 CSS11   R/W-0 R/W-0 R/W-0 R/W-0 | CSS14 CSS13 CSS12 CSS11 CSS10   R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 | CSS14 CSS13 CSS12 CSS11 CSS10 CSS9   R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CSS<15:0>: A/D Input Scan Selection bits<sup>(2,3)</sup>

1 = Includes the corresponding ANx input for scan

- 0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<8:5> bits are not implemented in 20-pin devices.

- 3: The CSS<8:6> bits are not implemented in 28-pin devices.

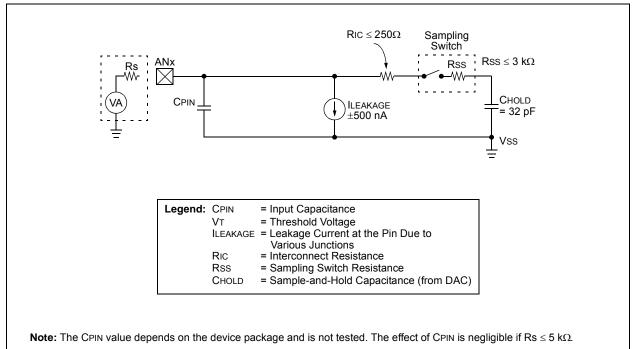

## 19.2 A/D Sampling Requirements

The analog input model of the 12-bit A/D Converter is shown in Figure 19-2. The total sampling time for the A/D is a function of the holding capacitor charge time.

For the A/D Converter to meet its specified accuracy, the Charge Holding Capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The Source Impedance (Rs), the Interconnect Impedance (Rsc) and the Internal Sampling Switch Impedance (Rss) combine to directly affect the time required to charge CHOLD. The combined impedance of the analog sources must, therefore, be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the A/D Converter, the maximum recommended source impedance, Rs, is  $2.5 \text{ k}\Omega$ . After the analog input channel is selected (changed), this sampling function

must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

At least 1 TAD time period should be allowed between conversions for the sample time. For more details, see **Section 27.0 "Electrical Characteristics"**.

## EQUATION 19-1: A/D CONVERSION CLOCK PERIOD

$$TAD = TCY (ADCS + 1)$$

$ADCS = \frac{TAD}{TCY} - 1$

**Note:** Based on Tcy = 2/Fosc; Doze mode and PLL are disabled.

## FIGURE 19-2: 12-BIT A/D CONVERTER ANALOG INPUT MODEL

| AC CHARACTERISTICS |       | Standard Operating Conditions:<br>Operating temperature |     |                    | : 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |                  |                                                     |  |

|--------------------|-------|---------------------------------------------------------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic <sup>(1)</sup>                           | Min | Тур <sup>(2)</sup> | Max                                                                                                                                                          | Units Conditions |                                                     |  |

| OS50               | Fplli | PLL Input Frequency<br>Range                            | 4   | —                  | 8                                                                                                                                                            | MHz              | ECPLL, HSPLL modes,<br>-40°C $\leq$ TA $\leq$ +85°C |  |

| OS51               | Fsys  | PLL Output Frequency<br>Range                           | 16  | —                  | 32                                                                                                                                                           | MHz              | $-40^{\circ}C \le TA \le +85^{\circ}C$              |  |

| OS52               | TLOCK | PLL Start-up Time<br>(Lock Time)                        | -   | 1                  | 2                                                                                                                                                            | ms               |                                                     |  |

| OS53               | DCLK  | CLKO Stability (Jitter)                                 | -2  | 1                  | 2                                                                                                                                                            | %                | Measured over 100 ms period                         |  |

## TABLE 27-21: PLL CLOCK TIMING SPECIFICATIONS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 27-22: INTERNAL RC OSCILLATOR ACCURACY

| AC CHA       | ARACTERISTICS                |     | r <b>d Opera</b><br>ng temp | •   | nditions | tions: 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                                                                                                                                        |  |  |

|--------------|------------------------------|-----|-----------------------------|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Characteristic               | Min | Тур                         | Max | Units    | Conditions                                                                                                                                                                            |                                                                                                                                                                        |  |  |

| F20          | FRC @ 8 MHz <sup>(1)</sup>   | -2  |                             | +2  | %        | +25°C                                                                                                                                                                                 | $\begin{array}{l} 3.0V \leq V \text{DD} \leq 3.6V, \mbox{ F device} \\ 3.2V \leq V \text{DD} \leq 5.5V, \mbox{ FV device} \end{array}$                                 |  |  |

|              |                              | -5  | _                           | +5  | %        | $-40^\circ C \le T A \le +125^\circ C$                                                                                                                                                | $\begin{array}{l} 1.8V \leq VDD \leq 3.6V, \mbox{ F device} \\ 2.0V \leq VDD \leq 5.5V, \mbox{ FV device} \end{array}$                                                 |  |  |

| F21          | LPRC @ 31 kHz <sup>(2)</sup> | -15 |                             | +15 | %        | $-40^{\circ}C \le TA \le +125^{\circ}C$                                                                                                                                               | $\begin{array}{l} 1.8V \leq V\text{DD} \leq 3.6\text{V}, \ \text{F} \ \text{device} \\ 2.0V \leq V\text{DD} \leq 5.5\text{V}, \ \text{FV} \ \text{device} \end{array}$ |  |  |

**Note 1:** The frequency is calibrated at +25°C and 3.3V. The OSCTUN bits can be used to compensate for temperature drift.

2: The change of LPRC frequency as VDD changes.

## TABLE 27-23: INTERNAL RC OSCILLATOR SPECIFICATIONS

| AC CHARACTERISTICS |       | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |     |       |            |  |

|--------------------|-------|-------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.       | Sym   | Characteristic                                        | Min | Тур | Мах | Units | Conditions |  |

|                    | TFRC  | FRC Start-up Time                                     | —   | 5   | _   | μS    |            |  |

|                    | TLPRC | LPRC Start-up Time                                    | —   | 70  | —   | μS    |            |  |

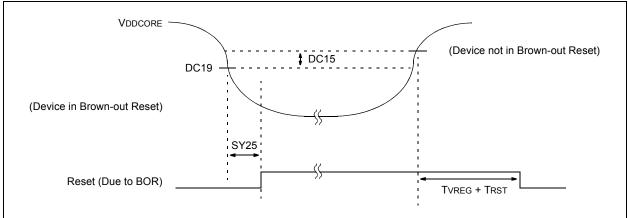

## FIGURE 27-9: BROWN-OUT RESET CHARACTERISTICS

## TABLE 27-25:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                |      | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C f$ |      |       | 8V to 3.6V (PIC24F16KM204)<br>0V to 5.5V (PIC24FV16KM204)<br>$0^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial<br>$0^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |

|--------------------|--------|----------------------------------------------------------------|------|----------------------------------------------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                 | Min. | Typ <sup>(1)</sup>                                             | Max. | Units | Conditions                                                                                                                                                                 |

| SY10               | TmcL   | MCLR Pulse Width (low)                                         | 2    | —                                                              | _    | μs    |                                                                                                                                                                            |

| SY11               | TPWRT  | Power-up Timer Period                                          | 50   | 64                                                             | 90   | ms    |                                                                                                                                                                            |

| SY12               | TPOR   | Power-on Reset Delay                                           | 1    | 5                                                              | 10   | μS    |                                                                                                                                                                            |

| SY13               | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | _    | —                                                              | 100  | ns    |                                                                                                                                                                            |

| SY20               | TWDT   | Watchdog Timer Time-out                                        | 0.85 | 1.0                                                            | 1.15 | ms    | 1.32 prescaler                                                                                                                                                             |

|                    |        | Period                                                         | 3.4  | 4.0                                                            | 4.6  | ms    | 1:128 prescaler                                                                                                                                                            |

| SY25               | TBOR   | Brown-out Reset Pulse<br>Width                                 | 1    | —                                                              | —    | μS    |                                                                                                                                                                            |

| SY35               | TFSCM  | Fail-Safe Clock Monitor<br>Delay                               | —    | 2.0                                                            | 2.3  | μS    |                                                                                                                                                                            |

| SY45               | TRST   | Internal State Reset Time                                      | —    | 5                                                              | _    | μS    |                                                                                                                                                                            |

| SY50               | Tvreg  | On-Chip Voltage Regulator<br>Output Delay                      | —    | 10                                                             | _    | μS    | (Note 2)                                                                                                                                                                   |

| SY55               | TLOCK  | PLL Start-up Time                                              | _    | 100                                                            |      | μs    |                                                                                                                                                                            |

| SY65               | Tost   | Oscillator Start-up Time                                       | —    | 1024                                                           | _    | Tosc  |                                                                                                                                                                            |

| SY71               | Трм    | Program Memory Wake-up<br>Time                                 | —    | 1                                                              | _    | μS    | Sleep wake-up with<br>PMSLP = 0                                                                                                                                            |

| SY72               | Tlvr   | Low-Voltage Regulator<br>Wake-up Time                          | —    | 250                                                            | _    | μS    |                                                                                                                                                                            |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: This applies to PIC24FV16KMXXX devices only.

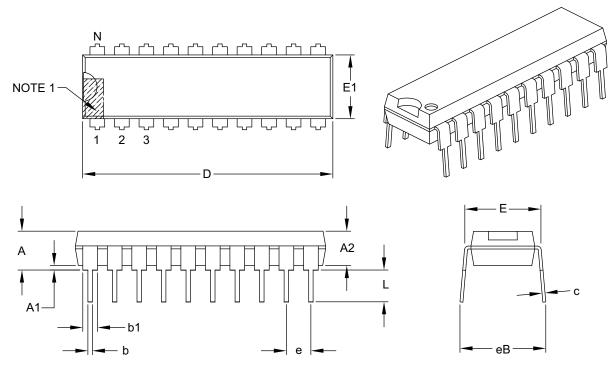

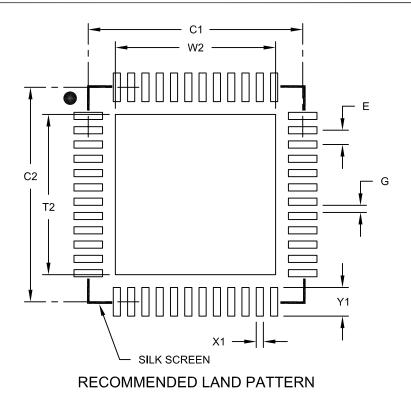

## 28.2 Package Details

The following sections give the technical details of the packages.

## 20-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |      | INCHES   |       |

|----------------------------|------------------|------|----------|-------|

|                            | Dimension Limits | MIN  | NOM      | MAX   |

| Number of Pins             | N                |      | 20       |       |

| Pitch                      | е                |      | .100 BSC |       |

| Top to Seating Plane       | А                | -    | -        | .210  |

| Molded Package Thickness   | A2               | .115 | .130     | .195  |

| Base to Seating Plane      | A1               | .015 | -        | -     |

| Shoulder to Shoulder Width | E                | .300 | .310     | .325  |

| Molded Package Width       | E1               | .240 | .250     | .280  |

| Overall Length             | D                | .980 | 1.030    | 1.060 |

| Tip to Seating Plane       | L                | .115 | .130     | .150  |

| Lead Thickness             | С                | .008 | .010     | .015  |

| Upper Lead Width           | b1               | .045 | .060     | .070  |

| Lower Lead Width           | b                | .014 | .018     | .022  |

| Overall Row Spacing §      | eB               | _    | -        | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

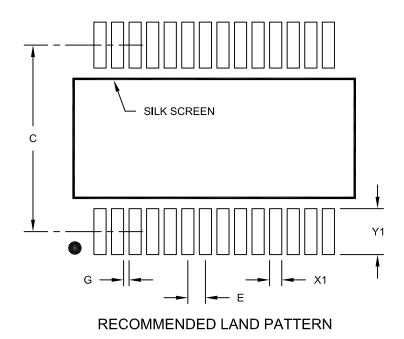

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      |          | S    |

|--------------------------|------------------|------|----------|------|

| Dimensio                 | Dimension Limits |      | NOM      | MAX  |

| Contact Pitch            | E                |      | 0.65 BSC |      |

| Contact Pad Spacing      | С                |      | 7.20     |      |