Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betano                     |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

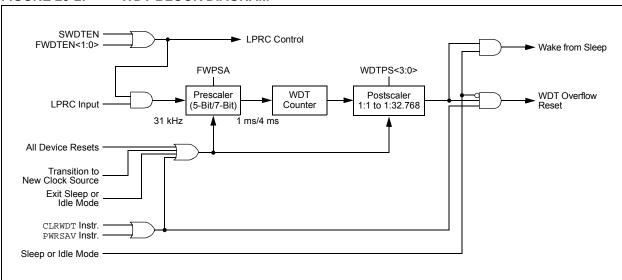

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km204t-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| TABLE 1-3: DEVICE FEATURES FOR                      | DR THE PIC24FV16KM204 FAMILY                                                                                                                        |                    |                               |                         |  |  |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|-------------------------|--|--|--|--|--|--|--|

| Features                                            | PIC24FV16KM204                                                                                                                                      | PIC24FV08KM204     | PIC24FV16KM202                | PIC24FV08KM202          |  |  |  |  |  |  |  |

| Operating Frequency                                 |                                                                                                                                                     | DC-3               | 2 MHz                         |                         |  |  |  |  |  |  |  |

| Program Memory (bytes)                              | 16K                                                                                                                                                 | 8K                 | 16K                           | 8K                      |  |  |  |  |  |  |  |

| Program Memory (instructions)                       | 5632                                                                                                                                                | 2816               | 5632                          | 2816                    |  |  |  |  |  |  |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 20                 | )48                           | I                       |  |  |  |  |  |  |  |

| Data EEPROM Memory (bytes)                          |                                                                                                                                                     | 5                  | 12                            |                         |  |  |  |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)          |                                                                                                                                                     | 40 (               | 36/4)                         |                         |  |  |  |  |  |  |  |

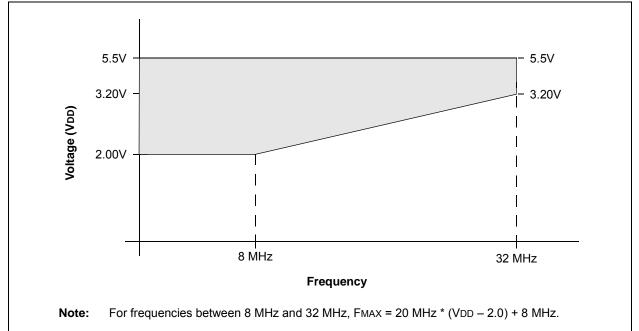

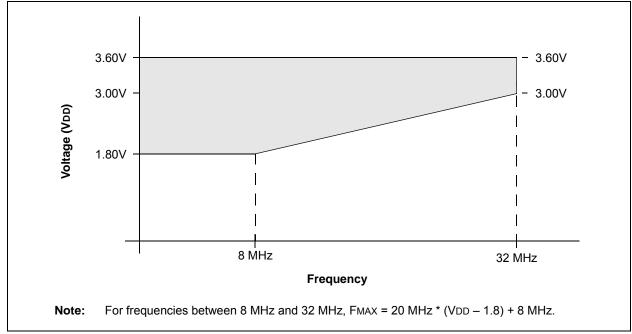

| Voltage Range                                       |                                                                                                                                                     | 2.0-               | -5.5V                         |                         |  |  |  |  |  |  |  |

| I/O Ports                                           | PORTA<1<br>PORTB<<br>PORTC                                                                                                                          | :15:0>             |                               | RTA<7,5:0><br>RTB<15:0> |  |  |  |  |  |  |  |

| Total I/O Pins                                      | 37                                                                                                                                                  |                    |                               | 23                      |  |  |  |  |  |  |  |

| Timers                                              | (One 16-bit timer, f                                                                                                                                |                    | 11<br>Ps with up to tv        | vo 16/32 timers each)   |  |  |  |  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                                                                                                                                                     |                    | 3<br>2                        |                         |  |  |  |  |  |  |  |

| Serial Communications<br>MSSP<br>UART               | 2 2                                                                                                                                                 |                    |                               |                         |  |  |  |  |  |  |  |

| Input Change Notification Interrupt                 | 36                                                                                                                                                  |                    |                               | 22                      |  |  |  |  |  |  |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                                                                                                                                  |                    |                               | 19                      |  |  |  |  |  |  |  |

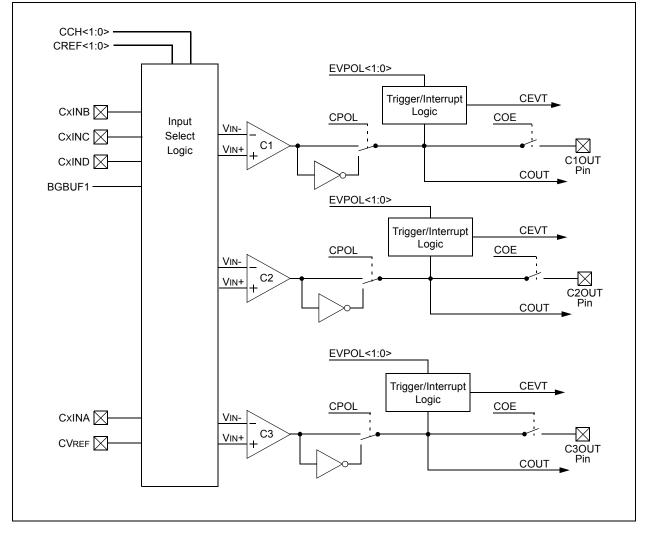

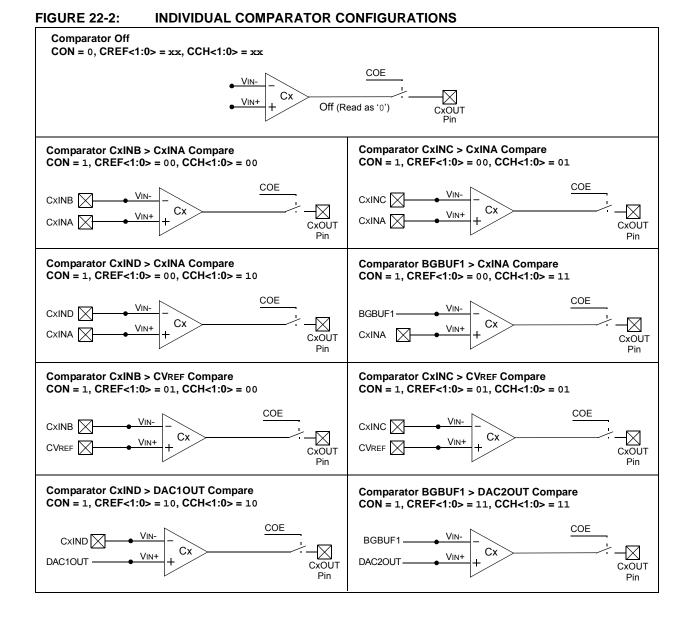

| Analog Comparators                                  |                                                                                                                                                     |                    | 3                             |                         |  |  |  |  |  |  |  |

| 8-Bit Digital-to-Analog Converters                  |                                                                                                                                                     |                    | 2                             |                         |  |  |  |  |  |  |  |

| Operational Amplifiers                              |                                                                                                                                                     |                    | 2                             |                         |  |  |  |  |  |  |  |

| Charge Time Measurement Unit (CTMU)                 |                                                                                                                                                     | Y                  | <i>ï</i> es                   |                         |  |  |  |  |  |  |  |

| Real-Time Clock and Calendar (RTCC)                 |                                                                                                                                                     | Y                  | 'es                           |                         |  |  |  |  |  |  |  |

| Configurable Logic Cell (CLC)                       |                                                                                                                                                     |                    | 2                             |                         |  |  |  |  |  |  |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                    |                               |                         |  |  |  |  |  |  |  |

| Instruction Set                                     | 76 Base Inst                                                                                                                                        | ructions, Multiple | e Addressing N                | Iode Variations         |  |  |  |  |  |  |  |

| Packages                                            | 44-Pin QFI<br>48-Pin U                                                                                                                              |                    | 28-Pin<br>SPDIP/SSOP/SOIC/QFN |                         |  |  |  |  |  |  |  |

#### TABLE 1-3: DEVICE FEATURES FOR THE PIC24FV16KM204 FAMILY

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART2 16x Baud Rate Clock Output               |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

FIGURE 2-1:

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

## 2.1 Basic Connection Requirements

Getting started with the PIC24FV16KM204 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pins (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

#### **MINIMUM CONNECTIONS** C2<sup>(2)</sup> Vdd Vss ₹R1 VDD R2 MCLR VCAP (1) C1 PIC24FV16KM204 Vdd Vss C6<sup>(2)</sup> C3(2) VDD Vss AVDD AVSS /SS 20/

RECOMMENDED

#### Key (all values are recommendations):

C5<sup>(2)</sup>

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic

C7: 10 µF, 16V tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for an explanation of VCAP pin connections.

- 2: The example shown is for a PIC24F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

C4(2)

|  | REGISTER 3-2: | CORCON: CPU CONTROL REGISTER |

|--|---------------|------------------------------|

|--|---------------|------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   |     | —   |     | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   |     | —   | IPL3 <sup>(1)</sup> | PSV   | —   | —     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settable   | e/Clearable bit    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in Data Space                                                                                    |

|          | 0 = Program space is not visible in Data Space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

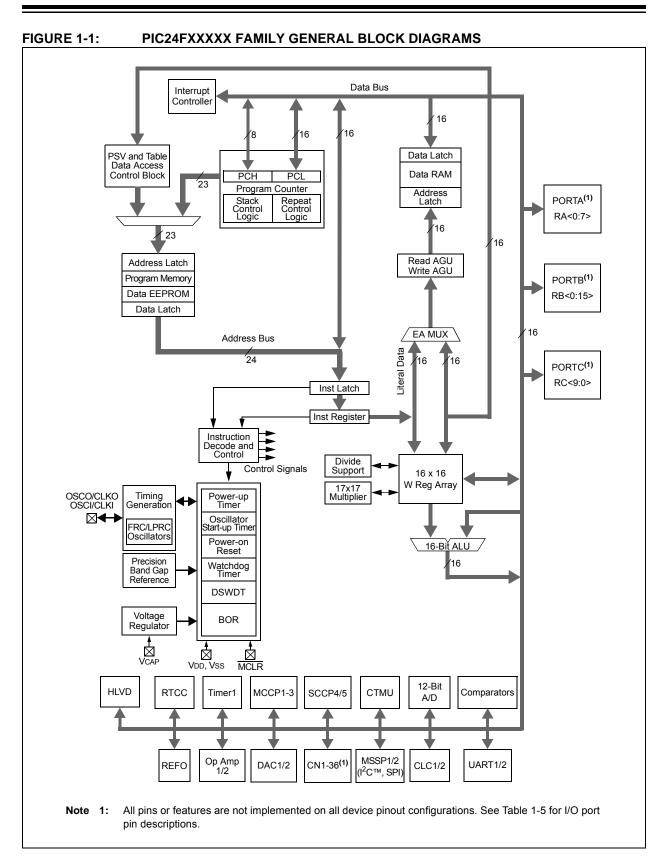

### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### TABLE 4-11: SCCP4 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14                                                                                     | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8       | Bit 7        | Bit 6       | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|---------|--------------------------------------------------------------------------------------------|---------|--------|---------|---------|-----------|-------------|--------------|-------------|--------|---------|---------|---------|--------|--------|---------------|

| CCP4CON1L <sup>(1)</sup> | 1ACh  | CCPON   | _                                                                                          | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0     | TMRPS1       | TMRPS0      | T32    | CCSEL   | MOD3    | MOD2    | MOD1   | MOD0   | 0000          |

| CCP4CON1H(1)             | 1AEh  | OPSSRC  | OPSSRC RTRGEN IOPS3 IOPS2 IOPS1 IOPS0 TRIGEN ONESHOT ALTSYNC SYNC4 SYNC3 SYNC2 SYNC1 SYNC0 |         |        |         |         |           |             |              |             |        |         |         | 0000    |        |        |               |

| CCP4CON2L <sup>(1)</sup> | 1B0h  | PWMRSEN | ASDGM                                                                                      | _       | SSDG   | _       | _       | _         | _           | ASDG7        | ASDG6       | ASDG5  | ASDG4   | ASDG3   | ASDG2   | ASDG1  | ASDG0  | 0000          |

| CCP4CON2H <sup>(1)</sup> | 1B2h  | OENSYNC | _                                                                                          | _       | _      | _       | _       | _         | OCAEN       | ICGSM1       | ICGSM0      | _      | AUXOUT1 | AUXOUT0 | ICSEL2  | ICSEL1 | ICSEL0 | 0100          |

| CCP4CON3H <sup>(1)</sup> | 1B6h  | OETRIG  | OSCNT2                                                                                     | OSCNT1  | OSCNT0 | _       | _       | _         | —           | _            | _           | POLACE | _       | PSSACE1 | PSSACE0 | _      | —      | 0000          |

| CCP4STATL <sup>(1)</sup> | 1B8h  | _       | _                                                                                          | _       |        | -       | _       | _         | _           | CCPTRIG      | TRSET       | TRCLR  | ASEVT   | SCEVT   | ICDIS   | ICOV   | ICBNE  | 0000          |

| CCP4TMRL <sup>(1)</sup>  | 1BCh  |         |                                                                                            |         |        |         |         | SCCP4     | 1 Time Base | Register Lo  | ow Word     |        |         |         |         |        |        | 0000          |

| CCP4TMRH <sup>(1)</sup>  | 1BEh  |         |                                                                                            |         |        |         |         | SCCP4     | Time Base   | Register Hi  | gh Word     |        |         |         |         |        |        | 0000          |

| CCP4PRL <sup>(1)</sup>   | 1C0h  |         |                                                                                            |         |        |         |         | SCCP4 Tir | ne Base Pe  | riod Registe | er Low Word |        |         |         |         |        |        | FFFF          |

| CCP4PRH <sup>(1)</sup>   | 1C2h  |         |                                                                                            |         |        |         |         | SCCP4 Tir | ne Base Pe  | riod Registe | r High Word |        |         |         |         |        |        | FFFF          |

| CCP4RAL <sup>(1)</sup>   | 1C4h  |         |                                                                                            |         |        |         |         | Out       | put Compar  | e 4 Data Wo  | ord A       |        |         |         |         |        |        | 0000          |

| CCP4RBL <sup>(1)</sup>   | 1C8h  |         |                                                                                            |         |        |         |         | Out       | put Compar  | e 4 Data Wo  | ord B       |        |         |         |         |        |        | 0000          |

| CCP4BUFL <sup>(1)</sup>  | 1CCh  |         | Input Capture 4 Data Buffer Low Word                                                       |         |        |         |         |           |             |              |             |        |         |         |         | 0000   |        |               |

| CCP4BUFH <sup>(1)</sup>  | 1CEh  |         | Input Capture 4 Data Buffer High Word                                                      |         |        |         |         |           |             |              |             |        |         |         |         | 0000   |        |               |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** These registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-26: CTMU REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|---------|---------|---------------|

| CTMUCON1L | 35Ah  | CTMUEN  | _       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1   | IRNG0   | 0000          |

| CTMUCON1H | 35Ch  | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _       | _       | 0000          |

| CTMUCON2L | 35Eh  | —       | _       | —        | _        |          |          | —        | -        | -       | -       | _        | IRSTEN   |          | DISCHS2  | DISCHS1 | DISCHS0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-27: ANSEL REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6    | Bit 5                | Bit 4    | Bit 3                | Bit 2                  | Bit 1                  | Bit 0                  | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|----------|----------------------|----------|----------------------|------------------------|------------------------|------------------------|---------------------|

| ANSA         | 4E0h  | —      | _      | —      | —      | —      | —      | —     | _     | _     | —        | —                    | ANSA4(2) | ANSA3                | ANSA2                  | ANSA1                  | ANSA0                  | 001F <sup>(1)</sup> |

| ANSB         | 4E2h  | ANSB15 | ANSB14 | ANSB13 | ANSB12 | _      | _      | ANSB9 | ANSB8 | ANSB7 | ANSB6(2) | ANSB5 <sup>(2)</sup> | ANSB4    | ANSB3 <sup>(2)</sup> | ANSB2                  | ANSB1                  | ANSB0                  | <sub>F3FF</sub> (1) |

| ANSC         | 4E4h  | _      |        | —      | _      | —      | —      | _     |       |       | _        |                      | _        | _                    | ANSC2 <sup>(2,3)</sup> | ANSC1 <sup>(2,3)</sup> | ANSC0 <sup>(2,3)</sup> | 0007 <b>(1)</b>     |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

#### TABLE 4-28: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                                                 | Bit 13  | Bit 12  | Bit 11  | Bit 10      | Bit 9          | Bit 8          | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets       |

|-----------|-------|--------|--------------------------------------------------------|---------|---------|---------|-------------|----------------|----------------|---------|--------|-------|-------|-------|-------|-------|-------|---------------------|

| ALRMVAL   | 620h  |        | Alarm Value High Register Window Based on APTR<1:0> xx |         |         |         |             |                |                |         |        |       |       | XXXX  |       |       |       |                     |

| ALCFGRPT  | 622h  | ALRMEN | CHIME                                                  | AMASK3  | AMASK2  | AMASK1  | AMASK0      | ALRMPTR1       | ALRMPTR0       | ARPT7   | ARPT6  | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | <sub>0000</sub> (1) |

| RTCVAL    | 624h  |        |                                                        |         |         | R       | TCC Value H | igh Register W | /indow Based o | n RTCPT | R<1:0> |       |       |       |       |       |       | xxxx                |

| RCFGCAL   | 626h  | RTCEN  | _                                                      | RTCWREN | RTCSYNC | HALFSEC | RTCOE       | RTCPTR1        | RTCPTR0        | CAL7    | CAL6   | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000 <b>(1)</b>     |

| RTCPWC    | 628h  | PWCEN  | PWCPOL                                                 | PWCCPRE | PWCSPRE | RTCCLK1 | RTCCLK0     | RTCOUT1        | RTCOUT0        | _       | _      | _     | _     | _     | -     | _     | _     | <sub>0000</sub> (1) |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** Values are reset only on a VDD POR event.

#### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts<br>for next 5 instructions |

|------|-------------|---|-------------------------------------------------|

| MOV  | #0x55, W0   |   |                                                 |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                                |

| MOV  | #0xAA, W1   | ; |                                                 |

| MOV  | W1, NVMKEY  | ; | Write the AA key                                |

| BSET | NVMCON, #WR | ; | Start the erase sequence                        |

| NOP  |             | ; | 2 NOPs required after setting WR                |

| NOP  |             | ; |                                                 |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed           |

| BRA  | \$-2        | ; |                                                 |

|      |             |   |                                                 |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

### 6.3 NVM Address Register

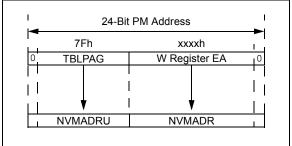

As with Flash program memory, the NVM Address registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and select the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", are unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

### 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

Note 1: Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.

2: The XC16 C compiler includes library procedures to automatically perform the Table Read and Table Write operations, manage the Table Pointer and write buffers, and unlock and initiate memory write sequences. This eliminates the need to create assembler macros or time critical routines in C for each application.

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the XC16 compiler libraries.

#### 10.5 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption. Meanwhile, the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

#### 10.6 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMDx Control registers.

Both bits have similar functions in enabling or disabling its associated module. Setting the PMDx bits for a module, disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect, and read values will be invalid. Many peripheral modules have a corresponding PMDx bit.

In contrast, disabling a module by clearing its XXXEN bit, disables its functionality, but leaves its registers available to be read and written to. Power consumption is reduced, but not by as much as when the PMDx bits are used. Most peripheral modules have an enable bit; exceptions include capture, compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature disables the module while in Idle mode, allowing further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

## REGISTER 14-3: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     |     | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:                            |                                                                                                                    |                                                                 |                                                                                    |                                                 |  |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| R = Read                           | lable bit                                                                                                          | W = Writable bit                                                | U = Unimplemented bit                                                              | , read as '0'                                   |  |  |  |  |

| -n = Value at POR (1' = Bit is set |                                                                                                                    | '1' = Bit is set                                                | '0' = Bit is cleared                                                               | x = Bit is unknown                              |  |  |  |  |

|                                    |                                                                                                                    |                                                                 |                                                                                    |                                                 |  |  |  |  |

| bit 15-8                           | Unimple                                                                                                            | mented: Read as '0'                                             |                                                                                    |                                                 |  |  |  |  |

| bit 7                              | WCOL: \                                                                                                            | Vrite Collision Detect bit                                      |                                                                                    |                                                 |  |  |  |  |

|                                    |                                                                                                                    | C C                                                             | while it is still transmitting the                                                 | previous word (must be cleared in               |  |  |  |  |

|                                    | softw<br>0 = No c                                                                                                  | ,                                                               |                                                                                    |                                                 |  |  |  |  |

| bit 6                              |                                                                                                                    |                                                                 | Port Receive Overflow Indicate                                                     | or hit(1)                                       |  |  |  |  |

| Sit 0                              | SPI Slav                                                                                                           |                                                                 |                                                                                    |                                                 |  |  |  |  |

|                                    |                                                                                                                    |                                                                 | SPxBUF register is still holding                                                   | g the previous data. In case of over-           |  |  |  |  |

|                                    |                                                                                                                    |                                                                 |                                                                                    | ave mode. The user must read the                |  |  |  |  |

|                                    | SSPxBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software<br>0 = No overflow |                                                                 |                                                                                    |                                                 |  |  |  |  |

| bit 5                              |                                                                                                                    | SSPEN: Master Synchronous Serial Port Enable bit <sup>(2)</sup> |                                                                                    |                                                 |  |  |  |  |

| DIL 5                              |                                                                                                                    | •                                                               | ures SCKx, SDOx, SDIx and                                                          | SSx as serial port pins                         |  |  |  |  |

|                                    |                                                                                                                    |                                                                 | jures these pins as I/O port pi                                                    | · ·                                             |  |  |  |  |

| bit 4                              | CKP: Clo                                                                                                           | ock Polarity Select bit                                         |                                                                                    |                                                 |  |  |  |  |

|                                    | 1 = Idle s                                                                                                         | state for clock is a high level                                 |                                                                                    |                                                 |  |  |  |  |

|                                    |                                                                                                                    | state for clock is a low level                                  |                                                                                    |                                                 |  |  |  |  |

| bit 3-0                            | SSPM<3                                                                                                             | :0>: Master Synchronous Se                                      | rial Port Mode Select bits <sup>(3)</sup>                                          |                                                 |  |  |  |  |

|                                    |                                                                                                                    | SPI Master mode, Clock = Fo                                     |                                                                                    | $\frac{1}{2}$                                   |  |  |  |  |

|                                    |                                                                                                                    |                                                                 | x pin; <u>SSx</u> pin control is disable<br>(x pin; <u>SSx</u> pin control is enab | led, $\overline{SSx}$ can be used as an I/O pin |  |  |  |  |

|                                    |                                                                                                                    | SPI Master mode, Clock = TM                                     |                                                                                    |                                                 |  |  |  |  |

|                                    |                                                                                                                    | SPI Master mode, Clock = Fo                                     |                                                                                    |                                                 |  |  |  |  |

|                                    |                                                                                                                    | SPI Master mode, Clock = Fo                                     |                                                                                    |                                                 |  |  |  |  |

|                                    | 0000 = 5                                                                                                           | SPI Master mode, Clock = Fo                                     | SC/Z                                                                               |                                                 |  |  |  |  |

| Note 1:                            |                                                                                                                    |                                                                 | t since each new reception (a                                                      | nd transmission) is initiated by                |  |  |  |  |

| writing to the SSPxBUF register.   |                                                                                                                    |                                                                 |                                                                                    |                                                 |  |  |  |  |

- 2: When enabled, these pins must be properly configured as inputs or outputs.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

#### REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER

| R/W-0                   | R/W-0                                                                                                                                    | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|------------------|------------------|-----------------|-------|--|--|

| G4D4T                   | G4D4N                                                                                                                                    | G4D3T                            | G4D3N            | G4D2T            | G4D2N            | G4D1T           | G4D1N |  |  |

| bit 15                  |                                                                                                                                          |                                  |                  |                  |                  |                 | bit 8 |  |  |

|                         |                                                                                                                                          |                                  |                  |                  |                  |                 |       |  |  |

| R/W-0                   | R/W-0                                                                                                                                    | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| G3D4T                   | G3D4N                                                                                                                                    | G3D3T                            | G3D3N            | G3D2T            | G3D2N            | G3D1T           | G3D1N |  |  |

| bit 7                   |                                                                                                                                          |                                  |                  |                  |                  |                 | bit 0 |  |  |

| Logondi                 |                                                                                                                                          |                                  |                  |                  |                  |                 |       |  |  |

| Legend:<br>R = Readable | , bit                                                                                                                                    | W = Writable                     | oit              | LI – Unimplor    | nonted bit read  | d ac '0'        |       |  |  |

| -n = Value at           |                                                                                                                                          | '1' = Bit is set                 | JIL              | '0' = Bit is cle | nented bit, read | x = Bit is unkr |       |  |  |

|                         | FUK                                                                                                                                      |                                  |                  |                  | aleu             |                 | IOWIT |  |  |

| bit 15                  | G4D4T: Gate                                                                                                                              | 4 Data Source                    | 4 True Enable    | e bit            |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 4 inver                   |                  |                  | e 4              |                 |       |  |  |

|                         |                                                                                                                                          | Source 4 inver                   |                  |                  |                  |                 |       |  |  |

| bit 14                  | G4D4N: Gate                                                                                                                              | e 4 Data Source                  | 4 Negated Er     | nable bit        |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 4 inver                   |                  |                  |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 4 inver                   | •                |                  | e 4              |                 |       |  |  |

| bit 13                  |                                                                                                                                          | 4 Data Source                    |                  |                  |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 3 inver<br>Source 3 inver |                  |                  |                  |                 |       |  |  |

| bit 12                  | <ul> <li>0 = The Data Source 3 inverted signal is disabled for Gate 4</li> <li>G4D3N: Gate 4 Data Source 3 Negated Enable bit</li> </ul> |                                  |                  |                  |                  |                 |       |  |  |

|                         | 1 = The Data Source 3 inverted signal is enabled for Gate 4                                                                              |                                  |                  |                  |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 3 inver                   | •                |                  |                  |                 |       |  |  |

| bit 11                  | G4D2T: Gate                                                                                                                              | 4 Data Source                    | 2 True Enable    | e bit            |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 2 inver                   |                  |                  |                  |                 |       |  |  |

| bit 10                  |                                                                                                                                          | Source 2 inver<br>4 Data Source  | -                |                  | 3 4              |                 |       |  |  |

|                         |                                                                                                                                          | Source 2 inver                   | -                |                  | A                |                 |       |  |  |

|                         |                                                                                                                                          | Source 2 inver                   |                  |                  |                  |                 |       |  |  |

| bit 9                   | G4D1T: Gate                                                                                                                              | 4 Data Source                    | 1 True Enable    | e bit            |                  |                 |       |  |  |

|                         | 1 = The Data                                                                                                                             | Source 1 inver                   | ted signal is ei | nabled for Gate  | e 4              |                 |       |  |  |

|                         | 0 = The Data                                                                                                                             | Source 1 inver                   | ted signal is di | sabled for Gate  | e 4              |                 |       |  |  |

| bit 8                   |                                                                                                                                          | e 4 Data Source                  | -                |                  |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 1 inver                   |                  |                  |                  |                 |       |  |  |

| hit 7                   |                                                                                                                                          | Source 1 inver                   | -                |                  | 3 4              |                 |       |  |  |

| bit 7                   | <b>G3D4T:</b> Gate 3 Data Source 4 True Enable bit<br>1 = The Data Source 4 inverted signal is enabled for Gate 3                        |                                  |                  |                  |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 4 inver                   |                  |                  |                  |                 |       |  |  |

| bit 6                   |                                                                                                                                          | e 3 Data Source                  | -                |                  |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 4 inver                   | -                |                  | e 3              |                 |       |  |  |

|                         | 0 = The Data                                                                                                                             | Source 4 inver                   | ted signal is di | sabled for Gate  | e 3              |                 |       |  |  |

| bit 5                   | G3D3T: Gate                                                                                                                              | 3 Data Source                    | 3 True Enable    | e bit            |                  |                 |       |  |  |

|                         |                                                                                                                                          | Source 3 inver                   |                  |                  |                  |                 |       |  |  |

| b:t 4                   |                                                                                                                                          | Source 3 inver                   | -                |                  | e 3              |                 |       |  |  |

| bit 4                   | G3D3N: Gate                                                                                                                              | e 3 Data Source                  | s Negated Er     | nable bit        |                  |                 |       |  |  |

|                         | 1 - The Det-                                                                                                                             | Source 3 inver                   | tod olanal in -  | ablad for Ort-   |                  |                 |       |  |  |

| R/W-0         | R/W-0                                                                                               | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| CH0NB2        | CH0NB1                                                                                              | CH0NB0                               | CH0SB4         | CH0SB3            | CH0SB2           | CH0SB1          | CH0SB0 |  |  |  |  |

| bit 15        |                                                                                                     |                                      |                |                   |                  |                 | bit    |  |  |  |  |

| R/W-0         | R/W-0                                                                                               | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| CH0NA2        | CH0NA1                                                                                              | CHONAO                               | CH0SA4         | CH0SA3            | CH0SA2           | CH0SA1          | CH0SA0 |  |  |  |  |

| bit 7         |                                                                                                     |                                      |                |                   |                  |                 | bit    |  |  |  |  |

| Legend:       |                                                                                                     |                                      |                |                   |                  |                 |        |  |  |  |  |

| R = Readabl   | le bit                                                                                              | W = Writable                         | bit            | U = Unimplem      | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value at | POR                                                                                                 | '1' = Bit is set                     |                | '0' = Bit is clea |                  | x = Bit is unkr | iown   |  |  |  |  |

| L: 45 40      |                                                                                                     | · Comple D Ch                        | annal O Nagati | ve less to Celest | hite             |                 |        |  |  |  |  |

| bit 15-13     | 111 = AN6 <sup>(1)</sup>                                                                            | •                                    | annei 0 Negati | ve Input Select   | DIIS             |                 |        |  |  |  |  |

|               | $111 = AN6^{(1)}$<br>$110 = AN5^{(2)}$                                                              |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 101 = AN3                                                                                           |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 101 - AN4<br>100 = AN3                                                                              |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 011 = AN2                                                                                           |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 010 = AN1                                                                                           |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 001 = ANO                                                                                           |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 000 = AVss                                                                                          |                                      |                |                   |                  |                 |        |  |  |  |  |

| bit 12-8      | CH0SB<4:0>: S/H Amplifier Positive Input Select for MUX B Multiplexer Setting bits                  |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 11111 = Unimplemented, do not use                                                                   |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 11110 = $AVDD^{(3)}$                                                                                |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 11101 = AVss <sup>(3)</sup>                                                                         |                                      |                |                   |                  |                 |        |  |  |  |  |

|               | 11100 = Upper guardband rail (0.785 * VDD)                                                          |                                      |                |                   |                  |                 |        |  |  |  |  |