Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

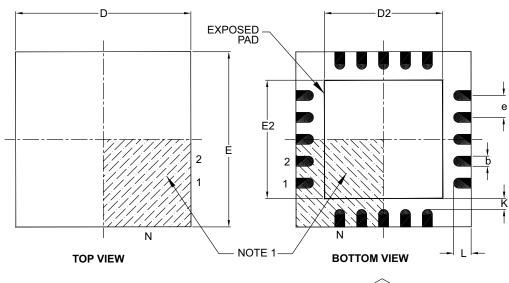

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08km204t-i-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART2 16x Baud Rate Clock Output               |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

NOTES:

# 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

# 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

# TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

# 4.0 MEMORY ORGANIZATION

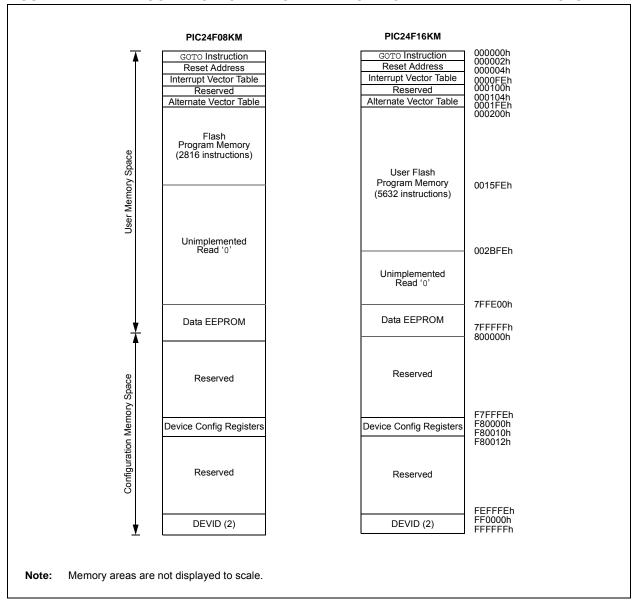

As with Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and busing. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

# 4.1 **Program Address Space**

The program address memory space of the PIC24F devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or Data Space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

The user access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FV16KM204 family of devices are displayed in Figure 4-1.

# FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FXXXXX FAMILY DEVICES

# TABLE 4-3:CPU CORE REGISTERS MAP

| TABLE        | 4-3.  | UP     |        | KE KEGI   | STERS     |           |           |          |          |             |          |          |          |          |          |          |          |               |

|--------------|-------|--------|--------|-----------|-----------|-----------|-----------|----------|----------|-------------|----------|----------|----------|----------|----------|----------|----------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9    | Bit 8    | Bit 7       | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| WREG0        | 0h    |        |        |           |           |           |           |          | W        | /REG0       |          |          |          |          |          |          |          | 0000          |

| WREG1        | 2h    |        |        |           |           |           |           |          | W        | /REG1       |          |          |          |          |          |          |          | 0000          |

| WREG2        | 4h    |        |        |           |           |           |           |          | W        | /REG2       |          |          |          |          |          |          |          | 0000          |

| WREG3        | 6h    |        |        |           |           |           |           |          | W        | /REG3       |          |          |          |          |          |          |          | 0000          |

| WREG4        | 8h    |        |        |           |           |           |           |          | W        | /REG4       |          |          |          |          |          |          |          | 0000          |

| WREG5        | Ah    |        |        |           |           |           |           |          | W        | /REG5       |          |          |          |          |          |          |          | 0000          |

| WREG6        | Ch    |        |        |           |           |           |           |          | W        | /REG6       |          |          |          |          |          |          |          | 0000          |

| WREG7        | Eh    |        |        |           |           |           |           |          | W        | /REG7       |          |          |          |          |          |          |          | 0000          |

| WREG8        | 10h   |        |        |           |           |           |           |          | W        | /REG8       |          |          |          |          |          |          |          | 0000          |

| WREG9        | 12h   |        |        |           |           |           |           |          | W        | /REG9       |          |          |          |          |          |          |          | 0000          |

| WREG10       | 14h   |        |        |           |           |           |           |          | W        | REG10       |          |          |          |          |          |          |          | 0000          |

| WREG11       | 16h   |        |        |           |           |           |           |          | W        | REG11       |          |          |          |          |          |          |          | 0000          |

| WREG12       | 18h   |        |        |           |           |           |           |          | W        | REG12       |          |          |          |          |          |          |          | 0000          |

| WREG13       | 1Ah   |        |        |           |           |           |           |          | W        | REG13       |          |          |          |          |          |          |          | 0000          |

| WREG14       | 1Ch   |        |        |           |           |           |           |          | W        | REG14       |          |          |          |          |          |          |          | 0000          |

| WREG15       | 1Eh   |        |        |           |           |           |           |          | W        | REG15       |          |          |          |          |          |          |          | 0800          |

| SPLIM        | 20h   |        |        |           |           |           |           |          | SPLI     | V Register  |          |          |          |          |          |          |          | xxxx          |

| PCL          | 2Eh   |        |        |           |           |           |           |          | PCL      | Register    |          |          |          |          |          |          |          | 0000          |

| PCH          | 30h   | _      |        |           |           | —         | —         |          | —        | PCH7        | PCH6     | PCH5     | PCH4     | PCH3     | PCH2     | PCH1     | PCH0     | 0000          |

| TBLPAG       | 32h   | _      |        |           |           | —         | —         |          | —        | TBLPAG7     | TBLPAG6  | TBLPAG5  | TBLPAG4  | TBLPAG3  | TBLPAG2  | TBLPAG1  | TBLPAG0  | 0000          |

| PSVPAG       | 34h   | _      |        |           |           | -         | —         | _        | _        | PSVPAG7     | PSVPAG6  | PSVPAG5  | PSVPAG4  | PSVPAG3  | PSVPAG2  | PSVPAG1  | PSVPAG0  | 0000          |

| RCOUNT       | 36h   |        |        |           |           |           |           |          | RCOU     | NT Register |          |          |          |          |          |          |          | xxxx          |

| SR           | 42h   | _      |        |           |           | -         | —         | _        | DC       | IPL2        | IPL1     | IPL0     | RA       | Ν        | OV       | Z        | С        | 0000          |

| CORCON       | 44h   | _      |        | _         |           | -         | —         | _        | —        | —           | —        | _        | _        | IPL3     | PSV      | _        | —        | 0000          |

| DISICNT      | 52h   | _      | -      | DISICNT13 | DISICNT12 | DISICNT11 | DISICNT10 | DISICNT9 | DISICNT8 | DISICNT7    | DISICNT6 | DISICNT5 | DISICNT4 | DISICNT3 | DISICNT2 | DISICNT1 | DISICNT0 | xxxx          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-26: CTMU REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|---------|---------|---------------|

| CTMUCON1L | 35Ah  | CTMUEN  | _       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1   | IRNG0   | 0000          |

| CTMUCON1H | 35Ch  | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _       | _       | 0000          |

| CTMUCON2L | 35Eh  | —       | _       | —        | _        |          |          | —        | -        | -       | -       | _        | IRSTEN   |          | DISCHS2  | DISCHS1 | DISCHS0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-27: ANSEL REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6    | Bit 5                | Bit 4    | Bit 3                | Bit 2                  | Bit 1                  | Bit 0                  | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|----------|----------------------|----------|----------------------|------------------------|------------------------|------------------------|---------------------|

| ANSA         | 4E0h  | —      | _      | —      | —      | —      | —      | —     | _     | _     | —        | —                    | ANSA4(2) | ANSA3                | ANSA2                  | ANSA1                  | ANSA0                  | 001F <sup>(1)</sup> |

| ANSB         | 4E2h  | ANSB15 | ANSB14 | ANSB13 | ANSB12 | _      | _      | ANSB9 | ANSB8 | ANSB7 | ANSB6(2) | ANSB5 <sup>(2)</sup> | ANSB4    | ANSB3 <sup>(2)</sup> | ANSB2                  | ANSB1                  | ANSB0                  | <sub>F3FF</sub> (1) |

| ANSC         | 4E4h  |        |        | —      | _      | —      | —      | _     |       |       | _        |                      | _        | _                    | ANSC2 <sup>(2,3)</sup> | ANSC1 <sup>(2,3)</sup> | ANSC0 <sup>(2,3)</sup> | 0007 <b>(1)</b>     |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

# TABLE 4-28: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10        | Bit 9          | Bit 8          | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets       |

|-----------|-------|--------|--------|---------|---------|---------|---------------|----------------|----------------|---------|--------|-------|-------|-------|-------|-------|-------|---------------------|

| ALRMVAL   | 620h  |        |        |         |         |         | Alarm Value I | High Register  | Window Based   | on APTR | <1:0>  |       |       |       |       |       |       | XXXX                |

| ALCFGRPT  | 622h  | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0        | ALRMPTR1       | ALRMPTR0       | ARPT7   | ARPT6  | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | <sub>0000</sub> (1) |

| RTCVAL    | 624h  |        |        |         |         | R       | TCC Value H   | igh Register W | /indow Based o | n RTCPT | R<1:0> |       |       |       |       |       |       | xxxx                |

| RCFGCAL   | 626h  | RTCEN  | _      | RTCWREN | RTCSYNC | HALFSEC | RTCOE         | RTCPTR1        | RTCPTR0        | CAL7    | CAL6   | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000 <b>(1)</b>     |

| RTCPWC    | 628h  | PWCEN  | PWCPOL | PWCCPRE | PWCSPRE | RTCCLK1 | RTCCLK0       | RTCOUT1        | RTCOUT0        | _       | _      | _     | _     | _     | -     | _     | _     | <sub>0000</sub> (1) |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** Values are reset only on a VDD POR event.

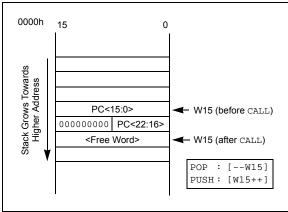

## 4.2.5 SOFTWARE STACK

In addition to its use as a working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as depicted in Figure 4-4.

For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6 in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

# 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit-wide program space and 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the Data Space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

See Table 4-35 and Figure 4-5 to know how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a Data Space word.

# REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----|-----------|

| —     | —   | —   | _   | —   | _   | —   | ULPWUIF   |

| bit 7 |     |     |     |     |     |     | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

### REGISTER 8-11: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----------|-----------|

| —     | —   | —   | —   | —   | —   | CLC2IF    | CLC1IF    |

| bit 7 |     |     |     |     |     |           | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IF: Configurable Logic Cell 2 Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

bit 0 CLC1IF: Configurable Logic Cell 1 Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

| U-0          | R/W-1         | R/W-0                                | R/W-0            | U-0                | R/W-1            | R/W-0           | R/W-0   |

|--------------|---------------|--------------------------------------|------------------|--------------------|------------------|-----------------|---------|

| —            | CCT1IP2       | CCT1IP1                              | CCT1IP0          | —                  | CCP4IP2          | CCP4IP1         | CCP4IP0 |

| bit 15       |               |                                      |                  |                    |                  |                 | bit 8   |

| U-0          | R/W-1         | R/W-0                                | R/W-0            | U-0                | U-0              | U-0             | U-0     |

|              | CCP3IP2       | CCP3IP1                              | CCP3IP0          |                    |                  |                 |         |

| bit 7        | 0010112       |                                      |                  |                    |                  |                 | bit 0   |

|              |               |                                      |                  |                    |                  |                 |         |

| Legend:      |               |                                      |                  |                    |                  |                 |         |

| R = Readab   | ole bit       | W = Writable                         | bit              | U = Unimplen       | nented bit, read | l as '0'        |         |

| -n = Value a | at POR        | '1' = Bit is set                     |                  | '0' = Bit is cle   | ared             | x = Bit is unkn | iown    |

|              |               |                                      |                  |                    |                  |                 |         |

| bit 15       | -             | ted: Read as '                       |                  |                    |                  |                 |         |

| bit 14-12    | CCT1IP<2:0>   | : Capture/Com                        | pare 1 Timer I   | nterrupt Priority  | / bits           |                 |         |

|              | 111 = Interru | pt is Priority 7(                    | highest priority | interrupt)         |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | 001 = Interru |                                      |                  |                    |                  |                 |         |

|              | •             | pt source is dis                     |                  |                    |                  |                 |         |

| bit 11       | -             | ted: Read as '                       |                  |                    |                  |                 |         |

| bit 10-8     |               | •                                    | •                | Interrupt Priority | y bits           |                 |         |

|              | 111 = Interru | pt is Priority 7(                    | highest priority | interrupt)         |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | 001 = Interru |                                      |                  |                    |                  |                 |         |

|              | -             | pt source is dis                     |                  |                    |                  |                 |         |

| bit 7        | -             | ted: Read as '                       |                  |                    |                  |                 |         |

| bit 6-4      |               | •                                    | •                | Interrupt Priority | y bits           |                 |         |

|              | 111 = Interru | pt is Priority 7(                    | nignest priority | (interrupt)        |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | 001 = Interru | pt is Priority 1<br>pt source is dis | ablad            |                    |                  |                 |         |

| bit 3-0      | •             | ted: Read as '                       |                  |                    |                  |                 |         |

| DIL 3-0      | Unimplemen    | ieu: Reau as                         | J                |                    |                  |                 |         |

# REGISTER 8-20: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0         U-0         U-0         U-0         U-0         U-0         U-0           -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <t< th=""><th>REGISTER</th><th>9-2: CLKL</th><th>DIV: CLOCK L</th><th></th><th>6151EK</th><th></th><th></th><th></th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REGISTER | 9-2: CLKL                                                                                                                                                                                                                                                        | DIV: CLOCK L                                                                                                                                                                                                                                                                                                                      |                                                                                                                  | 6151EK               |                  |                  |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------|

| bit 15       bit 1         U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -         bit 7       bit 10       U-0       U-0       U-0       U-0         Egend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       RO: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE       DOZE       2:0: CPU and Peripheral Clock Ratio Select bits       111 = 1:28         110 = 1:4       101 = 1:28       100 = 1:16       112       100 = 1:16         011 = 1:1       DOZE       2:0: CPU and peripheral clock ratio are set to 1:1       111 = 13:25 kHz (divide-by-26)         110 = 125 kHz (divide-by-32)       100 = 2:0: CPU and peripheral clock ratio are set to 1:1       111 = 31:25 kHz (divide-by-32)         101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)         101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)         101 = 156 kHz (d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0    | R/W-0                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                             | R/W-1                                                                                                            |                      | R/W-0            | R/W-0            | R/W-1  |

| U-0         U-0         U-0         U-0         U-0         U-0         U-0           -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ROI      | DOZE2                                                                                                                                                                                                                                                            | DOZE1                                                                                                                                                                                                                                                                                                                             | DOZE0                                                                                                            | DOZEN <sup>(1)</sup> | RCDIV2           | RCDIV1           | RCDIV0 |

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15   |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                      |                  |                  | bit 8  |

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11.0     | 11.0                                                                                                                                                                                                                                                             | 11.0                                                                                                                                                                                                                                                                                                                              | 11.0                                                                                                             | 11.0                 | 11.0             | 11.0             | 11.0   |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>bit 14-12 DOZE-2:0-: CPU and Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>110 = 1:132<br>100 = 1:16<br>011 = 1:3<br>100 = 1:16<br>011 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE-2:0-> bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10-8 RCDIV-2:0->: FRC Postscaler Select bits<br>When COSC-2:0-> (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-2)<br>100 = 500 kHz (divide-by-2) = default<br>001 = 1.4 (divide-by-2)<br>100 = 2 MHz (divide-by-2) = default<br>001 = 4 MHz (divide-by-2) = default<br>001 = 4 MHz (divide-by-2) = 110:<br>111 = 1.95 kHz (divide-by-2) = default<br>001 = 8 MHz (divide-by-2) = default<br>001 = 8 MHz (divide-by-2) = default<br>001 = 7.81 kHz (divide-by-2) = default<br>001 = 7.81 kHz (divide-by-2) = 110:<br>111 = 1.95 kHz (divide-by-2) = 110:<br>111 = 1.95 kHz (divide-by-2) = 110:<br>111 = 1.95 kHz (divide-by-2) = default<br>011 = 1.05 kHz (divide-by-2) = default<br>011 = 1.05 kHz (divide-by-2) = 110:<br>112 = 1.05 kHz (divide-by-2) = 0 = 0 = 110:<br>113 = 0.25 kHz (divide-by-2) = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0-0      | 0-0                                                                                                                                                                                                                                                              | 0-0                                                                                                                                                                                                                                                                                                                               | 0-0                                                                                                              | 0-0                  | 0-0              | 0-0              | 0-0    |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE-2:0>: CPU and Peripheral Clock Ratio Select bits       111 = 1:128         101 = 1:64       101 = 1:32       100 = 1:16         001 = 1:1       000 = 1:11       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE<2:0>: Dits specify the CPU and peripheral clock ratio       0 = CPU and peripheral clock ratio are set to 1:1         bit 10       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE         1 = 1:2       000 = 1:1       111 = 31.25 kHz (divide-by-256)         1 = 250 kHz (divide-by-256)       111 = 31.25 kHz (divide-by-256)         1 = 255 kHz (divide-by-32)       100 = 500 kHz (divide-by-32)         1 = 1 = 255 kHz (divide-by-32)       100 = 2 MHz (divide-by-41)         1 = 1 = 152 kHz (divide-by-42)       101 = 156 kHz (divide-by-32)         1 = 1 = 10:       111 = 115 kHz (divide-by-32)         1 = 1 = 112       111 = 111 = 111 = 111 = 115 kHz (divide-by-42)         1 = 1 = 250 kHz (divide-by-32)       100 = 2 MHz (divide-by-32)         1 = 0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 7    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                      |                  |                  | bit 0  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE-2:0>: CPU and Peripheral Clock Ratio Select bits       111 = 1:128         101 = 1:64       101 = 1:32       100 = 1:16         001 = 1:1       000 = 1:11       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE<2:0>: Dits specify the CPU and peripheral clock ratio       0 = CPU and peripheral clock ratio are set to 1:1         bit 10       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE         1 = 1:2       000 = 1:1       111 = 31.25 kHz (divide-by-256)         1 = 250 kHz (divide-by-256)       111 = 31.25 kHz (divide-by-256)         1 = 255 kHz (divide-by-32)       100 = 500 kHz (divide-by-32)         1 = 1 = 255 kHz (divide-by-32)       100 = 2 MHz (divide-by-41)         1 = 1 = 152 kHz (divide-by-42)       101 = 156 kHz (divide-by-32)         1 = 1 = 10:       111 = 115 kHz (divide-by-32)         1 = 1 = 112       111 = 111 = 111 = 111 = 115 kHz (divide-by-42)         1 = 1 = 250 kHz (divide-by-32)       100 = 2 MHz (divide-by-32)         1 = 0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Logondu  |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                      |                  |                  |        |

| <pre>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 ROI: Recover on Interrupt bit 1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1 0 = Interrupts have no effect on the DOZEN bit bit 14-12 DOZE-2:0&gt;: CPU and Peripheral Clock Ratio Select bits 111 = 1:128 110 = 1:64 101 = 1:32 100 = 1:1 001 = 1:4 001 = 1:2 000 = 1:1 bit 11 DOZEN: Doze Enable bit<sup>(1)</sup> 1 = DOZE-2:0&gt; bits specify the CPU and peripheral clock ratio 0 = CPU and peripheral clock ratio are set to 1:1 bit 10-8 RCDIVe2:0&gt;: FRC Postscaler Select bits When COSC&lt;2:0&gt; (OSCCON(14:12&gt;) = 111: 111 = 31.25 kHz (divide-by-266) 110 = 125 kHz (divide-by-4) 011 = 150 kHz (divide-by-4) 011 = 150 kHz (divide-by-4) 011 = 15.8 kHz (divide-by-4) 011 = 15.8 kHz (divide-by-4) 101 = 15.62 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-4) 011 = 62.5 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-2) - default 011 = 02.5 kHz (divide-by-2) - default 012 = 25 kHz (divide-by-4) 013 = 25 kHz (divide-by-4) 014 = 12.5 kHz (divide-by-4) 015 = 2.5 kHz (divide-by-4) 015 = 12.5 kHz (divide-by-4) 015 = 12.5 kHz (divide-by-4) 015 = 12.5 kHz (divide-by-4) 015 = 2.5 kHz (divide-by-4) 015 = 2</pre>                                                                                           | -        | le bit                                                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                                      | bit                                                                                                              | U = Unimplem         | nented bit, read | d as '0'         |        |

| bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>DOZE-2:00: CPU and Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE-2:00: bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10-8 RCDV-2:00: FRC Postscaler Select bits<br>When COSC-2:00: (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-29)<br>011 = 1 MHz (divide-by-2) - default<br>000 = 8 MHz (divide-by-2) - default<br>101 = 25 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 7.81 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-2) - default<br>001 = 125 kHz (divide-by-2)<br>100 = 125 kHz (divide-by-2)<br>100 = 125 kHz (divide-by-2)<br>100 = 125 kHz (divide-by-2) - default<br>001 = 25 kHz (divide-by-2) - default<br>002 = 500 kHz (divide-by-2) - default<br>003 = 500 kHz (divide-by-2) - default<br>004 = 500 kHz (divide-by-2) - default<br>005 = 500 kHz (divide-by-2) |          |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | -                    |                  |                  | nown   |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 1 = Interrupts<br>0 = Interrupts                                                                                                                                                                                                                                 | s clear the DOZ<br>s have no effect                                                                                                                                                                                                                                                                                               | EN bit, and re<br>t on the DOZE                                                                                  | N bit                | d peripheral cl  | ock ratio to 1:1 |        |

| 1 = DOZE<2:0> bits specify the CPU and peripheral clock ratio 0 = CPU and peripheral clock ratio are set to 1:1 bit 10-8 $RCDIV<2:0>: FRC Postscaler Select bits When COSC<2:0> (OSCCON<14:12>) = 111: 111 = 31.25 kHz (divide-by-256) 110 = 125 kHz (divide-by-264) 101 = 250 kHz (divide-by-32) 100 = 500 kHz (divide-by-32) 100 = 500 kHz (divide-by-4) 011 = 1 MHz (divide-by-4) 010 = 2 MHz (divide-by-2) - default 000 = 8 MHz (divide-by-2) 100 = 8 MHz (divide-by-2) = 110: 111 = 1.95 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-32) 100 = 31.25 kHz (divide-by-3) 100 = 31.25 kHz (divide-by-4) 011 = 125 kHz (divide-by-4) 010 = 125 kHz (divide-by-4) 010 = 125 kHz (divide-by-2) - default 000 = 500 kHz (divide-by-1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2                                                                                                                                                                     | 111 = 1:128 $110 = 1:64$ $101 = 1:32$ $100 = 1:16$ $011 = 1:8$ $010 = 1:4$                                                                                                                                                                                                                                                        |                                                                                                                  |                      |                  |                  |        |