# E·XFL

### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

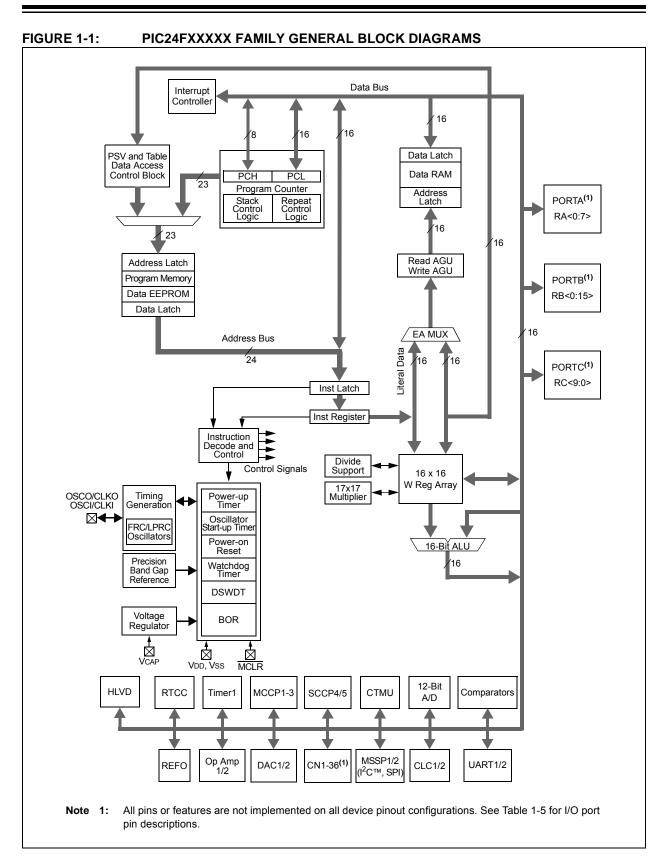

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 28-SPDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km102-i-sp |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: | DEVICE FEATURES FOR THE PIC24F16KM204 FAMILY |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| TABLE 1-1: DEVICE FEATURES FO                    | R THE PIC24F16                                                                                                                                      |                    | •                      |                        |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|------------------------|

| Features                                         | PIC24F16KM204                                                                                                                                       | PIC24F08KM204      | PIC24F16KM202          | PIC24F08KM202          |

| Operating Frequency                              |                                                                                                                                                     | DC-3               | 2 MHz                  |                        |

| Program Memory (bytes)                           | 16K                                                                                                                                                 | 8K                 | 16K                    | 8K                     |

| Program Memory (instructions)                    | 5632                                                                                                                                                | 2816               | 5632                   | 2816                   |

| Data Memory (bytes)                              |                                                                                                                                                     | 20                 | )48                    |                        |

| Data EEPROM Memory (bytes)                       |                                                                                                                                                     | 5                  | 12                     |                        |

| Interrupt Sources (soft vectors/NMI traps)       |                                                                                                                                                     | 40 (               | 36/4)                  |                        |

| Voltage Range                                    |                                                                                                                                                     | 1.8-               | 3.6V                   |                        |

| I/O Ports                                        | PORTA<<br>PORTB<<br>PORTC                                                                                                                           | :15:0>             | -                      | RTA<7:0><br>RTB<15:0>  |

| Total I/O Pins                                   | 38                                                                                                                                                  |                    |                        | 24                     |

| Timers                                           | (One 16-bit timer, f                                                                                                                                |                    | l1<br>Ps with up to tv | vo 16/32 timers each)  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP      |                                                                                                                                                     |                    | 3<br>2                 |                        |

| Serial Communications<br>MSSP<br>UART            |                                                                                                                                                     |                    | 2<br>2                 |                        |

| Input Change Notification Interrupt              | 37                                                                                                                                                  |                    | 23                     |                        |

| 12-Bit Analog-to-Digital Module (input channels) | 22                                                                                                                                                  | 22                 | 19                     | 19                     |

| Analog Comparators                               |                                                                                                                                                     | :                  | 3                      |                        |

| 8-Bit Digital-to-Analog Converters               |                                                                                                                                                     |                    | 2                      |                        |

| Operational Amplifiers                           |                                                                                                                                                     |                    | 2                      |                        |

| Charge Time Measurement Unit (CTMU)              |                                                                                                                                                     | Y                  | es                     |                        |

| Real-Time Clock and Calendar (RTCC)              |                                                                                                                                                     | Y                  | es                     |                        |

| Configurable Logic Cell (CLC)                    |                                                                                                                                                     |                    | 2                      |                        |

| Resets (and delays)                              | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                    |                        |                        |

| Instruction Set                                  | 76 Base Inst                                                                                                                                        | ructions, Multiple | e Addressing N         | lode Variations        |

| Packages                                         | 44-Pin QFI<br>48-Pin L                                                                                                                              |                    |                        | 28-Pin<br>SOP/SOIC/QFN |

## 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10 µF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### DC BIAS VOLTAGE vs. FIGURE 2-4: CAPACITANCE **CHARACTERISTICS** Capacitance Change (%) 0 -10 16V Capacitor -20 -30 -40 10V Capacitor -50 -60 -70 6.3V Capacitor -80 -9 10 11 12 13 2 8 15 16 DC Bias Voltage (VDC)

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 3.3V or 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100Ω.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pins, Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 26.0 "Development Support"**.

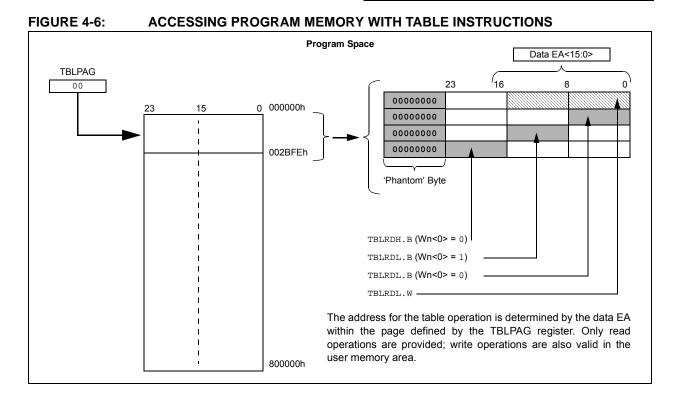

## 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through Data Space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

Note: The TBLRDH and TBLWTH instructions are not used while accessing data EEPROM memory.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit, word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table Write operations are not allowed.

© 2013 Microchip Technology Inc.

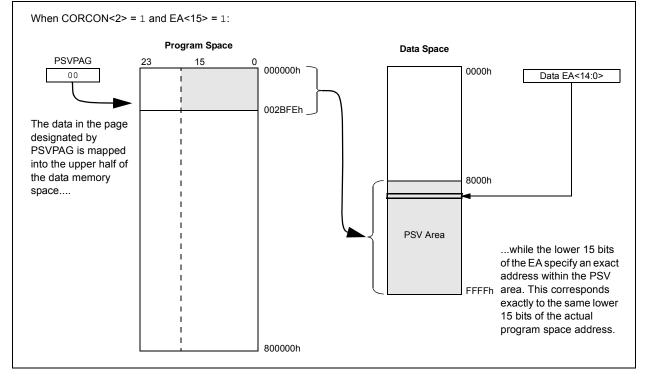

## 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of Data Space may optionally be mapped into a 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs if the MSb of the Data Space, EA, is '1' and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the Data Space is determined by the Program Space Visibility Page Address register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of Data Space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each Data Space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | Table Reads/Writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

## FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

## TABLE 8-1:TRAP VECTOR DETAILS

## TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS

|                                         |               |             | ΑΙντ    | Interrupt Bit Locations |          |              |  |

|-----------------------------------------|---------------|-------------|---------|-------------------------|----------|--------------|--|

| Interrupt Source                        | Vector Number | IVI Address | Address | Flag                    | Enable   | Priority     |  |

| ADC1 – ADC1 Convert Done                | 13            | 00002Eh     | 00012Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>    |  |

| CLC1                                    | 96            | 0000D4h     | 0001D4h | IFS6<0>                 | IEC6<0>  | IPC24<2:0>   |  |

| CLC2                                    | 97            | 0000D6h     | 0001D6h | IFS6<1>                 | IEC6<1>  | IPC24<6:4>   |  |

| Comparator Interrupt                    | 18            | 000038h     | 000138h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>   |  |

| СТМИ                                    | 77            | 0000AEh     | 0001AEh | IFS4<13>                | IEC4<13> | IPC19<6:4>   |  |

| DAC1 – Buffer Update                    | 78            | 0000B0h     | 0001B0h | IFS4<14>                | IEC4<14> | IPC19<10:8>  |  |

| DAC2 – Buffer Update                    | 79            | 0000B2h     | 0001B2h | IFS4<15>                | IEC4<15> | IPC19<14:12> |  |

| HLVD – High/Low-Voltage Detect          | 72            | 0000A4h     | 0001A4h | IFS4<8>                 | IEC4<8>  | IPC18<2:0>   |  |

| ICN – Input Change Notification         | 19            | 00003Ah     | 00013Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12>  |  |

| INT0 – External Interrupt 0             | 0             | 000014h     | 000114h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>    |  |

| INT1 – External Interrupt 1             | 20            | 00003Ch     | 00013Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>    |  |

| INT2 – External Interrupt 2             | 29            | 00004Eh     | 00014Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>    |  |

| MCCP1 – Capture/Compare                 | 1             | 000016h     | 000116h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>    |  |

| MCCP1 – Time Base                       | 7             | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |  |

| MCCP2 – Capture/Compare                 | 2             | 000018h     | 000118h | IFS0<2>                 | IEC0<2>  | IPC0<10:8>   |  |

| MCCP2 – Time Base                       | 8             | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |  |

| MCCP3 – Capture/Compare                 | 5             | 00001Eh     | 00011Eh | IFS0<5>                 | IEC0<5>  | IPC1<6:4>    |  |

| MCCP3 – Time Base                       | 27            | 00004Ah     | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |  |

| MSSP1 – Bus Collision Interrupt         | 17            | 000036h     | 000136h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>    |  |

| MSSP1 – I <sup>2</sup> C™/SPI Interrupt | 16            | 000034h     | 000134h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>    |  |

| MSSP2 – Bus Collision Interrupt         | 50            | 000078h     | 000178h | IFS3<2>                 | IEC3<2>  | IPC12<10:8>  |  |

| MSSP2 – I <sup>2</sup> C/SPI Interrupt  | 49            | 000076h     | 000176h | IFS3<1>                 | IEC3<1>  | IPC12<6:4>   |  |

| NVM – NVM Write Complete                | 15            | 000032h     | 000132h | IFS0<15>                | IEC0<15> | IPC3<14:12>  |  |

| RTCC – Real-Time Clock/Calendar         | 62            | 000090h     | 000190h | IFS3<14>                | IEC3<14> | IPC15<10:8>  |  |

| SCCP4 – Capture/Compare                 | 6             | 000020h     | 000120h | IFS0<6>                 | IEC0<6>  | IPC1<10:8>   |  |

| SCCP4 – Time Base                       | 28            | 00004Ch     | 00014Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |  |

| SCCP5 – Capture/Compare                 | 22            | 000040h     | 000140h | IFS1<6>                 | IEC1<6>  | IPC5<10:8>   |  |

| SCCP5 – Time Base                       | 41            | 000066h     | 000166h | IFS2<9>                 | IEC2<9>  | IPC10<6:4>   |  |

| TMR1 – Timer1                           | 3             | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |  |

| UART1 Error                             | 65            | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |  |

| UART2 Error                             | 66            | 000098h     | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |  |

| UART1RX – UART1 Receiver                | 11            | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |  |

| UART1TX – UART1 Transmitter             | 12            | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |  |

| UART2RX – UART2 Receiver                | 30            | 000050h     | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |  |

| UART2TX – UART2 Transmitter             | 31            | 000052h     | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |  |

| ULPWU – Ultra Low-Power Wake-up         | 80            | 0000B4h     | 0001B4h | IFS5<0>                 | IEC5<0>  | IPC20<2:0>   |  |

| R/W-0, HS       | R/W-0, HS                                                                           | R/W-0, HS                           | U-0              | U-0              | U-0              | U-0             | R/W-0, HS |

|-----------------|-------------------------------------------------------------------------------------|-------------------------------------|------------------|------------------|------------------|-----------------|-----------|

| DAC2IF          | DAC1IF                                                                              | CTMUIF                              | —                |                  | _                |                 | HLVDIF    |

| bit 15          |                                                                                     |                                     |                  |                  |                  |                 | bit 8     |

|                 |                                                                                     |                                     |                  |                  |                  |                 |           |

| U-0             | U-0                                                                                 | U-0                                 | U-0              | U-0              | R/W-0, HS        | R/W-0, HS       | U-0       |

| —               | —                                                                                   | —                                   | _                | —                | U2ERIF           | U1ERIF          | —         |

| bit 7           |                                                                                     |                                     |                  |                  |                  |                 | bit 0     |

|                 |                                                                                     |                                     |                  |                  |                  |                 |           |

| Legend:         |                                                                                     | HS = Hardwar                        | re Settable bit  |                  |                  |                 |           |

| R = Readable    | e bit                                                                               | W = Writable I                      | oit              | U = Unimpler     | nented bit, read | l as '0'        |           |

| -n = Value at I | POR                                                                                 | '1' = Bit is set                    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | iown      |

|                 |                                                                                     |                                     |                  |                  |                  |                 |           |

| bit 15          | •                                                                                   | tal-to-Analog C                     |                  | rrupt Flag Stat  | us bit           |                 |           |

|                 |                                                                                     | request has occ<br>request has not  |                  |                  |                  |                 |           |

| bit 14          |                                                                                     | •                                   |                  | reunt Flog Stat  | ua hit           |                 |           |

| DIL 14          | •                                                                                   | tal-to-Analog Co<br>request has occ |                  | mupt Flag Stat   |                  |                 |           |

|                 |                                                                                     | request has not                     |                  |                  |                  |                 |           |

| bit 13          |                                                                                     | MU Interrupt Fla                    |                  |                  |                  |                 |           |

|                 |                                                                                     | request has occ                     | •                |                  |                  |                 |           |

|                 | 0 = Interrupt r                                                                     | request has not                     | occurred         |                  |                  |                 |           |

| bit 12-9        | Unimplemen                                                                          | ted: Read as 'o                     | )'               |                  |                  |                 |           |

| bit 8           | HLVDIF: High                                                                        | n/Low-Voltage D                     | Detect Interrupt | t Flag Status bi | t                |                 |           |

|                 |                                                                                     | request has occ                     |                  |                  |                  |                 |           |

|                 |                                                                                     | request has not                     |                  |                  |                  |                 |           |

| bit 7-3         | Unimplemented: Read as '0'                                                          |                                     |                  |                  |                  |                 |           |

| bit 2           | U2ERIF: UART2 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                     |                  |                  |                  |                 |           |

|                 |                                                                                     | request has occ<br>request has not  |                  |                  |                  |                 |           |

| bit 1           | U1ERIF: UART1 Error Interrupt Flag Status bit                                       |                                     |                  |                  |                  |                 |           |

|                 |                                                                                     | request has occ                     |                  |                  |                  |                 |           |

|                 |                                                                                     | request has not                     |                  |                  |                  |                 |           |

| bit 0           | Unimplemen                                                                          | ted: Read as 'o                     | )'               |                  |                  |                 |           |

|                 |                                                                                     |                                     |                  |                  |                  |                 |           |

## REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0                          | U-0                                      | U-0                                                                                                                                     | U-0                             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|---------|

| _                            |                                          |                                                                                                                                         |                                 |                  | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| oit 15                       |                                          |                                                                                                                                         | •                               |                  |                  | •               | bit 8   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| U-0                          | R/W-1                                    | R/W-0                                                                                                                                   | R/W-0                           | U-0              | U-0              | U-0             | U-0     |

| —                            | U1ERIP2                                  | U1ERIP1                                                                                                                                 | U1ERIP0                         | —                | —                | —               | —       |

| bit 7                        |                                          |                                                                                                                                         |                                 |                  |                  |                 | bit 0   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| Legend:                      |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| R = Readab                   | ole bit                                  | W = Writable                                                                                                                            | bit                             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value a                 | at POR                                   | '1' = Bit is set                                                                                                                        |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8<br>bit 7<br>bit 6-4 | <pre>111 = Interru </pre>                | >: UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>>: UART1 Error<br>pt is Priority 7 ( | highest priority<br>abled<br>o' | interrupt)       |                  |                 |         |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '                                                             | abled                           | interrupt)       |                  |                 |         |

## REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

## 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC Oscillator by a fixed amount.

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                    | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit |                        |                    |

|----------------------------|---------------------------------------|------------------------|--------------------|

| HS = Hardware Settable bit | CO = Clearable Only bit               | SO = Settable Only bit |                    |

| R = Readable bit           | W = Writable bit                      | U = Unimplemented bit  | , read as '0'      |

| -n = Value at POR          | '1' = Bit is set                      | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| Note 1:   | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:        | This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                |

**3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

## 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O ports, refer to the *"PIC24F Family Reference Manual"*, *"I/O Ports with Peripheral Pin Select (PPS)"* (DS39711). Note that the PIC24FV16KM204 family devices do not support Peripheral Pin Select features.

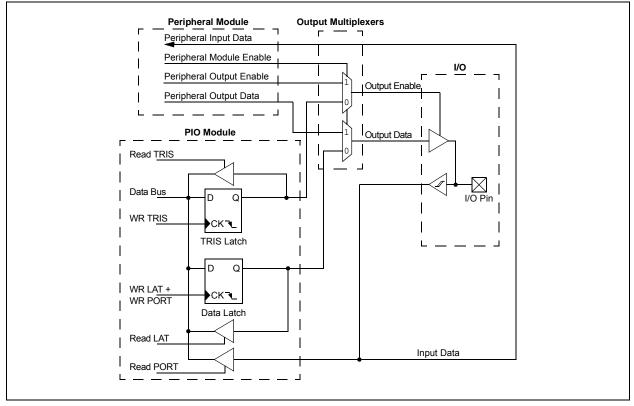

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

A Parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the Data Direction register bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LATx), read the latch. Writes to the latch, write the latch. Reads from the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

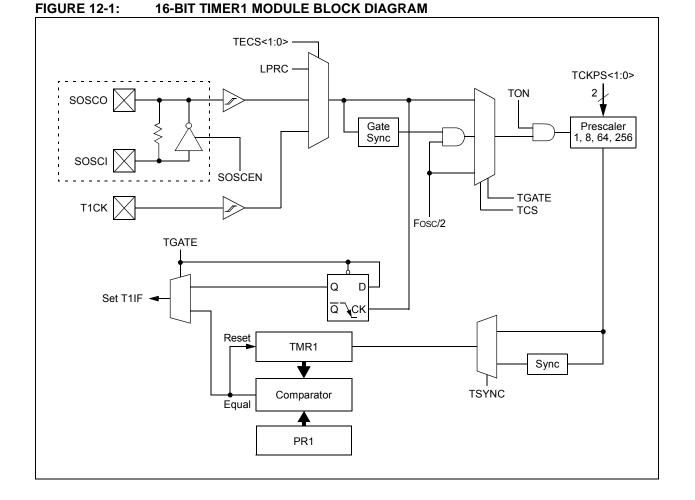

## 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on timers, refer to the "PIC24F Family Reference Manual", "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

| REGISTER 16-2: | RTCPWC: RTCC CONFIGURATION REGISTER 2 <sup>(1)</sup> |

|----------------|------------------------------------------------------|

|                |                                                      |

| R/W-0      | R/W-0                                                                                          | R/W-0                                         | R/W-0                        | R/W-0                                                          | R/W-0                  | R/W-0           | R/W-0      |  |  |  |

|------------|------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------|----------------------------------------------------------------|------------------------|-----------------|------------|--|--|--|

| PWCEN      | PWCPOL                                                                                         | PWCCPRE                                       | PWCSPRE                      | RTCCLK1 <sup>(2)</sup>                                         | RTCCLK0 <sup>(2)</sup> | RTCOUT1         | RTCOUT0    |  |  |  |

| bit 15     |                                                                                                |                                               |                              |                                                                |                        |                 | bit 8      |  |  |  |

|            |                                                                                                |                                               |                              |                                                                |                        |                 |            |  |  |  |

| U-0        | U-0                                                                                            | U-0                                           | U-0                          | U-0                                                            | U-0                    | U-0             | U-0        |  |  |  |

|            |                                                                                                |                                               |                              |                                                                |                        |                 |            |  |  |  |

| bit 7      |                                                                                                |                                               |                              |                                                                |                        |                 | bit C      |  |  |  |

| Legend:    |                                                                                                |                                               |                              |                                                                |                        |                 |            |  |  |  |

| R = Reada  | hle hit                                                                                        | W = Writable                                  | hit                          | II = I Inimpleme                                               | nted bit, read as      | ʻ <b>∩</b> '    |            |  |  |  |

| -n = Value |                                                                                                | '1' = Bit is set                              |                              | '0' = Bit is cleare                                            |                        | x = Bit is unkr | own        |  |  |  |

|            |                                                                                                |                                               |                              |                                                                | 50                     |                 |            |  |  |  |

| bit 15     | PWCEN: Po                                                                                      | wer Control Er                                | able bit                     |                                                                |                        |                 |            |  |  |  |

|            |                                                                                                | ontrol is enable                              |                              |                                                                |                        |                 |            |  |  |  |

|            | 0 = Power co                                                                                   | ontrol is disable                             | ed                           |                                                                |                        |                 |            |  |  |  |

| bit 14     | PWCPOL: P                                                                                      | ower Control F                                | Polarity bit                 |                                                                |                        |                 |            |  |  |  |

|            |                                                                                                | ontrol output is                              |                              |                                                                |                        |                 |            |  |  |  |

|            |                                                                                                | ontrol output is                              |                              |                                                                |                        |                 |            |  |  |  |

| bit 13     |                                                                                                | Power Control                                 | 2                            |                                                                |                        |                 |            |  |  |  |

|            |                                                                                                |                                               |                              | by-2 of source R <sup>-</sup><br>by-1 of source R <sup>-</sup> |                        |                 |            |  |  |  |

| bit 12     |                                                                                                | Power Control                                 |                              | 2                                                              |                        |                 |            |  |  |  |

|            |                                                                                                |                                               | •                            | by-2 of source R                                               | CC clock               |                 |            |  |  |  |

|            |                                                                                                |                                               |                              | by-1 of source R                                               |                        |                 |            |  |  |  |

| bit 11-10  | RTCCLK<1:                                                                                      | 0>: RTCC Clo                                  | ck Select bits <sup>(2</sup> | 2)                                                             |                        |                 |            |  |  |  |

|            | Determines the source of the internal RTCC clock, which is used for all RTCC timer operations. |                                               |                              |                                                                |                        |                 |            |  |  |  |

|            | 00 = External Secondary Oscillator (SOSC)<br>01 = Internal LPRC Oscillator                     |                                               |                              |                                                                |                        |                 |            |  |  |  |

|            | 10 = External power line source – 50 Hz                                                        |                                               |                              |                                                                |                        |                 |            |  |  |  |

|            |                                                                                                | al power line so                              |                              |                                                                |                        |                 |            |  |  |  |

| bit 9-8    | RTCOUT<1:0>: RTCC Output Select bits                                                           |                                               |                              |                                                                |                        |                 |            |  |  |  |

|            |                                                                                                | Determines the source of the RTCC pin output. |                              |                                                                |                        |                 |            |  |  |  |

|            | 00 = RTCC                                                                                      | alarm pulse<br>seconds clock                  |                              |                                                                |                        |                 |            |  |  |  |

|            | 10 = RTCC (                                                                                    |                                               |                              |                                                                |                        |                 |            |  |  |  |

|            | 11 = Power (                                                                                   | control                                       |                              |                                                                |                        |                 |            |  |  |  |

| bit 7-0    | Unimpleme                                                                                      | nted: Read as                                 | <b>'</b> 0 <b>'</b>          |                                                                |                        |                 |            |  |  |  |

| Note 1:    | The RTCPWC                                                                                     | register is only                              | affected by a                | POR                                                            |                        |                 |            |  |  |  |

|            |                                                                                                |                                               | -                            | r bits the Secon                                               | da Valua ragiatar      | should also be  | written to |  |  |  |

2: When a new value is written to these register bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

## REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit                  |

|-------|--------------------------------------------------------------|

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit               |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                  |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit               |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

| R/W-0        | U-0                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                    | R/W-0          | R/W-0                           | U-0              | R/W-0           | R/W-0        |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------|------------------|-----------------|--------------|--|--|

| DACEN        |                                                                                                                                                                                                                             | DACSIDL                                                                                                                                                                                  | DACSLP         | DACFM                           |                  | SRDIS           | DACTRIG      |  |  |

| bit 15       |                                                                                                                                                                                                                             |                                                                                                                                                                                          |                |                                 |                  |                 | bit 8        |  |  |

| R/W-0        | R/W-0                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                    | R/W-0          | R/W-0                           | R/W-0            | R/W-0           | R/W-0        |  |  |

| DACOE        | DACTSEL4                                                                                                                                                                                                                    | DACTSEL3                                                                                                                                                                                 | DACTSEL2       | DACTSEL1                        | DACTSEL0         | DACREF1         | DACREF0      |  |  |

| bit 7 k      |                                                                                                                                                                                                                             |                                                                                                                                                                                          |                |                                 |                  |                 |              |  |  |

| Legend:      |                                                                                                                                                                                                                             |                                                                                                                                                                                          |                |                                 |                  |                 |              |  |  |

| R = Readab   | le bit                                                                                                                                                                                                                      | W = Writable                                                                                                                                                                             | bit            | U = Unimplen                    | nented bit, read | l as '0'        |              |  |  |

| -n = Value a | t POR                                                                                                                                                                                                                       | '1' = Bit is set                                                                                                                                                                         |                | '0' = Bit is clea               |                  | x = Bit is unkr | nown         |  |  |

|              |                                                                                                                                                                                                                             |                                                                                                                                                                                          |                |                                 |                  |                 | -            |  |  |

| bit 15       | DACEN: DAC                                                                                                                                                                                                                  | x Enable bit                                                                                                                                                                             |                |                                 |                  |                 |              |  |  |

|              | 1 = Module is                                                                                                                                                                                                               | s enabled                                                                                                                                                                                |                |                                 |                  |                 |              |  |  |

|              | 0 = Module is                                                                                                                                                                                                               | s disabled                                                                                                                                                                               |                |                                 |                  |                 |              |  |  |

| bit 14       | Unimplement                                                                                                                                                                                                                 | ted: Read as 'd                                                                                                                                                                          | )'             |                                 |                  |                 |              |  |  |

| bit 13       | DACSIDL: DA                                                                                                                                                                                                                 | ACx Stop in Idle                                                                                                                                                                         | e Mode bit     |                                 |                  |                 |              |  |  |

|              |                                                                                                                                                                                                                             | ues module op<br>s module opera                                                                                                                                                          |                | device enters lo<br>ode         | lle mode         |                 |              |  |  |

| bit 12       | DACSLP: DA                                                                                                                                                                                                                  | Cx Enable Per                                                                                                                                                                            | ipheral During | Sleep bit                       |                  |                 |              |  |  |

|              |                                                                                                                                                                                                                             |                                                                                                                                                                                          |                | ent value of DA<br>; DACxOUT pi |                  |                 | nd LATx bits |  |  |

| bit 11       | DACFM: DAC                                                                                                                                                                                                                  | x Data Format                                                                                                                                                                            | Select bit     |                                 |                  |                 |              |  |  |

|              |                                                                                                                                                                                                                             | ft justified (data<br>ht justified (dat                                                                                                                                                  |                |                                 |                  |                 |              |  |  |

| bit 10       | Unimplement                                                                                                                                                                                                                 | ted: Read as '0                                                                                                                                                                          | )'             |                                 |                  |                 |              |  |  |

| bit 9        | SRDIS: Soft F                                                                                                                                                                                                               | Reset Disable b                                                                                                                                                                          | oit            |                                 |                  |                 |              |  |  |

|              | <ul> <li>1 = DACxCON and DACxDAT SFRs reset only on a POR or BOR Reset</li> <li>0 = DACxCON and DACxDAT SFRs reset on any type of device Reset</li> </ul>                                                                   |                                                                                                                                                                                          |                |                                 |                  |                 |              |  |  |

| bit 8        |                                                                                                                                                                                                                             |                                                                                                                                                                                          |                |                                 |                  |                 |              |  |  |

|              | <b>DACTRIG:</b> DACx Trigger Input Enable bit<br>1 = Analog output value updates when the selected (by DACTSEL<4:0>) event occurs<br>0 = Analog output value updates as soon as DACxDAT is written (DAC Trigger is ignored) |                                                                                                                                                                                          |                |                                 |                  |                 |              |  |  |

| bit 7        | DACOE: DAC                                                                                                                                                                                                                  | Cx Output Enab                                                                                                                                                                           | le bit         |                                 |                  |                 |              |  |  |

|              | 1 = DACx out                                                                                                                                                                                                                | <ul> <li>1 = DACx output pin is enabled and driven on the DACxOUT pin</li> <li>0 = DACx output pin is disabled, DACx output is available internally to other peripherals only</li> </ul> |                |                                 |                  |                 |              |  |  |

| Note 1.      |                                                                                                                                                                                                                             | in configuration                                                                                                                                                                         |                |                                 | -1.0~)           |                 | -            |  |  |

## REGISTER 20-1: DACxCON: DACx CONTROL REGISTER

**Note 1:** BGBUF1 voltage is configured by BUFREF<1:0> (BUFCON0<1:0>).