Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km102-i-ss |

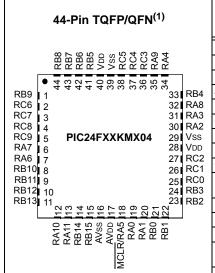

### Pin Diagrams (Continued)

| ED2/INT2/ |

|-----------|

| 1/CN12/   |

|           |

|           |

|           |

|           |

| 1         |

| 1         |

| 1         |

| 1         |

| 1         |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

| ,         |

|           |

Legend: Values in indicate pin

function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.

Note 1: Exposed pad on underside of

device is connected to Vss.

### **Table of Contents**

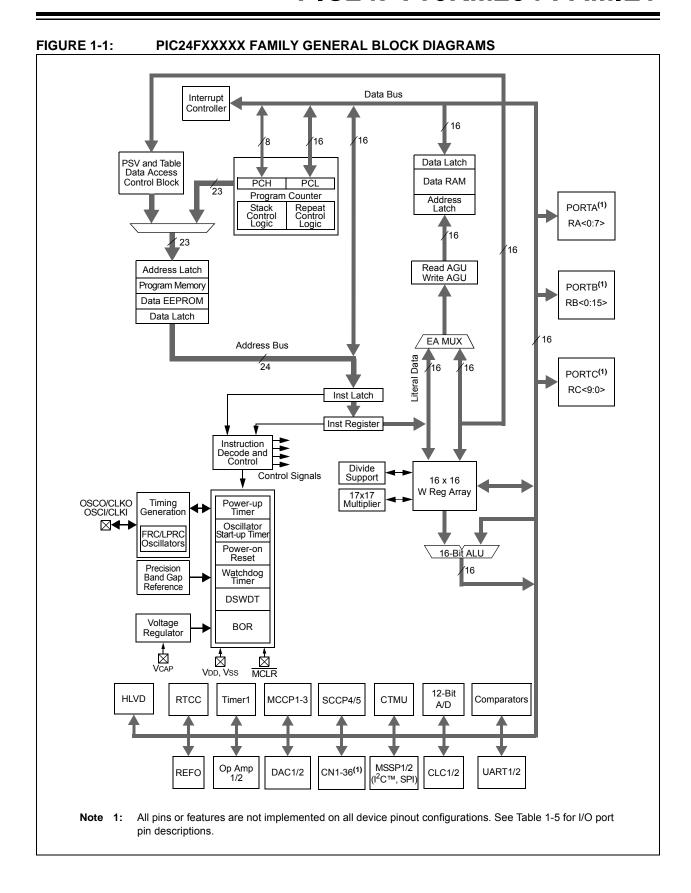

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 29  |

| 3.0   | CPU                                                         |     |

| 4.0   | Memory Organization                                         | 41  |

| 5.0   | Flash Program Memory                                        | 67  |

| 6.0   | Data EEPROM Memory                                          |     |

| 7.0   | Resets                                                      | 79  |

| 8.0   | Interrupt Controller                                        | 85  |

| 9.0   | Oscillator Configuration                                    | 121 |

| 10.0  | Power-Saving Features                                       | 131 |

| 11.0  | I/O Ports                                                   | 137 |

| 12.0  | Timer1                                                      | 141 |

| 13.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)           | 143 |

| 14.0  | Master Synchronous Serial Port (MSSP)                       |     |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART)          | 173 |

| 16.0  | Real-Time Clock and Calendar (RTCC)                         | 181 |

| 17.0  | Configurable Logic Cell (CLC)                               | 195 |

| 18.0  | High/Low-Voltage Detect (HLVD)                              | 207 |

|       | 12-Bit A/D Converter with Threshold Detect                  |     |

| 20.0  | 8-Bit Digital-to-Analog Converter (DAC)                     | 229 |

| 21.0  | Dual Operational Amplifier Module                           | 233 |

| 22.0  | Comparator Module                                           | 235 |

| 23.0  | Comparator Voltage Reference                                | 239 |

| 24.0  | Charge Time Measurement Unit (CTMU)                         | 241 |

| 25.0  | Special Features                                            | 249 |

| 26.0  | Development Support                                         | 261 |

| 27.0  | Electrical Characteristics                                  | 265 |

|       | Packaging Information                                       |     |

| Appe  | endix A: Revision History                                   | 325 |

| Index | X                                                           | 327 |

| The I | Microchip Web Site                                          | 333 |

| Custo | omer Change Notification Service                            | 333 |

| Custo | omer Support                                                | 333 |

| Produ | uct Identification System                                   | 335 |

### TABLE 4-24: PAD CONFIGURATION REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                 | Bit 10                 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|------------------------|------------------------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| PADCFG1   | 2FCh  | _      | _      | _      | _      | SDO2DIS <sup>(1)</sup> | SCK2DIS <sup>(1)</sup> | SDO1DIS | SCK1DIS | _     | _     | _     | _     | _     | _     | _     |       | 0000          |

PIC24FV16KM204 FAMILY

$\textbf{Legend:} \quad x = \text{unknown}, \ u = \text{unchanged}, \\ \textbf{\_} = \text{unimplemented}, \ q = \text{value depends on condition}, \ r = \text{reserved}.$

Note 1: These bits are not available on the PIC24F(V)08KM101 device, read as '0'.

### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | _   | _   | _   | _     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearable bit |                  |  |  |

|----------------------|------------------------|-----------------------------|------------------|--|--|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit            | W = Writable bit |  |  |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit, rea  | d as '0'         |  |  |

- bit 15 WR: Write Control bit

- 1 = Initiates a Flash memory program or erase operation; the operation is self-timed and the bit is cleared by hardware once the operation is complete

- 0 = Program or erase operation is complete and inactive

- bit 14 WREN: Write Enable bit

- 1 = Enables Flash program/erase operations

- 0 = Inhibits Flash program/erase operations

- bit 13 WRERR: Write Sequence Error Flag bit

- 1 = An improper program or erase sequence attempt, or termination has occurred (bit is set automatically on any set attempt of the WR bit)

- 0 = The program or erase operation completed normally

- bit 12 **PGMONLY:** Program Only Enable bit<sup>(4)</sup>

- bit 11-7 Unimplemented: Read as '0'

- bit 6 **ERASE:** Erase/Program Enable bit

- 1 = Performs the erase operation specified by the NVMOP<5:0> bits on the next WR command

- 0 = Performs the program operation specified by the NVMOP<5:0> bits on the next WR command

- bit 5-0 **NVMOP<5:0>:** Programming Operation Command Byte bits<sup>(1)</sup>

#### Erase Operations (when ERASE bit is '1'):

- 1010xx = Erase entire boot block (including code-protected boot block)<sup>(2)</sup>

- 1001xx = Erase entire memory (including boot block, configuration block, general block)(2)

- 011010 = Erase 4 rows of Flash memory<sup>(3)</sup>

- 011001 = Erase 2 rows of Flash memory(3)

- 011000 = Erase 1 row of Flash memory (3)

- 0101xx = Erase entire configuration block (except code protection bits)

- 0100xx = Erase entire data EEPROM<sup>(4)</sup>

- 0011xx = Erase entire general memory block programming operations

- 0001xx = Write 1 row of Flash memory (when ERASE bit is '0')(3)

- Note 1: All other combinations of NVMOP<5:0> are no operation.

- 2: Available in ICSP™ mode only. Refer to the device programming specification.

- 3: The address in the Table Pointer decides which rows will be erased.

- **4:** This bit is used only while accessing data EEPROM.

### REGISTER 8-31: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   |     | _   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|-----|-----|-----|-----|---------|---------|---------|

| _     | _   | _   | _   | _   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0'

bit 2-0 **HLVDIP<2:0>:** High/Low-Voltage Detect Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

-

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 7 CLKLOCK: Clock Selection Lock Enable bit

If FSCM is Enabled (FCKSM1 =  $\underline{1}$ ):

1 = Clock and PLL selections are locked

0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit

If FSCM is Disabled (FCKSM1 = 0):

Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.

bit 6 **Unimplemented:** Read as '0' bit 5 **LOCK:** PLL Lock Status bit<sup>(2)</sup>

1 = PLL module is in lock or PLL module start-up timer is satisfied

0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

bit 4 Unimplemented: Read as '0'

1 = FSCM has detected a clock failure0 = No clock failure has been detected

bit 2 **SOSCDRV**: Secondary Oscillator Drive Strength bit<sup>(3)</sup>

1 = High-power SOSC circuit is selected

0 = Low/high-power select is done via the SOSCSRC Configuration bit

bit 1 SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit

1 = Enables the Secondary Oscillator0 = Disables the Secondary Oscillator

bit 0 **OSWEN:** Oscillator Switch Enable bit

1 = Initiates an oscillator switch to the clock source specified by the NOSC<2:0> bits

0 = Oscillator switch is complete

Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

2: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

3: When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

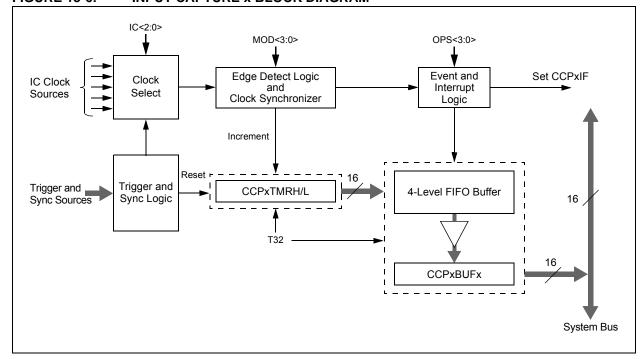

### 13.4 Input Capture Mode

Input Capture mode is used to capture a timer value from an independent timer base upon an event on an input pin or other internal Trigger source. The input capture features are useful in applications requiring frequency (time period) and pulse measurement. Figure 13-6 depicts a simplified block diagram of Input Capture mode.

Input Capture mode uses a dedicated 16/32-bit, synchronous, up counting timer for the capture function. The timer value is written to the FIFO when a capture event occurs. The internal value may be read (with a synchronization delay) using the CCPxTMRH/L register.

To use Input Capture mode, the CCSEL bit (CCPxCON1L<4>) must be set. The T32 and the MOD<3:0> bits are used to select the proper Capture mode, as shown in Table 13-4.

**TABLE 13-4: INPUT CAPTURE MODES**

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                     |  |  |  |  |

|------------------------------|-----------------------|------------------------------------|--|--|--|--|

| 0000                         | 0                     | Edge Detect (16-bit capture)       |  |  |  |  |

| 0000                         | 1                     | Edge Detect (32-bit capture)       |  |  |  |  |

| 0001                         | 0                     | Every Rising (16-bit capture)      |  |  |  |  |

| 0001                         | 1                     | Every Rising (32-bit capture)      |  |  |  |  |

| 0010                         | 0                     | Every Falling (16-bit capture)     |  |  |  |  |

| 0010                         | 1                     | Every Falling (32-bit capture)     |  |  |  |  |

| 0011                         | 0                     | Every Rise/Fall (16-bit capture)   |  |  |  |  |

| 0011                         | 1                     | Every Rise/Fall (32-bit capture)   |  |  |  |  |

| 0100                         | 0                     | Every 4th Rising (16-bit capture)  |  |  |  |  |

| 0100                         | 1                     | Every 4th Rising (32-bit capture)  |  |  |  |  |

| 0101                         | 0                     | Every 16th Rising (16-bit capture) |  |  |  |  |

| 0101                         | 1                     | Every 16th Rising (32-bit capture) |  |  |  |  |

FIGURE 13-6: INPUT CAPTURE x BLOCK DIAGRAM

#### REGISTER 16-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| _      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits

Contains a value from 0 to 5.

bit 11-8 MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits

Contains a value from 0 to 9.

bit 7 **Unimplemented:** Read as '0'

bit 6-4 SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits

Contains a value from 0 to 5.

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits

Contains a value from 0 to 9.

#### 16.3 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value, loaded into the lower half of RCFGCAL, is multiplied by four and will be either added or subtracted from the RTCC timer, once every minute. Refer to the steps below for RTCC calibration:

- Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- Once the error is known, it must be converted to the number of error clock pulses per minute.

- a) If the oscillator is faster than ideal (negative result from Step 2), the RCFGCAL register value must be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

- b) If the oscillator is slower than ideal (positive result from Step 2), the RCFGCAL register value must be positive. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

#### **EQUATION 16-1:**

(Ideal Frequency† – Measured Frequency) \* 60 = Clocks per Minute

† Ideal Frequency = 32,768 Hz

Writes to the lower half of the RCFGCAL register should only occur when the timer is turned off, or immediately after the rising edge of the seconds pulse, except when SECONDS = 00, 15, 30 or 45. This is due to the auto-adjust of the RTCC at 15 second intervals.

Note:

It is up to the user to include, in the error value, the initial error of the crystal: drift due to temperature and drift due to crystal aging.

### 16.4 Alarm

- · Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>)

- One-time alarm and repeat alarm options are available

#### 16.4.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVAL should only take place when ALRMEN = 0.

As shown in Figure 16-2, the interval selection of the alarm is configured through the AMASKx bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The amount of times this occurs, once the alarm is enabled, is stored in the ARPT<7:0> bits (ALCFGRPT<7:0>). When the value of the ARPTx bits equals 00h and the CHIME bit (ALCFGRPT<14>) is cleared, the repeat function is disabled, and only a single alarm will occur. The alarm can be repeated up to 255 times by loading ARPT<7:0> with FFh.

After each alarm is issued, the value of the ARPTx bits is decremented by one. Once the value has reached 00h, the alarm will be issued one last time, after which, the ALRMEN bit will be cleared automatically and the alarm will turn off.

Indefinite repetition of the alarm can occur if the CHIME bit = 1. Instead of the alarm being disabled when the value of the ARPTx bits reaches 00h, it rolls over to FFh and continues counting indefinitely while CHIME is set.

### 16.4.2 ALARM INTERRUPT

At every alarm event, an interrupt is generated. In addition, an alarm pulse output is provided that operates at half the frequency of the alarm. This output is completely synchronous to the RTCC clock and can be used as a Trigger clock to other peripherals.

Note:

Changing any of the registers, other than the RCFGCAL and ALCFGRPT registers, and the CHIME bit while the alarm is enabled (ALRMEN = 1), can result in a false alarm event leading to a false alarm interrupt. To avoid a false alarm event, the timer and alarm values should only be changed while the alarm is disabled (ALRMEN = 0). It is recommended that the ALCFGRPT register and CHIME bit be changed when RTCSYNC = 0.

### REGISTER 19-1: AD1CON1: A/DA/D CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|--------|-----|-----|--------|-------|-------|

| ADON   | _   | ADSIDL | _   | _   | MODE12 | FORM1 | FORM0 |

| bit 15 |     |        |     |     |        |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0, HSC | R/C-0, HSC |

|-------|-------|-------|-------|-----|-------|------------|------------|

| SSRC3 | SSRC2 | SSRC1 | SSRC0 | _   | ASAM  | SAMP       | DONE       |

| bit 7 |       |       |       |     |       |            | bit 0      |

| Legend:           | C = Clearable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | HSC = Hardware Settable/C   | learable bit       |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 ADON: A/D Operating Mode bit

1 = A/D Converter is operating

0 = A/D Converter is off

bit 14 Unimplemented: Read as '0'

bit 13 ADSIDL: A/D Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-11 **Unimplemented:** Read as '0'

bit 10 MODE12: 12-Bit A/D Operation Mode bit

1 = 12-bit A/D operation0 = 10-bit A/D operation

bit 9-8 **FORM<1:0>:** Data Output Format bits (see the following formats)

11 = Fractional result, signed, left justified

10 = Absolute fractional result, unsigned, left justified

01 = Decimal result, signed, right justified

00 = Absolute decimal result, unsigned, right justified

bit 7-4 SSRC<3:0>: Sample Clock Source Select bits

1111 = Reserved

•

\_

1101 = Reserved

1100 = CLC2 event ends sampling and starts conversion

1011 = SCCP4 Compare Event (CCP4IF) ends sampling and starts conversion

1010 = MCCP3 Compare Event (CCP3IF) ends sampling and starts conversion

1001 = MCCP2 Compare Event (CCP2IF) ends sampling and starts conversion

1000 = CLC1 event ends sampling and starts conversion

0111 = Internal counter ends sampling and starts conversion (auto-convert)

0110 = TMR1 Sleep mode Trigger event ends sampling and starts conversion<sup>(1)</sup>

0101 = TMR1 event ends sampling and starts conversion

0100 = CTMU event ends sampling and starts conversion

0011 = SCCP5 Compare Event (CCP5IF) ends sampling and starts conversion

0010 = MCCP1 Compare Event (CCP1IF) ends sampling and starts conversion

0001 = INTO event ends sampling and starts conversion

0000 = Clearing the Sample bit ends sampling and starts conversion

**Note 1:** This version of the TMR1 Trigger allows A/D conversions to be triggered from TMR1 while the device is operating in Sleep mode. The SSRC<3:0> = 0101 option allows conversions to be triggered in Run or Idle modes only.

### REGISTER 19-4: AD1CON5: A/D CONTROL REGISTER 5

| R/W-0               | R/W-0 | R/W-0  | R/W-0 | r-0 | U-0 | R/W-0  | R/W-0  |

|---------------------|-------|--------|-------|-----|-----|--------|--------|

| ASEN <sup>(1)</sup> | LPEN  | CTMREQ | BGREQ | r   | _   | ASINT1 | ASINT0 |

| bit 15              |       |        |       |     |     |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | WM1   | WM0   | CM1   | CM0   |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           | r = Reserved bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

- bit 15 **ASEN:** A/D Auto-Scan Enable bit<sup>(1)</sup>

- 1 = Auto-scan is enabled

- 0 = Auto-scan is disabled

- bit 14 LPEN: A/D Low-Power Enable bit

- 1 = Returns to Low-Power mode after scan

- 0 = Remains in Full-Power mode after scan

- bit 13 **CTMREQ:** CTMU Request bit

- 1 = CTMU is enabled when the A/D is enabled and active

- 0 = CTMU is not enabled by the A/D

- bit 12 BGREQ: Band Gap Request bit

- 1 = Band gap is enabled when the A/D is enabled and active

- 0 = Band gap is not enabled by the A/D

- bit 11 Reserved: Maintain as '0'

- bit 10 Unimplemented: Read as '0'

- bit 9-8 ASINT<1:0>: Auto-Scan (Threshold Detect) Interrupt Mode bits

- 11 = Interrupt after a Threshold Detect sequence has completed and a valid compare has occurred

- 10 = Interrupt after a valid compare has occurred

- 01 = Interrupt after a Threshold Detect sequence has completed

- 00 = No interrupt

- bit 7-4 Unimplemented: Read as '0'

- bit 3-2 WM<1:0>: A/D Write Mode bits

- 11 = Reserved

- 10 = Auto-compare only (conversion results are not saved, but interrupts are generated when a valid match, as defined by the CMx and ASINTx bits, occurs)

- 01 = Convert and save (conversion results are saved to locations as determined by the register bits when a match, as defined by the CMx bits, occurs)

- 00 = Legacy operation (conversion data is saved to a location determined by the buffer register bits)

- bit 1-0 CM<1:0>: A/D Compare Mode bits

- 11 = Outside Window mode (valid match occurs if the conversion result is outside of the window defined by the corresponding buffer pair)

- 10 = Inside Window mode (valid match occurs if the conversion result is inside the window defined by the corresponding buffer pair)

- 01 = Greater Than mode (valid match occurs if the result is greater than the value in the corresponding buffer register)

- 00 = Less Than mode (valid match occurs if the result is less than the value in the corresponding buffer register)

- Note 1: When using auto-scan with Threshold Detect (ASEN = 1), do not configure the sample clock source to Auto-Convert mode (SSRC<3:0> = 7). Any other available SSRC selection is valid. To use auto-convert as the sample clock source (SSRC<3:0> = 7), make sure ASEN is cleared.

NOTES:

TABLE 27-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |                |         | Operating temperatu |       | <b>2.0V</b> to -40°C ≤ | : 1.8V to 3.6V (PIC24F16KMXXX)<br>2.0V to 5.5V (PIC24FV16KMXXX)<br>-40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +125°C for Extended |  |  |

|--------------------|----------------|---------|---------------------|-------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter No.      | Device         | Typical | Max                 | Units |                        | Conditions                                                                                                                               |  |  |

| IDD Current        |                |         |                     |       |                        |                                                                                                                                          |  |  |

| D20                | PIC24FV16KMXXX | 269     | 450                 | μΑ    | 2.0V                   |                                                                                                                                          |  |  |

|                    |                | 465     | 830                 | μA    | 5.0V                   | 0.5 MIPS,                                                                                                                                |  |  |

|                    | PIC24F16KMXXX  | 200     | 330                 | μA    | 1.8V                   | Fosc = 1 MHz <sup>(1)</sup>                                                                                                              |  |  |

|                    |                | 410     | 750                 | μΑ    | 3.3V                   |                                                                                                                                          |  |  |

| DC22               | PIC24FV16KMXXX | 490     | _                   | μA    | 2.0V                   |                                                                                                                                          |  |  |

|                    |                | 880     | _                   | μA    | 5.0V                   | 1 MIPS,                                                                                                                                  |  |  |

|                    | PIC24F16KMXXX  | 407     | 1                   | μΑ    | 1.8V                   | Fosc = 2 MHz <sup>(1)</sup>                                                                                                              |  |  |

|                    |                | 800     | _                   | μA    | 3.3V                   |                                                                                                                                          |  |  |

| DC24               | PIC24FV16KMXXX | 13.0    | 15.0                | mA    | 5.0V                   | 16 MIPS,                                                                                                                                 |  |  |

|                    | PIC24F16KMXXX  | 12.0    | 13.0                | mA    | 3.3V                   | Fosc = 32 MHz <sup>(1)</sup>                                                                                                             |  |  |

| DC26               | PIC24FV16KMXXX | 2.0     | _                   | mA    | 2.0V                   |                                                                                                                                          |  |  |

|                    |                | 3.5     | 1                   | mA    | 5.0V                   | FRC (4 MIPS),                                                                                                                            |  |  |

|                    | PIC24F16KMXXX  | 1.80    | _                   | mA    | 1.8V                   | Fosc = 8 MHz                                                                                                                             |  |  |

|                    |                | 3.40    |                     | mA    | 3.3V                   |                                                                                                                                          |  |  |

| DC30               | PIC24FV16KMXXX | 48.0    | 250                 | μΑ    | 2.0V                   |                                                                                                                                          |  |  |

|                    |                | 75.0    | 275                 | μΑ    | 5.0V                   | LPRC (15.5 KIPS),                                                                                                                        |  |  |

|                    | PIC24F16KMXXX  | 8.1     | 28.0                | μΑ    | 1.8V                   | Fosc = 31 kHz                                                                                                                            |  |  |

|                    |                | 13.50   | 55.00               | μA    | 3.3V                   |                                                                                                                                          |  |  |

**Legend:** Unshaded rows represent PIC24F16KMXXX devices and shaded rows represent PIC24FV16KMXXX devices.

**Note 1:** The oscillator is in External Clock mode (FOSCSEL<2:0> = 010, FOSC<1:0> = 00).

TABLE 27-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

| DC CHARA         | CTERISTICS            | Standard C             |      | 24F16KM204)<br>24FV16KM204)<br>C for Industrial<br>°C for Extended |            |                           |  |  |

|------------------|-----------------------|------------------------|------|--------------------------------------------------------------------|------------|---------------------------|--|--|

| Parameter<br>No. | Device                | Typical <sup>(1)</sup> | Max  | Units                                                              | Conditions |                           |  |  |

| Module Diff      | erential Current (∆IF | PD) <sup>(3)</sup>     |      |                                                                    |            |                           |  |  |

| DC71             | PIC24FV16KMXXX        | 0.50                   | _    | μA                                                                 | 2.0V       |                           |  |  |

|                  |                       | 0.70                   | 1.5  | μA                                                                 | 5.0V       | Watchdog Timer Current:   |  |  |

|                  | PIC24F16KMXXX         | 0.50                   | _    | μA                                                                 | 1.8V       | Current.<br>∧WDT          |  |  |

|                  |                       | 0.70                   | 1.5  | μA                                                                 | 3.3V       |                           |  |  |

| DC72             | PIC24FV16KMXXX        | 0.80                   | _    | μA                                                                 | 2.0V       | 32 kHz Crystal with RTCC, |  |  |

|                  |                       | 1.50                   | 2.0  | μA                                                                 | 5.0V       | DSWDT or Timer1:          |  |  |

|                  | PIC24F16KMXXX         | 0.70                   | _    | μA                                                                 | 1.8V       | ΔSOSC                     |  |  |

|                  |                       | 1.0                    | 1.5  | μA                                                                 | 3.3V       | (SOSCSEL = 0)             |  |  |

| DC75             | PIC24FV16KMXXX        | 5.4                    | _    | μA                                                                 | 2.0V       |                           |  |  |

|                  |                       | 8.1                    | 14.0 | μA                                                                 | 5.0V       | ΔHLVD                     |  |  |

|                  | PIC24F16KMXXX         | 4.9                    | _    | μA                                                                 | 1.8V       | ΔΠΕΥΟ                     |  |  |

|                  |                       | 7.5                    | 14.0 | μA                                                                 | 3.3V       |                           |  |  |

| DC76             | PIC24FV16KMXXX        | 5.6                    | _    | μA                                                                 | 2.0V       |                           |  |  |

|                  |                       | 6.5                    | 11.2 | μA                                                                 | 5.0V       | ΔBOR                      |  |  |

|                  | PIC24F16KMXXX         | 5.6                    | _    | μA                                                                 | 1.8V       | ДВОК                      |  |  |

|                  |                       | 6.0                    | 11.2 | μA                                                                 | 3.3V       |                           |  |  |

| DC78             | PIC24FV16KMXXX        | 0.03                   | _    | μA                                                                 | 2.0V       |                           |  |  |

|                  |                       | 0.05                   | 0.3  | μA                                                                 | 5.0V       | Low-Power BOR:            |  |  |

|                  | PIC24F16KMXXX         | 0.03                   | _    | μA                                                                 | 1.8V       | ΔLPBOR                    |  |  |

|                  |                       | 0.05                   | 0.3  | μA                                                                 | 3.3V       |                           |  |  |

Legend: Unshaded rows represent PIC24F16KMXXX devices and shaded rows represent PIC24FV16KMXXX devices.

- **Note 1:** Data in the Typical column is at 3.3V, +25°C (PIC24F16KMXXX) or 5.0V, +25°C (PIC24FV16KMXXX) unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as outputs and set low. PMSLP is set to '0' and WDT, etc., are all switched off.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

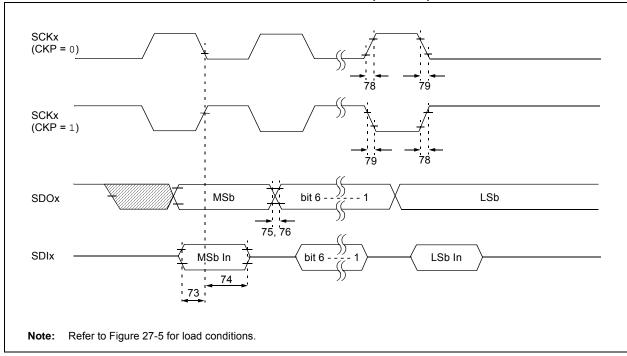

FIGURE 27-11: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

TABLE 27-29: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                             | Min | Max | Units | Conditions |

|--------------|-----------------------|--------------------------------------------|-----|-----|-------|------------|

| 73           | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 20  | _   | ns    |            |

| 74           | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 40  | _   | ns    |            |

| 75           | TDOR                  | SDOx Data Output Rise Time                 | _   | 25  | ns    |            |

| 76           | TDOF                  | SDOx Data Output Fall Time                 | _   | 25  | ns    |            |

| 78           | TscR                  | SCKx Output Rise Time (Master mode)        | _   | 25  | ns    |            |

| 79           | TscF                  | SCKx Output Fall Time (Master mode)        | _   | 25  | ns    |            |

|              | FSCK                  | SCKx Frequency                             | _   | 10  | MHz   |            |

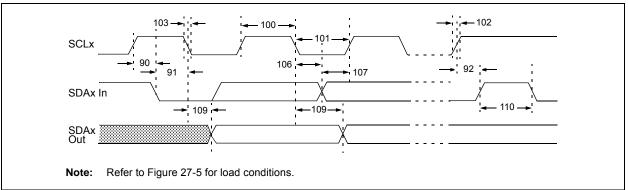

### FIGURE 27-18: MSSPx I<sup>2</sup>C™ BUS DATA TIMING

### TABLE 27-36: I<sup>2</sup>C™ BUS DATA REQUIREMENTS (MASTER MODE)

| Param.<br>No. | Symbol  | Charac           | teristic     | Min              | Max  | Units | Conditions                          |  |

|---------------|---------|------------------|--------------|------------------|------|-------|-------------------------------------|--|

| 100           | THIGH   | Clock High Time  | 100 kHz mode | 2(Tosc)(BRG + 1) |      | -     |                                     |  |

|               |         |                  | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                     |  |

| 101           | TLOW    | Clock Low Time   | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                     |  |

|               |         |                  | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                     |  |

| 102           | Tr      | SDAx and SCLx    | 100 kHz mode | _                | 1000 | ns    | CB is specified to be from          |  |

|               |         | Rise Time        | 400 kHz mode | 20 + 0.1 CB      | 300  | ns    | 10 to 400 pF                        |  |

| 103           | TF      | SDAx and SCLx    | 100 kHz mode | _                | 300  | ns    | CB is specified to be from          |  |

|               |         | Fall Time        | 400 kHz mode | 20 + 0.1 CB      | 300  | ns    | 10 to 400 pF                        |  |

| 90            | Tsu:sta | Start Condition  | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | Only relevant for Repeated          |  |

|               |         | Setup Time       | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | Start condition                     |  |

| 91            | THD:STA | Start Condition  | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | After this period, the first        |  |

|               |         | Hold Time        | 400 kHz mode | 2(Tosc)(BRG + 1) | _    |       | clock pulse is generated            |  |

| 106           | THD:DAT | Data Input       | 100 kHz mode | 0                | _    | ns    |                                     |  |

|               |         | Hold Time        | 400 kHz mode | 0                | 0.9  | μS    |                                     |  |

| 107           | TSU:DAT | Data Input       | 100 kHz mode | 250              | _    | ns    | (Note 1)                            |  |

|               |         | Setup Time       | 400 kHz mode | 100              | _    | ns    |                                     |  |

| 92            | Tsu:sto | Stop Condition   | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                     |  |

|               |         | Setup Time       | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                     |  |

| 109           | TAA     | Output Valid     | 100 kHz mode | _                | 3500 | ns    |                                     |  |

|               |         | from Clock       | 400 kHz mode | _                | 1000 | ns    |                                     |  |

| 110           | TBUF    | Bus Free Time    | 100 kHz mode | 4.7              | _    | μS    | Time the bus must be free           |  |

|               |         |                  | 400 kHz mode | 1.3              | _    | μS    | before a new transmission can start |  |

| D102          | Св      | Bus Capacitive L | oading       |                  | 400  | pF    |                                     |  |

Note 1: A Fast mode I²C bus device can be used in a Standard mode I²C bus system, but Parameter 107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, Parameter 102 + Parameter 107 = 1000 + 250 = 1250 ns (for 100 kHz mode), before the SCLx line is released.

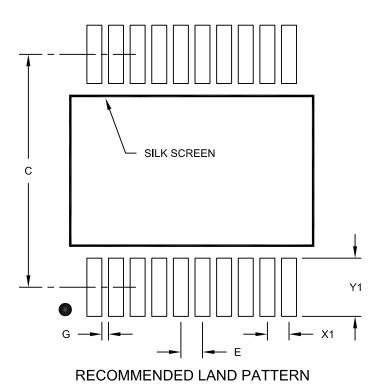

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N   | <b>II</b> LLIMETER | S    |      |  |

|--------------------------|-----|--------------------|------|------|--|

| Dimension                | MIN | NOM                | MAX  |      |  |

| Contact Pitch            | Е   | 0.65 BSC           |      |      |  |

| Contact Pad Spacing      | С   |                    | 7.20 |      |  |

| Contact Pad Width (X20)  | X1  |                    |      | 0.45 |  |

| Contact Pad Length (X20) | Y1  |                    |      | 1.75 |  |

| Distance Between Pads    | G   | 0.20               |      |      |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

### **INDEX**

| A                                                 |      | MCLR Pin Connections Example                    | 30  |

|---------------------------------------------------|------|-------------------------------------------------|-----|

| A/D                                               |      | MSSPx (I <sup>2</sup> C Master Mode)            | 161 |

| Buffer Data Formats                               | 225  | MSSPx (I <sup>2</sup> C Mode)                   | 161 |

| Control Registers                                 |      | MSSPx (SPI Mode)                                | 160 |

| AD1CHITH/L                                        |      | On-Chip Voltage Regulator Connections           | 257 |

| AD1CHS                                            |      | Output Compare x Module                         | 147 |

| AD1CON1                                           |      | PIC24F CPU Core                                 | 36  |

| AD1CON2                                           |      | PIC24FXXXXX Family (General)                    | 19  |

| AD1CON3                                           |      | PSV Operation                                   | 66  |

| AD1CON5                                           |      | Recommended Minimum Connections                 | 29  |

| AD1CSSH/L                                         |      | Reset System                                    | 79  |

| AD1CTMENH/L                                       |      | RTCC Module                                     | 181 |

| Sampling Requirements                             |      | Series Resistor                                 | 132 |

| Transfer Function                                 |      | Shared I/O Port Structure                       | 137 |

| AC Characteristics                                | 224  | Simplified Single DACx Module                   | 229 |

| 8-Bit DAC Specifications                          | 296  | Simplified UARTx                                | 173 |

| A/D Conversion Requirements                       |      | Single Operational Amplifier                    | 233 |

| A/D Module Specifications                         |      | SPI Master/Slave Connection                     | 160 |

| Capacitive Loading Requirements on                | 234  | Suggested Oscillator Circuit Placement          | 33  |

| Output Pins                                       | 270  | System Clock                                    | 121 |

| CLKO and I/O Requirements                         |      | Table Register Addressing                       | 67  |

| External Clock Requirements                       |      | Timer Clock Generator                           | 144 |

| Internal RC Accuracy                              |      | Watchdog Timer (WDT)                            | 258 |

| Internal RC Oscillator Specifications             |      | Brown-out Reset                                 |     |

| Load Conditions and Requirements                  |      | Trip Points                                     | 269 |

| PLL Clock Specification                           |      | С                                               |     |

| Reset, Watchdog Timer. Oscillator Start-up Tir    |      |                                                 |     |

| Power-up Timer, Brown-out Reset                   | nci, | C Compilers                                     |     |

| Requirements                                      | 284  | MPLAB XC Compilers                              | 262 |

| Temperature and Voltage Specifications            |      | Capture/Compare/PWM/Timer                       |     |

| Assembler                                         | 210  | Auxiliary Output                                |     |

| MPASM Assembler                                   | 262  | General Purpose Timer                           |     |

|                                                   | 202  | Input Capture Mode                              |     |

| В                                                 |      | Output Compare Mode                             |     |

| Block Diagrams                                    |      | Synchronization Sources                         |     |

| 12-Bit A/D Converter                              | 210  | Time Base Generator                             |     |

| 12-Bit A/D Converter Analog Input Model           |      | Capture/Compare/PWM/Timer (MCCP, SCCP)          | 143 |

| 16-Bit Timer1                                     |      | Charge Time Measurement Unit. See CTMU.         |     |

| 32-Bit Timer Mode                                 |      | CLC                                             |     |

| Accessing Program Memory with                     |      | Control Registers                               | 198 |

| Table Instructions                                | 65   | Code Examples                                   |     |

| CALL Stack Frame                                  |      | Assembly Code Sequence for Clock Switching      |     |

| CLCx Input Source Selection                       |      | C Code Power-Saving Entry                       |     |

| CLCx Logic Function Combinatorial Options         |      | C Code Sequence for Clock Switching             |     |

| CLCx Module                                       |      | Data EEPROM Bulk Erase                          |     |

| Comparator Voltage Reference                      |      | Data EEPROM Unlock Sequence                     | 73  |

| Comparator x Module                               |      | Erasing a Program Memory Row,                   |     |

| Conceptual MCCPx/SCCPx Modules                    |      | Assembly Language                               |     |

| CPU Programmer's Model                            |      | Erasing a Program Memory Row, C Language        |     |

| CTMU Connections, Internal Configuration for      |      | I/O Port Write/Read                             | 140 |

| Capacitance Measurement                           |      | Initiating a Programming Sequence,              |     |

| CTMU Connections, Internal Configuration for      |      | Assembly Language                               |     |

| Pulse Delay Generation                            |      | Initiating a Programming Sequence, C Language . |     |

| CTMU Connections, Internal Configuration for      |      | Loading the Write Buffers, Assembly Language    |     |

| Time Measurement                                  |      | Loading the Write Buffers, C Language           | 71  |

| Data Access from Program Space Address Ge         |      | Reading Data EEPROM Using                       |     |

| 64                                                |      | TBLRD Command                                   |     |

| Data EEPROM Addressing with TBLPAG and            |      | Setting the RTCWREN Bit in 'C'                  |     |

| NVM Registers                                     | 75   | Setting the RTCWREN Bit in Assembly             |     |

| Dual 16-Bit Timer Mode                            |      | Single-Word Erase                               |     |

| High/Low-Voltage Detect (HLVD)                    |      | Single-Word Write to Data EEPROM                |     |

| Individual Comparator Configurations              | 236  | Ultra Low-Power Wake-up Initialization          |     |

| Input Capture x Module                            |      | Code Protection                                 |     |

| L 22 - 25 - 22 - 23 - 23 - 24 - 24 - 24 - 24 - 24 |      | Comparator                                      | 225 |

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support