#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХЕ

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

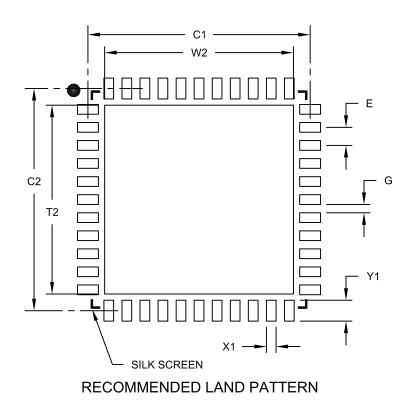

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km102t-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                |      | N                     | lemory       | 1               |                   |              |                  |      |      | Pe                  | riphe     | rals   |             |      |      |     |           |

|----------------|------|-----------------------|--------------|-----------------|-------------------|--------------|------------------|------|------|---------------------|-----------|--------|-------------|------|------|-----|-----------|

| Device         | Pins | Flash Program (bytes) | SRAM (bytes) | EE Data (bytes) | Voltage Range (V) | 16-Bit Timer | 16-Bit MCCP/SCCP | MSSP | UART | 12-Bit A/D Channels | 8-Bit DAC | Op Amp | Comparators | CTMU | RTCC | CLC | ICD BRKPT |

|                |      |                       |              |                 |                   | 5V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24FV16KM204 | 44   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM202 | 28   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM204 | 44   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM202 | 28   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM104 | 44   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 22                  | —         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV16KM102 | 28   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM102 | 28   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM101 | 20   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 16                  | _         | -      | 1           | Yes  | _    | 1   | 3         |

|                |      |                       |              |                 |                   | 3V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24F16KM204  | 44   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM202  | 28   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM204  | 44   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM202  | 28   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM104  | 44   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 22                  | _         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F16KM102  | 28   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24F08KM102  | 28   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | —         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F08KM101  | 20   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 16                  |           |        | 1           | Yes  | _    | 1   | 3         |

#### **Peripheral Features**

- High-Current Sink/Source, 18 mA/18 mA All Ports

- Independent Ultra Low-Power, 32 kHz Timer Oscillator

- Up to Two Master Synchronous Serial Ports (MSSPs) with SPI and I<sup>2</sup>C™ modes:

In SPI mode:

- User-configurable SCKx and SDOx pin outputs

- Daisy-chaining of SPI slave devices

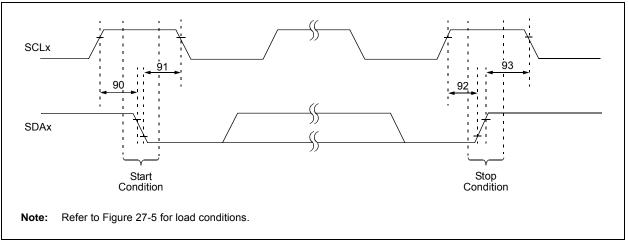

#### In I<sup>2</sup>C mode:

- Serial clock synchronization (clock stretching)

- Bus collision detection and will arbitrate accordingly

- Support for 16-bit read/write interface

- Up to Two Enhanced Addressable UARTs:

- LIN/J2602 bus support (auto-wake-up, Auto-Baud Detect, Break character support)

- High and low speed (SCI)

- IrDA<sup>®</sup> mode (hardware encoder/decoder function)

- Two External Interrupt Pins

- Hardware Real-Time Clock and Calendar (RTCC)

- Configurable Reference Clock Output (REFO)

- Two Configurable Logic Cells (CLC)

- Up to Two Single Output Capture/Compare/PWM (SCCP) modules and up to Three Multiple Output Capture/Compare/PWM (MCCP) modules

#### **Special Microcontroller Features**

- Wide Operating Voltage Range Options:

- 1.8V to 3.6V (PIC24F devices)

- 2.0V to 5.0V (PIC24FV devices)

- Selectable Power Management modes:

- Idle: CPU shuts down, allowing for significant power reduction

- Sleep: CPU and peripherals shut down for substantial power reduction and fast wake-up

- Retention Sleep mode: PIC24FV devices can enter Sleep mode, employing the Retention Regulator, further reducing power consumption

- Doze: CPU can run at a lower frequency than peripherals, a user-programmable feature

- Alternate Clock modes allow on-the-fly switching to a lower clock speed for selective power reduction

- · Fail-Safe Clock Monitor:

- Detects clock failure and switches to on-chip, low-power RC Oscillator

- Ultra Low-Power Wake-up Pin Provides an External Trigger for Wake from Sleep

- 10,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- 100,000 Erase/Write Cycle Endurance Data EEPROM, Typical

- Flash and Data EEPROM Data Retention: 20 Years Minimum

- Self-Programmable under Software Control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its Own On-Chip RC Oscillator for Reliable Operation

- On-Chip Regulator for 5V Operation

- Selectable Windowed WDT Feature

- Selectable Oscillator Options including:

4x Phase Locked Loop (PLL)

- 8 MHz (FRC) Internal RC Oscillator:

- HS/EC, High-Speed Crystal/Resonator Oscillator or External Clock

- In-Circuit Serial Programming™ (ICSP™) and In-Circuit Emulation (ICE) via Two Pins

- In-Circuit Debugging

- Programmable High/Low-Voltage Detect (HLVD) module

- Programmable Brown-out Reset (BOR):

- Software enable feature

- Configurable shutdown in Sleep

- Auto-configures power mode and sensitivity based on device operating speed

- LPBOR available for re-arming of the POR

## **Pin Diagrams**

| 20-Pin PDIP/SSOP/SOIC | RA5       1       20       VDD         RA0       2       19       VSs         RA1       3       18       RB15         RB0       4       17       RB14         RB1       5       RB12         RA2       6       9       16         RA3       8       00       VDC         RA4       10       11       RB7 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dia |                                               | Pin Features                                  |  |  |  |  |  |  |

|-----|-----------------------------------------------|-----------------------------------------------|--|--|--|--|--|--|

| Pin | PIC24F08KM101                                 | PIC24FVKM08KM101                              |  |  |  |  |  |  |

| 1   | MCLR/Vpp/RA5                                  | MCLR/VPP/RA5                                  |  |  |  |  |  |  |

| 2   | PGEC2/CVREF+/VREF+/AN0/CN2/RA0                |                                               |  |  |  |  |  |  |

| 3   | PGED2/CVREF-/VREF-/AN1/CN3/RA1                | PGED2/CVREF-/VREF-/AN1/CN3/RA1                |  |  |  |  |  |  |

| 4   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0      |                                               |  |  |  |  |  |  |

| 5   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                |                                               |  |  |  |  |  |  |

| 6   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                 |                                               |  |  |  |  |  |  |

| 7   | OSCI/CLKI/AN13/C1INB/CN30/RA2                 |                                               |  |  |  |  |  |  |

| 8   | OSCO/CLKO/AN14/C1INA/CN29/RA3                 |                                               |  |  |  |  |  |  |

| 9   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4               |                                               |  |  |  |  |  |  |

| 10  | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/    | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/RA4 |  |  |  |  |  |  |

| 11  | AN19/U1TX/CTED1/INT0/CN23/RB7                 | AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7        |  |  |  |  |  |  |

| 12  | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8          |                                               |  |  |  |  |  |  |

| 13  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4   | /CN21/RB9                                     |  |  |  |  |  |  |

| 14  | IC1/OC1A/INT2/CN8/RA6                         | VCAP OR VDDCORE                               |  |  |  |  |  |  |

| 15  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12         | AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12    |  |  |  |  |  |  |

| 16  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13           |                                               |  |  |  |  |  |  |

| 17  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RE | 814                                           |  |  |  |  |  |  |

| 18  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15            |                                               |  |  |  |  |  |  |

| 19  | Vss/AVss                                      |                                               |  |  |  |  |  |  |

| 20  | Vdd/AVdd                                      |                                               |  |  |  |  |  |  |

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | F                                | Pin Numb      | er                     |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| MCLR     | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Ι   | ST     | Master Clear (Device Reset) Input (active-low) |

| OA1INA   | _                                | 5                                | 2             | 22                     | 24             |                                  | 5                                | 2             | 22                     | 24             | Ι   | ANA    | Op Amp 1 Input A                               |

| OA1INB   | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | Ι   | ANA    | Op Amp 1 Input B                               |

| OA1INC   | _                                | 24                               | 21            | 11                     | 12             | _                                | 24                               | 21            | 11                     | 12             | Ι   | ANA    | Op Amp 1 Input C                               |

| OA1IND   | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | Ι   | ANA    | Op Amp 1 Input D                               |

| OA1OUT   | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | 0   | ANA    | Op Amp 1 Analog Output                         |

| OA2INA   | _                                | 5                                | 2             | 22                     | 24             | _                                | 5                                | 2             | 22                     | 24             | Ι   | ANA    | Op Amp 2 Input A                               |

| OA2INB   | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | Ι   | ANA    | Op Amp 2 Input B                               |

| OA2INC   | _                                | 24                               | 21            | 11                     | 12             | _                                | 24                               | 21            | 11                     | 12             | Ι   | ANA    | Op Amp 2 Input C                               |

| OA2IND   | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | Ι   | ANA    | Op Amp 2 Input D                               |

| OA2OUT   | _                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | 0   | ANA    | Op Amp 2 Analog Output                         |

| OC1A     | 14                               | 20                               | 17            | 7                      | 7              | 11                               | 16                               | 13            | 43                     | 47             | 0   | _      | MCCP1 Output Compare A                         |

| OC1B     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | 0   | _      | MCCP1 Output Compare B                         |

| OC1C     | 15                               | 21                               | 18            | 8                      | 9              | 15                               | 21                               | 18            | 8                      | 9              | 0   | _      | MCCP1 Output Compare C                         |

| OC1D     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   |        | MCCP1 Output Compare D                         |

| OC1E     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | 0   | _      | MCCP1 Output Compare E                         |

| OC1F     | _                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | 0   | _      | MCCP1 Output Compare F                         |

| OC2A     | 4                                | 22                               | 19            | 9                      | 10             | 4                                | 22                               | 19            | 9                      | 10             | 0   |        | MCCP2 Output Compare A                         |

| OC2B     | _                                | 23                               | 20            | 10                     | 11             |                                  | 23                               | 20            | 10                     | 11             | 0   | _      | MCCP2 Output Compare B                         |

| OC2C     | _                                |                                  | _             | 2                      | 2              |                                  |                                  |               | 2                      | 2              | 0   |        | MCCP2 Output Compare C                         |

| OC2D     | _                                |                                  | _             | 3                      | 3              |                                  |                                  |               | 3                      | 3              | 0   |        | MCCP2 Output Compare D                         |

| OC2E     | _                                |                                  | _             | 4                      | 4              |                                  |                                  |               | 4                      | 4              | 0   |        | MCCP2 Output Compare E                         |

| OC2F     | _                                |                                  | _             | 5                      | 5              |                                  |                                  |               | 5                      | 5              | 0   |        | MCCP2 Output Compare F                         |

| OC3A     | _                                | 21                               | 18            | 12                     | 13             |                                  | 21                               | 18            | 12                     | 13             | 0   | _      | MCCP3 Output Compare A                         |

| OC3B     | _                                | 24                               | 21            | 13                     | 14             | _                                | 24                               | 21            | 13                     | 14             | 0   | _      | MCCP3 Output Compare B                         |

| OC4      | _                                | 18                               | 15            | 1                      | 1              | _                                | 18                               | 15            | 1                      | 1              | 0   | _      | SCCP4 Output Compare                           |

| OC5      | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | 0   | _      | SCCP5 Output Compare                           |

| OCFA     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | Ι   | ST     | MCCP/SCCP Output Compare Fault Input A         |

| OCFB     | 16                               | 24                               | 21            | 32                     | 35             | 16                               | 24                               | 21            | 32                     | 35             | Ι   | ST     | MCCP/SCCP Output Compare Fault Input B         |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

# DS30003030B-page 24

#### TABLE 4-10: MCCP3 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9   | Bit 8       | Bit 7        | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------------------|-------|---------|--------|---------|--------|---------|---------|---------|-------------|--------------|--------------|---------|---------|---------|---------|---------|---------|---------------|

| CCP3CON1L <sup>(1)</sup> | 188h  | CCPON   | _      | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1 | CLKSEL0     | TMRPS1       | TMRPS0       | T32     | CCSEL   | MOD3    | MOD2    | MOD1    | MOD0    | 0000          |

| CCP3CON1H <sup>(1)</sup> | 18Ah  | OPSSRC  | RTRGEN | _       | _      | IOPS3   | IOPS2   | IOPS1   | IOPS0       | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1   | SYNC0   | 0000          |

| CCP3CON2L <sup>(1)</sup> | 18Ch  | PWMRSEN | ASDGM  | _       | SSDG   | _       | _       | _       | _           | ASDG7        | ASDG6        | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1   | ASDG0   | 0000          |

| CCP3CON2H <sup>(1)</sup> | 18Eh  | OENSYNC | _      | OCFEN   | OCEEN  | OCDEN   | OCCEN   | OCBEN   | OCAEN       | ICGSM1       | ICGSM0       | _       | AUXOUT1 | AUXOUT0 | ICS2    | ICS1    | ICS0    | 0100          |

| CCP3CON3L <sup>(1)</sup> | 190h  | _       | _      | _       | _      | _       | _       | _       | _           | _            | _            | DT5     | DT4     | DT3     | DT2     | DT1     | DT0     | 0000          |

| CCP3CON3H <sup>(1)</sup> | 192h  | OETRIG  | OSCNT2 | OSCNT1  | OSCNT0 | _       | OUTM2   | OUTM1   | OUTM0       | _            | _            | POLACE  | POLBDF  | PSSACE1 | PSSACE0 | PSSBDF1 | PSSBDF0 | 0000          |

| CCP3STAT <sup>(1)</sup>  | 194h  | _       | _      | _       | —      | _       | _       | _       | _           | CCPTRIG      | TRSET        | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV    | ICBNE   | 0000          |

| CCP3TMRL <sup>(1)</sup>  | 198h  |         |        |         |        |         |         | MCCF    | P3 Time Bas | se Register  | Low Word     |         |         |         |         | •       | •       | 0000          |

| CCP3TMRH <sup>(1)</sup>  | 19Ah  |         |        |         |        |         |         | MCCF    | 3 Time Bas  | e Register   | High Word    |         |         |         |         |         |         | 0000          |

| CCP3PRL <sup>(1)</sup>   | 19Ch  |         |        |         |        |         |         | MCCP3 1 | īme Base F  | Period Regis | ster Low Wor | d       |         |         |         |         |         | FFFF          |

| CCP3PRH <sup>(1)</sup>   | 19Eh  |         |        |         |        |         |         | МССРЗ Т | ime Base P  | eriod Regis  | ter High Wor | d       |         |         |         |         |         | FFFF          |

| CCP3RAL <sup>(1)</sup>   | 1A0h  |         |        |         |        |         |         | Οι      | Itput Compa | are 3 Data \ | Word A       |         |         |         |         |         |         | 0000          |

| CCP3RBL <sup>(1)</sup>   | 1A4h  |         |        |         |        |         |         | Οι      | Itput Compa | are 3 Data \ | Word B       |         |         |         |         |         |         | 0000          |

| CCP3BUFL <sup>(1)</sup>  | 1A8h  |         |        |         |        |         |         | Input   | Capture 3 [ | Data Buffer  | Low Word     |         |         |         |         |         |         | 0000          |

| CCP3BUFH <sup>(1)</sup>  | 1AAh  |         |        |         |        |         |         |         |             |              |              | 0000    |         |         |         |         |         |               |

$\label{eq:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:loge$

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### 6.4.1 ERASE DATA EEPROM

The data EEPROM can be fully erased, or can be partially erased, at three different sizes: one word, four words or eight words. The bits, NVMOP<1:0> (NVMCON<1:0>), decide the number of words to be erased. To erase partially from the data EEPROM, the following sequence must be followed:

- 1. Configure NVMCON to erase the required number of words: one, four or eight.

- 2. Load TBLPAG and WREG with the EEPROM address to be erased.

- 3. Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 4. Write the key sequence to NVMKEY.

- 5. Set the WR bit to begin the erase cycle.

- 6. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical erase sequence is provided in Example 6-2. This example shows how to do a one-word erase. Similarly, a four-word erase and an eight-word erase can be done. This example uses C library procedures to manage the Table Pointer (builtin\_tblpage and builtin\_tbloffset) and the Erase Page Pointer (builtin\_tblwt1). The memory unlock sequence (builtin\_write\_NVM) also sets the WR bit to initiate the operation and returns control when complete.

#### EXAMPLE 6-2: SINGLE-WORD ERASE

```

int __attribute__ ((space(eedata))) eeData = 0x1234;

/*_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the erase

_____

*/

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0 \times 4058;

// Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData); // Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData);

// Initizlize lower word of address

__builtin_tblwtl(offset, 0);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

__builtin_write_NVM();

// Issue Unlock Sequence & Start Write Cycle

while(NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

| U-0                          | U-0                                      | U-0                                                                                                                                     | U-0                             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|---------|

| _                            |                                          |                                                                                                                                         |                                 | _                | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| oit 15                       |                                          |                                                                                                                                         | •                               |                  |                  | •               | bit 8   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| U-0                          | R/W-1                                    | R/W-0                                                                                                                                   | R/W-0                           | U-0              | U-0              | U-0             | U-0     |

| —                            | U1ERIP2                                  | U1ERIP1                                                                                                                                 | U1ERIP0                         | —                | —                | —               | —       |

| bit 7                        |                                          |                                                                                                                                         |                                 |                  |                  |                 | bit 0   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| Legend:                      |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| R = Readab                   | ole bit                                  | W = Writable                                                                                                                            | bit                             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value a                 | at POR                                   | '1' = Bit is set                                                                                                                        |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8<br>bit 7<br>bit 6-4 | <pre>111 = Interru </pre>                | >: UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>>: UART1 Error<br>pt is Priority 7 ( | highest priority<br>abled<br>o' | interrupt)       |                  |                 |         |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '                                                             | abled                           | interrupt)       |                  |                 |         |

#### REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0                   | R/W-1                          | R/W-0                                | R/W-0             | U-0              | R/W-1             | R/W-0           | R/W-0   |

|-----------------------|--------------------------------|--------------------------------------|-------------------|------------------|-------------------|-----------------|---------|

| _                     | DAC2IP2                        | DAC2IP1                              | DAC2IP0           |                  | DAC1IP2           | DAC1IP1         | DAC1IP0 |

| bit 15                |                                |                                      |                   |                  |                   |                 | bit 8   |

| U-0                   | R/W-1                          | R/W-0                                | R/W-0             | U-0              | U-0               | U-0             | U-0     |

| _                     | CTMUIP2                        | CTMUIP1                              | CTMUIP0           | _                |                   | _               | _       |

| bit 7                 |                                |                                      |                   |                  |                   |                 | bit (   |

| Legend:               |                                |                                      |                   |                  |                   |                 |         |

| Legena.<br>R = Readab | le hit                         | W = Writable                         | hit               | II = Unimple     | mented bit, read  | las 'O'         |         |

| -n = Value a          |                                | '1' = Bit is set                     | on                | '0' = Bit is cle |                   | x = Bit is unkr |         |

|                       |                                |                                      |                   |                  | aleu              |                 |         |

| bit 15                | Unimplemen                     | ted: Read as '                       | )'                |                  |                   |                 |         |

| bit 14-12             | -                              |                                      |                   | 2 Event Interr   | upt Priority bits |                 |         |

|                       |                                | pt is Priority 7 (                   | •                 |                  | upt i nonty bits  |                 |         |

|                       | •                              |                                      | ingricor priority | ( interrupt)     |                   |                 |         |

|                       | •                              |                                      |                   |                  |                   |                 |         |

|                       | •                              |                                      |                   |                  |                   |                 |         |

|                       | 001 = Interru<br>000 = Interru | pt is Priority 1<br>pt source is dis | abled             |                  |                   |                 |         |

| bit 11                | Unimplemen                     | ted: Read as '                       | )'                |                  |                   |                 |         |

| bit 10-8              | DAC1IP<2:0>                    | -: Digital-to-Ana                    | alog Converter    | 1 Event Interr   | upt Priority bits |                 |         |

|                       | 111 = Interru                  | pt is Priority 7(                    | highest priority  | / interrupt)     |                   |                 |         |

|                       | •                              |                                      |                   |                  |                   |                 |         |

|                       | •                              |                                      |                   |                  |                   |                 |         |

|                       | •<br>001 = Interru             | nt is Priority 1                     |                   |                  |                   |                 |         |

|                       |                                | pt is Fridity 1                      | abled             |                  |                   |                 |         |

| bit 7                 | -                              | ted: Read as '                       |                   |                  |                   |                 |         |

| bit 6-4               | -                              | >: CTMU Interr                       |                   | s                |                   |                 |         |

|                       |                                | pt is Priority 7 (                   |                   |                  |                   |                 |         |

|                       | •                              |                                      |                   |                  |                   |                 |         |

|                       | •                              |                                      |                   |                  |                   |                 |         |

|                       | •                              |                                      |                   |                  |                   |                 |         |

|                       | 001 = Interru                  | pt is Priority 1<br>pt source is dis | ahlad             |                  |                   |                 |         |

| hit 2 0               |                                |                                      |                   |                  |                   |                 |         |

| bit 3-0               | ommplemen                      | ted: Read as '                       | J                 |                  |                   |                 |         |

#### REGISTER 8-32: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24FXXXXX family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator:

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The Primary Oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

#### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 25.1 "Configuration Bits"). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

## 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                      | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|------------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler<br>(LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                       | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)                 | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)      | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)      | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                              | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                              | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                              | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

## 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O ports, refer to the *"PIC24F Family Reference Manual"*, *"I/O Ports with Peripheral Pin Select (PPS)"* (DS39711). Note that the PIC24FV16KM204 family devices do not support Peripheral Pin Select features.

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 11.1 Parallel I/O (PIO) Ports

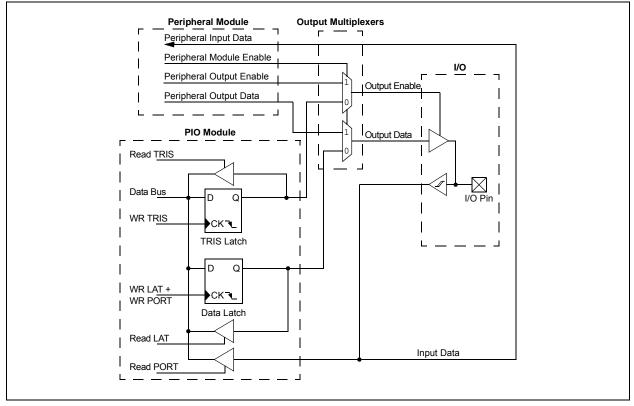

A Parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the Data Direction register bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LATx), read the latch. Writes to the latch, write the latch. Reads from the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

| R/W-0         | U-0                                                                                              | R/W-0                                                         | R/W-0                            | R/W-0                             | R/W-0                | R/W-0                                                  | R/W-0    |

|---------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|-----------------------------------|----------------------|--------------------------------------------------------|----------|

| OENSYNC       |                                                                                                  | OCFEN <sup>(1)</sup>                                          | OCEEN <sup>(1)</sup>             | OCDEN <sup>(1)</sup>              | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup>                                   | OCAEN    |

| bit 15        |                                                                                                  |                                                               |                                  |                                   |                      |                                                        | bit      |

| R/W-0         | R/W-0                                                                                            | U-0                                                           | R/W-0                            | R/W-0                             | R/W-0                | R/W-0                                                  | R/W-0    |

| ICGSM1        | ICGSM0                                                                                           | _                                                             | AUXOUT1                          | AUXOUT0                           | ICS2                 | ICS1                                                   | ICS0     |

| bit 7         |                                                                                                  |                                                               |                                  |                                   |                      | 1                                                      | bit      |

| Legend:       |                                                                                                  |                                                               |                                  |                                   |                      |                                                        |          |

| R = Readable  | e bit                                                                                            | W = Writable                                                  | bit                              | U = Unimplem                      | nented bit, read     | 1 as '0'                                               |          |

| -n = Value at | POR                                                                                              | '1' = Bit is set                                              |                                  | '0' = Bit is clea                 | ared                 | x = Bit is unkn                                        | own      |

| bit 15        | 1 = Update b                                                                                     | Dutput Enable S<br>by output enable<br>by output enable       | e bits occurs or                 | n the next Time                   | Base Reset or        | rollover                                               |          |

| bit 14        | Unimplemen                                                                                       | ted: Read as '                                                | )'                               |                                   |                      |                                                        |          |

| bit 13-8      | 1 = OCx pin<br>0 = OCx pin                                                                       |                                                               | the CCPx moded by the CCP        | dule and produc                   |                      | compare or PWI<br>e to the port log                    |          |

| bit 7-6       | ICGSM<1:0>                                                                                       | : Input Capture                                               | Gating Source                    | Mode Control                      | bits                 |                                                        |          |

|               | 01 = One-Sh<br>00 = Level-Se                                                                     | ot mode: Falling<br>ot mode: Rising                           | edge from gat<br>A high level fr | ting source ena<br>om gating sour | bles future cap      | pture events (IC<br>oture events (IC<br>future capture | DIS = 0) |

| bit 5         | Unimplemen                                                                                       | ted: Read as '                                                | )'                               |                                   |                      |                                                        |          |

| bit 4-3       | AUXOUT<1:0                                                                                       | <b>0&gt;:</b> Auxiliary Oເ                                    | tput Signal on                   | Event Selectio                    | n bits               |                                                        |          |

|               | 10 = Signal c                                                                                    | pture or output<br>output is defined<br>ise rollover eve<br>d | l by module op                   |                                   |                      | )                                                      |          |

| bit 2-0       | 111 = Unuse<br>110 = CLC2<br>101 = CLC1<br>100 = Unuse<br>011 = Comp<br>010 = Comp<br>001 = Comp | output<br>output                                              |                                  | 3                                 |                      |                                                        |          |

#### REGISTER 13-4: CCPxCON2H: CCPx CONTROL 2 HIGH REGISTERS

#### **Note 1:** OCFEN through OCBEN (bits<13:9>) are implemented in MCCPx modules only.

#### 16.2.4 RTCC CONTROL REGISTERS

## REGISTER 16-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                      | R-0, HSC                                                                                                                                                      | R-0, HSC                                                                                                              | R/W-0                                                                 | R/W-0                                                                  | R/W-0                                               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------|

| RTCEN <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                                                           | RTCWREN                                                                                                                                                                                                                                                                                                                                    | RTCSYNC                                                                                                                                                       | HALFSEC <sup>(3)</sup>                                                                                                | RTCOE                                                                 | RTCPTR1                                                                | RTCPTR0                                             |

| bit 15               |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |                                                                                                                       |                                                                       |                                                                        | bit 8                                               |

|                      |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |                                                                                                                       |                                                                       |                                                                        |                                                     |

| R/W-0                | R/W-0                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                         | R/W-0                                                                                                                 | R/W-0                                                                 | R/W-0                                                                  | R/W-0                                               |

| CAL7                 | CAL6                                                                                                                                                                                                                                                                                                                        | CAL5                                                                                                                                                                                                                                                                                                                                       | CAL4                                                                                                                                                          | CAL3                                                                                                                  | CAL2                                                                  | CAL1                                                                   | CAL0                                                |

| bit 7                |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |                                                                                                                       |                                                                       |                                                                        | bit C                                               |

| Legend:              |                                                                                                                                                                                                                                                                                                                             | HSC = Hardw                                                                                                                                                                                                                                                                                                                                | are Settable/C                                                                                                                                                | learable bit                                                                                                          |                                                                       |                                                                        |                                                     |

| R = Readable         | e bit                                                                                                                                                                                                                                                                                                                       | W = Writable I                                                                                                                                                                                                                                                                                                                             | oit                                                                                                                                                           | U = Unimplem                                                                                                          | ented bit, rea                                                        | d as '0'                                                               |                                                     |

| -n = Value at        | POR                                                                                                                                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               | '0' = Bit is clea                                                                                                     | red                                                                   | x = Bit is unkr                                                        | iown                                                |

|                      |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |                                                                                                                       |                                                                       |                                                                        |                                                     |

| bit 15               | RTCEN: RT                                                                                                                                                                                                                                                                                                                   | CC Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               |                                                                                                                                                               |                                                                                                                       |                                                                       |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                             | nodule is enable                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |                                                                                                                       |                                                                       |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                             | nodule is disable                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                             |                                                                                                                       |                                                                       |                                                                        |                                                     |

| bit 14               | •                                                                                                                                                                                                                                                                                                                           | nted: Read as '0                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |                                                                                                                       |                                                                       |                                                                        |                                                     |

| bit 13               |                                                                                                                                                                                                                                                                                                                             | RTCC Value Re                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                             |                                                                                                                       | , the upper                                                           |                                                                        |                                                     |