Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

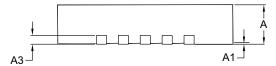

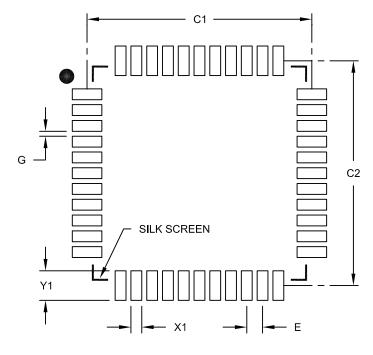

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km104-e-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

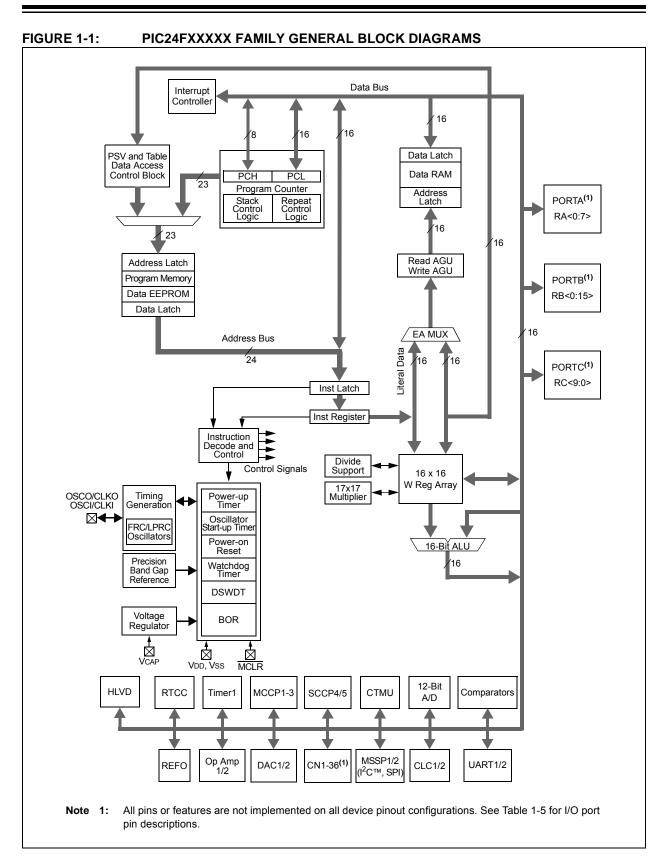

| TABLE 1-1: | DEVICE FEATURES FOR THE PIC24F16KM204 FAMILY |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| TABLE 1-1: DEVICE FEATURES FO                    | R THE PIC24F16                                                                                                                                      |               | •                      |                       |  |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------|-----------------------|--|--|--|--|

| Features                                         | PIC24F16KM204                                                                                                                                       | PIC24F08KM204 | PIC24F16KM202          | PIC24F08KM202         |  |  |  |  |

| Operating Frequency                              | DC-32 MHz                                                                                                                                           |               |                        |                       |  |  |  |  |

| Program Memory (bytes)                           | 16K                                                                                                                                                 | 8K            | 16K                    | 8K                    |  |  |  |  |

| Program Memory (instructions)                    | 5632                                                                                                                                                | 2816          | 5632                   | 2816                  |  |  |  |  |

| Data Memory (bytes)                              |                                                                                                                                                     | 20            | )48                    |                       |  |  |  |  |

| Data EEPROM Memory (bytes)                       |                                                                                                                                                     | 5             | 12                     |                       |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)       |                                                                                                                                                     | 40 (          | 36/4)                  |                       |  |  |  |  |

| Voltage Range                                    |                                                                                                                                                     | 1.8-          | 3.6V                   |                       |  |  |  |  |

| I/O Ports                                        | PORTA<<br>PORTB<<br>PORTC                                                                                                                           | :15:0>        | -                      | RTA<7:0><br>RTB<15:0> |  |  |  |  |

| Total I/O Pins                                   | 38                                                                                                                                                  |               |                        | 24                    |  |  |  |  |

| Timers                                           | (One 16-bit timer, f                                                                                                                                |               | l1<br>Ps with up to tv | vo 16/32 timers each) |  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP      |                                                                                                                                                     |               | 3<br>2                 |                       |  |  |  |  |

| Serial Communications<br>MSSP<br>UART            |                                                                                                                                                     |               | 2<br>2                 |                       |  |  |  |  |

| Input Change Notification Interrupt              | 37                                                                                                                                                  |               |                        | 23                    |  |  |  |  |

| 12-Bit Analog-to-Digital Module (input channels) | 22                                                                                                                                                  | 22            | 19                     | 19                    |  |  |  |  |

| Analog Comparators                               |                                                                                                                                                     | :             | 3                      |                       |  |  |  |  |

| 8-Bit Digital-to-Analog Converters               |                                                                                                                                                     |               | 2                      |                       |  |  |  |  |

| Operational Amplifiers                           |                                                                                                                                                     |               | 2                      |                       |  |  |  |  |

| Charge Time Measurement Unit (CTMU)              |                                                                                                                                                     | Y             | es                     |                       |  |  |  |  |

| Real-Time Clock and Calendar (RTCC)              |                                                                                                                                                     | Y             | es                     |                       |  |  |  |  |

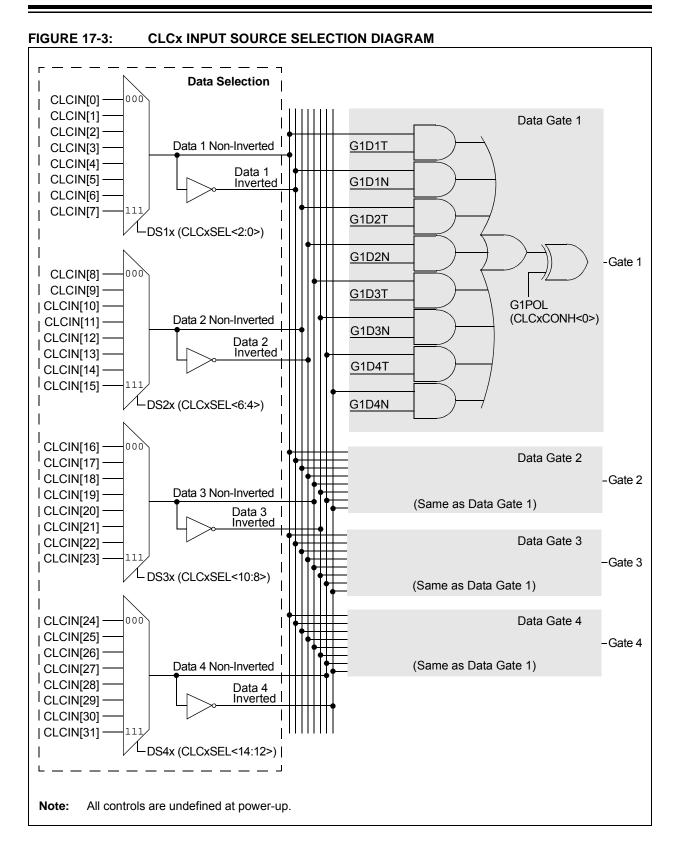

| Configurable Logic Cell (CLC)                    |                                                                                                                                                     |               | 2                      |                       |  |  |  |  |

| Resets (and delays)                              | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |               |                        |                       |  |  |  |  |

| Instruction Set                                  | 76 Base Instructions, Multiple Addressing Mode Variations                                                                                           |               |                        |                       |  |  |  |  |

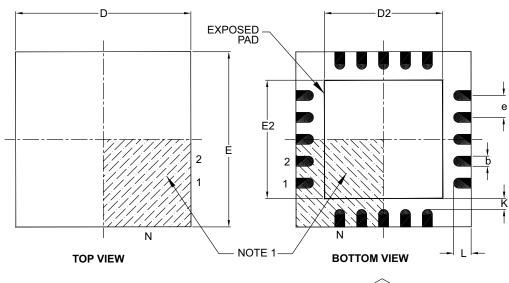

| Packages                                         | 44-Pin QFN/TQFP,<br>48-Pin UQFN SPDIP/SSOP/SOIC/QF                                                                                                  |               |                        |                       |  |  |  |  |

| TABLE 1-3: DEVICE FEATURES FOR                      | R THE PIC24FV1                                                                                                                                      |                    |                               |                         |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|-------------------------|--|--|--|--|

| Features                                            | PIC24FV16KM204                                                                                                                                      | PIC24FV08KM204     | PIC24FV16KM202                | PIC24FV08KM202          |  |  |  |  |

| Operating Frequency                                 |                                                                                                                                                     | DC-3               | 2 MHz                         |                         |  |  |  |  |

| Program Memory (bytes)                              | 16K                                                                                                                                                 | 8K                 | 16K                           | 8K                      |  |  |  |  |

| Program Memory (instructions)                       | 5632                                                                                                                                                | 2816               | 5632                          | 2816                    |  |  |  |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 20                 | )48                           | I                       |  |  |  |  |

| Data EEPROM Memory (bytes)                          |                                                                                                                                                     | 5                  | 12                            |                         |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)          |                                                                                                                                                     | 40 (               | 36/4)                         |                         |  |  |  |  |

| Voltage Range                                       |                                                                                                                                                     | 2.0-               | -5.5V                         |                         |  |  |  |  |

| I/O Ports                                           | PORTA<1<br>PORTB<<br>PORTC                                                                                                                          | :15:0>             |                               | RTA<7,5:0><br>RTB<15:0> |  |  |  |  |

| Total I/O Pins                                      | 37                                                                                                                                                  |                    |                               | 23                      |  |  |  |  |

| Timers                                              | 11<br>(One 16-bit timer, five MCCPs/SCCPs with up to two 16/32 timers each)                                                                         |                    |                               |                         |  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         | 3 2                                                                                                                                                 |                    |                               |                         |  |  |  |  |

| Serial Communications<br>MSSP<br>UART               |                                                                                                                                                     |                    | 2<br>2                        |                         |  |  |  |  |

| Input Change Notification Interrupt                 | 36                                                                                                                                                  |                    |                               | 22                      |  |  |  |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                                                                                                                                  |                    | 19                            |                         |  |  |  |  |

| Analog Comparators                                  |                                                                                                                                                     |                    | 3                             |                         |  |  |  |  |

| 8-Bit Digital-to-Analog Converters                  |                                                                                                                                                     |                    | 2                             |                         |  |  |  |  |

| Operational Amplifiers                              |                                                                                                                                                     |                    | 2                             |                         |  |  |  |  |

| Charge Time Measurement Unit (CTMU)                 |                                                                                                                                                     | Y                  | íes 🛛                         |                         |  |  |  |  |

| Real-Time Clock and Calendar (RTCC)                 |                                                                                                                                                     | Y                  | 'es                           |                         |  |  |  |  |

| Configurable Logic Cell (CLC)                       |                                                                                                                                                     |                    | 2                             |                         |  |  |  |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                    |                               |                         |  |  |  |  |

| Instruction Set                                     | 76 Base Inst                                                                                                                                        | ructions, Multiple | e Addressing N                | Iode Variations         |  |  |  |  |

| Packages                                            | 44-Pin QFI<br>48-Pin U                                                                                                                              |                    | 28-Pin<br>SPDIP/SSOP/SOIC/QFN |                         |  |  |  |  |

#### TABLE 1-3: DEVICE FEATURES FOR THE PIC24FV16KM204 FAMILY

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

| TABLE 1-5. |                                  |                                  | F             |                        |                |                                  | <u> </u>                         | FV            | ,                      |                |     |        |                             |

|------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|-----------------------------|

|            |                                  | I                                | Pin Numb      | er                     |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                             |

| Function   | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                 |

| OSCI       | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | Ι   | ANA    | Primary Oscillator Input    |

| OSCO       | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | 0   | ANA    | Primary Oscillator Output   |

| PGEC1      | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I/O | ST     | ICSP Clock 1                |

| PGED1      | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I/O | ST     | ICSP Data 1                 |

| PGEC2      | 2                                | 22                               | 19            | 9                      | 10             | 2                                | 22                               | 19            | 9                      | 10             | I/O | ST     | ICSP Clock 2                |

| PGED2      | 3                                | 21                               | 18            | 8                      | 9              | 3                                | 21                               | 18            | 8                      | 9              | I/O | ST     | ICSP Data 2                 |

| PGEC3      | 10                               | 15                               | 12            | 42                     | 46             | 10                               | 15                               | 12            | 42                     | 46             | I/O | ST     | ICSP Clock 3                |

| PGED3      | 9                                | 14                               | 11            | 41                     | 45             | 9                                | 14                               | 11            | 41                     | 45             | I/O | ST     | ICSP Data 3                 |

| PWRLCLK    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | RTCC Power Line Clock Input |

| RA0        | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I/O | ST     | PORTA Pins                  |

| RA1        | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | I/O | ST     | PORTA Pins                  |

| RA2        | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I/O | ST     | PORTA Pins                  |

| RA3        | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | I/O | ST     | PORTA Pins                  |

| RA4        | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | I/O | ST     | PORTA Pins                  |

| RA5        | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | I/O | ST     | PORTA Pins                  |

| RA6        | 14                               | 20                               | 17            | 7                      | 7              | _                                |                                  | _             | _                      | _              | I/O | ST     | PORTA Pins                  |

| RA7        | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | I/O | ST     | PORTA Pins                  |

| RA8        | —                                | —                                |               | 32                     | 35             | —                                |                                  | —             | 32                     | 35             | I/O | ST     | PORTA Pins                  |

| RA9        | —                                | —                                |               | 35                     | 38             | —                                |                                  | —             | 35                     | 38             | I/O | ST     | PORTA Pins                  |

| RA10       | _                                | _                                | _             | 12                     | 13             | _                                | _                                | —             | 12                     | 13             | I/O | ST     | PORTA Pins                  |

| RA11       | _                                | _                                | _             | 13                     | 14             | _                                | _                                | —             | 13                     | 14             | I/O | ST     | PORTA Pins                  |

| RB0        | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I/O | ST     | PORTB Pins                  |

| RB1        | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I/O | ST     | PORTB Pins                  |

| RB2        | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I/O | ST     | PORTB Pins                  |

| RB3        | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | ST     | PORTB Pins                  |

| RB4        | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | I/O | ST     | PORTB Pins                  |

| RB5        | —                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I/O | ST     | PORTB Pins                  |

| RB6        | —                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | I/O | ST     | PORTB Pins                  |

| RB7        | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I/O | ST     | PORTB Pins                  |

| RB8        | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | ST     | PORTB Pins                  |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                 |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------|

|          |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                                 |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                     |

| RB9      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | ST     | PORTB Pins                      |

| RB10     | —                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I/O | ST     | PORTB Pins                      |

| RB11     | —                                | 22                               | 19            | 9                      | 10             | _                                | 22                               | 19            | 9                      | 10             | I/O | ST     | PORTB Pins                      |

| RB12     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I/O | ST     | PORTB Pins                      |

| RB13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I/O | ST     | PORTB Pins                      |

| RB14     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I/O | ST     | PORTB Pins                      |

| RB15     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I/O | ST     | PORTB Pins                      |

| RC0      | —                                | _                                |               | 25                     | 27             | _                                |                                  |               | 25                     | 27             | I/O | ST     | PORTC Pins                      |

| RC1      | —                                | _                                | _             | 26                     | 28             | _                                | _                                | _             | 26                     | 28             | I/O | ST     | PORTC Pins                      |

| RC2      | —                                | _                                | _             | 27                     | 29             | _                                | _                                | _             | 27                     | 29             | I/O | ST     | PORTC Pins                      |

| RC3      | —                                | _                                | _             | 36                     | 39             | _                                | _                                | _             | 36                     | 39             | I/O | ST     | PORTC Pins                      |

| RC4      | —                                | _                                | _             | 37                     | 40             | _                                | _                                | _             | 37                     | 40             | I/O | ST     | PORTC Pins                      |

| RC5      | —                                | _                                | _             | 38                     | 41             | _                                | _                                | _             | 38                     | 41             | I/O | ST     | PORTC Pins                      |

| RC6      | —                                | _                                | _             | 2                      | 2              | _                                | _                                | _             | 2                      | 2              | I/O | ST     | PORTC Pins                      |

| RC7      | —                                | _                                | _             | 3                      | 3              | _                                | _                                | _             | 3                      | 3              | I/O | ST     | PORTC Pins                      |

| RC8      | —                                | _                                | _             | 4                      | 4              | _                                | _                                | _             | 4                      | 4              | I/O | ST     | PORTC Pins                      |

| RC9      | —                                | _                                | _             | 5                      | 5              | _                                | _                                | _             | 5                      | 5              | I/O | ST     | PORTC Pins                      |

| REFO     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | 0   | _      | Reference Clock Output          |

| RTCC     | —                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | _      | Real-Time Clock/Calendar Output |

| SCK1     | 15                               | 22                               | 19            | 9                      | 10             | 15                               | 22                               | 19            | 9                      | 10             | I/O | ST     | MSSP1 SPI Clock                 |

| SDI1     | 17                               | 21                               | 18            | 8                      | 9              | 17                               | 21                               | 18            | 8                      | 9              | Ι   | ST     | MSSP1 SPI Data Input            |

| SDO1     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   |        | MSSP1 SPI Data Output           |

| SS1      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | MSSP1 SPI Slave Select Input    |

| SCK2     | —                                | 14                               | 11            | 38                     | 41             | _                                | 14                               | 11            | 38                     | 41             | I/O | ST     | MSSP2 SPI Clock                 |

| SDI2     | —                                | 19                               | 16            | 36                     | 39             | _                                | 19                               | 16            | 36                     | 39             | Ι   | ST     | MSSP2 SPI Data Input            |

| SDO2     | —                                | 15                               | 12            | 37                     | 40             | —                                | 15                               | 12            | 37                     | 40             | 0   |        | MSSP2 SPI Data Output           |

| SS2      | —                                | 23                               | 20            | 35                     | 38             | _                                | 23                               | 20            | 35                     | 38             | Ι   | ST     | MSSP2 SPI Slave Select Input    |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

#### TABLE 4-3:CPU CORE REGISTERS MAP

| TABLE        | 4-3.  | UP     |                      | KE KEGI   | STERS     |           |           |          |          |            |          |          |          |          |          |          |          |               |

|--------------|-------|--------|----------------------|-----------|-----------|-----------|-----------|----------|----------|------------|----------|----------|----------|----------|----------|----------|----------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14               | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9    | Bit 8    | Bit 7      | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| WREG0        | 0h    |        |                      |           |           |           |           |          | W        | /REG0      |          |          |          |          |          |          |          | 0000          |

| WREG1        | 2h    |        | WREG1 0              |           |           |           |           |          |          |            |          |          |          |          | 0000     |          |          |               |

| WREG2        | 4h    |        |                      |           |           |           |           |          | W        | /REG2      |          |          |          |          |          |          |          | 0000          |

| WREG3        | 6h    |        |                      |           |           |           |           |          | W        | /REG3      |          |          |          |          |          |          |          | 0000          |

| WREG4        | 8h    |        |                      |           |           |           |           |          | W        | /REG4      |          |          |          |          |          |          |          | 0000          |

| WREG5        | Ah    |        |                      |           |           |           |           |          | W        | /REG5      |          |          |          |          |          |          |          | 0000          |

| WREG6        | Ch    |        |                      |           |           |           |           |          | W        | /REG6      |          |          |          |          |          |          |          | 0000          |

| WREG7        | Eh    |        |                      |           |           |           |           |          | W        | /REG7      |          |          |          |          |          |          |          | 0000          |

| WREG8        | 10h   |        |                      |           |           |           |           |          | W        | /REG8      |          |          |          |          |          |          |          | 0000          |

| WREG9        | 12h   |        |                      |           |           |           |           |          | W        | /REG9      |          |          |          |          |          |          |          | 0000          |

| WREG10       | 14h   |        |                      |           |           |           |           |          | W        | REG10      |          |          |          |          |          |          |          | 0000          |

| WREG11       | 16h   |        |                      |           |           |           |           |          | W        | REG11      |          |          |          |          |          |          |          | 0000          |

| WREG12       | 18h   |        |                      |           |           |           |           |          | W        | REG12      |          |          |          |          |          |          |          | 0000          |

| WREG13       | 1Ah   |        |                      |           |           |           |           |          | W        | REG13      |          |          |          |          |          |          |          | 0000          |

| WREG14       | 1Ch   |        |                      |           |           |           |           |          | W        | REG14      |          |          |          |          |          |          |          | 0000          |

| WREG15       | 1Eh   |        |                      |           |           |           |           |          | W        | REG15      |          |          |          |          |          |          |          | 0800          |

| SPLIM        | 20h   |        |                      |           |           |           |           |          | SPLI     | V Register |          |          |          |          |          |          |          | xxxx          |

| PCL          | 2Eh   |        |                      |           |           |           |           |          | PCL      | Register   |          |          |          |          |          |          |          | 0000          |

| PCH          | 30h   | _      |                      |           |           | —         | —         |          | —        | PCH7       | PCH6     | PCH5     | PCH4     | PCH3     | PCH2     | PCH1     | PCH0     | 0000          |

| TBLPAG       | 32h   | _      |                      |           |           | —         | —         |          | —        | TBLPAG7    | TBLPAG6  | TBLPAG5  | TBLPAG4  | TBLPAG3  | TBLPAG2  | TBLPAG1  | TBLPAG0  | 0000          |

| PSVPAG       | 34h   | _      |                      |           |           | -         | —         | _        | _        | PSVPAG7    | PSVPAG6  | PSVPAG5  | PSVPAG4  | PSVPAG3  | PSVPAG2  | PSVPAG1  | PSVPAG0  | 0000          |

| RCOUNT       | 36h   |        | RCOUNT Register xxxx |           |           |           |           |          |          |            |          | xxxx     |          |          |          |          |          |               |

| SR           | 42h   | _      |                      |           |           | -         | —         | _        | DC       | IPL2       | IPL1     | IPL0     | RA       | Ν        | OV       | Z        | С        | 0000          |

| CORCON       | 44h   | _      |                      | _         |           | -         | —         | _        | —        | —          | —        | _        | _        | IPL3     | PSV      | _        | —        | 0000          |

| DISICNT      | 52h   | _      | -                    | DISICNT13 | DISICNT12 | DISICNT11 | DISICNT10 | DISICNT9 | DISICNT8 | DISICNT7   | DISICNT6 | DISICNT5 | DISICNT4 | DISICNT3 | DISICNT2 | DISICNT1 | DISICNT0 | xxxx          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-8: MCCP1 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14                                   | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9   | Bit 8       | Bit 7        | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Rese |

|-----------|-------|---------|------------------------------------------|---------|--------|---------|---------|---------|-------------|--------------|--------------|---------|---------|---------|---------|---------|---------|-------------|

| CCP1CON1L | 140h  | CCPON   | —                                        | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1 | CLKSEL0     | TMRPS1       | TMRPS0       | T32     | CCSEL   | MOD3    | MOD2    | MOD1    | MOD0    | 0000        |

| CCP1CON1H | 142h  | OPSSRC  | RTRGEN                                   | _       | _      | OPS3    | OPS2    | OPS1    | OPS0        | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1   | SYNC0   | 0000        |

| CCP1CON2L | 144h  | PWMRSEN | ASDGM                                    | _       | SSDG   | _       | _       | _       | _           | ASDG7        | ASDG6        | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1   | ASDG0   | 0000        |

| CCP1CON2H | 146h  | OENSYNC | _                                        | OCFEN   | OCEEN  | OCDEN   | OCCEN   | OCBEN   | OCAEN       | ICGSM1       | ICGSM0       | _       | AUXOUT1 | AUXOUT0 | ICS2    | ICS1    | ICS0    | 0100        |

| CCP1CON3L | 148h  | _       | _                                        | _       | _      | _       | _       | _       | _           | _            |              | DT5     | DT4     | DT3     | DT2     | DT1     | DT0     | 0000        |

| CCP1CON3H | 14Ah  | OETRIG  | OSCNT2                                   | OSCNT1  | OSCNT0 | _       | OUTM2   | OUTM1   | OUTM0       | _            | _            | POLACE  | POLBDF  | PSSACE1 | PSSACE0 | PSSBDF1 | PSSBDF0 | 0000        |

| CCP1STATL | 14Ch  | _       | _                                        | _       | _      | _       | _       | _       | _           | CCPTRIG      | TRSET        | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV    | ICBNE   | 0000        |

| CCP1TMRL  | 150h  |         |                                          |         |        |         |         | MCCI    | P1 Time Ba  | se Register  | Low Word     |         |         |         |         |         |         | 0000        |

| CCP1TMRH  | 152h  |         |                                          |         |        |         |         | MCCF    | P1 Time Ba  | se Register  | High Word    |         |         |         |         |         |         | 0000        |

| CCP1PRL   | 154h  |         |                                          |         |        |         |         | MCCP1   | Fime Base F | Period Regis | ster Low Wor | ď       |         |         |         |         |         | FFFF        |

| CCP1PRH   | 156h  |         |                                          |         |        |         |         | MCCP1 T | īme Base F  | Period Regis | ster High Wo | rd      |         |         |         |         |         | FFFF        |

| CCP1RAL   | 158h  |         |                                          |         |        |         |         | O       | utput Comp  | are 1 Data \ | Nord A       |         |         |         |         |         |         | 0000        |

| CCP1RBL   | 15Ch  |         | Output Compare 1 Data Word B             |         |        |         |         |         |             |              |              |         | 0000    |         |         |         |         |             |

| CCP1BUFL  | 160h  |         | Input Capture 1 Data Buffer Low Word 00  |         |        |         |         |         |             |              |              |         | 0000    |         |         |         |         |             |

| CCP1BUFH  | 162h  |         | Input Capture 1 Data Buffer High Word 00 |         |        |         |         |         |             |              |              | 0000    |         |         |         |         |         |             |

Legend: x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

| U-0                 | R/W-1                                    | R/W-0                                                                       | R/W-0            | U-0                                | U-0              | U-0             | U-0     |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------|------------------|------------------------------------|------------------|-----------------|---------|

| 0-0                 | NVMIP2                                   | NVMIP1                                                                      | NVMIP0           | 0-0                                | 0-0              | 0-0             | 0-0     |

| <br>bit 15          |                                          |                                                                             |                  | —                                  | _                | _               | <br>bit |

|                     |                                          |                                                                             |                  |                                    |                  |                 | bit     |

| U-0                 | R/W-1                                    | R/W-0                                                                       | R/W-0            | U-0                                | R/W-1            | R/W-0           | R/W-0   |

| _                   | AD1IP2                                   | AD1IP1                                                                      | AD1IP0           |                                    | U1TXIP2          | U1TXIP1         | U1TXIP0 |

| bit 7               |                                          |                                                                             |                  |                                    |                  |                 | bit     |

| Legend:             |                                          |                                                                             |                  |                                    |                  |                 |         |

| R = Readab          | ole bit                                  | W = Writable                                                                | bit              | U = Unimplem                       | nented bit, read | l as '0'        |         |

| -n = Value a        | at POR                                   | '1' = Bit is set                                                            |                  | '0' = Bit is clea                  | ared             | x = Bit is unkr | nown    |

| =                   |                                          |                                                                             |                  |                                    |                  |                 |         |

| bit 15<br>bit 14-12 | -                                        | ited: Read as '<br>: NVM Interrup                                           |                  |                                    |                  |                 |         |

|                     | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                   | abled            | .,                                 |                  |                 |         |

| bit 11-7            | -                                        | ted: Read as '                                                              |                  |                                    |                  |                 |         |

| bit 6-4             | 111 = Interru<br>•<br>•<br>001 = Interru | A/D Conversic<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis | highest priority | terrupt Priority I<br>/ interrupt) | bits             |                 |         |

| bit 3               | Unimplemen                               | ted: Read as '                                                              | 0'               |                                    |                  |                 |         |

| bit 2-0             |                                          | ➤: UART1 Trans<br>pt is Priority 7 (                                        |                  |                                    |                  |                 |         |

|                     |                                          | pt is Priority 1<br>pt source is dis                                        | abled            |                                    |                  |                 |         |

#### REGISTER 8-22: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

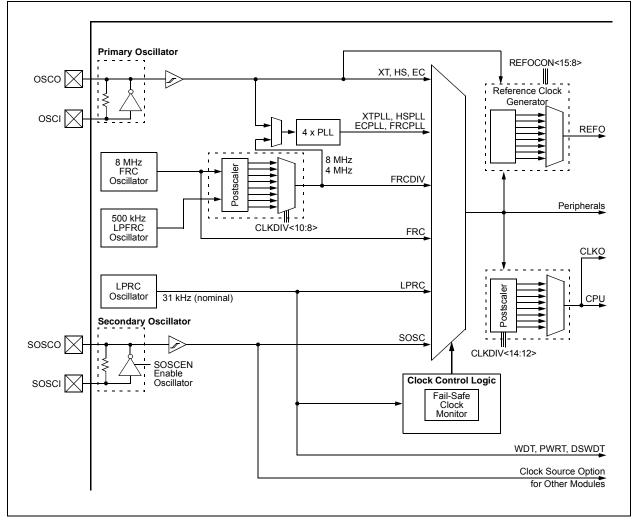

### 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on oscillator configuration, refer to the *"PIC24F Family Reference Manual"*, **"Oscillator with 500 kHz Low-Power FRC"** (DS39726).

The oscillator system for the PIC24FV16KM204 family of devices has the following features:

A total of five external and internal oscillator options as clock sources, providing 11 different clock modes.

- On-chip 4x Phase Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources.

- Software-controllable switching between various clock sources.

- Software-controllable postscaler for selective clocking of CPU for system power savings.

- System frequency range declaration bits for External Clock (EC) mode. When using an EC source, the current consumption is reduced by setting the declaration bits to the expected frequency range.

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown.

A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: PIC24FXXXXX FAMILY CLOCK DIAGRAM

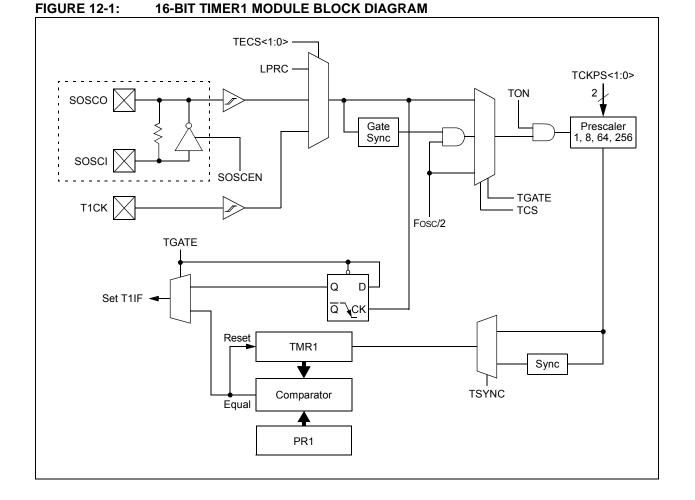

### 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on timers, refer to the "PIC24F Family Reference Manual", "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

| R/W-0        | U-0                             | R/W-0                       | U-0                                | U-0                     | U-0              | R/W-0                | R/W-0                |

|--------------|---------------------------------|-----------------------------|------------------------------------|-------------------------|------------------|----------------------|----------------------|

| TON          |                                 | TSIDL                       | —                                  | _                       | —                | TECS1 <sup>(1)</sup> | TECS0 <sup>(1)</sup> |

| bit 15       |                                 | •                           | -                                  |                         |                  |                      | bit                  |

|              |                                 |                             |                                    |                         |                  |                      |                      |

| U-0          | R/W-0                           | R/W-0                       | R/W-0                              | U-0                     | R/W-0            | R/W-0                | U-0                  |

| —            | TGATE                           | TCKPS1                      | TCKPS0                             | —                       | TSYNC            | TCS                  | —                    |

| bit 7        |                                 |                             |                                    |                         |                  |                      | bit                  |

| Legend:      |                                 |                             |                                    |                         |                  |                      |                      |

| R = Readab   | ole bit                         | W = Writable                | bit                                | U = Unimpler            | mented bit, read | d as '0'             |                      |

| -n = Value a | It POR                          | '1' = Bit is set            |                                    | '0' = Bit is cle        | ared             | x = Bit is unkr      | iown                 |

|              |                                 |                             |                                    |                         |                  |                      |                      |

| bit 15       | TON: Timer1                     | On bit                      |                                    |                         |                  |                      |                      |

|              | 1 = Starts 16-<br>0 = Stops 16- |                             |                                    |                         |                  |                      |                      |

| bit 14       | Unimplemen                      | ted: Read as '              | 0'                                 |                         |                  |                      |                      |

| bit 13       | TSIDL: Timer                    | 1 Stop in Idle I            | Node bit                           |                         |                  |                      |                      |

|              |                                 |                             | eration when o<br>ation in Idle mo | device enters lo<br>ode | lle mode         |                      |                      |

| bit 12-10    | Unimplemen                      | ted: Read as '              | 0'                                 |                         |                  |                      |                      |

| bit 9-8      |                                 |                             | ed Clock Seled                     | ct bits <sup>(1)</sup>  |                  |                      |                      |

|              | 11 = Reserve                    | •                           | as the sleek s                     | 0.1700                  |                  |                      |                      |

|              |                                 |                             | as the clock s<br>al Clock (EC)    |                         |                  |                      |                      |

|              |                                 |                             |                                    | r (SOSC) as th          | e clock source   |                      |                      |

| bit 7        | Unimplemen                      | ted: Read as '              | 0'                                 |                         |                  |                      |                      |

| bit 6        |                                 |                             | Accumulation                       | Enable bit              |                  |                      |                      |

|              | When TCS =                      |                             |                                    |                         |                  |                      |                      |

|              | When TCS = $\frac{1}{2}$        |                             |                                    |                         |                  |                      |                      |

|              |                                 | <u>o.</u><br>ne accumulatio | n is enabled                       |                         |                  |                      |                      |

|              | 0 = Gated tim                   | ne accumulatio              | n is disabled                      |                         |                  |                      |                      |

| bit 5-4      | TCKPS<1:0>                      | : Timer1 Input              | Clock Prescale                     | e Select bits           |                  |                      |                      |

|              | 11 = 1:256                      |                             |                                    |                         |                  |                      |                      |

|              | 10 = 1:64<br>01 = 1:8           |                             |                                    |                         |                  |                      |                      |

|              | 00 = 1:1                        |                             |                                    |                         |                  |                      |                      |

| bit 3        | Unimplemen                      | ted: Read as '              | 0'                                 |                         |                  |                      |                      |

| bit 2        | TSYNC: Time                     | er1 External Cl             | ock Input Sync                     | hronization Se          | lect bit         |                      |                      |

|              | <u>When TCS =</u>               | <u>1:</u><br>nizes External | Clock input                        |                         |                  |                      |                      |

|              |                                 |                             | External Clock                     | input                   |                  |                      |                      |

|              | When TCS =                      | -                           |                                    |                         |                  |                      |                      |

|              | This bit is igno                | ored.                       |                                    |                         |                  |                      |                      |

| bit 1        |                                 | Clock Source                |                                    |                         |                  |                      |                      |

|              |                                 |                             | selected by TE                     | CS<1:0>                 |                  |                      |                      |

|              | 0 = Internal c                  |                             |                                    |                         |                  |                      |                      |

| bit 0        | Unimplemen                      | tod. Dood oo .              | Ω'                                 |                         |                  |                      |                      |

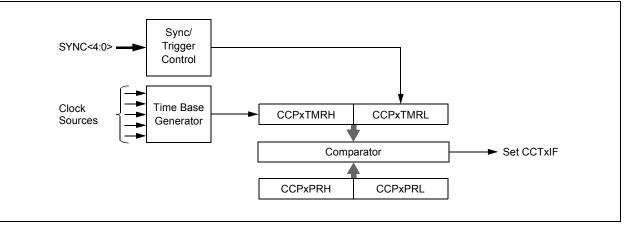

#### FIGURE 13-4: 32-BIT TIMER MODE

#### REGISTER 13-7: CCPxSTATL: CCPx STATUS REGISTER

| U-0           | U-0                                                                                                                                    | U-0                                    | U-0          | U-0               | U-0              | U-0             | U-0           |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|-------------------|------------------|-----------------|---------------|--|--|--|--|

| _             | _                                                                                                                                      | —                                      | _            | —                 | _                | —               |               |  |  |  |  |

| bit 15        |                                                                                                                                        |                                        |              |                   |                  |                 | bit 8         |  |  |  |  |

|               |                                                                                                                                        |                                        | 5/0.0        | 5/2.2             | 5/0.0            | 5/2.2           | R/C-0         |  |  |  |  |

| R-0           |                                                                                                                                        |                                        |              |                   |                  |                 |               |  |  |  |  |

| CCPTRIG       | TRSET                                                                                                                                  | TRSET TRCLR ASEVT SCEVT ICDIS ICOV IC  |              |                   |                  |                 |               |  |  |  |  |

| bit 7         |                                                                                                                                        |                                        |              |                   |                  |                 | bit 0         |  |  |  |  |

| Legend:       |                                                                                                                                        | C = Clearable                          | bit          |                   |                  |                 |               |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                  | W1 = Write '1'                         | only         | U = Unimplem      | nented bit, read | as '0'          |               |  |  |  |  |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set                       |              | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |  |  |  |  |

|               |                                                                                                                                        |                                        |              |                   |                  |                 |               |  |  |  |  |

| bit 15-8      | Unimplemen                                                                                                                             | ted: Read as '0                        | ,            |                   |                  |                 |               |  |  |  |  |

| bit 7         | CCPTRIG: CCPx Trigger Status bit                                                                                                       |                                        |              |                   |                  |                 |               |  |  |  |  |

|               | <ul> <li>1 = Timer has been triggered and is running</li> <li>0 = Timer has not been triggered and is held in Reset</li> </ul>         |                                        |              |                   |                  |                 |               |  |  |  |  |

| <b>h</b> :# 0 |                                                                                                                                        |                                        |              | eiu in Resel      |                  |                 |               |  |  |  |  |

| bit 6         |                                                                                                                                        | x Trigger Set Re                       |              | when TRIGEN       | = 1 (location a  | wave reade as   | : '∩')        |  |  |  |  |

| bit 5         |                                                                                                                                        | Px Trigger Clear                       |              |                   |                  | ways icaus as   | , , ,         |  |  |  |  |

| bit o         |                                                                                                                                        | is location to ca                      | •            | Trigger when T    | RIGEN = 1 (lo    | cation alwavs r | eads as '0'). |  |  |  |  |

| bit 4         |                                                                                                                                        | x Auto-Shutdow                         |              |                   | - (-             | ,               | ····,         |  |  |  |  |

|               | 1 = A shutdo                                                                                                                           | wn event is in p                       | rogress; CCP | x outputs are in  | the shutdown     | state           |               |  |  |  |  |

|               | 0 = CCPx ou                                                                                                                            | itputs operate n                       | ormally      |                   |                  |                 |               |  |  |  |  |

| bit 3         | •                                                                                                                                      | le Edge Compa                          |              |                   |                  |                 |               |  |  |  |  |

|               |                                                                                                                                        | edge compare e<br>edge compare e       |              |                   |                  |                 |               |  |  |  |  |

| bit 2         | •                                                                                                                                      | Capture x Disat                        |              | occurred          |                  |                 |               |  |  |  |  |

| Dit Z         | •                                                                                                                                      | Input Capture :                        |              | es not generate   | a capture ever   | nt              |               |  |  |  |  |

|               |                                                                                                                                        | Input Capture                          |              |                   |                  |                 |               |  |  |  |  |

| bit 1         | ICOV: Input Capture x Buffer Overflow Status bit                                                                                       |                                        |              |                   |                  |                 |               |  |  |  |  |

|               | <ul> <li>1 = The Input Capture x FIFO buffer has overflowed</li> <li>0 = The Input Capture x FIFO buffer has not overflowed</li> </ul> |                                        |              |                   |                  |                 |               |  |  |  |  |

|               |                                                                                                                                        | -                                      |              | ot overflowed     |                  |                 |               |  |  |  |  |

| bit 0         | •                                                                                                                                      | Capture x Buffe                        |              | -  -   -          |                  |                 |               |  |  |  |  |

|               |                                                                                                                                        | apture x buffer h<br>apture x buffer i |              | adie              |                  |                 |               |  |  |  |  |

|               |                                                                                                                                        |                                        | c sinply     |                   |                  |                 |               |  |  |  |  |

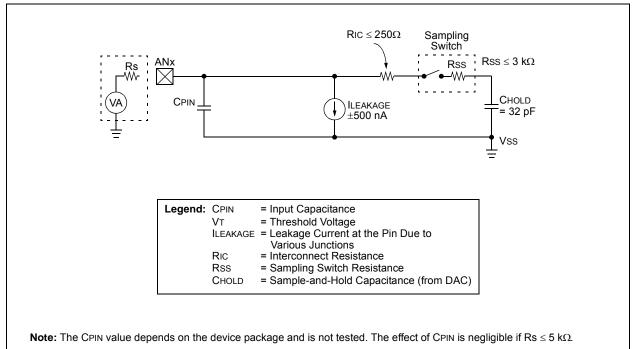

### 19.2 A/D Sampling Requirements

The analog input model of the 12-bit A/D Converter is shown in Figure 19-2. The total sampling time for the A/D is a function of the holding capacitor charge time.

For the A/D Converter to meet its specified accuracy, the Charge Holding Capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The Source Impedance (Rs), the Interconnect Impedance (Rsc) and the Internal Sampling Switch Impedance (Rss) combine to directly affect the time required to charge CHOLD. The combined impedance of the analog sources must, therefore, be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the A/D Converter, the maximum recommended source impedance, Rs, is  $2.5 \text{ k}\Omega$ . After the analog input channel is selected (changed), this sampling function

must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

At least 1 TAD time period should be allowed between conversions for the sample time. For more details, see **Section 27.0 "Electrical Characteristics"**.

### EQUATION 19-1: A/D CONVERSION CLOCK PERIOD

$$TAD = TCY (ADCS + 1)$$

$ADCS = \frac{TAD}{TCY} - 1$

**Note:** Based on Tcy = 2/Fosc; Doze mode and PLL are disabled.

#### FIGURE 19-2: 12-BIT A/D CONVERTER ANALOG INPUT MODEL

| AC CHA       | ARACTE | RISTICS                                                  |    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |    |       |                                                     |  |  |  |  |  |