Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

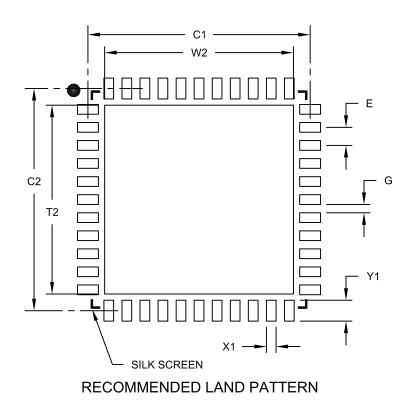

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 48-UQFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km104-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-24: PAD CONFIGURATION REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                 | Bit 10                 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|------------------------|------------------------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

|           |       |        |        |        |        |                        |                        |         |         |       |       |       |       |       |       |       |       |               |

| PADCFG1   | 2FCh  | _      | —      | _      | _      | SDO2DIS <sup>(1)</sup> | SCK2DIS <sup>(1)</sup> | SDO1DIS | SCK1DIS | _     | _     | _     | _     | _     | _     | _     | _     | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are not available on the PIC24F(V)08KM101 device, read as '0'.

# 7.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 7-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. For more information, see **Section 9.0** "Oscillator Configuration".

# TABLE 7-2:OSCILLATOR SELECTION vs.TYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | FNOSC<2:0> Configuration bits |

| BOR        | (FOSCSEL<2:0>)                |

| MCLR       | COSC<2:0> Control bits        |

| WDTO       | (OSCCON<14:12>)               |

| SWR        |                               |

### 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Reset Type         | Clock Source | SYSRST Delay | System Clock<br>Delay | Notes      |

|--------------------|--------------|--------------|-----------------------|------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT |                       | 1, 2       |

|                    | FRC, FRCDIV  | TPOR + TPWRT | TFRC                  | 1, 2, 3    |

|                    | LPRC         | TPOR + TPWRT | TLPRC                 | 1, 2, 3    |

|                    | ECPLL        | TPOR + TPWRT | Тьоск                 | 1, 2, 4    |

|                    | FRCPLL       | TPOR + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4 |

|                    | XT, HS, SOSC | TPOR+ TPWRT  | Tost                  | 1, 2, 5    |

|                    | XTPLL, HSPLL | TPOR + TPWRT | TOST + TLOCK          | 1, 2, 4, 5 |

| BOR                | EC           | TPWRT        | —                     | 2          |

|                    | FRC, FRCDIV  | TPWRT        | TFRC                  | 2, 3       |

|                    | LPRC         | TPWRT        | TLPRC                 | 2, 3       |

|                    | ECPLL        | TPWRT        | Тьоск                 | 2, 4       |

|                    | FRCPLL       | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

|                    | XT, HS, SOSC | TPWRT        | Тоѕт                  | 2, 5       |

|                    | XTPLL, HSPLL | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

| All Others         | Any Clock    | _            | _                     | None       |

#### TABLE 7-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay.

- 2: TPWRT = 64 ms nominal if the Power-up Timer is enabled; otherwise, it is zero.

- **3:** TFRC and TLPRC = RC Oscillator start-up times.

- **4:** TLOCK = PLL Lock time.

- **5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

- 6: If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 27.0 "Electrical Characteristics".

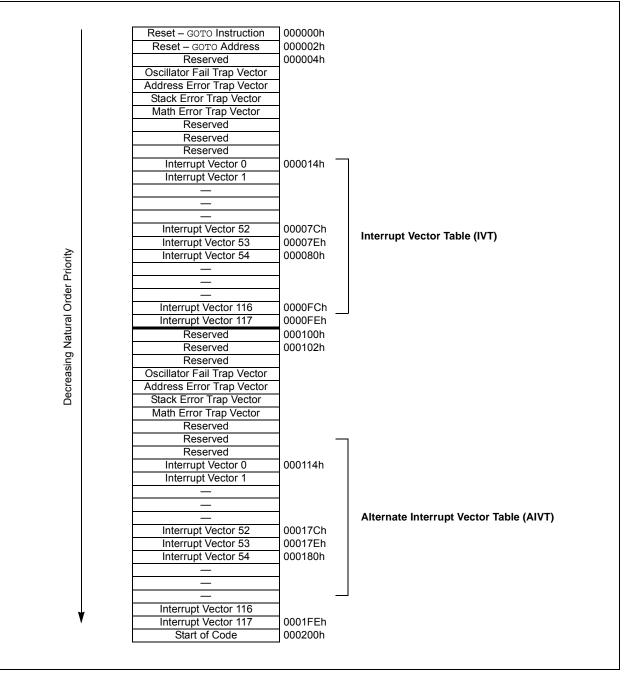

FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE

| U-0                   | R/W-1                                                                                 | R/W-0                                | R/W-0             | U-0          | R/W-1            | R/W-0   | R/W-0   |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------|--------------------------------------|-------------------|--------------|------------------|---------|---------|--|--|--|--|--|

| _                     | DAC2IP2                                                                               | DAC2IP1                              | DAC2IP0           |              | DAC1IP2          | DAC1IP1 | DAC1IP0 |  |  |  |  |  |

| bit 15                |                                                                                       |                                      |                   |              |                  |         | bit 8   |  |  |  |  |  |

| U-0                   | R/W-1                                                                                 | R/W-0                                | R/W-0             | U-0          | U-0              | U-0     | U-0     |  |  |  |  |  |

| _                     | CTMUIP2                                                                               | CTMUIP1                              | CTMUIP0           | _            |                  | _       | _       |  |  |  |  |  |

| bit 7                 |                                                                                       |                                      |                   |              |                  |         | bit (   |  |  |  |  |  |

| Legend:               |                                                                                       |                                      |                   |              |                  |         |         |  |  |  |  |  |

| Legena.<br>R = Readab | le hit                                                                                | W = Writable                         | hit               | II = Unimple | mented bit, read | las 'O' |         |  |  |  |  |  |

| -n = Value a          |                                                                                       |                                      | on                |              |                  |         |         |  |  |  |  |  |

|                       | at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                       |                                      |                   |              |                  |         |         |  |  |  |  |  |

| bit 15                | Unimplemen                                                                            | ted: Read as '                       | )'                |              |                  |         |         |  |  |  |  |  |

| bit 14-12             | <b>DAC2IP&lt;2:0&gt;:</b> Digital-to-Analog Converter 2 Event Interrupt Priority bits |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | 111 = Interrupt is Priority 7 (highest priority interrupt)                            |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | •                                                                                     |                                      | ingricor priority | ( interrupt) |                  |         |         |  |  |  |  |  |

|                       | •                                                                                     |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       |                                                                                       |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | 001 = Interru<br>000 = Interru                                                        | pt is Priority 1<br>pt source is dis | abled             |              |                  |         |         |  |  |  |  |  |

| bit 11                | Unimplemen                                                                            | ted: Read as '                       | )'                |              |                  |         |         |  |  |  |  |  |

| bit 10-8              | DAC1IP<2:0>: Digital-to-Analog Converter 1 Event Interrupt Priority bits              |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | 111 = Interrupt is Priority 7 (highest priority interrupt)                            |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | •                                                                                     |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | •                                                                                     |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | •<br>001 - Interru                                                                    | nt is Priority 1                     |                   |              |                  |         |         |  |  |  |  |  |

|                       | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                   |                                      |                   |              |                  |         |         |  |  |  |  |  |

| bit 7                 | -                                                                                     | ted: Read as '                       |                   |              |                  |         |         |  |  |  |  |  |

| bit 6-4               | -                                                                                     | >: CTMU Interr                       |                   | s            |                  |         |         |  |  |  |  |  |

|                       |                                                                                       | pt is Priority 7 (                   |                   |              |                  |         |         |  |  |  |  |  |

|                       | •                                                                                     |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | •                                                                                     |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | •                                                                                     |                                      |                   |              |                  |         |         |  |  |  |  |  |

|                       | 001 = Interru                                                                         | pt is Priority 1<br>pt source is dis | ahlad             |              |                  |         |         |  |  |  |  |  |

| hit 2 0               |                                                                                       |                                      |                   |              |                  |         |         |  |  |  |  |  |

| bit 3-0               | ommplemen                                                                             | ted: Read as '                       | J                 |              |                  |         |         |  |  |  |  |  |

#### REGISTER 8-32: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

| U-0           | U-0                                                                                                                     | U-0                               | U-0              | U-0                | U-0            | U-0             | U-0              |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|--------------------|----------------|-----------------|------------------|--|--|--|--|--|

|               | —                                                                                                                       | —                                 |                  | —                  |                | _               |                  |  |  |  |  |  |

| bit 15        |                                                                                                                         |                                   |                  |                    |                |                 | bit 8            |  |  |  |  |  |

|               |                                                                                                                         |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                   | R-0                               | R-0              | R-0                | R-0            | R-0             | R-0              |  |  |  |  |  |

| SMP           | CKE <sup>(1)</sup>                                                                                                      | D/Ā                               | Р                | S                  | R/W            | UA              | BF               |  |  |  |  |  |

| bit 7         |                                                                                                                         |                                   |                  |                    |                |                 | bit (            |  |  |  |  |  |

| Legend:       |                                                                                                                         |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                   | W = Writable I                    | oit              | U = Unimplem       | ented bit. rea | d as '0'        |                  |  |  |  |  |  |

| -n = Value at |                                                                                                                         | '1' = Bit is set                  |                  | '0' = Bit is clea  |                | x = Bit is unkr | nown             |  |  |  |  |  |

|               |                                                                                                                         |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

| bit 15-8      | Unimplemen                                                                                                              | ted: Read as '0                   | )'               |                    |                |                 |                  |  |  |  |  |  |

| bit 7         | SMP: Sample                                                                                                             | e bit                             |                  |                    |                |                 |                  |  |  |  |  |  |

|               | SPI Master m                                                                                                            |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

|               | 1 = Input data is sampled at the end of data output time<br>0 = Input data is sampled at the middle of data output time |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

|               | <ul> <li>Input data is sampled at the middle of data output time</li> <li>SPI Slave mode:</li> </ul>                    |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

|               |                                                                                                                         | de:<br>cleared when \$            | SPI is used in   | Slave mode         |                |                 |                  |  |  |  |  |  |

| bit 6         |                                                                                                                         | ck Select bit <sup>(1)</sup>      |                  |                    |                |                 |                  |  |  |  |  |  |

|               | 1 = Transmit o                                                                                                          | occurs on trans                   | ition from acti  | ve to Idle clock s | state          |                 |                  |  |  |  |  |  |

|               | 0 = Transmit                                                                                                            | occurs on trans                   | ition from Idle  | to active clock s  | state          |                 |                  |  |  |  |  |  |

| bit 5         | D/A: Data/Ad                                                                                                            |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

|               | Used in I <sup>2</sup> C™                                                                                               | mode only.                        |                  |                    |                |                 |                  |  |  |  |  |  |

| bit 4         | P: Stop bit                                                                                                             |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

|               |                                                                                                                         | node only. This                   | bit is cleared v | when the MSSP:     | x module is di | sabled; SSPEN   | l bit is cleared |  |  |  |  |  |

| bit 3         | S: Start bit                                                                                                            |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

|               | Used in I <sup>2</sup> C m                                                                                              | •                                 |                  |                    |                |                 |                  |  |  |  |  |  |

| bit 2         |                                                                                                                         | rite Information                  | bit              |                    |                |                 |                  |  |  |  |  |  |

|               | Used in I <sup>2</sup> C m                                                                                              |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

| bit 1         | UA: Update A                                                                                                            |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

|               | Used in I <sup>2</sup> C m                                                                                              | ,                                 |                  |                    |                |                 |                  |  |  |  |  |  |

| bit 0         | BF: Buffer Fu                                                                                                           |                                   |                  |                    |                |                 |                  |  |  |  |  |  |

|               |                                                                                                                         | s complete, SS<br>s not complete, |                  | emntv              |                |                 |                  |  |  |  |  |  |

|               |                                                                                                                         | -                                 |                  |                    |                |                 |                  |  |  |  |  |  |

|               | plarity of clock s                                                                                                      | tata ia aat by th                 |                  |                    |                |                 |                  |  |  |  |  |  |

### REGISTER 14-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

| R/W-0         | U-0                          | R/W-0                                                               | R/W-0                         | R/W-0                                      | U-0                                        | R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup> |

|---------------|------------------------------|---------------------------------------------------------------------|-------------------------------|--------------------------------------------|--------------------------------------------|----------------------|----------------------|

| UARTEN        | —                            | USIDL                                                               | IREN <sup>(1)</sup>           | RTSMD                                      | _                                          | UEN1                 | UEN0                 |

| bit 15        |                              |                                                                     |                               |                                            |                                            |                      | bit 8                |

| R/C-0, HC     | R/W-0                        | R/W-0, HC                                                           | R/W-0                         | R/W-0                                      | R/W-0                                      | R/W-0                | R/W-0                |

| WAKE          | LPBACK                       | ABAUD                                                               | URXINV                        | BRGH                                       | PDSEL1                                     | PDSEL0               | STSEL                |

| bit 7         | LIDAON                       |                                                                     | UIXIIIV                       | BRGH                                       | TDSELT                                     | T DOLLO              | bit 0                |

|               |                              |                                                                     |                               |                                            |                                            |                      |                      |

| Legend:       |                              | C = Clearable                                                       |                               |                                            | are Clearable bi                           |                      |                      |

| R = Readabl   |                              | W = Writable                                                        | oit                           |                                            | mented bit, read                           |                      |                      |

| -n = Value at | POR                          | '1' = Bit is set                                                    |                               | '0' = Bit is cle                           | ared                                       | x = Bit is unkn      | iown                 |

| bit 15        | UARTEN: UA                   | ARTx Enable bit                                                     |                               |                                            |                                            |                      |                      |

|               |                              | s enabled; all U                                                    |                               | e controlled by l                          | JARTx. as defir                            | ned by UEN<1:        | 0>                   |

|               |                              | s disabled; all L                                                   |                               |                                            |                                            |                      |                      |

| bit 14        | Unimplemen                   | ted: Read as 'd                                                     | )'                            |                                            |                                            |                      |                      |

| bit 13        | USIDL: UAR                   | Tx Stop in Idle N                                                   | /lode bit                     |                                            |                                            |                      |                      |

|               |                              | nues module op                                                      |                               |                                            | ers Idle mode                              |                      |                      |

|               |                              | s module opera                                                      |                               |                                            |                                            |                      |                      |

| bit 12        |                              | Encoder and D                                                       |                               |                                            |                                            |                      |                      |

|               |                              | oder and decoo<br>oder and decoo                                    |                               |                                            |                                            |                      |                      |

| bit 11        | RTSMD: Mod                   | le Selection for                                                    | UxRTS Pin bi                  | t                                          |                                            |                      |                      |

|               |                              | in is in Simplex<br>in is in Flow Co                                |                               |                                            |                                            |                      |                      |

| bit 10        | Unimplemen                   | ted: Read as 'd                                                     | )'                            |                                            |                                            |                      |                      |

| bit 9-8       | UEN<1:0>: U                  | IARTx Enable b                                                      | its <sup>(2)</sup>            |                                            |                                            |                      |                      |

|               | 10 = UxTX, U<br>01 = UxTX, U | JxRX and UxBC<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins are | nd UxRTS pin<br>S pins are en | is are enabled a<br>abled <u>and us</u> ec | an <u>d used</u><br>I; <u>UxCTS</u> pin is | controlled by p      | ort latches          |

| bit 7         | WAKE: Wake                   | e-up on Start Bit                                                   | Detect During                 | g Sleep Mode E                             | Enable bit                                 |                      |                      |

|               | cleared in                   | vill continue to<br>n hardware on t                                 | •                             |                                            | rupt is generate                           | ed on the fallin     | ig edge, bit is      |

| hit C         |                              | -up is enabled                                                      | Mada Salaat                   | hit                                        |                                            |                      |                      |

| bit 6         |                              | ARTx Loopback<br>Loopback mode                                      |                               | DIL                                        |                                            |                      |                      |

|               |                              | k mode is disab                                                     |                               |                                            |                                            |                      |                      |

| bit 5         | -                            | o-Baud Enable                                                       |                               |                                            |                                            |                      |                      |

|               | cleared in                   | baud rate meas<br>n hardware upo                                    | n completion                  |                                            | er – requires re                           | ception of a Sy      | nc field (55h);      |

|               |                              | e measurement                                                       |                               | •                                          |                                            |                      |                      |

| bit 4         |                              | RTx Receive Po                                                      | plarity Inversio              | n dit                                      |                                            |                      |                      |

|               | 1 = UxRX IdI<br>0 = UxRX IdI |                                                                     |                               |                                            |                                            |                      |                      |

| Note 1: Th    | nis feature is is            | only available fo                                                   | or the 16x BR                 | G mode (BRGF                               | <b>I</b> = 0).                             |                      |                      |

|               |                              | , donondo on th                                                     |                               | -                                          |                                            |                      |                      |

#### REGISTER 15-1: UXMODE: UARTX MODE REGISTER

**2:** The bit availability depends on the pin availability.

#### REGISTER 15-3: UXTXREG: UARTX TRANSMIT REGISTER

| U-x    | U-x | U-x | U-x | U-x | U-x | U-x | W-x   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | _   | —   | UTX8  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-x   | W-x  | W-x  | W-x  | W-x  | W-x  | W-x  | W-x   |

|-------|------|------|------|------|------|------|-------|

| UTX7  | UTX6 | UTX5 | UTX4 | UTX3 | UTX2 | UTX1 | UTX0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-9 Unimplemented: Read as '0'

bit 8 **UTX8:** Data of the Transmitted Character bit (in 9-bit mode)

bit 7-0 UTX<7:0>: Data of the Transmitted Character bits

# REGISTER 15-4: UxRXREG: UARTx RECEIVE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC |

|--------|-----|-----|-----|-----|-----|-----|----------|

| —      | —   | —   | —   | —   | —   | _   | URX8     |

| bit 15 |     |     |     |     |     |     | bit 8    |

| R-0, HSC |

|----------|----------|----------|----------|----------|----------|----------|----------|

| URX7     | URX6     | URX5     | URX4     | URX3     | URX2     | URX1     | URX0     |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/ | HSC = Hardware Settable/Clearable bit |                    |  |  |  |

|-------------------|--------------------------|---------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0'    |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

bit 15-9 Unimplemented: Read as '0'

bit 8 URX8: Data of the Received Character bit (in 9-bit mode)

bit 7-0 URX<7:0>: Data of the Received Character bits

#### 16.2.6 ALRMVAL REGISTER MAPPINGS

# REGISTER 16-8: ALMTHDY: ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0      | U-0 | U-0     | R/W-x   | R/W-x            | R/W-x            | R/W-x   | R/W-x            |

|----------|-----|---------|---------|------------------|------------------|---------|------------------|

| —        | —   | —       | MTHTEN0 | MTHONE3          | MTHONE2          | MTHONE1 | MTHONE0          |

| bit 15   |     |         |         |                  |                  |         | bit 8            |

|          |     |         |         |                  |                  |         |                  |

| 11.0     |     | D/1/    |         | D/14/            |                  |         |                  |

| U-0      | U-0 | R/W-x   | R/W-x   | R/W-x            | R/W-x            | R/W-x   | R/W-x            |

| <u> </u> |     | DAYTEN1 | DAYTEN0 | R/W-X<br>DAYONE3 | R/W-X<br>DAYONE2 | DAYONE1 | R/W-x<br>DAYONE0 |

#### Legend:

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13<br>bit 12 | <b>Unimplemented:</b> Read as '0'<br><b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit<br>Contains a value of '0' or '1'. |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8            | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits<br>Contains a value from 0 to 9.                                          |

| bit 7-6             | Unimplemented: Read as '0'                                                                                                                   |

| bit 5-4             | <b>DAYTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Day's Tens Digit bits<br>Contains a value from 0 to 3.                               |

| bit 3-0             | <b>DAYONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Day's Ones Digit bits<br>Contains a value from 0 to 9.                               |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# REGISTER 16-9: ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0    | U-0    | U-0    | R/W-x  | R/W-x  | R/W-x  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | —      | —      | —      | WDAY2  | WDAY1  | WDAY0  |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

| —      | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits<br>Contains a value from 0 to 6. |

|           |                                                                                              |

| bit 7-6   | Unimplemented: Read as '0'                                                                   |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits                             |

|           | Contains a value from 0 to 2.                                                                |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits                             |

|           | Contains a value from 0 to 9.                                                                |

|           |                                                                                              |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# 17.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCONL

- CLCxCONH

- CLCxSEL

- CLCxGLSL

- CLCxGLSH

The CLCx Control registers (CLCxCONL and CLCxCONH) are used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Source Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Select registers (CLCxGLSL and CLCxGLSH) allow the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

# REGISTER 17-1: CLCxCONL: CLCx CONTROL REGISTER (LOW)

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 L                                                                                                                                                    | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                              | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   |                                    | U-0<br>—<br>R/W-0<br>MODE1 | U-0<br>bit 8<br>R/W-0<br>MODE0<br>bit 0                                                                             |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 15<br>R-0<br>LCOE<br>bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15<br>bit 14-12<br>bit 14-12<br>bit 11<br>bit 10<br>bit 9-8<br>bit 7                                                    | LCOUT<br>bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt | LCPOL<br>W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene | bit<br>xing input sign<br>s logic zero c<br>o'<br>nterrupt Enabl<br>ed when a risi | U-0<br>—<br>U = Unimpler<br>'0' = Bit is cle<br>nals<br>putputs | R/W-0<br>MODE2<br>nented bit, read | MODE1                      | R/W-0<br>MODE0<br>bit 0                                                                                             |  |  |  |  |  |  |

| R-0<br>LCOE<br>bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PO<br>bit 15<br>bit 14-12<br>bit 14-12<br>bit 11<br>bit 10<br>bit 10<br>bit 9-8<br>bit 7                                                    | LCOUT<br>bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt | LCPOL<br>W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene | bit<br>xing input sign<br>s logic zero c<br>o'<br>nterrupt Enabl<br>ed when a risi | U = Unimpler<br>'0' = Bit is cle<br>nals<br>putputs             | MODE2                              | MODE1                      | R/W-0<br>MODE0<br>bit 0                                                                                             |  |  |  |  |  |  |

| LCOE<br>bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15 L<br>bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                          | LCOUT<br>bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt | LCPOL<br>W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene | bit<br>xing input sign<br>s logic zero c<br>o'<br>nterrupt Enabl<br>ed when a risi | U = Unimpler<br>'0' = Bit is cle<br>nals<br>putputs             | MODE2                              | MODE1                      | MODE0<br>bit 0                                                                                                      |  |  |  |  |  |  |

| LCOE<br>bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15 L<br>bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                          | LCOUT<br>bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt | LCPOL<br>W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene | bit<br>xing input sign<br>s logic zero c<br>o'<br>nterrupt Enabl<br>ed when a risi | U = Unimpler<br>'0' = Bit is cle<br>nals<br>putputs             | MODE2                              | MODE1                      | MODE0<br>bit 0                                                                                                      |  |  |  |  |  |  |

| bit 7<br>Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15<br>bit 14-12<br>bit 14-12<br>bit 10<br>bit 10<br>bit 9-8<br>bit 7                                                                             | bit<br>OR<br>LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt          | W = Writable I<br>'1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and hance<br>ted: Read as '0<br>Positive Edge In<br>will be generated<br>will not be generated        | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | nented bit, read                   | d as '0'                   | bit 0                                                                                                               |  |  |  |  |  |  |

| Legend:<br>R = Readable b<br>-n = Value at PC<br>bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                                                       | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | '1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and ha<br><b>nted:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                           | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | ared                               |                            |                                                                                                                     |  |  |  |  |  |  |

| R = Readable b         -n = Value at PC         bit 15       L         bit 14-12       L         bit 14-12       L         bit 11       L         bit 10       L         bit 9-8       L         bit 7       L | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | '1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and ha<br><b>nted:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                           | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | ared                               |                            | ıown                                                                                                                |  |  |  |  |  |  |

| R = Readable b         -n = Value at PC         bit 15       L         bit 14-12       L         bit 14-12       L         bit 11       L         bit 10       L         bit 9-8       L         bit 7       L | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | '1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and ha<br><b>nted:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                           | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | ared                               |                            | ıown                                                                                                                |  |  |  |  |  |  |

| -n = Value at P(<br>bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                                                                                    | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | '1' = Bit is set<br>Enable bit<br>enabled and mit<br>disabled and ha<br><b>nted:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                           | xing input sign<br>is logic zero c<br>)'<br>iterrupt Enabl<br>ed when a risi       | '0' = Bit is cle<br>nals<br>putputs<br>le bit                   | ared                               |                            | nown                                                                                                                |  |  |  |  |  |  |

| bit 15 L<br>bit 14-12 L<br>bit 11 L<br>bit 10 L<br>bit 9-8 L<br>bit 7 L                                                                                                                                        | LCEN: CLCx<br>1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                      | Enable bit<br>enabled and mi<br>disabled and ha<br><b>ated:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                | ns logic zero c<br>)'<br>nterrupt Enabl<br>ed when a risi                          | nals<br>outputs<br>e bit                                        |                                    | x = Bit is unkr            | nown                                                                                                                |  |  |  |  |  |  |

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 L                                                                                                                                                    | 1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                    | enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                              | ns logic zero c<br>)'<br>nterrupt Enabl<br>ed when a risi                          | outputs<br>e bit                                                | on LCOUT                           |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 L                                                                                                                                                    | 1 = CLCx is<br>0 = CLCx is<br>Unimplement<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                    | enabled and mi<br>disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                              | ns logic zero c<br>)'<br>nterrupt Enabl<br>ed when a risi                          | outputs<br>e bit                                                | on LCOUT                           |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 L                                                                                                                                                    | 0 = CLCx is 0<br>Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                                  | disabled and ha<br><b>ited:</b> Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                                                | ns logic zero c<br>)'<br>nterrupt Enabl<br>ed when a risi                          | outputs<br>e bit                                                | on LCOUT                           |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 14-12 U<br>bit 11 I<br>bit 10 I<br>bit 10 I<br>bit 9-8 U<br>bit 7 I                                                                                                                                        | Unimplemen<br>INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                                                   | nted: Read as '0<br>Positive Edge Ir<br>will be generate<br>will not be gene                                                                                                          | )'<br>hterrupt Enabl<br>ed when a risi                                             | e bit                                                           | on LCOUT                           |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 11                                                                                                                                                                                                         | INTP: CLCx I<br>1 = Interrupt<br>0 = Interrupt                                                                                 | Positive Edge Ir<br>will be generate<br>will not be gene                                                                                                                              | nterrupt Enabl<br>ed when a risi                                                   |                                                                 | on LCOUT                           |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 10 I<br>bit 9-8 I<br>bit 7 I                                                                                                                                                                               | 1 = Interrupt<br>0 = Interrupt                                                                                                 | will be generate<br>will not be gene                                                                                                                                                  | ed when a risi                                                                     |                                                                 | on LCOUT                           |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 10 I<br>bit 9-8 U<br>bit 7 I                                                                                                                                                                               | 0 = Interrupt                                                                                                                  | will not be gene                                                                                                                                                                      |                                                                                    | ing eage occurs                                                 | ULCOOL                             |                            | INTP: CLCx Positive Edge Interrupt Enable bit<br>1 = Interrupt will be generated when a rising edge occurs on LCOUT |  |  |  |  |  |  |

| bit 9-8                                                                                                                                                                                                        | INTN: CLCx                                                                                                                     |                                                                                                                                                                                       | <ul> <li>0 = Interrupt will not be generated</li> </ul>                            |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 9-8                                                                                                                                                                                                        | INTN: CLCx Negative Edge Interrupt Enable bit                                                                                  |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 9-8 <b>U</b><br>bit 7 <b>L</b>                                                                                                                                                                             | 1 = Interrupt will be generated when a falling edge occurs on LCOUT                                                            |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 7 L                                                                                                                                                                                                        | 0 = Interrupt will not be generated                                                                                            |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                | Unimplemented: Read as '0'                                                                                                     |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                | LCOE: CLCx Port Enable bit                                                                                                     |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                | 1 = CLCx port pin output is enabled                                                                                            |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                | 0 = CLCx port pin output is disabled                                                                                           |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                | LCOUT: CLCx Data Output Status bit                                                                                             |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                | 1 = CLCx output high<br>0 = CLCx output low                                                                                    |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 5 L                                                                                                                                                                                                        | LCPOL: CLC                                                                                                                     | x Output Polari                                                                                                                                                                       | ty Control bit                                                                     |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                |                                                                                                                                | out of the module                                                                                                                                                                     |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                | 0 = The outr                                                                                                                   | ut of the medul                                                                                                                                                                       |                                                                                    | ed                                                              |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

| bit 4-3 <b>L</b>                                                                                                                                                                                               | 0 = The output of the module is not inverted<br>Unimplemented: Read as '0'                                                     |                                                                                                                                                                                       |                                                                                    |                                                                 |                                    |                            |                                                                                                                     |  |  |  |  |  |  |

#### REGISTER 17-3: CLCxSEL: CLCx INPUT MUX SELECT REGISTER (CONTINUED)

- bit 6-4 DS2<2:0>: Data Selection MUX 2 Signal Selection bits

- 111 = MCCP2 Compare Event Flag (CCP2IF)

- 110 = MCCP1 Compare Event Flag (CCP1IF)

- 101 = Digital logic low

- 100 = A/D end of conversion event

- For CLC1:

- 011 = UART1 TX

- 010 = Comparator 1 output

- 001 = CLC2 output

- 000 = CLCINB I/O pin

- For CLC2:

- 011 = UART2 TX

- 010 = Comparator 1 output

- 001 = CLC1 output

- 000 = CLCINB I/O pin

- bit 3 Unimplemented: Read as '0'

- bit 2-0 DS1<2:0>: Data Selection MUX 1 Signal Selection bits

- 111 = SCCP5 Compare Event Flag (CCP5IF)

- 110 = SCCP4 Compare Event Flag (CCP4IF)

- 101 = Digital logic low

- 100 = 8 MHz FRC clock source

- 011 = LPRC clock source

- 010 = SOSC clock source

- 001 = System clock (TCY)

- 000 = CLCINA I/O pin

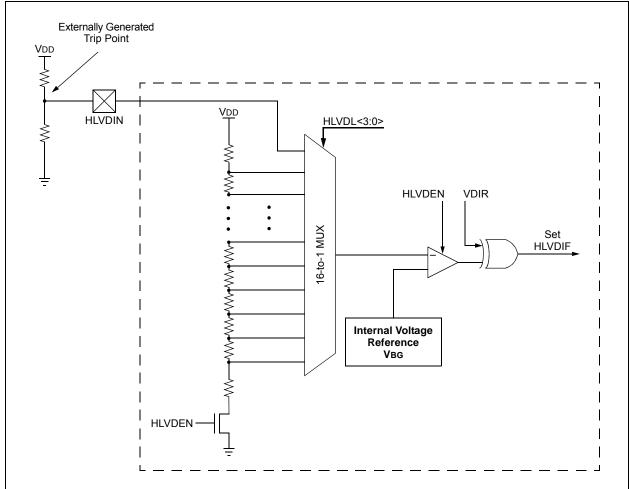

# 18.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

| Note: | This data sheet summarizes the features of<br>this group of PIC24F devices. It is not<br>intended to be a comprehensive reference                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|       | source. For more information on<br>the High/Low-Voltage Detect, refer to<br>the "PIC24F Family Reference Manual",<br>"High-Level Integration with |

|       | Programmable High/Low-Voltage<br>Detect (HLVD)" (DS39725).                                                                                        |

The High/Low-Voltage Detect module (HLVD) is a programmable circuit that allows the user to specify both the device voltage trip point and the direction of change.

An interrupt flag is set if the device experiences an excursion past the trip point in the direction of change. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The HLVD Control register (see Register 18-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

### FIGURE 18-1: HIGH/LOW-VOLTAGE DETECT (HLVD) MODULE BLOCK DIAGRAM

# 19.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR)

Conversion

- Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (internal and external)

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H)

Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU, and a configurable results buffer. There is a legacy 10-bit mode on this A/D to allow the option to run with lower resolution in order to obtain higher throughput. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 19-1.