Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 22x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km104t-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-13: MSSP1 (I<sup>2</sup>C<sup>™</sup>/SPI) REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                                                                                                    | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-------|-------|-------|-------|---------------|

| SSP1BUF   | 200h  | —      | _      | _      | —      | —      | —      | _     | —     | MSSP1 Receive Buffer/Transmit Register                                                                                   |         |       |       |       |       | 00xx  |       |               |

| SSP1CON1  | 202h  | _      | _      | _      | _      | _      | _      | _     | _     | WCOL                                                                                                                     | SSPOV   | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | 0000          |

| SSP1CON2  | 204h  | _      | _      | _      | _      | _      | _      | _     | _     | GCEN                                                                                                                     | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 0000          |

| SSP1CON3  | 206h  | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM                                                                                                                   | PCIE    | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  | 0000          |

| SSP1STAT  | 208h  | _      | _      | _      | _      | _      | _      | —     | _     | SMP                                                                                                                      | CKE     | D/A   | Р     | S     | R/W   | UA    | BF    | 0000          |

| SSP1ADD   | 20Ah  | —      | _      | _      | —      | _      | —      |       |       | MSSP1 Address Register in I <sup>2</sup> C Slave Mode<br>MSSP1 Baud Rate Reload Register in I <sup>2</sup> C Master Mode |         |       |       |       |       |       | 0000  |               |

| SSP1MSK   | 20Ch  | _      | _      | _      | _      | _      | _      |       | _     | MSK7                                                                                                                     | MSK6    | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  | OOFF          |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-14: MSSP2 (I<sup>2</sup>C<sup>™</sup>/SPI) REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                                                                                                    | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-------|-------|-------|-------|---------------|

| SSP2BUF <sup>(1)</sup>  | 210h  | —      | _      | —      | —      |        | _      |       | _     | MSSP2 Receive Buffer/Transmit Register                                                                                   |         |       |       |       |       | 00xx  |       |               |

| SSP2CON1 <sup>(1)</sup> | 212h  | _      | _      | _      | _      | _      | _      | _     | _     | WCOL                                                                                                                     | SSPOV   | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | 0000          |

| SSP2CON2 <sup>(1)</sup> | 214h  | _      | _      | _      | _      | _      | _      | _     | _     | GCEN                                                                                                                     | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 0000          |

| SSP2CON3 <sup>(1)</sup> | 216h  | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM                                                                                                                   | PCIE    | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  | 0000          |

| SSP2STAT <sup>(1)</sup> | 218h  | _      | _      | _      | _      | _      | _      | _     | _     | SMP                                                                                                                      | CKE     | D/A   | Р     | S     | R/W   | UA    | BF    | 0000          |

| SSP2ADD <sup>(1)</sup>  | 21Ah  | —      | _      | —      | —      | _      | —      | _     | _     | MSSP2 Address Register in I <sup>2</sup> C Slave Mode<br>MSSP2 Baud Rate Reload Register in I <sup>2</sup> C Master Mode |         |       |       |       |       |       | 0000  |               |

| SSP2MSK <sup>(1)</sup>  | 21Ch  | —      | _      | _      | _      |        | _      | _     | _     | MSK7                                                                                                                     | MSK6    | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  | 00FF          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

### 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time. It is also possible to program single words.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks, and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

| Note: | Writing                                 | to | а | location | multiple | times, |  |  |  |  |  |  |

|-------|-----------------------------------------|----|---|----------|----------|--------|--|--|--|--|--|--|

|       | without erasing it, is not recommended. |    |   |          |          |        |  |  |  |  |  |  |

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.5 "Programming Operations"** for further details.

### 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | —   | —   | —   | —     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

|            |       |       |                        |     |     |     |       |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearable b  | it               |

|----------------------|------------------------|----------------------------|------------------|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit           | W = Writable bit |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit, rea | d as '0'         |

| bit 15   | WR: Write Control bit                                                                                                                                                                                                        |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Initiates a Flash memory program or erase operation; the operation is self-timed and the bit is                                                                                                                          |

|          | cleared by hardware once the operation is complete                                                                                                                                                                           |

|          | <ul><li>0 = Program or erase operation is complete and inactive</li></ul>                                                                                                                                                    |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                       |

|          | 1 = Enables Flash program/erase operations                                                                                                                                                                                   |

|          | 0 = Inhibits Flash program/erase operations                                                                                                                                                                                  |

| bit 13   | WRERR: Write Sequence Error Flag bit                                                                                                                                                                                         |

|          | 1 = An improper program or erase sequence attempt, or termination has occurred (bit is set automatically                                                                                                                     |

|          | on any set attempt of the WR bit)                                                                                                                                                                                            |

|          | 0 = The program or erase operation completed normally                                                                                                                                                                        |

| bit 12   | PGMONLY: Program Only Enable bit <sup>(4)</sup>                                                                                                                                                                              |

| bit 11-7 | Unimplemented: Read as '0'                                                                                                                                                                                                   |

| bit 6    | ERASE: Erase/Program Enable bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Performs the erase operation specified by the NVMOP&lt;5:0&gt; bits on the next WR command</li> <li>0 = Performs the program operation specified by the NVMOP&lt;5:0&gt; bits on the next WR command</li> </ul> |

| bit 5-0  | NVMOP<5:0>: Programming Operation Command Byte bits <sup>(1)</sup>                                                                                                                                                           |

|          | Erase Operations (when ERASE bit is '1'):                                                                                                                                                                                    |

|          | 1010xx = Erase entire boot block (including code-protected boot block) <sup>(2)</sup>                                                                                                                                        |

|          | 1001xx = Erase entire memory (including boot block, configuration block, general block) <sup>(2)</sup>                                                                                                                       |

|          | 011010 = Erase 4 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                         |

|          | 011001 = Erase 2 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                         |

|          | 011000 = Erase 1 row of Flash memory <sup>(3)</sup>                                                                                                                                                                          |

|          | 0101xx = Erase entire configuration block (except code protection bits)                                                                                                                                                      |

|          | 0100xx = Erase entire data EEPROM <sup>(4)</sup>                                                                                                                                                                             |

|          | 0011xx = Erase entire general memory block programming operations                                                                                                                                                            |

|          | 0001xx = Write 1 row of Flash memory (when ERASE bit is '0') <sup>(3)</sup>                                                                                                                                                  |

| Note 1:  | All other combinations of NVMOP<5:0> are no operation.                                                                                                                                                                       |

| 2:       | Available in ICSP™ mode only. Refer to the device programming specification.                                                                                                                                                 |

| 2.       | The address in the Table Deinter decides which rows will be created                                                                                                                                                          |

- 3: The address in the Table Pointer decides which rows will be erased.

- 4: This bit is used only while accessing data EEPROM.

**IFS1: INTERRUPT FLAG STATUS REGISTER 1**

**REGISTER 8-6:**

| R/W-0, HS     | R/W-0, HS       | R/W-0, HS                       | R/W-0, HS       | R/W-0, HS         | U-0              | U-0             | U-0       |

|---------------|-----------------|---------------------------------|-----------------|-------------------|------------------|-----------------|-----------|

| U2TXIF        | U2RXIF          | INT2IF                          | CCT4IF          | CCT3IF            |                  | —               | —         |

| bit 15        |                 |                                 |                 |                   |                  |                 | bit 8     |

|               |                 |                                 |                 |                   |                  |                 |           |

| U-0           | R/W-0, HS       | U-0                             | R/W-0, HS       | R/W-0, HS         | R/W-0, HS        | R/W-0, HS       | R/W-0, HS |

| —             | CCP5IF          | —                               | INT1IF          | CNIF              | CMIF             | BCL1IF          | SSP1IF    |

| bit 7         |                 |                                 |                 |                   |                  |                 | bit 0     |

|               |                 |                                 |                 |                   |                  |                 |           |

| Legend:       |                 |                                 | re Settable bit |                   |                  |                 |           |

| R = Readable  |                 | W = Writable                    |                 | -                 | nented bit, read | d as '0'        |           |

| -n = Value at | POR             | '1' = Bit is set                |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown      |

|               |                 |                                 |                 |                   |                  |                 |           |

| bit 15        |                 | T2 Transmitter                  |                 | Status bit        |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

| bit 14        | -               | RT2 Receiver Ir                 |                 | atus hit          |                  |                 |           |

|               |                 | request has oc                  |                 |                   |                  |                 |           |

|               |                 | equest has not                  |                 |                   |                  |                 |           |

| bit 13        | INT2IF: Exter   | nal Interrupt 2                 | Flag Status bit |                   |                  |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

|               | •               | equest has not                  |                 |                   |                  |                 |           |

| bit 12        |                 | -                               |                 | pt Flag Status b  | bit              |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

| bit 11        | -               | equest has not                  |                 | nt Elan Statua k  | -:+              |                 |           |

|               | -               | request has oc                  |                 | pt Flag Status b  | JIL              |                 |           |

|               |                 | request has not                 |                 |                   |                  |                 |           |

| bit 10-7      | -               | ted: Read as '                  |                 |                   |                  |                 |           |

| bit 6         | CCP5IF: Cap     | ture/Compare                    | 5 Event Interru | pt Flag Status I  | bit              |                 |           |

|               | 1 = Interrupt r | equest has oc                   | curred          |                   |                  |                 |           |

|               | 0 = Interrupt r | equest has no                   | occurred        |                   |                  |                 |           |

| bit 5         | •               | ted: Read as '                  |                 |                   |                  |                 |           |

| bit 4         |                 | nal Interrupt 1                 | •               |                   |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

| bit 3         |                 | •                               |                 | lag Status bit    |                  |                 |           |

| DIUS          | -               | hange Notifica<br>equest has oc | -               | lay Status bit    |                  |                 |           |

|               |                 | request has not                 |                 |                   |                  |                 |           |

| bit 2         | CMIF: Compa     | arator Interrupt                | Flag Status Bit | t                 |                  |                 |           |

|               | -               | equest has oc                   | -               |                   |                  |                 |           |

|               | -               | equest has no                   |                 |                   |                  |                 |           |

| bit 1         |                 |                                 |                 | upt Flag Status   | bit              |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

| <b>L</b> H 0  | -               | equest has not                  |                 |                   |                  |                 |           |

| bit 0         |                 | SP1 SPI/I <sup>2</sup> C Ev     | •               | lag Status bit    |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

|               | 5 monupti       |                                 |                 |                   |                  |                 |           |

| U-0                 | R/W-1                                    | R/W-0                                                                       | R/W-0            | U-0                                | U-0              | U-0                | U-0     |  |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------|------------------|------------------------------------|------------------|--------------------|---------|--|

| 0-0                 | NVMIP2                                   | NVMIP1                                                                      | NVMIP0           | 0-0                                | 0-0              | 0-0                | 0-0     |  |

| <br>bit 15          |                                          |                                                                             |                  | —                                  | _                | _                  | <br>bit |  |

|                     |                                          |                                                                             |                  |                                    |                  |                    | bit     |  |

| U-0                 | R/W-1                                    | R/W-0                                                                       | R/W-0            | U-0                                | R/W-1            | R/W-0              | R/W-0   |  |

| _                   | AD1IP2                                   | AD1IP1                                                                      | AD1IP0           |                                    | U1TXIP2          | U1TXIP1            | U1TXIP0 |  |

| bit 7               |                                          |                                                                             |                  |                                    |                  |                    | bit     |  |

| Legend:             |                                          |                                                                             |                  |                                    |                  |                    |         |  |

| R = Readab          | ole bit                                  | W = Writable                                                                | bit              | U = Unimplem                       | nented bit, read | 1 as '0'           |         |  |

| -n = Value a        | at POR                                   | '1' = Bit is set                                                            |                  | '0' = Bit is clea                  | ared             | x = Bit is unknown |         |  |

| =                   |                                          |                                                                             |                  |                                    |                  |                    |         |  |

| bit 15<br>bit 14-12 | -                                        | ited: Read as '<br>: NVM Interrup                                           |                  |                                    |                  |                    |         |  |

|                     | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                   | abled            | .,                                 |                  |                    |         |  |

| bit 11-7            | -                                        | ted: Read as '                                                              |                  |                                    |                  |                    |         |  |

| bit 6-4             | 111 = Interru<br>•<br>•<br>001 = Interru | A/D Conversic<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis | highest priority | terrupt Priority I<br>/ interrupt) | bits             |                    |         |  |

| bit 3               | Unimplemen                               | ted: Read as '                                                              | 0'               |                                    |                  |                    |         |  |

| bit 2-0             |                                          | ➤: UART1 Trans<br>pt is Priority 7 (                                        | •                |                                    |                  |                    |         |  |

|                     |                                          | pt is Priority 1<br>pt source is dis                                        | abled            |                                    |                  |                    |         |  |

#### REGISTER 8-22: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

#### REGISTER 8-31: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

| _       | —   | —   | —   | —   | —       | —       | —       |

| bit 15  |     | •   |     |     | •       |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _       | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Logondi |     |     |     |     |         |         |         |

| Legend: |  |

|---------|--|

|---------|--|

bit 2-0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### 13.5 Auxiliary Output

The MCCPx and SCCPx modules have an auxiliary (secondary) output that provides other peripherals access to internal module signals. The auxiliary output is intended to connect to other MCCP or SCCP modules, or other digital peripherals, to provide these types of functions:

- Time Base Synchronization

- Peripheral Trigger and Clock Inputs

- Signal Gating

The type of output signal is selected using the AUXOUT<1:0> control bits (CCPxCON2H<4:3>). The type of output signal is also dependent on the module operating mode.

On the PIC24FV16KM204 family of devices, only the CTMU discharge trigger has access to the auxiliary output signal.

| AUXOUT<1:0> | CCSEL | MOD<3:0> | Comments                  | Signal Description                  |

|-------------|-------|----------|---------------------------|-------------------------------------|

| 00          | x     | xxxx     | Auxiliary output disabled | No Output                           |

| 01          | 0     | 0000     | Time Base modes           | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Special Event Trigger Output        |

| 11          |       |          |                           | No Output                           |

| 01          | 0     | 0001     | Output Compare modes      | Time Base Period Reset or Rollover  |

| 10          |       | through  |                           | Output Compare Event Signal         |

| 11          |       | 1111     |                           | Output Compare Signal               |

| 01          | 1     | xxxx     | Input Capture modes       | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Reflects the Value of the ICDIS bit |

| 11          |       |          |                           | Input Capture Event Signal          |

#### TABLE 13-5: AUXILIARY OUTPUT

| R/W-0         | U-0                                                              | R/W-0                                  | r-0            | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |  |  |  |

|---------------|------------------------------------------------------------------|----------------------------------------|----------------|--------------------------------------|------------------------|------------------------|------------------------|--|--|--|

| CCPON         |                                                                  | CCPSIDL                                | r              | TMRSYNC                              | CLKSEL2 <sup>(1)</sup> | CLKSEL1 <sup>(1)</sup> | CLKSEL0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                  |                                        |                |                                      | •                      | •                      | bit 8                  |  |  |  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |  |  |  |

| R/W-0         | R/W-0                                                            | R/W-0                                  | R/W-0          | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |  |  |  |

| TMRPS1        | TMRPS0                                                           | T32                                    | CCSEL          | MOD3                                 | MOD2                   | MOD1                   | MOD0                   |  |  |  |

| bit 7         |                                                                  |                                        |                |                                      |                        |                        | bit (                  |  |  |  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |  |  |  |

| Legend:       |                                                                  | r = Reserved I                         |                |                                      |                        |                        |                        |  |  |  |

| R = Readable  |                                                                  | W = Writable I                         | oit            |                                      | nented bit, read       |                        |                        |  |  |  |

| -n = Value at | POR                                                              | '1' = Bit is set                       |                | '0' = Bit is clea                    | ared                   | x = Bit is unkn        | own                    |  |  |  |

| bit 15        | CCPON: CCF                                                       | x Module Enat                          | ole bit        |                                      |                        |                        |                        |  |  |  |

|               | 1 = Module is<br>0 = Module is                                   |                                        | an operating r | node specified b                     | by the MOD<3:          | 0> control bits        |                        |  |  |  |

| bit 14        | Unimplemen                                                       | ted: Read as 'd                        | )'             |                                      |                        |                        |                        |  |  |  |

| bit 13        | CCPSIDL: CO                                                      | CPx Stop in Idle                       | Mode Bit       |                                      |                        |                        |                        |  |  |  |

|               |                                                                  | ues module op<br>s module opera        |                | device enters lo<br>ode              | lle mode               |                        |                        |  |  |  |

| bit 12        | Reserved: Ma                                                     |                                        |                |                                      |                        |                        |                        |  |  |  |

| bit 11        | TMRSYNC: Time Base Clock Synchronization bit                     |                                        |                |                                      |                        |                        |                        |  |  |  |

|               | (CLKSEL<br>0 = Synchron                                          | <b>&lt;2:0&gt;</b> ≠ 000)              |                | k is selected and<br>lock is selecte | -                      |                        | -                      |  |  |  |

| bit 10-8      | CLKSEL<2:0>: CCPx Time Base Clock Select bits <sup>(1)</sup>     |                                        |                |                                      |                        |                        |                        |  |  |  |

|               | 110 = Externa<br>101 = CLC1<br>100 = Reserv<br>011 = LPRC (      | 31 kHz source<br>dary Oscillator<br>ed | t              |                                      |                        |                        |                        |  |  |  |

| bit 7-6       | TMRPS<1:0>                                                       | : Time Base Pr                         | escale Select  | t bits                               |                        |                        |                        |  |  |  |

|               | 11 = 1:64 Pre<br>10 = 1:16 Pre<br>01 = 1:4 Pres<br>00 = 1:1 Pres | scaler<br>caler                        |                |                                      |                        |                        |                        |  |  |  |

| bit 5         | T32: 32-Bit Ti                                                   | me Base Selec                          | t bit          |                                      |                        |                        |                        |  |  |  |

|               |                                                                  |                                        |                | e edge output co<br>e edge output co |                        |                        |                        |  |  |  |

| bit 4         |                                                                  | ure/Compare N                          |                |                                      |                        |                        |                        |  |  |  |

|               | 1 = Input Cap                                                    | -                                      |                |                                      |                        |                        |                        |  |  |  |

#### REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

| -                     |                                                    |                                       |                                                 |                                                                                     |                                    |                     | ,                   |

|-----------------------|----------------------------------------------------|---------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------|---------------------|---------------------|

| R/W-0                 | R/W-0                                              | U-0                                   | U-0                                             | R/W-0                                                                               | R/W-0                              | R/W-0               | R/W-0               |

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup>                              |                                       | —                                               | OPS3 <sup>(3)</sup>                                                                 | OPS2 <sup>(3)</sup>                | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |

| bit 15                |                                                    |                                       |                                                 |                                                                                     |                                    |                     | bit 8               |

|                       |                                                    |                                       |                                                 |                                                                                     |                                    |                     |                     |

| R/W-0                 | R/W-0                                              | R/W-0                                 | R/W-0                                           | R/W-0                                                                               | R/W-0                              | R/W-0               | R/W-0               |

| TRIGEN <sup>(4)</sup> | ONESHOT                                            | ALTSYNC                               | SYNC4                                           | SYNC3                                                                               | SYNC2                              | SYNC1               | SYNC0               |

| bit 7                 |                                                    |                                       |                                                 |                                                                                     |                                    |                     | bit 0               |

|                       |                                                    |                                       |                                                 |                                                                                     |                                    |                     |                     |

| Legend:               |                                                    |                                       |                                                 |                                                                                     |                                    |                     |                     |

| R = Readable          |                                                    | W = Writable I                        | oit                                             | -                                                                                   | nented bit, read                   | l as '0'            |                     |

| -n = Value at         | POR                                                | '1' = Bit is set                      |                                                 | '0' = Bit is clea                                                                   | ared                               | x = Bit is unkr     | iown                |

|                       |                                                    |                                       |                                                 | (1)                                                                                 |                                    |                     |                     |

| bit 15                |                                                    | tput Postscaler                       |                                                 |                                                                                     |                                    |                     |                     |

|                       |                                                    | ostscaler scales                      |                                                 | er output event                                                                     | IS                                 |                     |                     |

| bit 14                |                                                    | trigger Enable                        |                                                 |                                                                                     |                                    |                     |                     |

|                       |                                                    | e can be retrig                       |                                                 | RIGEN bit = 1                                                                       |                                    |                     |                     |

|                       |                                                    |                                       |                                                 | en TRIGEN bit =                                                                     | = 1                                |                     |                     |

| bit 13-12             | Unimplement                                        | ted: Read as 'o                       | )'                                              |                                                                                     |                                    |                     |                     |

| bit 11-8              | OPS3<3:0>: (                                       | CCPx Interrupt                        | Output Postso                                   | ale Select bits <sup>(</sup>                                                        | 3)                                 |                     |                     |

|                       |                                                    | upt every 16th t<br>upt every 15th t  |                                                 |                                                                                     |                                    |                     |                     |

|                       | 0011 = Interru<br>0010 = Interru<br>0001 = Interru | upt every 3rd tir<br>upt every 2nd ti | ne base perio<br>ne base perio<br>me base perio | d match<br>d match or 4th i<br>d match or 3rd<br>od match or 2nc<br>od match or inp | input capture e<br>l input capture | event<br>event      |                     |

| bit 7                 | TRIGEN: CCF                                        | Px Trigger Enal                       | ole bit <sup>(4)</sup>                          |                                                                                     |                                    |                     |                     |

|                       |                                                    | peration of time<br>peration of time  |                                                 |                                                                                     |                                    |                     |                     |

| bit 6                 | ONESHOT: O                                         | ne-Shot Mode                          | Enable bit                                      |                                                                                     |                                    |                     |                     |

|                       |                                                    | t Trigger mode<br>t Trigger mode      |                                                 | igger duration is                                                                   | s set by OSCN                      | T<2:0>              |                     |

| bit 5                 | ALTSYNC: C                                         | CPx Clock Sele                        | ect bits                                        |                                                                                     |                                    |                     |                     |

|                       |                                                    |                                       |                                                 | ule synchroniza                                                                     |                                    |                     |                     |

|                       |                                                    | -                                     |                                                 | nal is the Time                                                                     | Base Reset/ro                      | ollover event       |                     |

| bit 4-0               |                                                    | CCPx Synchroi                         |                                                 | e Select bits                                                                       |                                    |                     |                     |

|                       | See lable 13-                                      | 6 for the definit                     | ion of inputs.                                  |                                                                                     |                                    |                     |                     |

| Note 1: Th            | nis control bit ha                                 | is no function ir                     | Input Capture                                   | e modes.                                                                            |                                    |                     |                     |

|                       | nis control bit ha                                 |                                       |                                                 |                                                                                     |                                    |                     |                     |

|                       | utput postscale s<br>odes.                         | settings from 1:8                     | 5 to 1:16 (0100                                 | )-1111) will resu                                                                   | ult in a FIFO but                  | ffer overflow for   | Input Capture       |

#### REGISTER 13-2: CCPxCON1H: CCPx CONTROL 1 HIGH REGISTERS

4: Clock source options are limited when Trigger operation is enabled; refer to Table 13-1.

#### REGISTER 13-7: CCPxSTATL: CCPx STATUS REGISTER

| U-0           | U-0           | U-0                                    | U-0           | U-0               | U-0              | U-0             | U-0           |

|---------------|---------------|----------------------------------------|---------------|-------------------|------------------|-----------------|---------------|

| _             | _             | —                                      | _             | —                 | _                | —               |               |

| bit 15        |               |                                        |               |                   |                  |                 | bit 8         |

|               |               |                                        | 5/2.2         | 5/2.2             | 5/0.0            | 5/2.2           | 5/2.2         |

| R-0           | W1-0          | W1-0                                   | R/C-0         | R/C-0             | R/C-0            | R/C-0           | R/C-0         |

| CCPTRIG       | TRSET         | TRCLR                                  | ASEVT         | SCEVT             | ICDIS            | ICOV            | ICBNE         |

| bit 7         |               |                                        |               |                   |                  |                 | bit 0         |

| Legend:       |               | C = Clearable                          | bit           |                   |                  |                 |               |

| R = Readabl   | e bit         | W1 = Write '1'                         | only          | U = Unimplem      | nented bit, read | as '0'          |               |

| -n = Value at | POR           | '1' = Bit is set                       |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |

|               |               |                                        |               |                   |                  |                 |               |

| bit 15-8      | Unimplemen    | ted: Read as '0                        | ,             |                   |                  |                 |               |

| bit 7         | CCPTRIG: C    | CPx Trigger Sta                        | tus bit       |                   |                  |                 |               |

|               |               | s been triggered<br>s not been trigg   |               |                   |                  |                 |               |

| <b>h</b> :# 0 |               |                                        |               | eiu in Resel      |                  |                 |               |

| bit 6         |               | x Trigger Set Re                       |               | when TRIGEN       | = 1 (location a) | wave reade as   | : '∩')        |

| bit 5         |               | Px Trigger Clear                       |               |                   |                  | ways icaus as   | , , ,         |

| bit o         |               | is location to ca                      | •             | Trigger when T    | RIGEN = 1 (lo    | cation alwavs r | eads as '0'). |

| bit 4         |               | x Auto-Shutdow                         |               |                   | - (-             | ,               | ····,         |

|               | 1 = A shutdo  | wn event is in p                       | rogress; CCP  | x outputs are in  | the shutdown     | state           |               |

|               | 0 = CCPx ou   | itputs operate n                       | ormally       |                   |                  |                 |               |

| bit 3         | •             | le Edge Compa                          |               |                   |                  |                 |               |

|               |               | edge compare e<br>edge compare e       |               |                   |                  |                 |               |

| bit 2         | •             | Capture x Disat                        |               | occurred          |                  |                 |               |

| Dit Z         | •             | Input Capture :                        |               | es not generate   | a capture ever   | nt              |               |

|               |               | Input Capture                          |               |                   |                  |                 |               |

| bit 1         | ICOV: Input ( | Capture x Buffer                       | Overflow Stat | tus bit           |                  |                 |               |

|               |               | t Capture x FIF                        |               |                   |                  |                 |               |

|               |               | t Capture x FIF                        |               | ot overflowed     |                  |                 |               |

| bit 0         | •             | Capture x Buffe                        |               | -  -   -          |                  |                 |               |

|               |               | apture x buffer h<br>apture x buffer i |               | adie              |                  |                 |               |

|               |               |                                        | c sinply      |                   |                  |                 |               |

'1' = Bit is set

#### REGISTER 14-8: SSPxADD: MSSPx SLAVE ADDRESS/BAUD RATE GENERATOR REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | U-0      | U-0   |

|--------------|-------|--------------|-------|--------------|------------------|----------|-------|

| —            | —     | —            |       | —            | _                | —        | _     |

| bit 15       |       |              |       |              |                  |          | bit 8 |

|              |       |              |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| ADD7         | ADD6  | ADD5         | ADD4  | ADD3         | ADD2             | ADD1     | ADD0  |

| bit 7        |       |              |       |              |                  |          | bit 0 |

|              |       |              |       |              |                  |          |       |

| Legend:      |       |              |       |              |                  |          |       |

| R = Readable | e bit | W = Writable | bit   | U = Unimplen | nented bit, read | l as '0' |       |

'0' = Bit is cleared

x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0

ADD<7:0>: Slave Address/Baud Rate Generator Value bits

SPI Master and I<sup>2</sup>C™ Master modes:

Reload value for the Baud Rate Generator. Clock period is (([SPxADD] + 1) \* 2)/Fosc.

I<sup>2</sup>C Slave modes:

Represents 7 or 8 bits of the slave address, depending on the addressing mode used:

7-Bit mode:

Address is ADD<7:1>; ADD<0> is ignored.

10-Bit LSb mode:

ADD<7:0> are the Least Significant bits of the address.

10-Bit MSb mode:

ADD<2:1> are the two Most Significant bits of the address; ADD<7:3> are always '11110' as a specification requirement; ADD<0> is ignored.

#### REGISTER 14-9: SSPxMSK: I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(1)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                              |

|----------|---------------------------------------------------------|

| bit 7-0  | MSK<7:0>: Slave Address Mask Select bits <sup>(1)</sup> |

|          | 1 = Masking of corresponding bit of SSPxADD is enabled  |

|          | 0 = Masking of corresponding bit of SSPxADD is disabled |

Note 1: MSK0 is not used as a mask bit in 7-bit addressing.

### REGISTER 15-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                 |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                          |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                         |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                     |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                    |

|       | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul> |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                               |

|       | 1 = Receive buffer has overflowed                                                                                                                                             |

|       | 0 = Receive buffer has not overflowed (clearing a previously set OERR bit ( $1 \rightarrow 0$ transition) will reset the receiver buffer and the RSR to the empty state)      |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                    |

|       | <ul> <li>1 = Receive buffer has data; at least one more characters can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                |

© 2013 Microchip Technology Inc.

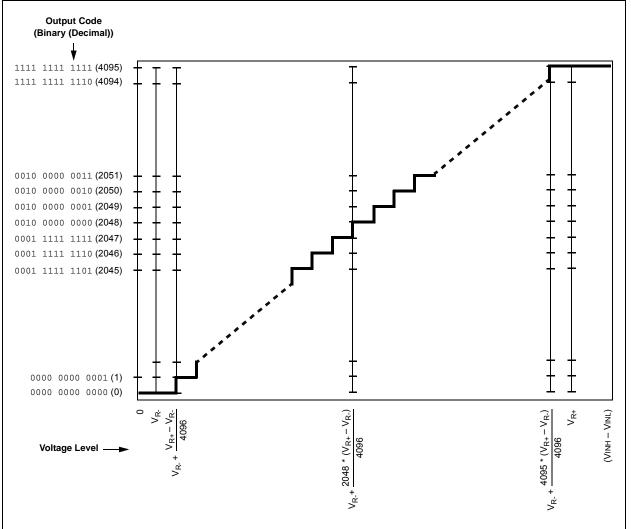

#### **19.3 Transfer Function**

The transfer functions of the A/D Converter in 12-bit resolution are shown in Figure 19-3. The difference of the input voltages (VINH – VINL) is compared to the reference ((VR+) – (VR-)).

- The first code transition occurs when the input voltage is ((VR+) (VR-))/4096 or 1.0 LSb.

- The '0000 0000 0001' code is centered at VR- + (1.5 \* ((VR+) (VR-))/4096).

- The '0010 0000 0000' code is centered at VREFL + (2048.5 \* ((VR+) – (VR-))/4096).

- An input voltage less than VR- + (((VR-) – (VR-))/4096) converts as '0000 0000 0000'.

- An input voltage greater than (VR-) + (4095 ((VR+) – (VR-))/4096) converts as '1111 1111 1111'.

### FIGURE 19-3: 12-BIT A/D TRANSFER FUNCTION

### TABLE 19-2:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>12-BIT FRACTIONAL FORMATS

| VIN/VREF 12-Bit<br>Output Code |                  | 16-Bit Fractional Format<br>Equivalent Decimal Value |       | 16-Bit Signed Fractional Format/<br>Equivalent Decimal Value |        |  |  |  |

|--------------------------------|------------------|------------------------------------------------------|-------|--------------------------------------------------------------|--------|--|--|--|

| +4095/4096                     | 0 1111 1111 1111 | 1111 1111 1111 0000                                  | 0.999 | 0111 1111 1111 1000                                          | 0.999  |  |  |  |

| +4094/4096                     | 0 1111 1111 1110 | 1111 1111 1110 0000                                  | 0.998 | 0111 1111 1110 1000                                          | 0.998  |  |  |  |

|                                | •••              |                                                      |       |                                                              |        |  |  |  |

| +1/4096                        | 0 0000 0000 0001 | 0000 0000 0001 0000                                  | 0.001 | 0000 0000 0000 1000                                          | 0.001  |  |  |  |

| 0/4096                         | 0 0000 0000 0000 | 0000 0000 0000 0000                                  | 0.000 | 0000 0000 0000 0000                                          | 0.000  |  |  |  |

| -1/4096                        | 1 0111 1111 1111 | 0000 0000 0000 0000                                  | 0.000 | 1111 1111 1111 1000                                          | -0.001 |  |  |  |

|                                |                  | •••                                                  |       |                                                              |        |  |  |  |

| -4095/4096                     | 1 0000 0000 0001 | 0000 0000 0000 0000                                  | 0.000 | 1000 0000 0000 1000                                          | -0.999 |  |  |  |

| -4096/4096                     | 1 0000 0000 0000 | 0000 0000 0000 0000                                  | 0.000 | 1000 0000 0000 0000                                          | -1.000 |  |  |  |

### FIGURE 19-5: A/D OUTPUT DATA FORMATS (10-BIT)

| RAM Contents:            |     |     |     |     |     |     | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Read to Bus:             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | I   |

| Integer                  | 0   | 0   | 0   | 0   | 0   | 0   | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Integer           | s0  | s0  | s0  | s0  | s0  | s0  | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Fractional (1.15)        | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   | 0   |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional (1.15) | s0  | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   |

|                          | L   | I   |     |     |     |     |     | 1   | I   |     |     |     |     |     |     |     |

### TABLE 19-3:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>10-BIT INTEGER FORMATS

| VIN/VREF   | 10-Bit Differential<br>Output Code<br>(11-bit result) | 16-Bit Integer Format/<br>Equivalent Decimal Value | 16-Bit Signed Integer Forn<br>Equivalent Decimal Valu |                     |       |  |  |

|------------|-------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|---------------------|-------|--|--|

| +1023/1024 | 011 1111 1111                                         | 0000 0011 1111 1111                                | 1023                                                  | 0000 0001 1111 1111 | 1023  |  |  |

| +1022/1024 | 011 1111 1110                                         | 0000 0011 1111 1110                                | 1022                                                  | 0000 0001 1111 1110 | 1022  |  |  |

|            | •••                                                   |                                                    |                                                       |                     |       |  |  |

| +1/1024    | 000 0000 0001                                         | 0000 0000 0000 0001                                | 1                                                     | 0000 0000 0000 0001 | 1     |  |  |

| 0/1024     | 000 0000 0000                                         | 0000 0000 0000 0000                                | 0                                                     | 0000 0000 0000 0000 | 0     |  |  |

| -1/1024    | 101 1111 1111                                         | 0000 0000 0000 0000                                | 0                                                     | 1111 1111 1111 1111 | -1    |  |  |

|            |                                                       | •••                                                |                                                       |                     |       |  |  |

| -1023/1024 | 100 0000 0001                                         | 0000 0000 0000 0000                                | 0                                                     | 1111 1110 0000 0001 | -1023 |  |  |

| -1024/1024 | 100 0000 0000                                         | 0000 0000 0000 0000                                | 0                                                     | 1111 1110 0000 0000 | -1024 |  |  |

#### REGISTER 22-1: CMxCON: COMPARATOR x CONTROL REGISTERS

| R/W-0                 | R/W-0                                                   | R/W-0                                | R/W-0            | U-0                            | U-0                                   | R/W-0            | R-0              |

|-----------------------|---------------------------------------------------------|--------------------------------------|------------------|--------------------------------|---------------------------------------|------------------|------------------|

| CON                   | COE                                                     | CPOL                                 | CLPWR            | _                              |                                       | CEVT             | COUT             |

| bit 15                | •                                                       |                                      |                  |                                |                                       |                  | bit 8            |

| R/W-0                 | R/W-0                                                   | U-0                                  | R/W-0            | R/W-0                          | U-0                                   | R/W-0            | R/W-0            |

| EVPOL1 <sup>(2)</sup> | EVPOL0 <sup>(2)</sup>                                   | _                                    | CREF1            | CREF0                          | _                                     | CCH1             | CCH0             |

| bit 7                 |                                                         |                                      | UNL I            | UNLI U                         |                                       | 00111            | bit (            |

| Legend:               |                                                         |                                      |                  |                                |                                       |                  |                  |

| R = Readable          | e bit                                                   | W = Writable                         | bit              | U = Unimplen                   | nented bit, read                      | d as '0'         |                  |

| -n = Value at         | POR                                                     | '1' = Bit is set                     |                  | '0' = Bit is clea              |                                       | x = Bit is unkr  | nown             |

|                       |                                                         |                                      |                  |                                |                                       |                  |                  |

| bit 15                | CON: Compa                                              | rator x Enable                       | bit              |                                |                                       |                  |                  |

|                       |                                                         | tor is enabled                       |                  |                                |                                       |                  |                  |

| bit 11                | •                                                       | tor is disabled                      | Enchlo hit       |                                |                                       |                  |                  |