Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 22x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km104t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                             |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|          |                                  | ı                                | Pin Numb      | er                     |                |                                  | ı                                | Pin Numb      | er                     |                |     |        |                                             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CTED1    | 11                               | 20                               | 17            | 7                      | 7              | 11                               | 2                                | 27            | 19                     | 21             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2    | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED3    | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED4    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED5    | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED6    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED7    | _                                | _                                | _             | 5                      | 5              | _                                | _                                | _             | 5                      | 5              | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED8    | _                                | _                                | _             | 13                     | 14             | _                                | _                                | _             | 13                     | 14             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED9    | _                                | 22                               | 19            | 9                      | 10             | _                                | 22                               | 19            | 9                      | 10             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED10   | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED11   | _                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED12   | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED13   | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTPLS    | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   | _      | CTMU Pulse Output                           |

| CVREF    | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | 0   | ANA    | Comparator Voltage Reference Output         |

| CVREF+   | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | Comparator Voltage Reference Positive Input |

| CVREF-   | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | I   | ANA    | Comparator Voltage Reference Negative Input |

| DAC1OUT  | _                                | 23                               | 20            | 10                     | 11             | _                                | 23                               | 20            | 10                     | 11             | 0   | ANA    | DAC1 Output                                 |

| DAC1REF+ | _                                | 2                                | 27            | 19                     | 21             | _                                | 2                                | 27            | 19                     | 21             | I   | ANA    | DAC1 Positive Voltage Reference Input       |

| DAC2OUT  | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | ANA    | DAC2 Output                                 |

| DAC2REF+ | _                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | ı   | ANA    | DAC2 Positive Voltage Reference Input       |

| HLVDIN   | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | ı   | ANA    | External High/Low-Voltage Detect Input      |

| IC1      | 14                               | 19                               | 16            | 6                      | 6              | 11                               | 19                               | 16            | 6                      | 6              | ı   | ST     | MCCP1 Input Capture Input                   |

| IC2      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | ı   | ST     | MCCP2 Input Capture Input                   |

| IC3      | _                                | 23                               | 20            | 13                     | 14             | _                                | 23                               | 20            | 13                     | 14             | Ī   | ST     | MCCP3 Input Capture Input                   |

| IC4      | _                                | 14                               | 11            | 5                      | 5              | _                                | 14                               | 11            | 5                      | 5              | I   | ST     | SCCP4 Input Capture Input                   |

| IC5      | _                                | 15                               | 12            | 12                     | 13             | _                                | 15                               | 12            | 12                     | 13             | I   | ST     | SCCP5 Input Capture Input                   |

| INT0     | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ST     | External Interrupt 0 Input                  |

| INT1     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | External Interrupt 1 Input                  |

| INT2     | 14                               | 20                               | 17            | 7                      | 7              | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | External Interrupt 2 Input                  |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C™ = I<sup>2</sup>C/SMBus input buffer

TABLE 4-3: CPU CORE REGISTERS MAP

| File<br>Name | Addr. | Bit 15                           | Bit 14   | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9    | Bit 8    | Bit 7       | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------|----------------------------------|----------|-----------|-----------|-----------|-----------|----------|----------|-------------|----------|----------|----------|----------|----------|----------|----------|---------------|

| WREG0        | 0h    |                                  |          |           |           |           |           |          | W        | REG0        |          |          |          |          |          |          |          | 0000          |

| WREG1        | 2h    |                                  |          |           |           |           |           |          | W        | /REG1       |          |          |          |          |          |          |          | 0000          |

| WREG2        | 4h    |                                  | WREG2    |           |           |           |           |          |          |             |          |          |          |          | 0000     |          |          |               |

| WREG3        | 6h    |                                  | WREG3    |           |           |           |           |          |          |             |          |          |          |          | 0000     |          |          |               |

| WREG4        | 8h    | WREG4                            |          |           |           |           |           |          |          |             |          |          |          | 0000     |          |          |          |               |

| WREG5        | Ah    | WREG5                            |          |           |           |           |           |          |          |             |          |          |          | 0000     |          |          |          |               |

| WREG6        | Ch    | WREG6                            |          |           |           |           |           |          |          |             |          |          |          | 0000     |          |          |          |               |

| WREG7        | Eh    |                                  |          |           |           |           |           |          | W        | REG7        |          |          |          |          |          |          |          | 0000          |

| WREG8        | 10h   |                                  |          |           |           |           |           |          | W        | REG8        |          |          |          |          |          |          |          | 0000          |

| WREG9        | 12h   |                                  |          |           |           |           |           |          | W        | REG9        |          |          |          |          |          |          |          | 0000          |

| WREG10       | 14h   |                                  | WREG10 0 |           |           |           |           |          |          |             |          |          |          | 0000     |          |          |          |               |

| WREG11       | 16h   |                                  |          |           |           |           |           |          | W        | REG11       |          |          |          |          |          |          |          | 0000          |

| WREG12       | 18h   |                                  |          |           |           |           |           |          | WI       | REG12       |          |          |          |          |          |          |          | 0000          |

| WREG13       | 1Ah   |                                  |          |           |           |           |           |          | WI       | REG13       |          |          |          |          |          |          |          | 0000          |

| WREG14       | 1Ch   |                                  |          |           |           |           |           |          | WI       | REG14       |          |          |          |          |          |          |          | 0000          |

| WREG15       | 1Eh   |                                  |          |           |           |           |           |          | WI       | REG15       |          |          |          |          |          |          |          | 0800          |

| SPLIM        | 20h   |                                  |          |           |           |           |           |          | SPLI     | √ Register  |          |          |          |          |          |          |          | xxxx          |

| PCL          | 2Eh   |                                  |          |           |           |           |           |          | PCL      | Register    |          |          |          |          |          |          |          | 0000          |

| PCH          | 30h   | _                                | _        | _         | _         | _         | _         | _        | _        | PCH7        | PCH6     | PCH5     | PCH4     | PCH3     | PCH2     | PCH1     | PCH0     | 0000          |

| TBLPAG       | 32h   | _                                | _        | _         | _         | _         | _         | _        | _        | TBLPAG7     | TBLPAG6  | TBLPAG5  | TBLPAG4  | TBLPAG3  | TBLPAG2  | TBLPAG1  | TBLPAG0  | 0000          |

| PSVPAG       | 34h   | _                                | _        | _         | _         | _         | _         | _        | _        | PSVPAG7     | PSVPAG6  | PSVPAG5  | PSVPAG4  | PSVPAG3  | PSVPAG2  | PSVPAG1  | PSVPAG0  | 0000          |

| RCOUNT       | 36h   |                                  |          |           |           |           |           |          | RCOU     | NT Register |          |          |          |          |          |          |          | xxxx          |

| SR           | 42h   | DC IPL2 IPL1 IPL0 RA N OV Z C 00 |          |           |           |           |           |          |          |             |          |          | 0000     |          |          |          |          |               |

| CORCON       | 44h   |                                  | _        | _         | _         | _         | _         | _        | _        | _           | _        | _        | _        | IPL3     | PSV      | _        | _        | 0000          |

| DISICNT      | 52h   | _                                | _        | DISICNT13 | DISICNT12 | DISICNT11 | DISICNT10 | DISICNT9 | DISICNT8 | DISICNT7    | DISICNT6 | DISICNT5 | DISICNT4 | DISICNT3 | DISICNT2 | DISICNT1 | DISICNT0 | xxxx          |

**Legend:** x = unknown, u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.

TABLE 4-12: SCCP5 REGISTER MAP

| File Name                | Addr. | Bit 15                               | Bit 14                                             | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8       | Bit 7         | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|--------------------------------------|----------------------------------------------------|---------|--------|---------|---------|-----------|-------------|---------------|-------------|---------|---------|---------|---------|--------|--------|---------------|

| CCP5CON1L <sup>(1)</sup> | 1D0h  | CCPON                                | _                                                  | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0     | TMRPS1        | TMRPS0      | T32     | CCSEL   | MOD3    | MOD2    | MOD1   | MOD0   | 0000          |

| CCP5CON1H <sup>(1)</sup> | 1D2h  | OPSSRC                               | RTRGEN                                             | _       | _      | IOPS3   | IOPS2   | IOPS1     | IOPS0       | TRIGEN        | ONESHOT     | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1  | SYNC0  | 0000          |

| CCP5CON2L <sup>(1)</sup> | 1D4h  | PWMRSEN                              | ASDGM                                              |         | SSDG   | ı       | _       | _         | _           | ASDG7         | ASDG6       | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1  | ASDG0  | 0000          |

| CCP5CON2H <sup>(1)</sup> | 1D6h  | OENSYNC                              | 1                                                  | -       | -      | _       | _       | _         | OCAEN       | ICGSM1        | ICGSM0      | _       | AUXOUT1 | AUXOUT0 | ICSEL2  | ICSEL1 | ICSEL0 | 0100          |

| CCP5CON3H <sup>(1)</sup> | 1DAh  | OETRIG                               | OSCNT2                                             | OSCNT1  | OSCNT0 | ı       | _       | _         | _           | _             | _           | POLACE  | _       | PSSACE1 | PSSACE0 | _      | _      | 0000          |

| CCP5STATL <sup>(1)</sup> | 1DCh  | _                                    | CCPTRIG TRSET TRCLR ASEVT SCEVT ICDIS ICOV ICBNE C |         |        |         |         |           |             |               |             |         |         | 0000    |         |        |        |               |

| CCP5TMRL <sup>(1)</sup>  | 1E0h  |                                      |                                                    |         |        |         |         | SCCP5     | Time Base   | Register Lo   | w Word      |         |         |         |         |        |        | 0000          |

| CCP5TMRH <sup>(1)</sup>  | 1E2h  |                                      |                                                    |         |        |         |         | SCCP5     | Time Base   | Register Hig  | gh Word     |         |         |         |         |        |        | 0000          |

| CCP5PRL <sup>(1)</sup>   | 1E4h  |                                      |                                                    |         |        |         |         | SCCP5 Tir | ne Base Pe  | riod Registe  | r Low Word  |         |         |         |         |        |        | FFFF          |

| CCP5PRH <sup>(1)</sup>   | 1E6h  |                                      |                                                    |         |        |         |         | SCCP5 Tin | ne Base Per | riod Register | r High Word |         |         |         |         |        |        | FFFF          |

| CCP5RAL <sup>(1)</sup>   | 1E8h  |                                      |                                                    |         |        |         |         | Out       | put Compar  | e 5 Data Wo   | ord A       |         |         |         |         |        |        | 0000          |

| CCP5RBL <sup>(1)</sup>   | 1ECh  |                                      | Output Compare 5 Data Word B                       |         |        |         |         |           |             |               |             |         |         | 0000    |         |        |        |               |

| CCP5BUFL <sup>(1)</sup>  | 1F0h  | Input Capture 5 Data Buffer Low Word |                                                    |         |        |         |         |           |             |               |             |         | 0000    |         |         |        |        |               |

| CCP5BUFH <sup>(1)</sup>  | 1F2h  |                                      |                                                    |         | •      | •       |         | Input C   | apture 5 Da | ta Buffer Hig | gh Word     |         |         | •       | •       |        |        | 0000          |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### 7.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 7-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. For more information, see **Section 9.0 "Oscillator Configuration"**.

TABLE 7-2: OSCILLATOR SELECTION vs.

TYPE OF RESET (CLOCK

SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | FNOSC<2:0> Configuration bits |

| BOR        | (FOSCSEL<2:0>)                |

| MCLR       | COSC<2:0> Control bits        |

| WDTO       | (OSCCON<14:12>)               |

| SWR        |                               |

#### 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

TABLE 7-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

| Reset Type         | Clock Source | SYSRST Delay | System Clock<br>Delay | Notes      |

|--------------------|--------------|--------------|-----------------------|------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT | _                     | 1, 2       |

|                    | FRC, FRCDIV  | TPOR + TPWRT | TFRC                  | 1, 2, 3    |

|                    | LPRC         | TPOR + TPWRT | TLPRC                 | 1, 2, 3    |

|                    | ECPLL        | TPOR + TPWRT | TLOCK                 | 1, 2, 4    |

|                    | FRCPLL       | TPOR + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4 |

|                    | XT, HS, SOSC | TPOR+ TPWRT  | Tost                  | 1, 2, 5    |

|                    | XTPLL, HSPLL | TPOR + TPWRT | Tost + Tlock          | 1, 2, 4, 5 |

| BOR                | EC           | TPWRT        | _                     | 2          |

|                    | FRC, FRCDIV  | TPWRT        | TFRC                  | 2, 3       |

|                    | LPRC         | TPWRT        | TLPRC                 | 2, 3       |

|                    | ECPLL        | TPWRT        | TLOCK                 | 2, 4       |

|                    | FRCPLL       | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

|                    | XT, HS, SOSC | TPWRT        | Tost                  | 2, 5       |

|                    | XTPLL, HSPLL | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

| All Others         | Any Clock    | _            | _                     | None       |

**Note 1:** TPOR = Power-on Reset delay.

- 2: TPWRT = 64 ms nominal if the Power-up Timer is enabled; otherwise, it is zero.

- 3: TFRC and TLPRC = RC Oscillator start-up times.

- 4: TLOCK = PLL Lock time.

- **5:** Tost = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

- **6:** If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 27.0 "Electrical Characteristics".

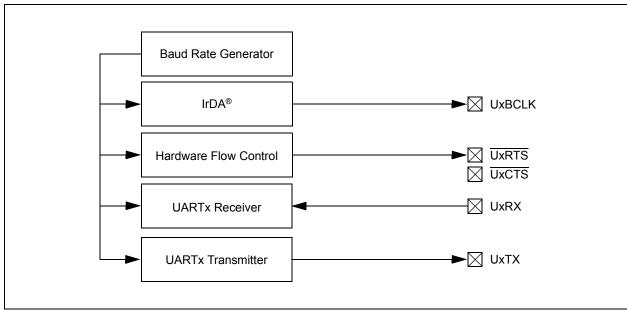

# 15.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Universal Asynchronous Receiver Transmitter, refer to the "PIC24F Family Reference Manual", "UART" (DS39708).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins, and also includes an IrDA® encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA® Encoder and Decoder Logic

- · 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 15-1. The UARTx module consists of these important hardware elements:

- · Baud Rate Generator

- · Asynchronous Transmitter

- Asynchronous Receiver

Note:

Throughout this section, references to register and bit names that may be associated with a specific USART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the USART Status register for either USART1 or USART2.

FIGURE 15-1: UARTX MODULE SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 16-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

| R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0    | R/W-0    |

|--------|-------|--------|--------|--------|--------|----------|----------|

| ALRMEN | CHIME | AMASK3 | AMASK2 | AMASK1 | AMASK0 | ALRMPTR1 | ALRMPTR0 |

| bit 15 |       |        |        |        |        |          | bit 8    |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **ALRMEN:** Alarm Enable bit

1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 00h and

CHIME = 0)

0 = Alarm is disabled

bit 14 CHIME: Chime Enable bit

1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 00h to FFh

0 = Chime is disabled; ARPT<7:0> bits stop once they reach 00h

bit 13-10 AMASK<3:0>: Alarm Mask Configuration bits

0000 = Every half second

0001 = Every second

0010 = Every 10 seconds

0011 = Every minute

0100 = Every 10 minutes

0101 = Every hour

0110 = Once a day

0111 = Once a week

1000 = Once a month

1001 = Once a year (except when configured for February 29<sup>th</sup>, once every 4 years)

101x = Reserved – do not use

11xx = Reserved – do not use

bit 9-8 **ALRMPTR<1:0>:** Alarm Value Register Window Pointer bits

Points to the corresponding Alarm Value registers when reading the ALRMVALH and ALRMVALL registers. The ALRMPTR<1:0> value decrements on every read or write of ALRMVALH until it reaches '00'.

THE ALIXWIT TIX 1.02 value decrements on every read of write of ALIXWIA

ALRMVAL<15:8>:

00 = ALRMMIN

01 = ALRMWD

10 = ALRMMNTH

11 = Unimplemented

ALRMVAL<7:0>:

00 = ALRMSEC

01 = ALRMHR

10 = ALRMDAY

11 = Unimplemented

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits

11111111 = Alarm will repeat 255 more times

.

00000000 = Alarm will not repeat

The counter decrements on any alarm event; it is prevented from rolling over from 00h to FFh unless CHIME = 1.

#### 16.2.6 ALRMVAL REGISTER MAPPINGS

#### REGISTER 16-8: ALMTHDY: ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | _   | _   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit

Contains a value of '0' or '1'.

bit 11-8 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits

Contains a value from 0 to 9.

bit 7-6 Unimplemented: Read as '0'

bit 5-4 DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits

Contains a value from 0 to 3.

bit 3-0 DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 16-9: ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER(1)

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| _      | _   | _   | _   | _   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 Unimplemented: Read as '0'

bit 10-8 WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits

Contains a value from 0 to 6.

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits

Contains a value from 0 to 2.

bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

**FIGURE 17-3: CLCx INPUT SOURCE SELECTION DIAGRAM Data Selection** 000 CLCIN[0] CLCIN[1] Data Gate 1 CLCIN[2] Data 1 Non-Inverted G1D1T CLCIN[3] CLCIN[4] Data 1 Inverted CLCIN[5] G1D1N CLCIN[6] CLCIN[7] -G1D2T -DS1x (CLCxSEL<2:0>) G1D2N Gate 1 CLCIN[8] 000 CLCIN[9] G1D3T G1POL | CLCIN[10] -(CLCxCONH<0>) Data 2 Non-Inverted CLCIN[11] G1D3N CLCIN[12] Data 2 Inverted CLCIN[13] -G1D4T CLCIN[14] -CLCIN[15] -DS2x (CLCxSEL<6:4>) G1D4N CLCIN[16] -000 Data Gate 2 CLCIN[17] CLCIN[18] -Gate 2 Data 3 Non-Inverted CLCIN[19] (Same as Data Gate 1) | CLCIN[20] Data 3 Inverted CLCIN[21] Data Gate 3 CLCIN[22] CLCIN[23] --Gate 3 DS3x (CLCxSEL<10:8>) (Same as Data Gate 1) | CLCIN[24] 000 Data Gate 4 CLCIN[25] -Gate 4 CLCIN[26] (Same as Data Gate 1) Data 4 Non-Inverted CLCIN[27] -CLCIN[28] Data 4 CLCIN[29] Inverted CLCIN[30] | CLCIN[31] -111 DS4x (CLCxSEL<14:12>) | All controls are undefined at power-up. Note:

#### REGISTER 17-3: CLCxSEL: CLCx INPUT MUX SELECT REGISTER (CONTINUED)

bit 6-4 DS2<2:0>: Data Selection MUX 2 Signal Selection bits

111 = MCCP2 Compare Event Flag (CCP2IF)

110 = MCCP1 Compare Event Flag (CCP1IF)

101 = Digital logic low

100 = A/D end of conversion event

For CLC1:

011 **= UART1 TX**

010 = Comparator 1 output

001 = CLC2 output

000 = CLCINB I/O pin

For CLC2:

011 = UART2 TX

010 = Comparator 1 output

001 = CLC1 output

000 = CLCINB I/O pin

bit 3 **Unimplemented:** Read as '0'

bit 2-0 DS1<2:0>: Data Selection MUX 1 Signal Selection bits

111 = SCCP5 Compare Event Flag (CCP5IF)

110 = SCCP4 Compare Event Flag (CCP4IF)

101 = Digital logic low

100 = 8 MHz FRC clock source

011 = LPRC clock source

010 = SOSC clock source

001 = System clock (TcY)

000 = CLCINA I/O pin

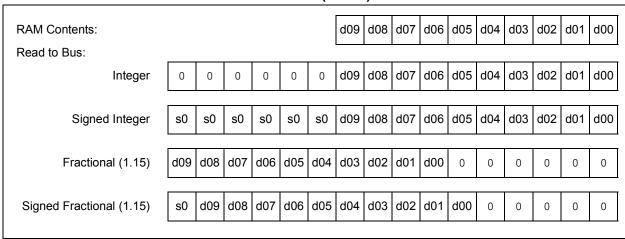

# 19.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR) Conversion

- · Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (internal and external)

- · Multiple Internal Reference Input Channels

- · External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H) Amplifier

- Automated Threshold Scan and Compare Operation to Pre-Evaluate Conversion Results

- · Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- · Four Options for Results Alignment

- · Configurable Interrupt Generation

- · Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU, and a configurable results buffer. There is a legacy 10-bit mode on this A/D to allow the option to run with lower resolution in order to obtain higher throughput. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 19-1.

TABLE 19-2: NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES: 12-BIT FRACTIONAL FORMATS

| VIN/VREF   | 12-Bit<br>Output Code | 16-Bit Fractional Format/<br>Equivalent Decimal Value |       | 16-Bit Signed Fractional Format/<br>Equivalent Decimal Value |        |  |  |  |

|------------|-----------------------|-------------------------------------------------------|-------|--------------------------------------------------------------|--------|--|--|--|

| +4095/4096 | 0 1111 1111 1111      | 1111 1111 1111 0000                                   | 0.999 | 0111 1111 1111 1000                                          | 0.999  |  |  |  |

| +4094/4096 | 0 1111 1111 1110      | 1111 1111 1110 0000                                   | 0.998 | 0111 1111 1110 1000                                          | 0.998  |  |  |  |

|            |                       | • • •                                                 |       |                                                              |        |  |  |  |

| +1/4096    | 0 0000 0000 0001      | 0000 0000 0001 0000                                   | 0.001 | 0000 0000 0000 1000                                          | 0.001  |  |  |  |

| 0/4096     | 0 0000 0000 0000      | 0000 0000 0000 0000                                   | 0.000 | 0000 0000 0000 0000                                          | 0.000  |  |  |  |

| -1/4096    | 1 0111 1111 1111      | 0000 0000 0000 0000                                   | 0.000 | 1111 1111 1111 1000                                          | -0.001 |  |  |  |

|            | •••                   |                                                       |       |                                                              |        |  |  |  |

| -4095/4096 | 1 0000 0000 0001      | 0000 0000 0000 0000                                   | 0.000 | 1000 0000 0000 1000                                          | -0.999 |  |  |  |

| -4096/4096 | 1 0000 0000 0000      | 0000 0000 0000 0000                                   | 0.000 | 1000 0000 0000 0000                                          | -1.000 |  |  |  |

FIGURE 19-5: A/D OUTPUT DATA FORMATS (10-BIT)

TABLE 19-3: NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES: 10-BIT INTEGER FORMATS

| Vin/Vref   | 10-Bit Differential<br>Output Code<br>(11-bit result) | 16-Bit Integer Format/<br>Equivalent Decimal Value |      | 16-Bit Signed Integer Format/<br>Equivalent Decimal Value |       |  |  |

|------------|-------------------------------------------------------|----------------------------------------------------|------|-----------------------------------------------------------|-------|--|--|

| +1023/1024 | 011 1111 1111                                         | 0000 0011 1111 1111                                | 1023 | 0000 0001 1111 1111                                       | 1023  |  |  |

| +1022/1024 | 011 1111 1110                                         | 0000 0011 1111 1110                                | 1022 | 0000 0001 1111 1110                                       | 1022  |  |  |

|            | •••                                                   |                                                    |      |                                                           |       |  |  |

| +1/1024    | 000 0000 0001                                         | 0000 0000 0000 0001                                | 1    | 0000 0000 0000 0001                                       | 1     |  |  |

| 0/1024     | 000 0000 0000                                         | 0000 0000 0000 0000                                | 0    | 0000 0000 0000 0000                                       | 0     |  |  |

| -1/1024    | 101 1111 1111                                         | 0000 0000 0000 0000                                | 0    | 1111 1111 1111 1111                                       | -1    |  |  |

|            | •••                                                   |                                                    |      |                                                           |       |  |  |

| -1023/1024 | 100 0000 0001                                         | 0000 0000 0000 0000                                | 0    | 1111 1110 0000 0001                                       | -1023 |  |  |

| -1024/1024 | 100 0000 0000                                         | 0000 0000 0000 0000                                | 0    | 1111 1110 0000 0000                                       | -1024 |  |  |

#### REGISTER 21-1: AMPxCON: OP AMP x CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0   | R/W-0  | U-0 | U-0 | U-0 | U-0   |

|--------|-----|---------|--------|-----|-----|-----|-------|

| AMPEN  | _   | AMPSIDL | AMPSLP | _   | _   | _   | _     |

| bit 15 |     |         |        |     |     |     | bit 8 |

| R/W-0  | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| SPDSEL | _   | NINSEL2 | NINSEL1 | NINSEL0 | PINSEL2 | PINSEL1 | PINSEL0 |

| bit 7  |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 AMPEN: Op Amp x Control Module Enable bit

1 = Module is enabled0 = Module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 AMPSIDL: Op Amp x Peripheral Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 AMPSLP: Op Amp x Peripheral Enabled in Sleep Mode bit

1 = Continues module operation when device enters Sleep mode

0 = Discontinues module operation in Sleep mode

bit 11-8 Unimplemented: Read as '0'

bit 7 SPDSEL: Op Amp x Power/Speed Select bit

1 = Higher power and bandwidth (faster response time)

0 = Lower power and bandwidth (slower response time)

bit 6 **Unimplemented:** Read as '0'

bit 5-3 NINSEL<2:0>: Negative Op Amp Input Select bits

111 = Reserved; do not use

110 = Reserved; do not use

101 = Op amp negative input is connected to the op amp output (voltage follower)

100 = Reserved; do not use

011 = Reserved; do not use

010 = Op amp negative input is connected to the OAxIND pin

001 = Op amp negative input is connected to the OAxINB pin

000 = Op amp negative input is connected to AVss

bit 2-0 PINSEL<2:0>: Positive Op Amp Input Select bits

111 = Op amp positive input is connected to the output of the A/D input multiplexer

110 = Reserved; do not use

101 = Op amp positive input is connected to the DAC1 output for OA1 (DAC2 output for OA2)

100 = Reserved; do not use

011 = Reserved; do not use

010 = Op amp positive input is connected to the OAxINC pin

001 = Op amp positive input is connected to the OAxINA pin

000 = Op amp positive input is connected to AVss

Note 1: This register is available only on PIC24F(V)16KM2XX devices.

NOTES:

#### 26.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 26.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 26.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 26.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

#### 26.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

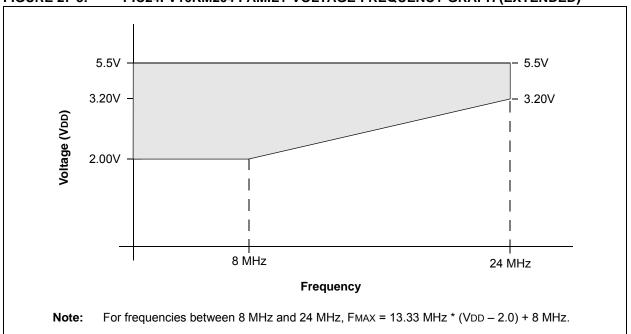

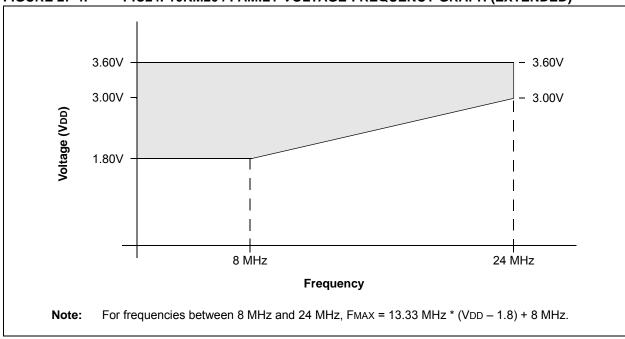

FIGURE 27-3: PIC24FV16KM204 FAMILY VOLTAGE-FREQUENCY GRAPH (EXTENDED)

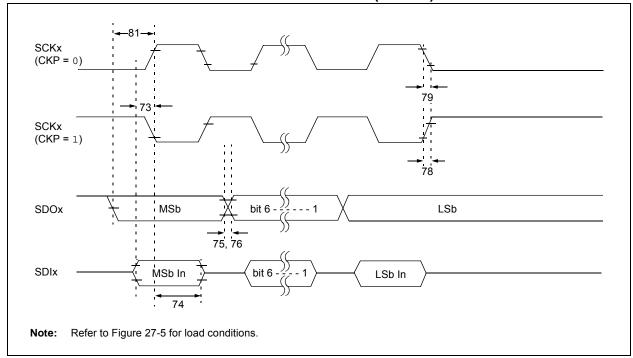

FIGURE 27-12: EXAMPLE SPI MASTER MODE TIMING (CKE = 1)

TABLE 27-30: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                | Characteristic                             | Min | Max | Units | Conditions |

|---------------|-----------------------|--------------------------------------------|-----|-----|-------|------------|

| 73            | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge | 35  | _   | ns    |            |

| 74            | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 40  | _   | ns    |            |

| 75            | TDOR                  | SDOx Data Output Rise Time                 | _   | 25  | ns    |            |

| 76            | TDOF                  | SDOx Data Output Fall Time                 | _   | 25  | ns    |            |

| 78            | TscR                  | SCKx Output Rise Time (Master mode)        | _   | 25  | ns    |            |

| 79            | TscF                  | SCKx Output Fall Time (Master mode)        | _   | 25  | ns    |            |

| 81            | TDOV2SCH,<br>TDOV2SCL | SDOx Data Output Setup to SCKx Edge        | Tcy | _   | ns    |            |

|               | FSCK                  | SCKx Frequency                             | _   | 10  | MHz   |            |

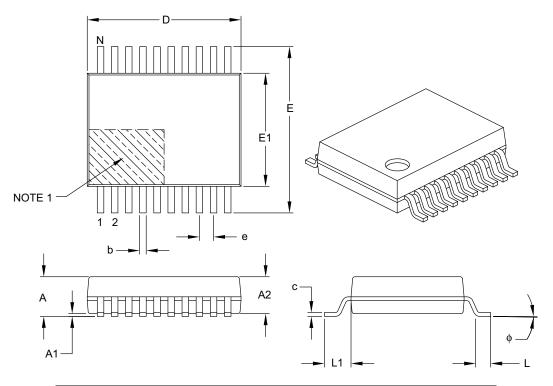

#### 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**te:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units      |          |          | MILLIMETERS |  |  |  |

|--------------------------|------------|----------|----------|-------------|--|--|--|

| Dimens                   | ion Limits | MIN      | NOM      | MAX         |  |  |  |

| Number of Pins           | N          | 20       |          |             |  |  |  |

| Pitch                    | е          |          | 0.65 BSC |             |  |  |  |

| Overall Height           | Α          | _        | _        | 2.00        |  |  |  |

| Molded Package Thickness | A2         | 1.65     | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1         | 0.05     | _        | _           |  |  |  |

| Overall Width            | Е          | 7.40     | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1         | 5.00     | 5.30     | 5.60        |  |  |  |

| Overall Length           | D          | 6.90     | 7.20     | 7.50        |  |  |  |

| Foot Length              | L          | 0.55     | 0.75     | 0.95        |  |  |  |

| Footprint                | L1         | 1.25 REF |          |             |  |  |  |

| Lead Thickness           | С          | 0.09     | _        | 0.25        |  |  |  |

| Foot Angle               | ф          | 0°       | 4°       | 8°          |  |  |  |

| Lead Width               | b          | 0.22     | _        | 0.38        |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

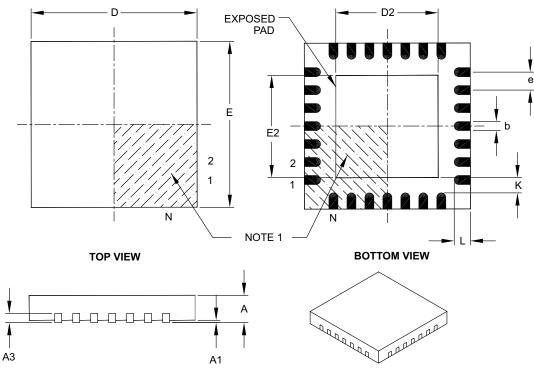

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |                | MILLIMETERS | 3    |

|------------------------|------------------|----------------|-------------|------|

|                        | Dimension Limits | MIN            | NOM         | MAX  |

| Number of Pins         | N                |                | 28          |      |

| Pitch                  | е                |                | 0.65 BSC    |      |

| Overall Height         | А                | 0.80           | 0.90        | 1.00 |

| Standoff               | A1               | 0.00           | 0.02        | 0.05 |

| Contact Thickness      | A3               | 0.20 REF       |             |      |

| Overall Width          | E                | 6.00 BSC       |             |      |

| Exposed Pad Width      | E2               | 3.65 3.70 4.20 |             |      |

| Overall Length         | D                |                | 6.00 BSC    |      |

| Exposed Pad Length     | D2               | 3.65           | 3.70        | 4.20 |

| Contact Width          | b                | 0.23           | 0.30        | 0.35 |

| Contact Length         | L                | 0.50 0.55 0.70 |             |      |

| Contact-to-Exposed Pad | K                | 0.20 – –       |             |      |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

NOTES:

NOTES: