#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 22x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

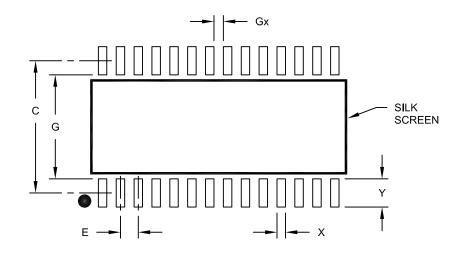

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km104t-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Pin Diagrams**

| 20-Pin PDIP/SSOP/SOIC | RA5       1       20       VDD         RA0       2       19       VSs         RA1       3       18       RB15         RB0       4       17       RB14         RB1       5       RB12         RA2       6       9       16         RA3       8       00       VDC         RA4       10       11       RB7 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dia | Pin Features                                  |                                            |  |  |  |  |  |

|-----|-----------------------------------------------|--------------------------------------------|--|--|--|--|--|

| Pin | PIC24F08KM101                                 | PIC24FVKM08KM101                           |  |  |  |  |  |

| 1   | MCLR/Vpp/RA5                                  |                                            |  |  |  |  |  |

| 2   | PGEC2/CVREF+/VREF+/AN0/CN2/RA0                |                                            |  |  |  |  |  |

| 3   | PGED2/CVREF-/VREF-/AN1/CN3/RA1                |                                            |  |  |  |  |  |

| 4   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0      |                                            |  |  |  |  |  |

| 5   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                |                                            |  |  |  |  |  |

| 6   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                 |                                            |  |  |  |  |  |

| 7   | OSCI/CLKI/AN13/C1INB/CN30/RA2                 |                                            |  |  |  |  |  |

| 8   | OSCO/CLKO/AN14/C1INA/CN29/RA3                 |                                            |  |  |  |  |  |

| 9   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4               |                                            |  |  |  |  |  |

| 10  | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/    | RA4                                        |  |  |  |  |  |

| 11  | AN19/U1TX/CTED1/INT0/CN23/RB7                 | AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7     |  |  |  |  |  |

| 12  | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8          |                                            |  |  |  |  |  |

| 13  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4   | /CN21/RB9                                  |  |  |  |  |  |

| 14  | IC1/OC1A/INT2/CN8/RA6                         | VCAP OR VDDCORE                            |  |  |  |  |  |

| 15  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12         | AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |  |

| 16  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13           |                                            |  |  |  |  |  |

| 17  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RE | 814                                        |  |  |  |  |  |

| 18  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15            |                                            |  |  |  |  |  |

| 19  | Vss/AVss                                      |                                            |  |  |  |  |  |

| 20  | Vdd/AVdd                                      |                                            |  |  |  |  |  |

### **Pin Diagrams (Continued)**

|          | 28-Pin QFN <sup>(1)</sup>                                                            | 22<br>21 RB13<br>20 RB12                         |  |  |  |  |

|----------|--------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|--|

|          | RB3 4<br>Vss 5<br>RA2 6<br>RA3 7<br><u>8 9 10 11 12 <b>13</b> 1</u>                  | 18 RB10<br>17 RA6 or VDDcore<br>16 RA7<br>15 RB9 |  |  |  |  |

|          | R 85<br>R 85<br>R 85<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82 | 5<br>0<br>2<br>2                                 |  |  |  |  |

| Pin      | Pin Features                                                                         | Pin Features                                     |  |  |  |  |

|          | PIC24FXXKMX02                                                                        | PIC24FVXXKMX02                                   |  |  |  |  |

| 1        | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/I                                              | RB0                                              |  |  |  |  |

| 2        | PGEC1/ / /AN3/C1INC/ / /CTED12/CN                                                    | I5/RB1                                           |  |  |  |  |

| 3        | / /AN4/C1INB/ / /U1RX/TCKIB/CTED13/CN6/RB2                                           |                                                  |  |  |  |  |

| 4        | /AN5/C1INA/ / /CN7/RB3                                                               |                                                  |  |  |  |  |

| 5        | Vss                                                                                  |                                                  |  |  |  |  |

| 6        | OSCI/CLKI/AN13/CN30/RA2                                                              |                                                  |  |  |  |  |

| 7        | OSCO/CLKO/AN14/CN29/RA3                                                              |                                                  |  |  |  |  |

| 8        | SOSCI/AN15/ / /CN1/RB4                                                               |                                                  |  |  |  |  |

| 9        | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                   |                                                  |  |  |  |  |

| 10       |                                                                                      |                                                  |  |  |  |  |

| 11       | PGED3/AN17/ASDA1/ / /OC1E/CLCINA/CN27/RB5                                            |                                                  |  |  |  |  |

| 12       | PGEC3/AN18/ASCL1/ / /OC1F/CLCINB/CN24/RB6<br>AN19/U1TX/INT0/CN23/RB7                 | AN19/U1TX/ /OC1A/INT0/CN23/RB7                   |  |  |  |  |

| 13<br>14 | AN19/0112/IN10/CN23/RB7<br>AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                | AN 19/011X/ /OCTA/IN10/CN23/RB7                  |  |  |  |  |

| 14       | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN                                     | 121/PB0                                          |  |  |  |  |

| 16       | /IC1/ / /CTED3/CN9/RA7                                                               | vz //KD9                                         |  |  |  |  |

| 17       | /OC1A/CTED1/INT2/CN8/RA6                                                             | VDDCORE/VCAP                                     |  |  |  |  |

| 18       | PGED2/SDI1/ /OC1C/CTED11/CN16/RB10                                                   |                                                  |  |  |  |  |

| 19       | PGEC2/SCK1/OC2A/CTED9/CN15/RB11                                                      | <u></u>                                          |  |  |  |  |

| 20       | /AN12/HLVDIN/ / / /CTED2/CN14/RB12                                                   | /AN12/HLVDIN/SS2/ / /CTED2/INT2/CN14/RB12        |  |  |  |  |

| 21       | / /AN11/SDO1/OCFB/OC3B/OC1D/CTPLS/CN13                                               | 3/RB13                                           |  |  |  |  |

| 22       | /CVREF/ / /AN10/ / /C1OUT                                                            | OCFA/CTED5/INT1/CN12/RB14                        |  |  |  |  |

| 23       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN                                                     | I11/RB15                                         |  |  |  |  |

| 24       | Vss                                                                                  |                                                  |  |  |  |  |

| 25       | Vdd                                                                                  |                                                  |  |  |  |  |

| 26       | MCLR/Vpp/RA5                                                                         |                                                  |  |  |  |  |

|          | CVREF+/VREF+/ /AN0/ /CN2/RA0                                                         | CVREF+/VREF+/ /AN0/ /CTED1/CN2/RA0               |  |  |  |  |

| 27       |                                                                                      |                                                  |  |  |  |  |

Legend:Values inindicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.Note 1:Exposed pad on underside of device is connected to Vss.

### 2.2 Power Supply Pins

### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g.,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ ).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

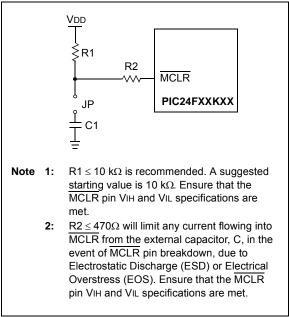

### 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

**IFS1: INTERRUPT FLAG STATUS REGISTER 1**

**REGISTER 8-6:**

| R/W-0, HS     | R/W-0, HS       | R/W-0, HS                       | R/W-0, HS       | R/W-0, HS         | U-0              | U-0             | U-0       |

|---------------|-----------------|---------------------------------|-----------------|-------------------|------------------|-----------------|-----------|

| U2TXIF        | U2RXIF          | INT2IF                          | CCT4IF          | CCT3IF            |                  | —               | —         |

| bit 15        |                 |                                 |                 |                   |                  |                 | bit 8     |

|               |                 |                                 |                 |                   |                  |                 |           |

| U-0           | R/W-0, HS       | U-0                             | R/W-0, HS       | R/W-0, HS         | R/W-0, HS        | R/W-0, HS       | R/W-0, HS |

| —             | CCP5IF          | —                               | INT1IF          | CNIF              | CMIF             | BCL1IF          | SSP1IF    |

| bit 7         |                 |                                 |                 |                   |                  |                 | bit 0     |

|               |                 |                                 |                 |                   |                  |                 |           |

| Legend:       |                 |                                 | re Settable bit |                   |                  |                 |           |

| R = Readable  |                 | W = Writable                    |                 | -                 | nented bit, read | d as '0'        |           |

| -n = Value at | POR             | '1' = Bit is set                |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown      |

|               |                 |                                 |                 |                   |                  |                 |           |

| bit 15        |                 | T2 Transmitter                  |                 | Status bit        |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

| bit 14        | -               | RT2 Receiver Ir                 |                 | atus hit          |                  |                 |           |

|               |                 | request has oc                  |                 |                   |                  |                 |           |

|               |                 | equest has not                  |                 |                   |                  |                 |           |

| bit 13        | INT2IF: Exter   | nal Interrupt 2                 | Flag Status bit |                   |                  |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

|               | •               | equest has not                  |                 |                   |                  |                 |           |

| bit 12        |                 | -                               |                 | pt Flag Status b  | bit              |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

| bit 11        | -               | equest has not                  |                 | nt Elan Statua k  | -:+              |                 |           |

|               | -               | request has oc                  |                 | pt Flag Status b  | JIL              |                 |           |

|               |                 | request has not                 |                 |                   |                  |                 |           |

| bit 10-7      | -               | ted: Read as '                  |                 |                   |                  |                 |           |

| bit 6         | CCP5IF: Cap     | ture/Compare                    | 5 Event Interru | pt Flag Status I  | bit              |                 |           |

|               | 1 = Interrupt r | equest has oc                   | curred          |                   |                  |                 |           |

|               | 0 = Interrupt r | equest has no                   | occurred        |                   |                  |                 |           |

| bit 5         | •               | ted: Read as '                  |                 |                   |                  |                 |           |

| bit 4         |                 | nal Interrupt 1                 | •               |                   |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

| bit 3         |                 | •                               |                 | lag Status bit    |                  |                 |           |

| DIUS          | -               | hange Notifica<br>equest has oc | -               | lay Status bit    |                  |                 |           |

|               | •               | request has not                 |                 |                   |                  |                 |           |

| bit 2         | CMIF: Compa     | arator Interrupt                | Flag Status Bit | t                 |                  |                 |           |

|               | -               | equest has oc                   | -               |                   |                  |                 |           |

|               | -               | equest has no                   |                 |                   |                  |                 |           |

| bit 1         |                 |                                 |                 | upt Flag Status   | bit              |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

| <b>L</b> H 0  | -               | equest has not                  |                 |                   |                  |                 |           |

| bit 0         |                 | SP1 SPI/I <sup>2</sup> C Ev     | •               | lag Status bit    |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

|               | 5 monupti       |                                 |                 |                   |                  |                 |           |

| R/W-0, HS       | R/W-0, HS                                                                                  | R/W-0, HS                           | U-0              | U-0              | U-0              | U-0             | R/W-0, HS |  |  |

|-----------------|--------------------------------------------------------------------------------------------|-------------------------------------|------------------|------------------|------------------|-----------------|-----------|--|--|

| DAC2IF          | DAC1IF                                                                                     | CTMUIF                              | —                |                  | _                |                 | HLVDIF    |  |  |

| bit 15          |                                                                                            |                                     |                  |                  |                  |                 | bit 8     |  |  |

|                 |                                                                                            |                                     |                  |                  |                  |                 |           |  |  |

| U-0             | U-0                                                                                        | U-0                                 | U-0              | U-0              | R/W-0, HS        | R/W-0, HS       | U-0       |  |  |

| —               | —                                                                                          | —                                   | _                | —                | U2ERIF           | U1ERIF          | —         |  |  |

| bit 7           |                                                                                            |                                     |                  |                  |                  |                 | bit 0     |  |  |

|                 |                                                                                            |                                     |                  |                  |                  |                 |           |  |  |

| Legend:         |                                                                                            | HS = Hardwar                        | re Settable bit  | bit              |                  |                 |           |  |  |

| R = Readable    | e bit                                                                                      | W = Writable I                      | oit              | U = Unimpler     | nented bit, read | l as '0'        |           |  |  |

| -n = Value at I | POR                                                                                        | '1' = Bit is set                    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | iown      |  |  |

|                 |                                                                                            |                                     |                  |                  |                  |                 |           |  |  |

| bit 15          | •                                                                                          | tal-to-Analog C                     |                  | rrupt Flag Stat  | us bit           |                 |           |  |  |

|                 |                                                                                            | request has occ<br>request has not  |                  |                  |                  |                 |           |  |  |

| bit 14          |                                                                                            | •                                   |                  | reunt Flog Stat  | ua hit           |                 |           |  |  |

| DIL 14          | •                                                                                          | tal-to-Analog Co<br>request has occ |                  | mupt Flag Stat   |                  |                 |           |  |  |

|                 |                                                                                            | request has not                     |                  |                  |                  |                 |           |  |  |

| bit 13          |                                                                                            | MU Interrupt Fla                    |                  |                  |                  |                 |           |  |  |

|                 |                                                                                            | request has occ                     | •                |                  |                  |                 |           |  |  |

|                 | 0 = Interrupt r                                                                            | request has not                     | occurred         |                  |                  |                 |           |  |  |

| bit 12-9        | Unimplemen                                                                                 | ted: Read as 'o                     | )'               |                  |                  |                 |           |  |  |

| bit 8           | HLVDIF: High                                                                               | n/Low-Voltage D                     | Detect Interrupt | t Flag Status bi | t                |                 |           |  |  |

|                 |                                                                                            | request has occ                     |                  |                  |                  |                 |           |  |  |

|                 |                                                                                            | request has not                     |                  |                  |                  |                 |           |  |  |

| bit 7-3         | Unimplemented: Read as '0'                                                                 |                                     |                  |                  |                  |                 |           |  |  |

| bit 2           | <b>U2ERIF:</b> UART2 Error Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                     |                  |                  |                  |                 |           |  |  |

|                 |                                                                                            | request has occ<br>request has not  |                  |                  |                  |                 |           |  |  |

| bit 1           | •                                                                                          | RT1 Error Interro                   |                  | s bit            |                  |                 |           |  |  |

|                 |                                                                                            | request has occ                     |                  |                  |                  |                 |           |  |  |

|                 |                                                                                            | request has not                     |                  |                  |                  |                 |           |  |  |

| bit 0           | Unimplemen                                                                                 | ted: Read as 'o                     | )'               |                  |                  |                 |           |  |  |

|                 |                                                                                            |                                     |                  |                  |                  |                 |           |  |  |

### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

### REGISTER 8-31: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

| _       | —   | —   | —   | —   | —       | —       | —       |

| bit 15  | ·   | •   |     |     | •       |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _       | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Logondi |     |     |     |     |         |         |         |

| Legend: |  |

|---------|--|

|---------|--|

bit 2-0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC Oscillator by a fixed amount.

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                    | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit          |                                    |                    |  |  |

|----------------------------|------------------------------------------------|------------------------------------|--------------------|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit SO = Settable Only bit |                                    |                    |  |  |

| R = Readable bit           | W = Writable bit                               | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR          | '1' = Bit is set                               | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| Note 1:   | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:        | This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                |

**3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

| R/W-0        | U-0                             | R/W-0                       | U-0                                | U-0                     | U-0              | R/W-0                | R/W-0                |

|--------------|---------------------------------|-----------------------------|------------------------------------|-------------------------|------------------|----------------------|----------------------|

| TON          |                                 | TSIDL                       | —                                  | _                       | —                | TECS1 <sup>(1)</sup> | TECS0 <sup>(1)</sup> |

| bit 15       |                                 | •                           | -                                  |                         |                  |                      | bit                  |

|              |                                 |                             |                                    |                         |                  |                      |                      |

| U-0          | R/W-0                           | R/W-0                       | R/W-0                              | U-0                     | R/W-0            | R/W-0                | U-0                  |

| —            | TGATE                           | TCKPS1                      | TCKPS0                             | —                       | TSYNC            | TCS                  | —                    |

| bit 7        |                                 |                             |                                    |                         |                  |                      | bit                  |

| Legend:      |                                 |                             |                                    |                         |                  |                      |                      |

| R = Readab   | ole bit                         | W = Writable                | bit                                | U = Unimpler            | mented bit, read | d as '0'             |                      |

| -n = Value a | It POR                          | '1' = Bit is set            |                                    | '0' = Bit is cle        | ared             | x = Bit is unkr      | iown                 |

|              |                                 |                             |                                    |                         |                  |                      |                      |

| bit 15       | TON: Timer1                     | On bit                      |                                    |                         |                  |                      |                      |

|              | 1 = Starts 16-<br>0 = Stops 16- |                             |                                    |                         |                  |                      |                      |

| bit 14       | Unimplemen                      | ted: Read as '              | 0'                                 |                         |                  |                      |                      |

| bit 13       | TSIDL: Timer                    | 1 Stop in Idle I            | Node bit                           |                         |                  |                      |                      |

|              |                                 |                             | eration when o<br>ation in Idle mo | device enters lo<br>ode | lle mode         |                      |                      |

| bit 12-10    | Unimplemen                      | ted: Read as '              | 0'                                 |                         |                  |                      |                      |

| bit 9-8      |                                 |                             | ed Clock Seled                     | ct bits <sup>(1)</sup>  |                  |                      |                      |

|              | 11 = Reserve                    | •                           | as the sleek s                     | 0.1700                  |                  |                      |                      |

|              |                                 |                             | as the clock s<br>al Clock (EC)    |                         |                  |                      |                      |

|              |                                 |                             |                                    | r (SOSC) as th          | e clock source   |                      |                      |

| bit 7        | Unimplemen                      | ted: Read as '              | 0'                                 |                         |                  |                      |                      |

| bit 6        |                                 |                             | Accumulation                       | Enable bit              |                  |                      |                      |

|              | When TCS =                      |                             |                                    |                         |                  |                      |                      |

|              | When TCS = $\frac{1}{2}$        |                             |                                    |                         |                  |                      |                      |

|              |                                 | <u>o.</u><br>ne accumulatio | n is enabled                       |                         |                  |                      |                      |

|              | 0 = Gated tim                   | ne accumulatio              | n is disabled                      |                         |                  |                      |                      |

| bit 5-4      | TCKPS<1:0>                      | : Timer1 Input              | Clock Prescale                     | e Select bits           |                  |                      |                      |

|              | 11 = 1:256                      |                             |                                    |                         |                  |                      |                      |

|              | 10 = 1:64<br>01 = 1:8           |                             |                                    |                         |                  |                      |                      |

|              | 00 = 1:1                        |                             |                                    |                         |                  |                      |                      |

| bit 3        | Unimplemen                      | ted: Read as '              | 0'                                 |                         |                  |                      |                      |

| bit 2        | TSYNC: Time                     | er1 External Cl             | ock Input Sync                     | hronization Se          | lect bit         |                      |                      |

|              | <u>When TCS =</u>               | <u>1:</u><br>nizes External | Clock input                        |                         |                  |                      |                      |

|              |                                 |                             | External Clock                     | input                   |                  |                      |                      |

|              | When TCS =                      | -                           |                                    |                         |                  |                      |                      |

|              | This bit is igno                | ored.                       |                                    |                         |                  |                      |                      |

| bit 1        |                                 | Clock Source                |                                    |                         |                  |                      |                      |

|              |                                 |                             | selected by TE                     | CS<1:0>                 |                  |                      |                      |

|              | 0 = Internal c                  |                             |                                    |                         |                  |                      |                      |

| bit 0        | Unimplemen                      | tod. Dood oo .              | Ω'                                 |                         |                  |                      |                      |

### 13.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive refer-      |

|       | ence source. For more information on the   |

|       | MCCP/SCCP modules, refer to the            |

|       | "PIC24F Family Reference Manual".          |

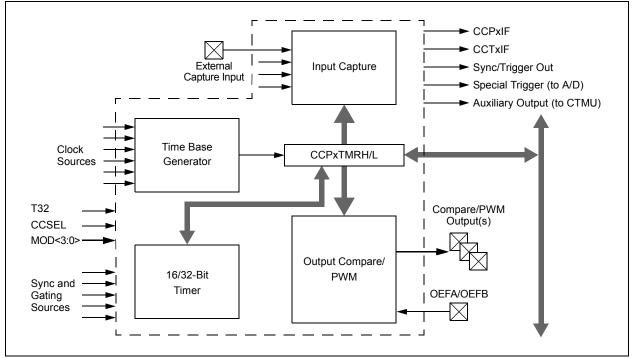

PIC24FV16KM204 family devices include several Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals of earlier PIC24F devices. The module can operate in one of three major modes:

- General Purpose Timer

- Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single output modules (SCCPs) provide only one PWM output. Multiple output modules (MCCPs) can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical.

The SCCP and MCCP modules can be operated only in one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode. A conceptual block diagram for the module is shown in Figure 13-1. All three modes share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of seven control and status registers:

- CCPxCON1L (Register 13-1)

- CCPxCON1H (Register 13-2)

- CCPxCON2L (Register 13-3)

- CCPxCON2H (Register 13-4)

- CCPxCON3L (Register 13-5)

- CCPxCON3H (Register 13-6)

- CCPxSTATL (Register 13-7)

Each module also includes eight buffer/counter registers that serve as Timer Value registers or data holding buffers:

- CCPxTMRH/CCPxTMRL (Timer High/Low Counters)

- CCPxPRH/CCPxPRL (Timer Period High/Low)

- CCPxRA (Primary Output Compare Data Buffer)

- CCPxRB (Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (Input Capture High/Low Buffers)

### FIGURE 13-1: MCCPx/SCCPx CONCEPTUAL BLOCK DIAGRAM

| R/W-0         | U-0                                                              | R/W-0                                  | r-0            | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |

|---------------|------------------------------------------------------------------|----------------------------------------|----------------|--------------------------------------|------------------------|------------------------|------------------------|

| CCPON         |                                                                  | CCPSIDL                                | r              | TMRSYNC                              | CLKSEL2 <sup>(1)</sup> | CLKSEL1 <sup>(1)</sup> | CLKSEL0 <sup>(1)</sup> |

| bit 15        |                                                                  |                                        |                |                                      | •                      | •                      | bit 8                  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |

| R/W-0         | R/W-0                                                            | R/W-0                                  | R/W-0          | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |

| TMRPS1        | TMRPS0                                                           | T32                                    | CCSEL          | MOD3                                 | MOD2                   | MOD1                   | MOD0                   |

| bit 7         |                                                                  |                                        |                |                                      |                        |                        | bit (                  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |

| Legend:       |                                                                  | r = Reserved I                         |                |                                      |                        |                        |                        |

| R = Readable  |                                                                  | W = Writable I                         | oit            |                                      | nented bit, read       |                        |                        |

| -n = Value at | POR                                                              | '1' = Bit is set                       |                | '0' = Bit is clea                    | ared                   | x = Bit is unkn        | own                    |

| bit 15        | CCPON: CCF                                                       | x Module Enat                          | ole bit        |                                      |                        |                        |                        |

|               | 1 = Module is<br>0 = Module is                                   |                                        | an operating r | node specified b                     | by the MOD<3:          | 0> control bits        |                        |

| bit 14        | Unimplemen                                                       | ted: Read as 'd                        | )'             |                                      |                        |                        |                        |

| bit 13        | CCPSIDL: CO                                                      | CPx Stop in Idle                       | Mode Bit       |                                      |                        |                        |                        |

|               |                                                                  | ues module op<br>s module opera        |                | device enters lo<br>ode              | lle mode               |                        |                        |

| bit 12        | Reserved: Ma                                                     |                                        |                |                                      |                        |                        |                        |

| bit 11        | TMRSYNC: T                                                       | ime Base Cloc                          | k Synchroniza  | ation bit                            |                        |                        |                        |

|               | (CLKSEL<br>0 = Synchron                                          | <b>&lt;2:0&gt;</b> ≠ 000)              |                | k is selected and<br>lock is selecte | -                      |                        | -                      |

| bit 10-8      |                                                                  | >: CCPx Time                           | Base Clock S   | elect bits <sup>(1)</sup>            |                        |                        |                        |

|               | 110 = Externa<br>101 = CLC1<br>100 = Reserv<br>011 = LPRC (      | 31 kHz source<br>dary Oscillator<br>ed | t              |                                      |                        |                        |                        |

| bit 7-6       | TMRPS<1:0>                                                       | : Time Base Pr                         | escale Select  | t bits                               |                        |                        |                        |

|               | 11 = 1:64 Pre<br>10 = 1:16 Pre<br>01 = 1:4 Pres<br>00 = 1:1 Pres | scaler<br>caler                        |                |                                      |                        |                        |                        |

| bit 5         | T32: 32-Bit Ti                                                   | me Base Selec                          | t bit          |                                      |                        |                        |                        |

|               |                                                                  |                                        |                | e edge output co<br>e edge output co |                        |                        |                        |

| bit 4         |                                                                  | ure/Compare N                          |                |                                      |                        |                        |                        |

|               | 1 = Input Cap                                                    | -                                      |                |                                      |                        |                        |                        |

### REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

NOTES:

### REGISTER 19-10: AD1CTMENH: CTMU ENABLE REGISTER (HIGH WORD)<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   | R/W-0   | R/W-0   | R/W-0                  | R/W-0                  | R/W-0   | R/W-0   | R/W-0   |

|---------|---------|---------|------------------------|------------------------|---------|---------|---------|

| CTMEN23 | CTMEN22 | CTMEN21 | CTMEN20 <sup>(2)</sup> | CTMEN19 <sup>(2)</sup> | CTMEN18 | CTMEN17 | CTMEN16 |

| bit 7   |         |         |                        |                        |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'.

bit 7-0 CTMEN<23:16>: CTMU Enabled During Conversion bits<sup>(2)</sup> 1 = CTMU is enabled and connected to the selected channel during conversion 0 = CTMU is not connected to this channel

- **Note 1:** Unimplemented channels are read as '0'.

- **2:** The CTMEN<20:19> bits are not implemented in 20-pin devices.

### REGISTER 19-11: AD1CTMENL: CTMU ENABLE REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0                   |

|---------|---------|---------|---------|---------|---------|--------|-------------------------|

| CTMEN15 | CTMEN14 | CTMEN13 | CTMEN12 | CTMEN11 | CTMEN10 | CTMEN9 | CTMEN8 <sup>(2,3)</sup> |

| bit 15  |         |         |         |         |         |        | bit 8                   |

| R/W-0                   |                         |                                                                  | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 |

|-------------------------|-------------------------|------------------------------------------------------------------|-------|--------|--------|--------|-------|

| CTMEN7 <sup>(2,3)</sup> | CTMEN6 <sup>(2,3)</sup> | MEN6 <sup>(2,3)</sup> CTMEN5 <sup>(2)</sup> CTMEN4 CTMEN3 CTMEN2 |       | CTMEN2 | CTMEN1 | CTMEN0 |       |

| bit 7                   |                         |                                                                  |       |        |        |        | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 CTMEN<15:0>: CTMU Enabled During Conversion bits<sup>(2,3)</sup>

1 = CTMU is enabled and connected to the selected channel during conversion

0 = CTMU is not connected to this channel

- Note 1: Unimplemented channels are read as '0'.

- 2: The CTMEN<8:5> bits are not implemented in 20-pin devices.

- **3:** The CTMEN<8:6> bits are not implemented in 28-pin devices.

NOTES:

| R/P-1                | R/P-1                               | R/P-1                | R/P-1                         | R/P-1                | R/P-1                 | R/P-1           | R/P-1            |

|----------------------|-------------------------------------|----------------------|-------------------------------|----------------------|-----------------------|-----------------|------------------|

| MCLRE <sup>(2)</sup> | BORV1 <sup>(3)</sup>                | BORV0 <sup>(3)</sup> | I2C1SEL <sup>(1)</sup>        | PWRTEN               | RETCFG <sup>(1)</sup> | BOREN1          | BOREN0           |

| bit 7                |                                     |                      |                               |                      |                       |                 | bit (            |

| Legend:              |                                     |                      |                               |                      |                       |                 |                  |

| R = Reada            | ble bit                             | P = Programr         | nable bit                     | U = Unimplen         | nented bit, read      | as '0'          |                  |

| -n = Value           | at POR                              | '1' = Bit is set     |                               | '0' = Bit is clea    |                       | x = Bit is unkr | nown             |

| bit 7                | MCLRE: MCL                          | R Pin Enable b       | <sub>it</sub> (2)             |                      |                       |                 |                  |

|                      |                                     |                      | 5 input pin is di             | sabled               |                       |                 |                  |

|                      |                                     |                      | MCLR is disab                 |                      |                       |                 |                  |

| bit 6-5              | BORV<1:0>: [                        | Brown-out Rese       | et Enable bits <sup>(3)</sup> | )                    |                       |                 |                  |

|                      | 11 = Brown-ou                       | it Reset is set t    | o the lowest vo               | ltage                |                       |                 |                  |

|                      |                                     |                      | o the middle vo               | 0                    |                       |                 |                  |

|                      |                                     |                      | o the highest ve              |                      |                       |                 |                  |

|                      |                                     | -                    |                               | a – Low-Power        | BOR (LPBOR)           | is selected     |                  |

| bit 4                | I2C1SEL: Alte                       |                      |                               |                      |                       |                 |                  |

|                      | 1 = Default loc<br>0 = Alternate lo |                      |                               |                      |                       |                 |                  |

| bit 3                | PWRTEN: Pov                         | ver-up Timer E       | nable bit                     |                      |                       |                 |                  |

|                      | 1 = PWRT is e                       | nabled               |                               |                      |                       |                 |                  |

|                      | 0 = PWRT is d                       | isabled              |                               |                      |                       |                 |                  |

| bit 2                | RETCFG: Ret                         | ention Regulate      | or Configuratior              | n bit <sup>(1)</sup> |                       |                 |                  |

|                      | 1 = Low-voltag<br>0 = Low-voltag    |                      |                               | ontrolled by the     | RETEN bit (RC         | ON<12>) durin   | g Sleep          |

| bit 1-0              | BOREN<1:0>:                         | Brown-out Re         | set Enable bits               |                      |                       |                 |                  |

|                      | 11 = Brown-ou                       | it Reset is enal     | oled in hardwar               | e; SBOREN bit        | is disabled           |                 |                  |

|                      |                                     |                      | •                             |                      | and disabled in S     | leep; SBOREN    | l bit is disable |

|                      |                                     |                      | rolled with the               |                      |                       |                 |                  |

|                      | 00 = Brown-ol                       | It Reset is disa     | bled in hardwar               | re; SBOREN DI        | t is disabled         |                 |                  |

| Note 1:              | This setting only devices.          | applies to the       | "FV" devices. T               | his bit is reserv    | ved and should I      | be maintained a | as '1' on "F"    |

| 2:                   | The MCLRE fus                       | e can only be c      | hanged when ι                 | using the VPP-b      | ased ICSP™ m          | ode entry. This | prevents a       |

|                      | user from accide                    |                      |                               |                      |                       | -               |                  |

|                      | Refer to Section                    |                      |                               |                      |                       |                 |                  |

### REGISTER 25-6: FPOR: RESET CONFIGURATION REGISTER

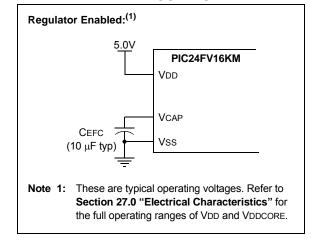

### 25.2 On-Chip Voltage Regulator

All of the PIC24FXXXXX family devices power their core digital logic at a nominal 3.0V. This may create an issue for designs that are required to operate at a higher typical voltage, as high as 5.0V. To simplify system design, all devices in the "FV" family incorporate an on-chip regulator that allows the device core to run at 3.0V, while the I/O is powered by VDD at a higher voltage.

The regulator is always enabled and provides power to the core from the other VDD pins. A low-ESR capacitor (such as ceramic) must be connected to the VCAP pin (Figure 25-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 27.1 "DC Characteristics"** and discussed in detail in **Section 2.0 "Guidelines for Getting Started with 16-Bit Microcontrollers"**.

In all of the "F" family of devices, the regulator is disabled. Instead, the core logic is directly powered from VDD. "F" devices operate at a lower range of VDD voltage, from 1.8V-3.6V.

### 25.2.1 VOLTAGE REGULATOR TRACKING MODE AND LOW-VOLTAGE DETECTION

For all PIC24FXXXXX devices, the on-chip regulator provides a constant voltage of 3.0V nominal to the digital core logic. The regulator can provide this level from a VDD of about 3.2V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels below 3.2V. In order to prevent "brown out" conditions when the voltage drops too low for the regulator, the regulator enters Tracking mode. In Tracking mode, the regulator output follows VDD with a typical voltage drop of 150 mV.

When the device enters Tracking mode, it is no longer possible to operate at full speed. To provide information about when the device enters Tracking mode, the on-chip High/Low-Voltage Detect (HLVD) module can be used. The HLVD trip point should be configured so that if VDD drops close to the minimum voltage for the operating frequency of the device, the HLVD Interrupt Flag, HLVDIF (IFS4<8>), will occur. This can be used to generate an interrupt and put the application into a low-power operational mode or trigger an orderly shutdown. Refer to **Section 27.1 "DC Characteristics"** for the specifications detailing the maximum operating speed based on the applied VDD voltage.

### FIGURE 25-1:

### CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR

### 25.2.2 VOLTAGE REGULATOR START-UP TIME

For PIC24FXXXXX family devices, it takes a short time, designated as TPM, for the regulator to generate a stable output. During this time, code execution is disabled. TPM is applied every time the device resumes operation after any power-down, including Sleep mode. TPM is specified in Section 27.2 "AC Characteristics and Timing Parameters".

### 25.3 Watchdog Timer (WDT)

For the PIC24FXXXXX family of devices, the WDT is driven by the LPRC Oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT Time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the Configuration bits, WDTPS<3:0> (FWDT<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranges from 1 ms to 131 seconds can be achieved.

### TABLE 27-4: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

|              | Standard Operating Conditions: 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |                 |                                  |      |     |      |       |            |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------|------|-----|------|-------|------------|--|--|--|

| Param<br>No. | Symbol                                                                                                                                                                                    | Chara           | octeristic                       | Min  | Тур | Max  | Units | Conditions |  |  |  |

| DC18         | Vhlvd                                                                                                                                                                                     | HLVD Voltage on | HLVDL<3:0> = 0000 <sup>(2)</sup> | _    | _   | 1.90 | V     |            |  |  |  |

|              |                                                                                                                                                                                           | VDD Transition  | HLVDL<3:0> = 0001                | 1.88 | —   | 2.13 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0010                | 2.09 | —   | 2.35 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0011                | 2.25 | —   | 2.53 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0100                | 2.35 | —   | 2.62 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0101                | 2.55 | —   | 2.84 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0110                | 2.80 | —   | 3.10 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0111                | 2.95 | _   | 3.25 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1000                | 3.09 | —   | 3.41 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1001                | 3.27 | —   | 3.59 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1010 <sup>(1)</sup> | 3.46 | _   | 3.79 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1011 <sup>(1)</sup> | 3.62 | _   | 4.01 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1100 <sup>(1)</sup> | 3.91 | —   | 4.26 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1101 <sup>(1)</sup> | 4.18 |     | 4.55 | V     |            |  |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1110 <sup>(1)</sup> | 4.49 |     | 4.87 | V     |            |  |  |  |

Note 1: These trip points should not be used on PIC24FXXKMXXX devices.

2: This trip point should not be used on PIC24FVXXKMXXX devices.

### TABLE 27-5:BOR TRIP POINTS