Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХЕ

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km202-e-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Pin Diagrams (Continued)

|                                                                                                                                                                                                      | 48-Pin UQFN <sup>(1)</sup> Pin Pion Features |                                     |                                         |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| 48-Pin UQFN(')                                                                                                                                                                                       | FIII                                         | PIC24FXXKMX04                       | PIC24FVXXKMX04                          |  |  |  |  |  |  |

| RBS<br>VCDD<br>VCDD<br>VCDD<br>VCDD<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3                                                                                            | 1                                            | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/    | /CLC10/CTED4/CN21/RB9                   |  |  |  |  |  |  |

| $\overline{x} \overline{x} \overline{x} \overline{x} \overline{z} \overline{z} \overline{z} \overline{z} \overline{z} \overline{x} \overline{x} \overline{x} \overline{x} \overline{x} \overline{x}$ | 2                                            | U1RX/ /CN18/RC6                     |                                         |  |  |  |  |  |  |

| RB9 1 8 4 8 4 7 7 7 7 7 7 8 8 8 8 8 8 8 8 8 8                                                                                                                                                        | 3                                            | U1TX/ /CN17/RC7                     |                                         |  |  |  |  |  |  |

| RB9 1 36 RB4<br>RC6 2 35 RA8                                                                                                                                                                         |                                              | OC2/CN20/RC8                        |                                         |  |  |  |  |  |  |

| RC7 3 34 RA3<br>RC8 4 33 RA2                                                                                                                                                                         |                                              | IC4/OC2F/CTED7/CN19/RC9             |                                         |  |  |  |  |  |  |

| RC9 5 32 n/c                                                                                                                                                                                         | 6                                            | IC1/ / /CTED3/CN9/RA7               | 1                                       |  |  |  |  |  |  |

| RA7         6         PIC24FXXKMX04         31         Vss           RA6         7         PIC24FVXXKMX04         30         Vbb                                                                     |                                              | /OC1A/CTED1/INT2/CN8/RA6            | VDDCORE OF VCAP                         |  |  |  |  |  |  |

| n/c 8 29 RC2                                                                                                                                                                                         | 2 0                                          | n/c                                 | n/c                                     |  |  |  |  |  |  |

| RB10 9 28 RC <sup>2</sup><br>RB11 10 27 RC                                                                                                                                                           | <u> </u>                                     | PGED2/SDI1/OC1C/CTED11/CN16/RB10    |                                         |  |  |  |  |  |  |

| RB12 11 26 RB3                                                                                                                                                                                       | 3 10                                         | PGEC2/SCK1/OC2A/CTED9/CN15/RB11     |                                         |  |  |  |  |  |  |

| RB13 12 25 RB2 25 RB2 25 RB2                                                                                                                                                                         | 2 11                                         | /AN12/HLVDIN/ /CTED2/<br>CN14/RB12  | /AN12/HLVDIN/ /CTED2/<br>INT2/CN14/RB12 |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 12                                           | / /AN11/SDO1/OC1D/CTPLS             |                                         |  |  |  |  |  |  |

| RA10<br>RA11<br>RB14<br>RB14<br>Vss/AVsp<br>WCLR/RA5<br>MCLR/RA5<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10                                                               | 13                                           | / /CN35/RA10                        |                                         |  |  |  |  |  |  |

| R R SSS/ANDI                                                                                                                                                                                         | 14                                           | / /CTED8/CN36/RA11                  |                                         |  |  |  |  |  |  |

| > >                                                                                                                                                                                                  | 15                                           | /CVREF/ / /AN10/                    | / /C1OUT/OCFA/CTED5/INT1/               |  |  |  |  |  |  |

|                                                                                                                                                                                                      |                                              | CN12/RB14                           |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 16                                           |                                     | I/TCKIA/CTED6/CN11/RB15                 |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 17                                           | Vss/AVss                            |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 18                                           | VDD/AVDD                            |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 19                                           | MCLR/VPP/RA5                        |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 20<br>21                                     | n/c<br>CVREF+/VREF+/ +/AN0/ /       | CVREF+/VREF+/ +/AN0/ /                  |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 21                                           | CN2/RA0                             | CTED1/CN2/RA0                           |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 22                                           | CVREF-/VREF-/AN1/CN3/RA1            |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 23                                           | PGED1/AN2/CTCMP/ULPWU/C1IND/        | / /CN4/RB0                              |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 24                                           | PGEC1/ / /AN3/C1INC/                | / /CTED12/CN5/RB1                       |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 25                                           | / /AN4/C1INB/ / /T                  | CKIB/CTED13/CN6/RB2                     |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 26                                           | /AN5/C1INA/ / /CN7/RB3              |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 27                                           | AN6/CN32/RC0                        |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 28                                           |                                     |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 29<br>30                                     | AN8/CN10/RC2<br>Vdd                 |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 30                                           | Vss                                 |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 32                                           | n/c                                 |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 33                                           | OSCI/AN13/CLKI/CN30/RA2             |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 34                                           | OSCO/CLKO/AN14/CN29/RA3             |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 35                                           | OCFB/CN33/RA8                       |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 36                                           | SOSCI/AN15/ / /CN1/RB4              |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 37                                           | SOSCO/SCLKI/AN16/PWRLCLK/ /CN       | 0/RA4                                   |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 38                                           | /CN34/RA9                           |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 39                                           | /CN28/RC3                           |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 40                                           | /CN25/RC4                           |                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 41                                           | /CN26/RC5                           |                                         |  |  |  |  |  |  |

| Legend: Values in indicate pin                                                                                                                                                                       | 42                                           | Vss                                 |                                         |  |  |  |  |  |  |

| Legend: Values in indicate pin<br>function differences between                                                                                                                                       | 43                                           | VDD                                 |                                         |  |  |  |  |  |  |

| PIC24F(V)XXKM202 and                                                                                                                                                                                 | 44                                           | n/c                                 |                                         |  |  |  |  |  |  |

| PIC24F(V)XXKM102 devices.                                                                                                                                                                            | 45                                           | PGED3/AN17/ASDA1/OC1E/CLCINA/CN27/F |                                         |  |  |  |  |  |  |

| Note 1: Exposed pad on underside of                                                                                                                                                                  | 46                                           | PGEC3/AN18/ASCL1/OC1F/CLCINB/CN24/F |                                         |  |  |  |  |  |  |

| device is connected to Vss.                                                                                                                                                                          | 47                                           | AN19/INT0/CN23/RB7                  | AN19/ /OC1A/INT0/CN23/RB7               |  |  |  |  |  |  |

|                                                                                                                                                                                                      | 48                                           | AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/  | CN22/RB8                                |  |  |  |  |  |  |

NOTES:

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FV08KM101 PIC24F08KM101

- PIC24FV08KM102

- PIC24F08KM102

PIC24F16KM102

- PIC24FV16KM102

- PIC24FV16KM104 PIC24F16KM104

- PIC24FV08KM202 PIC24F08KM202

- PIC24FV08KM204 PIC24F08KM204

- PIC24FV16KM202

- PIC24F16KM202

- PIC24FV16KM204 PIC24F16KM204

The PIC24FV16KM204 family introduces many new analog features to the extreme low-power Microchip devices. This is a 16-bit microcontroller family with a broad peripheral feature set and enhanced computational performance. This family also offers a new migration option for those high-performance applications which may be outgrowing their 8-bit platforms, but do not require the numerical processing power of a Digital Signal Processor (DSC).

## 1.1 Core Features

### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear Addressing of up to 16 Mbytes (program space) and 16 Kbytes (data)

- A 16-element working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32-bit by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as C

- Operational performance up to 16 MIPS

## 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24FV16KM204 family incorporate a range of features that can significantly reduce power consumption during operation. Key features include:

- On-the-Fly Clock Switching, to allow the device clock to be changed under software control to the Timer1 source or the internal, low-power RC Oscillator during operation, allowing users to incorporate power-saving ideas into their software designs.

- Doze Mode Operation, when timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes, to allow the microcontroller to suspend all operations or selectively shut down its core while leaving its peripherals active with a single instruction in software.

# 1.1.3 OSCILLATOR OPTIONS AND FEATURES

The PIC24FV16KM204 family offers five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock (EC) modes offering the option of a divide-by-2 clock output.

- Two Fast Internal Oscillators (FRCs), one with a nominal 8 MHz output and the other with a nominal 500 kHz output. These outputs can also be divided under software control to provide clock speed as low as 31 kHz or 2 kHz.

- A Phase Locked Loop (PLL) frequency multiplier, available to the external oscillator modes and the 8 MHz FRC Oscillator, which allows clock speeds of up to 32 MHz.

- A separate internal RC Oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

## TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                            |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  | I                                | Pin Numb      | er                     |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| C1OUT    | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | 0   | —      | Comparator 1 Output        |

| C2INA    | _                                | 5                                | 2             | 22                     | 24             |                                  | 5                                | 2             | 22                     | 24             | I   | ANA    | Comparator 2 Input A (+)   |

| C2INB    | _                                | 4                                | 1             | 21                     | 23             |                                  | 4                                | 1             | 21                     | 23             | I   | ANA    | Comparator 2 Input B (-)   |

| C2INC    | _                                | 7                                | 4             | 24                     | 26             |                                  | 7                                | 4             | 24                     | 26             | I   | ANA    | Comparator 2 Input C (+)   |

| C2IND    | _                                | 6                                | 3             | 23                     | 25             |                                  | 6                                | 3             | 23                     | 25             | I   | ANA    | Comparator 2 Input D (-)   |

| C2OUT    | _                                | 20                               | 17            | 7                      | 7              |                                  | 16                               | 13            | 43                     | 47             | 0   |        | Comparator 2 Output        |

| C3INA    | _                                | 26                               | 23            | 15                     | 16             |                                  | 26                               | 23            | 15                     | 16             | I   | ANA    | Comparator 3 Input A (+)   |

| C3INB    | _                                | 25                               | 22            | 14                     | 15             |                                  | 25                               | 22            | 14                     | 15             | I   | ANA    | Comparator 3 Input B (-)   |

| C3INC    | _                                | 2                                | 27            | 19                     | 21             |                                  | 2                                | 27            | 19                     | 21             | I   | ANA    | Comparator 3 Input C (+)   |

| C3IND    | _                                | 4                                | 1             | 21                     | 23             |                                  | 4                                | 1             | 21                     | 23             | I   | ANA    | Comparator 3 Input D (-)   |

| C3OUT    | _                                | 17                               | 14            | 44                     | 48             |                                  | 17                               | 14            | 44                     | 48             | 0   | _      | Comparator 3 Output        |

| CLC10    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   |        | CLC 1 Output               |

| CLC2O    | _                                | 19                               | 16            | 6                      | 6              |                                  | 19                               | 16            | 6                      | 6              | 0   |        | CLC 2 Output               |

| CLCINA   | 9                                | 14                               | 11            | 41                     | 45             | 9                                | 14                               | 11            | 41                     | 45             | I   | ST     | CLC External Input A       |

| CLCINB   | 10                               | 15                               | 12            | 42                     | 46             | 10                               | 15                               | 12            | 42                     | 46             | I   | ST     | CLC External Input B       |

| CLKI     | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I   | ANA    | Primary Clock Input        |

| CLKO     | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | 0   |        | System Clock Output        |

| CN0      | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | I   | ST     | Interrupt-on-Change Inputs |

| CN1      | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | I   | ST     | Interrupt-on-Change Inputs |

| CN2      | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ST     | Interrupt-on-Change Inputs |

| CN3      | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | I   | ST     | Interrupt-on-Change Inputs |

| CN4      | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I   | ST     | Interrupt-on-Change Inputs |

| CN5      | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I   | ST     | Interrupt-on-Change Inputs |

| CN6      | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | Interrupt-on-Change Inputs |

| CN7      | _                                | 7                                | 4             | 24                     | 26             |                                  | 7                                | 4             | 24                     | 26             | Ι   | ST     | Interrupt-on-Change Inputs |

| CN8      | 14                               | 20                               | 17            | 7                      | 7              |                                  |                                  |               | _                      |                | Ι   | ST     | Interrupt-on-Change Inputs |

| CN9      | _                                | 19                               | 16            | 6                      | 6              |                                  | 19                               | 16            | 6                      | 6              | Ι   | ST     | Interrupt-on-Change Inputs |

| CN10     | _                                | _                                | _             | 27                     | 29             |                                  |                                  | _             | 27                     | 29             | Ι   | ST     | Interrupt-on-Change Inputs |

| CN11     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | Interrupt-on-Change Inputs |

| CN12     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | Interrupt-on-Change Inputs |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

NOTES:

#### TABLE 4-21: PORTA REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 <sup>(4,5)</sup> | Bit 10 <sup>(4,5)</sup> | Bit 9 <sup>(4,5)</sup> | Bit 8 <sup>(4,5)</sup> | Bit 7 <sup>(4)</sup> | Bit 6 <sup>(3)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|--------|--------|--------|--------|-------------------------|-------------------------|------------------------|------------------------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|---------------------|

| TRISA     | 2C0h  |        | _      | _      | _      | TRISA11                 | TRISA10                 | TRISA9                 | TRISA8                 | TRISA7               | TRISA6               | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 0FDF <sup>(1)</sup> |

| PORTA     | 2C2h  | -      | —      | —      |        | RA11                    | RA10                    | RA9                    | RA8                    | RA7                  | RA6                  | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx                |

| LATA      | 2C4h  | -      | —      | —      |        | LATA11                  | LATA10                  | LATA9                  | LATA8                  | LATA7                | LATA6                | _                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx                |

| ODCA      | 2C6h  | _      | —      | _      | _      | ODA11                   | ODA10                   | ODA9                   | ODA8                   | ODA7                 | ODA6                 | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are only available when MCLRE (FPOR<7>) = 0.

3: These bits are not implemented in FV devices.

4: These bits are not implemented in 20-pin devices.

5: These bits are not implemented in 28-pin devices.

#### TABLE 4-22: PORTB REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7  | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|--------|----------------------|----------------------|--------|----------------------|--------|--------|--------|---------------------|

| TRISB     | 2C8h  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7 | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2 | TRISB1 | TRISB0 | <sub>FFFF</sub> (1) |

| PORTB     | 2CAh  | RB15    | RB14    | RB13    | RB12    | RB11                  | RB10                  | RB9    | RB8    | RB7    | RB6                  | RB5                  | RB4    | RB3                  | RB2    | RB1    | RB0    | xxxx                |

| LATB      | 2CCh  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11                | LATB10                | LATB9  | LATB8  | LATB7  | LATB6                | LATB5                | LATB4  | LATB3                | LATB2  | LATB1  | LATB0  | xxxx                |

| ODCB      | 2CEh  | ODB15   | ODB14   | ODB13   | ODB12   | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7   | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2   | ODB1   | ODB0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

#### TABLE 4-23: PORTC REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 <sup>(2,3)</sup> | Bit 8 <sup>(2,3)</sup> | Bit 7 <sup>(2,3)</sup> | Bit 6 <sup>(2,3)</sup> | Bit 5 <sup>(2,3)</sup> | Bit 4 <sup>(2,3)</sup> | Bit 3 <sup>(2,3)</sup> | Bit 2 <sup>(2,3)</sup> | Bit 1 <sup>(2,3)</sup> | Bit 0 <sup>(2,3)</sup> | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------|

| TRISC        | 2D0h  | _      | _      |        | _      | —      | _      | TRISC9                 | TRISC8                 | TRISC7                 | TRISC6                 | TRISC5                 | TRISC4                 | TRISC3                 | TRISC2                 | TRISC1                 | TRISC0                 | 03FF <sup>(1)</sup> |

| PORTC        | 2D2h  | —      | _      | _      | -      | —      | _      | RC9                    | RC8                    | RC7                    | RC6                    | RC5                    | RC4                    | RC3                    | RC2                    | RC1                    | RC0                    | xxxx                |

| LATTC        | 2D4h  | —      | _      | _      | -      | —      | _      | LATC9                  | LATC8                  | LATC7                  | LATC6                  | LATC5                  | LATC4                  | LATC3                  | LATC2                  | LATC1                  | LATC0                  | xxxx                |

| ODCC         | 2D6h  | _      | _      | —      | -      | —      | _      | ODC9                   | ODC8                   | ODC7                   | ODC6                   | ODC5                   | ODC4                   | ODC3                   | ODC2                   | ODC1                   | ODC0                   | 0000                |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

**2:** These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

# **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit<br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | SLEEP: Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode                                       |

| bit 2 | IDLE: Wake-up from Idle Flag bit<br>1 = Device has been in Idle mode<br>0 = Device has not been in Idle mode                                           |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred (the BOR is also set after a POR)<br>0 = A Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-on Reset has occurred<br>0 = A Power-on Reset has not occurred                                      |

|       |                                                                                                                                                        |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

#### TABLE 7-1: RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

Note: All Reset flag bits may be set or cleared by the user software.

### REGISTER 8-21: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0                 | R/W-1      | R/W-0            | R/W-0   | U-0               | U-0              | U-0             | U-0     |

|---------------------|------------|------------------|---------|-------------------|------------------|-----------------|---------|

|                     | U1RXIP2    | U1RXIP1          | U1RXIP0 | _                 | —                | —               | _       |

| bit 15              |            |                  |         |                   |                  |                 | bit 8   |

| U-0                 | U-0        | U-0              | U-0     | U-0               | R/W-1            | R/W-0           | R/W-0   |

| _                   | _          | _                | _       | _                 | CCT2IP2          | CCT2IP1         | CCT2IP0 |

| bit 7               |            |                  |         | •                 |                  |                 | bit 0   |

|                     |            |                  |         |                   |                  |                 |         |

| Legend:             |            |                  |         |                   |                  |                 |         |

| R = Readab          | le bit     | W = Writable     | bit     | U = Unimplem      | nented bit, read | l as '0'        |         |

| -n = Value a        | t POR      | '1' = Bit is set |         | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|                     |            |                  |         |                   |                  |                 |         |

|                     |            |                  |         |                   |                  |                 |         |

| bit 15              | Unimplemen | ted: Read as 'd  | כ'      |                   |                  |                 |         |

| bit 15<br>bit 14-12 | •          | ted: Read as 'd  |         | Priority bits     |                  |                 |         |

- bit 11-3

bit 2-0

CCT2IP<2:0>: Capture/Compare 2 Timer Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt)

- ٠

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

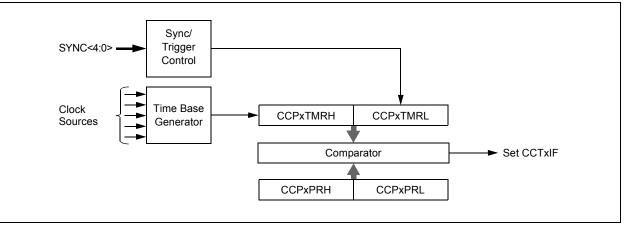

## FIGURE 13-4: 32-BIT TIMER MODE

'1' = Bit is set

#### REGISTER 14-8: SSPxADD: MSSPx SLAVE ADDRESS/BAUD RATE GENERATOR REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | U-0      | U-0   |

|--------------|-------|--------------|-------|--------------|------------------|----------|-------|

| —            | —     | —            |       | —            | _                | —        | _     |

| bit 15       |       |              |       |              |                  |          | bit 8 |

|              |       |              |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| ADD7         | ADD6  | ADD5         | ADD4  | ADD3         | ADD2             | ADD1     | ADD0  |

| bit 7        |       |              |       |              |                  |          | bit 0 |

|              |       |              |       |              |                  |          |       |

| Legend:      |       |              |       |              |                  |          |       |

| R = Readable | e bit | W = Writable | bit   | U = Unimplen | nented bit, read | l as '0' |       |

'0' = Bit is cleared

x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0

ADD<7:0>: Slave Address/Baud Rate Generator Value bits

SPI Master and I<sup>2</sup>C™ Master modes:

Reload value for the Baud Rate Generator. Clock period is (([SPxADD] + 1) \* 2)/Fosc.

I<sup>2</sup>C Slave modes:

Represents 7 or 8 bits of the slave address, depending on the addressing mode used:

7-Bit mode:

Address is ADD<7:1>; ADD<0> is ignored.

10-Bit LSb mode:

ADD<7:0> are the Least Significant bits of the address.

10-Bit MSb mode:

ADD<2:1> are the two Most Significant bits of the address; ADD<7:3> are always '11110' as a specification requirement; ADD<0> is ignored.

### REGISTER 14-9: SSPxMSK: I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(1)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                              |

|----------|---------------------------------------------------------|

| bit 7-0  | MSK<7:0>: Slave Address Mask Select bits <sup>(1)</sup> |

|          | 1 = Masking of corresponding bit of SSPxADD is enabled  |

|          | 0 = Masking of corresponding bit of SSPxADD is disabled |

Note 1: MSK0 is not used as a mask bit in 7-bit addressing.

## 19.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR)

Conversion

- Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (internal and external)

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H)

Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU, and a configurable results buffer. There is a legacy 10-bit mode on this A/D to allow the option to run with lower resolution in order to obtain higher throughput. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 19-1.

#### REGISTER 19-5: AD1CHS: A/D SAMPLE SELECT REGISTER (CONTINUED)

- bit 7-5 **CH0NA<2:0>:** Sample A Channel 0 Negative Input Select bits The same definitions as for CHONB<2:0>.

- bit 4-0 **CH0SA<4:0>:** Sample A Channel 0 Positive Input Select bits The same definitions as for CHONA<4:0>.

- Note 1: This is implemented on 44-pin devices only.

- 2: This is implemented on 28-pin and 44-pin devices only.

- 3: The band gap value used for this input is 2x or 4x the internal VBG, which is selected when PVCFG<1:0> = 1x.

## REGISTER 19-6: AD1CHITH: A/D SCAN COMPARE HIT REGISTER (HIGH WORD)<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|----------------------|----------------------|-------|-------|-------|

| CHH23 | CHH22 | CHH21 | CHH20 <sup>(2)</sup> | CHH19 <sup>(2)</sup> | CHH18 | CHH17 | CHH16 |

| bit 7 |       |       |                      |                      |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'.

bit 7-0 CHH<23:16>: A/D Compare Hit bits<sup>(2)</sup>

If CM<1:0> = 11:

1 = A/D Result Buffer x has been written with data or a match has occurred

0 = A/D Result Buffer x has not been written with data

For All Other Values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

2: The CHH<20:19> bits are not implemented in 20-pin devices.

| U-0    | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | U-0   | U-0   |

|--------|-------|-------|----------------------|----------------------|-------|-------|-------|

| _      | CSS30 | CSS29 | CSS28                | CSS27                | CSS26 | —     | —     |

| bit 15 |       |       |                      |                      |       |       | bit 8 |

|        |       |       |                      |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| CSS23  | CSS22 | CSS21 | CSS20 <sup>(2)</sup> | CSS19 <sup>(2)</sup> | CSS18 | CSS17 | CSS16 |

| bit 7  |       |       |                      |                      |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

- bit 14-10CSS<30:26>: A/D Input Scan Selection bits1 = Includes the corresponding channel for input scan0 = Skips the channel for input scanbit 9-8Unimplemented: Read as '0'bit 7-0CSS<23:16>: A/D Input Scan Selection bits<sup>(2)</sup>1 = Includes the corresponding channel for input scan0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<20:19> bits are not implemented in 20-pin devices.

#### REGISTER 19-9: AD1CSSL: A/D INPUT SCAN SELECT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                 | R/W-0               | R/W-0                      | R/W-0                                  | R/W-0                                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                                                                                                              |

|-----------------------|---------------------|----------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| CSS14                 | CSS13               | CSS12                      | CSS11                                  | CSS10                                                                                                     | CSS9                                                                                                                                  | CSS8 <sup>(2,3)</sup>                                                                                                                              |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       | bit 8                                                                                                                                              |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       |                                                                                                                                                    |

| R/W-0                 | R/W-0               | R/W-0                      | R/W-0                                  | R/W-0                                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                                                                                                              |

| CSS6 <sup>(2,3)</sup> | CSS5 <sup>(2)</sup> | CSS4                       | CSS3                                   | CSS2                                                                                                      | CSS1                                                                                                                                  | CSS0                                                                                                                                               |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       | bit 0                                                                                                                                              |

|                       | R/W-0               | CSS14 CSS13<br>R/W-0 R/W-0 | CSS14 CSS13 CSS12<br>R/W-0 R/W-0 R/W-0 | CSS14         CSS13         CSS12         CSS11           R/W-0         R/W-0         R/W-0         R/W-0 | CSS14         CSS13         CSS12         CSS11         CSS10           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0 | CSS14         CSS13         CSS12         CSS11         CSS10         CSS9           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CSS<15:0>: A/D Input Scan Selection bits<sup>(2,3)</sup>

1 = Includes the corresponding ANx input for scan

- 0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<8:5> bits are not implemented in 20-pin devices.

- 3: The CSS<8:6> bits are not implemented in 28-pin devices.

| R/W-0        | U-0           | R/W-0                                          | R/W-0          | R/W-0                            | U-0              | R/W-0           | R/W-0        |  |  |  |

|--------------|---------------|------------------------------------------------|----------------|----------------------------------|------------------|-----------------|--------------|--|--|--|

| DACEN        |               | DACSIDL                                        | DACSLP         | DACFM                            |                  | SRDIS           | DACTRIG      |  |  |  |

| bit 15       |               |                                                | 27.002         |                                  |                  | 0.12.0          | bit 8        |  |  |  |

| R/W-0        | R/W-0         | R/W-0                                          | R/W-0          | R/W-0                            | R/W-0            | R/W-0           | R/W-0        |  |  |  |

| DACOE        | DACTSEL4      | DACTSEL3                                       | DACTSEL2       | DACTSEL1                         | DACTSEL0         | DACREF1         | DACREF0      |  |  |  |

| bit 7        |               |                                                |                |                                  |                  |                 | bit 0        |  |  |  |

| Legend:      |               |                                                |                |                                  |                  |                 |              |  |  |  |

| R = Readab   | le bit        | W = Writable                                   | bit            | U = Unimplen                     | nented bit, read | l as '0'        |              |  |  |  |

| -n = Value a | t POR         | '1' = Bit is set                               |                | '0' = Bit is clea                |                  | x = Bit is unkr | nown         |  |  |  |

|              |               |                                                |                |                                  |                  |                 | -            |  |  |  |

| bit 15       | DACEN: DAC    | x Enable bit                                   |                |                                  |                  |                 |              |  |  |  |

|              | 1 = Module is | s enabled                                      |                |                                  |                  |                 |              |  |  |  |

|              | 0 = Module is | s disabled                                     |                |                                  |                  |                 |              |  |  |  |

| bit 14       | Unimplement   | ted: Read as 'd                                | )'             |                                  |                  |                 |              |  |  |  |

| bit 13       | DACSIDL: DA   | DACSIDL: DACx Stop in Idle Mode bit            |                |                                  |                  |                 |              |  |  |  |

|              |               | ues module op<br>s module opera                |                | device enters lo<br>ode          | lle mode         |                 |              |  |  |  |

| bit 12       | DACSLP: DA    | ACSLP: DACx Enable Peripheral During Sleep bit |                |                                  |                  |                 |              |  |  |  |

|              |               |                                                |                | ent value of DA<br>; DACxOUT pi  |                  |                 | nd LATx bits |  |  |  |

| bit 11       | DACFM: DAC    | x Data Format                                  | Select bit     |                                  |                  |                 |              |  |  |  |

|              |               | ft justified (data<br>ht justified (dat        |                |                                  |                  |                 |              |  |  |  |

| bit 10       | Unimplement   | ted: Read as '0                                | )'             |                                  |                  |                 |              |  |  |  |

| bit 9        | SRDIS: Soft F | Reset Disable b                                | oit            |                                  |                  |                 |              |  |  |  |

|              |               |                                                |                | only on a POR<br>on any type of  |                  | :               |              |  |  |  |

| bit 8        |               | ACx Trigger Inp                                |                |                                  |                  |                 |              |  |  |  |

|              |               |                                                |                | selected (by D<br>as DACxDAT is  |                  |                 | ed)          |  |  |  |

| bit 7        | DACOE: DAC    | Cx Output Enab                                 | le bit         |                                  |                  |                 |              |  |  |  |

|              | 1 = DACx out  | put pin is enabl                               | led and driven | on the DACxO<br>put is available |                  | her peripherals | only         |  |  |  |

| Note 1.      |               | in configuration                               |                |                                  | -1.0~)           |                 | -            |  |  |  |

### REGISTER 20-1: DACxCON: DACx CONTROL REGISTER

**Note 1:** BGBUF1 voltage is configured by BUFREF<1:0> (BUFCON0<1:0>).

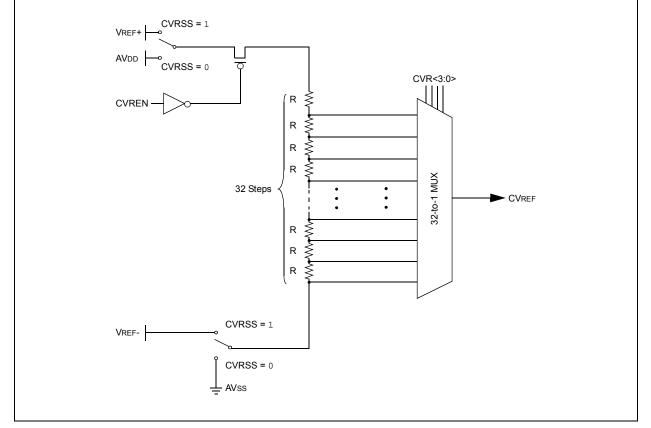

## 23.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator Voltage Reference, refer to the "PIC24F Family Reference Manual", "Comparator Voltage Reference Module" (DS39709).

## 23.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 23-1). The comparator voltage reference provides a range of output voltages with 32 distinct levels.

The comparator voltage reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

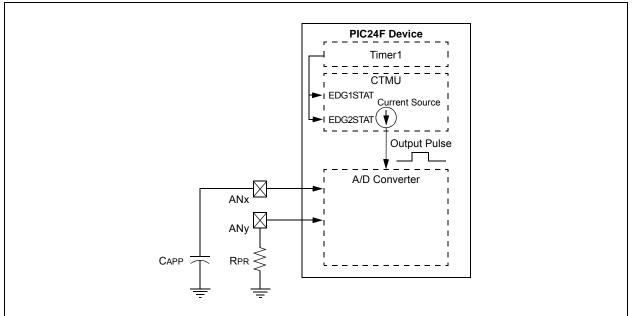

# FIGURE 24-1: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR CAPACITANCE MEASUREMENT

### 24.2 Measuring Time

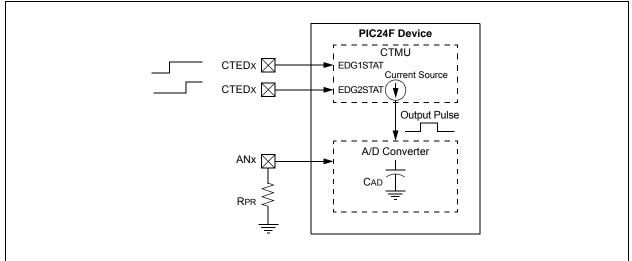

Time measurements on the pulse width can be similarly performed using the A/D module's Internal Capacitor (CAD) and a precision resistor for current calibration. Figure 24-2 displays the external connections used for time measurements, and how the CTMU and A/D modules are related in this application. This example also shows both edge events coming from the external CTEDx pins, but other configurations using internal edge sources are possible.

FIGURE 24-2: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

| DC CHARACTERISTICS |     |                     |     | l <b>Operatin</b><br>g tempera | -   | <b>2.0V</b><br>-40° | : 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |            |  |  |

|--------------------|-----|---------------------|-----|--------------------------------|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Param<br>No.       | Sym | Characteristic      | Min | Typ <sup>(1)</sup>             | Max | Units               | Cond                                                                                                                                                                             | itions     |  |  |

|                    | Vol | Output Low Voltage  |     |                                |     |                     |                                                                                                                                                                                  |            |  |  |

| DO10               |     | All I/O Pins        | _   | —                              | 0.4 | V                   | IOL = 8.0 mA                                                                                                                                                                     | VDD = 4.5V |  |  |

|                    |     |                     | _   | _                              | 0.4 | V                   | IOL = 4.0 mA                                                                                                                                                                     | VDD = 3.6V |  |  |

|                    |     |                     | _   | _                              | 0.4 | V                   | IOL = 3.5 mA                                                                                                                                                                     | VDD = 2.0V |  |  |

| DO16               |     | OSC2/CLKO           | _   | _                              | 0.4 | V                   | IOL = 2.0 mA                                                                                                                                                                     | VDD = 4.5V |  |  |

|                    |     |                     | _   | _                              | 0.4 | V                   | IOL = 1.2 mA                                                                                                                                                                     | VDD = 3.6V |  |  |

|                    |     |                     | _   | _                              | 0.4 | V                   | IOL = 0.4 mA                                                                                                                                                                     | VDD = 2.0V |  |  |

|                    | Vон | Output High Voltage |     |                                |     |                     |                                                                                                                                                                                  |            |  |  |

| DO20               |     | All I/O Pins        | 3.8 | _                              | _   | V                   | Iон = -3.5 mA                                                                                                                                                                    | VDD = 4.5V |  |  |

|                    |     |                     | 3   | _                              | —   | V                   | Iон = -3.0 mA                                                                                                                                                                    | VDD = 3.6V |  |  |

|                    |     |                     | 1.6 | —                              | —   | V                   | Іон = -1.0 mA                                                                                                                                                                    | VDD = 2.0V |  |  |

| DO26               |     | OSC2/CLKO           | 3.8 | —                              | —   | V                   | Іон = -2.0 mA                                                                                                                                                                    | VDD = 4.5V |  |  |

|                    |     |                     | 3   | —                              | —   | V                   | Іон = -1.0 mA                                                                                                                                                                    | VDD = 3.6V |  |  |

|                    |     |                     | 1.6 | _                              | —   | V                   | Iон = -0.5 mA                                                                                                                                                                    | VDD = 2.0V |  |  |

### TABLE 27-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 27-11: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |       |                                      | Standard Operating Conditions Operating temperature |                    |     |       | ns: 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +125°C for Extended |  |  |

|--------------------|-------|--------------------------------------|-----------------------------------------------------|--------------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                       | Min                                                 | Typ <sup>(1)</sup> | Max | Units | Conditions                                                                                                                                 |  |  |

|                    |       | Program Flash Memory                 |                                                     |                    |     |       |                                                                                                                                            |  |  |

| D130               | Eр    | Cell Endurance                       | 10,000 <b>(2)</b>                                   | —                  | —   | E/W   |                                                                                                                                            |  |  |

| D131               | Vpr   | VDD for Read                         | VMIN                                                | —                  | 3.6 | V     | VMIN = Minimum operating voltage                                                                                                           |  |  |

| D133A              | Tiw   | Self-Timed Write Cycle<br>Time       | —                                                   | 2                  | —   | ms    |                                                                                                                                            |  |  |

| D134               | TRETD | Characteristic Retention             | 40                                                  | —                  | —   | Year  | Provided no other specifications are violated                                                                                              |  |  |

| D135               | IDDP  | Supply Current During<br>Programming | —                                                   | 10                 | _   | mA    |                                                                                                                                            |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: Self-write and block erase.

| Param.<br>No. | Symbol  | Characteristic             |              | Min         | Max  | Units | Conditions                                 |  |

|---------------|---------|----------------------------|--------------|-------------|------|-------|--------------------------------------------|--|