# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

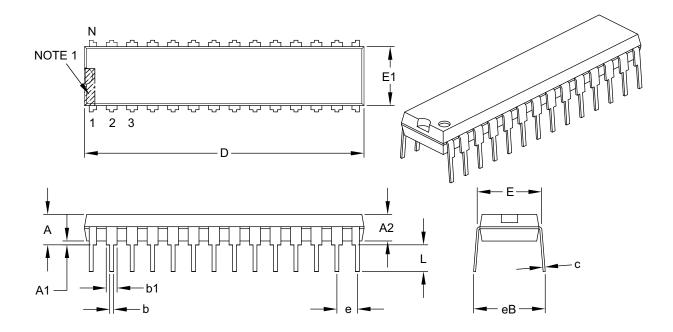

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 28-SPDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km202-e-sp |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                |      | N                     | lemory       | 1               |                   |              |                  |      |      | Pe                  | riphe     | rals   |             |      |      |     |           |

|----------------|------|-----------------------|--------------|-----------------|-------------------|--------------|------------------|------|------|---------------------|-----------|--------|-------------|------|------|-----|-----------|

| Device         | Pins | Flash Program (bytes) | SRAM (bytes) | EE Data (bytes) | Voltage Range (V) | 16-Bit Timer | 16-Bit MCCP/SCCP | MSSP | UART | 12-Bit A/D Channels | 8-Bit DAC | Op Amp | Comparators | CTMU | RTCC | CLC | ICD BRKPT |

| 5V Devices     |      |                       |              |                 |                   |              |                  |      |      |                     |           |        |             |      |      |     |           |

| PIC24FV16KM204 | 44   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM202 | 28   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM204 | 44   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM202 | 28   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM104 | 44   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 22                  | —         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV16KM102 | 28   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM102 | 28   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM101 | 20   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 16                  | _         | -      | 1           | Yes  | _    | 1   | 3         |

|                |      |                       |              |                 |                   | 3V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24F16KM204  | 44   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM202  | 28   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM204  | 44   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM202  | 28   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM104  | 44   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 22                  | _         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F16KM102  | 28   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24F08KM102  | 28   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | —         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F08KM101  | 20   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 16                  |           |        | 1           | Yes  | _    | 1   | 3         |

# **Table of Contents**

| 1.0   | Device Overview                                             |       |

|-------|-------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 29    |

| 3.0   | CPU                                                         | 35    |

| 4.0   | Memory Organization                                         | 41    |

| 5.0   | Flash Program Memory                                        | 67    |

| 6.0   | Data EEPROM Memory                                          | 73    |

| 7.0   | Resets                                                      | 79    |

| 8.0   | Interrupt Controller                                        | 85    |

| 9.0   | Oscillator Configuration                                    | . 121 |

| 10.0  | Power-Saving Features                                       | . 131 |

| 11.0  | I/O Ports                                                   | . 137 |

| 12.0  | Timer1                                                      |       |

| 13.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)           | . 143 |

| 14.0  | Master Synchronous Serial Port (MSSP)                       |       |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART)          | . 173 |

| 16.0  | Real-Time Clock and Calendar (RTCC)                         | . 181 |

| 17.0  | Configurable Logic Cell (CLC)                               | . 195 |

| 18.0  | High/Low-Voltage Detect (HLVD)                              | . 207 |

|       | 12-Bit A/D Converter with Threshold Detect                  |       |

| 20.0  | 8-Bit Digital-to-Analog Converter (DAC)                     | . 229 |

| 21.0  | Dual Operational Amplifier Module                           | . 233 |

| 22.0  | Comparator Module                                           |       |

| 23.0  | Comparator Voltage Reference                                | . 239 |

| 24.0  | Charge Time Measurement Unit (CTMU)                         | . 241 |

| 25.0  | Special Features                                            | . 249 |

| 26.0  | Development Support                                         | . 261 |

| 27.0  | Electrical Characteristics                                  | . 265 |

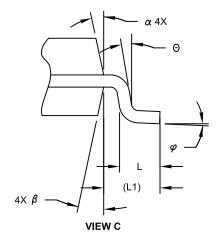

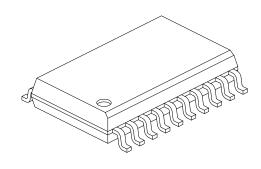

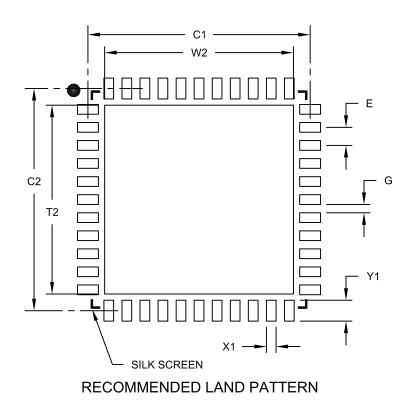

| 28.0  | Packaging Information                                       | . 297 |

| Appe  | ndix A: Revision History                                    | . 325 |

| Index | · · · · · · · · · · · · · · · · · · ·                       | 327   |

|       | /icrochip Web Site                                          |       |

| Custo | omer Change Notification Service                            | . 333 |

| Custo | omer Support                                                | . 333 |

| Produ | uct Identification System                                   | . 335 |

# 4.0 MEMORY ORGANIZATION

As with Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and busing. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 **Program Address Space**

The program address memory space of the PIC24F devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or Data Space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

The user access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

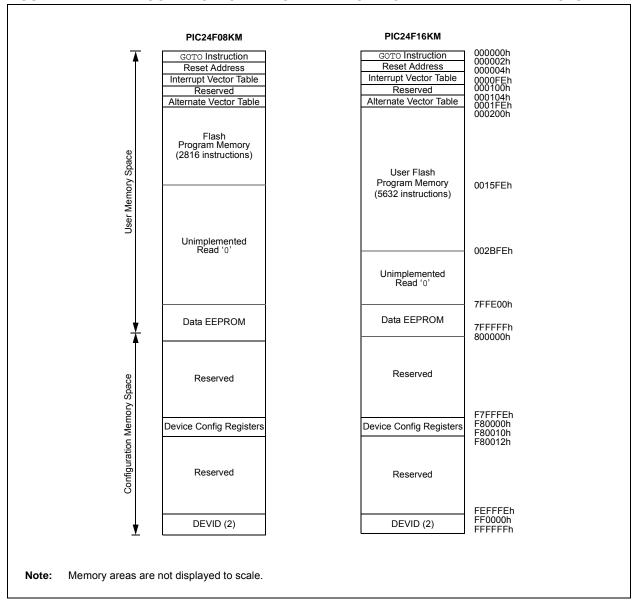

Memory maps for the PIC24FV16KM204 family of devices are displayed in Figure 4-1.

# FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FXXXXX FAMILY DEVICES

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

## TABLE 8-1:TRAP VECTOR DETAILS

## TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS

|                                         |               |             | ΑΙντ    | Int      | errupt Bit Loc | ations       |

|-----------------------------------------|---------------|-------------|---------|----------|----------------|--------------|

| Interrupt Source                        | Vector Number | IVT Address | Address | Flag     | Enable         | Priority     |

| ADC1 – ADC1 Convert Done                | 13            | 00002Eh     | 00012Eh | IFS0<13> | IEC0<13>       | IPC3<6:4>    |

| CLC1                                    | 96            | 0000D4h     | 0001D4h | IFS6<0>  | IEC6<0>        | IPC24<2:0>   |

| CLC2                                    | 97            | 0000D6h     | 0001D6h | IFS6<1>  | IEC6<1>        | IPC24<6:4>   |

| Comparator Interrupt                    | 18            | 000038h     | 000138h | IFS1<2>  | IEC1<2>        | IPC4<10:8>   |

| СТМИ                                    | 77            | 0000AEh     | 0001AEh | IFS4<13> | IEC4<13>       | IPC19<6:4>   |

| DAC1 – Buffer Update                    | 78            | 0000B0h     | 0001B0h | IFS4<14> | IEC4<14>       | IPC19<10:8>  |

| DAC2 – Buffer Update                    | 79            | 0000B2h     | 0001B2h | IFS4<15> | IEC4<15>       | IPC19<14:12> |

| HLVD – High/Low-Voltage Detect          | 72            | 0000A4h     | 0001A4h | IFS4<8>  | IEC4<8>        | IPC18<2:0>   |

| ICN – Input Change Notification         | 19            | 00003Ah     | 00013Ah | IFS1<3>  | IEC1<3>        | IPC4<14:12>  |

| INT0 – External Interrupt 0             | 0             | 000014h     | 000114h | IFS0<0>  | IEC0<0>        | IPC0<2:0>    |

| INT1 – External Interrupt 1             | 20            | 00003Ch     | 00013Ch | IFS1<4>  | IEC1<4>        | IPC5<2:0>    |

| INT2 – External Interrupt 2             | 29            | 00004Eh     | 00014Eh | IFS1<13> | IEC1<13>       | IPC7<6:4>    |

| MCCP1 – Capture/Compare                 | 1             | 000016h     | 000116h | IFS0<1>  | IEC0<1>        | IPC0<6:4>    |

| MCCP1 – Time Base                       | 7             | 000022h     | 000122h | IFS0<7>  | IEC0<7>        | IPC1<14:12>  |

| MCCP2 – Capture/Compare                 | 2             | 000018h     | 000118h | IFS0<2>  | IEC0<2>        | IPC0<10:8>   |

| MCCP2 – Time Base                       | 8             | 000024h     | 000124h | IFS0<8>  | IEC0<8>        | IPC2<2:0>    |

| MCCP3 – Capture/Compare                 | 5             | 00001Eh     | 00011Eh | IFS0<5>  | IEC0<5>        | IPC1<6:4>    |

| MCCP3 – Time Base                       | 27            | 00004Ah     | 00014Ah | IFS1<11> | IEC1<11>       | IPC6<14:12>  |

| MSSP1 – Bus Collision Interrupt         | 17            | 000036h     | 000136h | IFS1<1>  | IEC1<1>        | IPC4<6:4>    |

| MSSP1 – I <sup>2</sup> C™/SPI Interrupt | 16            | 000034h     | 000134h | IFS1<0>  | IEC1<0>        | IPC4<2:0>    |

| MSSP2 – Bus Collision Interrupt         | 50            | 000078h     | 000178h | IFS3<2>  | IEC3<2>        | IPC12<10:8>  |

| MSSP2 – I <sup>2</sup> C/SPI Interrupt  | 49            | 000076h     | 000176h | IFS3<1>  | IEC3<1>        | IPC12<6:4>   |

| NVM – NVM Write Complete                | 15            | 000032h     | 000132h | IFS0<15> | IEC0<15>       | IPC3<14:12>  |

| RTCC – Real-Time Clock/Calendar         | 62            | 000090h     | 000190h | IFS3<14> | IEC3<14>       | IPC15<10:8>  |

| SCCP4 – Capture/Compare                 | 6             | 000020h     | 000120h | IFS0<6>  | IEC0<6>        | IPC1<10:8>   |

| SCCP4 – Time Base                       | 28            | 00004Ch     | 00014Ch | IFS1<12> | IEC1<12>       | IPC7<2:0>    |

| SCCP5 – Capture/Compare                 | 22            | 000040h     | 000140h | IFS1<6>  | IEC1<6>        | IPC5<10:8>   |

| SCCP5 – Time Base                       | 41            | 000066h     | 000166h | IFS2<9>  | IEC2<9>        | IPC10<6:4>   |

| TMR1 – Timer1                           | 3             | 00001Ah     | 00011Ah | IFS0<3>  | IEC0<3>        | IPC0<14:12>  |

| UART1 Error                             | 65            | 000096h     | 000196h | IFS4<1>  | IEC4<1>        | IPC16<6:4>   |

| UART2 Error                             | 66            | 000098h     | 000198h | IFS4<2>  | IEC4<2>        | IPC16<10:8>  |

| UART1RX – UART1 Receiver                | 11            | 00002Ah     | 00012Ah | IFS0<11> | IEC0<11>       | IPC2<14:12>  |

| UART1TX – UART1 Transmitter             | 12            | 00002Ch     | 00012Ch | IFS0<12> | IEC0<12>       | IPC3<2:0>    |

| UART2RX – UART2 Receiver                | 30            | 000050h     | 000150h | IFS1<14> | IEC1<14>       | IPC7<10:8>   |

| UART2TX – UART2 Transmitter             | 31            | 000052h     | 000152h | IFS1<15> | IEC1<15>       | IPC7<14:12>  |

| ULPWU – Ultra Low-Power Wake-up         | 80            | 0000B4h     | 0001B4h | IFS5<0>  | IEC5<0>        | IPC20<2:0>   |

|                       | R/W-1                                                                                     | R/W-0                                                                                                                                          | R/W-0                                                                 | U-0                                         | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------|------------------|-----------------|---------|--|--|--|--|--|

| —                     | U2TXIP2                                                                                   | U2TXIP1                                                                                                                                        | U2TXIP0                                                               |                                             | U2RXIP2          | U2RXIP1         | U2RXIP0 |  |  |  |  |  |

| bit 15                |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 | bit     |  |  |  |  |  |

| U-0                   | R/W-1                                                                                     | R/W-0                                                                                                                                          | R/W-0                                                                 | U-0                                         | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|                       | INT2IP2                                                                                   | INT2IP1                                                                                                                                        | INT2IP0                                                               | _                                           | CCT4IP2          | CCT4IP1         | CCT4IP0 |  |  |  |  |  |

| bit 7                 |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 | bit     |  |  |  |  |  |

|                       |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

| Legend:<br>R = Readat | ole hit                                                                                   | W = Writable                                                                                                                                   | hit                                                                   | II = Unimple                                | mented bit, read | 1 as '0'        |         |  |  |  |  |  |

| -n = Value a          |                                                                                           | '1' = Bit is set                                                                                                                               |                                                                       | '0' = Bit is cle                            |                  | x = Bit is unkr | iown    |  |  |  |  |  |

|                       |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

| bit 15                | Unimplemen                                                                                | ted: Read as 'o                                                                                                                                | )'                                                                    |                                             |                  |                 |         |  |  |  |  |  |

| bit 14-12             |                                                                                           | : UART2 Trans                                                                                                                                  |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

|                       | 111 = Interru                                                                             | pt is Priority 7(                                                                                                                              | highest priority                                                      | interrupt)                                  |                  |                 |         |  |  |  |  |  |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

|                       | 001 = Interru                                                                             | pt is Priority 1<br>pt source is dis                                                                                                           | abled                                                                 |                                             |                  |                 |         |  |  |  |  |  |

| bit 11                |                                                                                           | ted: Read as '                                                                                                                                 |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

| bit 10-8              | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits                                       |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

|                       | 111 = Interrupt is Priority 7 (highest priority interrupt)                                |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

|                       | •<br>001 = Interrupt is Priority 1                                                        |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |  |  |

|                       | 000 = Interru                                                                             | pt source is dis                                                                                                                               | abled                                                                 |                                             |                  |                 |         |  |  |  |  |  |

| bit 7                 | Unimplemen                                                                                | ted: Read as 'o                                                                                                                                | Unimplemented: Read as '0'                                            |                                             |                  |                 |         |  |  |  |  |  |

|                       |                                                                                           |                                                                                                                                                | )'                                                                    |                                             |                  |                 |         |  |  |  |  |  |

| bit 6-4               |                                                                                           | External Interr                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |  |  |  |  |  |

|                       | 111 = Interru                                                                             |                                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |  |  |  |  |  |

|                       |                                                                                           | External Interr                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |  |  |  |  |  |

|                       | 111 = Interru<br>•<br>•                                                                   | External Interr<br>pt is Priority 7(                                                                                                           | upt 2 Priority b                                                      |                                             |                  |                 |         |  |  |  |  |  |

|                       | 111 = Interru<br>•<br>•<br>001 = Interru                                                  | External Interr<br>pt is Priority 7(<br>pt is Priority 1                                                                                       | upt 2 Priority t<br>highest priority                                  |                                             |                  |                 |         |  |  |  |  |  |

| bit 6-4               | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru                                 | External Interr<br>pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                                                                   | upt 2 Priority b<br>highest priority<br>abled                         |                                             |                  |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3      | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                   | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                        | upt 2 Priority b<br>highest priority<br>abled<br>)                    | v interrupt)                                | av hits          |                 |         |  |  |  |  |  |

|                       | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>-: Capture/Com                      | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                        | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>-: Capture/Com                      | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Capture/Com<br>pt is Priority 7 ( | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | ty bits          |                 |         |  |  |  |  |  |

## REGISTER 8-26: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

# 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

**Note:** The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

# 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 25.0** "**Special Features**" for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically, as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT, FSCM or RTCC with LPRC as a clock source is enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

# 10.4 Voltage Regulator-Based Power-Saving Features

The PIC24FV16KM204 family series devices have a voltage regulator that has the ability to alter functionality to provide power savings. The on-chip regulator is made up of two basic modules: the Voltage Regulator (VREG) and the Retention Regulator (RETREG). With the combination of VREG and RETREG, the following power modes are available:

### 10.4.1 RUN MODE

In Run mode, the main VREG is providing a regulated voltage with enough current to supply a device running at full speed and the device is not in Sleep mode. The RETREG may or may not be running, but is unused.

### 10.4.2 SLEEP MODE

In Sleep mode, the device is in Sleep and the main VREG is providing a regulated voltage to the core. By default, in Sleep mode, the regulator enters a low-power standby state which consumes reduced quiescent current. The PMSLP bit (RCON<8>) controls the regulator state in Sleep mode. If the PMSLP bit is set, the program Flash memory will stay powered on during Sleep mode and the regulator will stay in its full-power mode.

# 10.4.3 RETENTION REGULATOR

The Retention Regulator, sometimes referred to as the low-voltage regulator, is designed to provide power to the core at a lower voltage than the standard voltage regulator, while consuming significantly lower quiescent current. Refer to **Section 27.0** "Electrical Characteristics" for the voltage output range of the RETREG. This regulator is only used in Sleep mode, and has limited output current to maintain the RAM and provide power for limited peripherals, such as the WDT, while the device is in Sleep. It is controlled by the RETCFG Configuration bit (FPOR<2>) and in firmware by the RETEN bit (RCON<12>). RETCFG must be programmed (= 0) and the RETEN bit must be set (= 1) for the Retention Regulator to be enabled.

## 10.4.4 RETENTION SLEEP MODE

In Retention Sleep mode, the device is in Sleep and all regulated voltage is provided solely by the RETREG, while the main VREG is disabled. Consequently, this mode provides the lowest Sleep power consumption, but has a trade-off of a longer wake-up time. The low-voltage Sleep wake-up time is longer than Sleep mode due to the extra time required to re-enable the VREG and raise the VDDCORE supply rail back to normal regulated levels.

**Note:** The PIC24F16KM204 family devices do not have any internal voltage regulation, and therefore, do not support Retention Sleep mode.

### TABLE 10-1: VOLTAGE REGULATION CONFIGURATION SETTINGS FOR PIC24FXXXXX FAMILY DEVICES

| RETCFG Bit<br>(FPOR<2>) | RETEN Bit<br>(RCON<12> | PMSLP Bit<br>(RCON<8>) | Power Mode<br>During Sleep | Description                                              |

|-------------------------|------------------------|------------------------|----------------------------|----------------------------------------------------------|

| 0                       | 0                      | 1                      | Sleep                      | VREG mode (normal) is unchanged during Sleep.            |

|                         |                        |                        |                            | RETREG is unused.                                        |

| 0                       | 0                      | 0                      | Sleep                      | VREG goes to Low-Power Standby mode during<br>Sleep.     |

|                         |                        |                        | (Standby)                  | RETREG is unused.                                        |

| 0                       | 1                      | 0                      | Retention                  | VREG is off during Sleep.                                |

|                         |                        |                        | Sleep                      | RETREG is enabled and provides Sleep voltage regulation. |

| 1                       | x                      | 1                      | Sleep                      | VREG mode (normal) is unchanged during Sleep.            |

|                         |                        |                        |                            | RETREG is disabled at all times.                         |

| 1                       | х                      | 0                      | Sleep                      | VREG goes to Low-Power Standby mode during Sleep.        |

|                         |                        |                        | (Standby)                  | RETREG is disabled at all times.                         |

## 10.5 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption. Meanwhile, the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

## 10.6 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMDx Control registers.

Both bits have similar functions in enabling or disabling its associated module. Setting the PMDx bits for a module, disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect, and read values will be invalid. Many peripheral modules have a corresponding PMDx bit.

In contrast, disabling a module by clearing its XXXEN bit, disables its functionality, but leaves its registers available to be read and written to. Power consumption is reduced, but not by as much as when the PMDx bits are used. Most peripheral modules have an enable bit; exceptions include capture, compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature disables the module while in Idle mode, allowing further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

### REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS (CONTINUED)

bit 3-0 MOD<3:0>: CCPx Mode Select bits

For CCSEL = 1 (Input Capture modes):

- 1xxx = Reserved

- 011x = Reserved

- 0101 = Capture every 16th rising edge

- 0100 = Capture every 4th rising edge

- 0011 = Capture every rising and falling edge

- 0010 = Capture every falling edge

- 0001 = Capture every rising edge

- 0000 = Capture every rising and falling edge (Edge Detect mode)

- For CCSEL = 0 (Output Compare/Timer modes):

- 1111 = External Input mode: Pulse generator is disabled, source is selected by ICS<2:0>

- 1110 = Reserved

- 110x = Reserved

- 10xx = Reserved

- 0111 = Variable Frequency Pulse mode

- 0110 = Center-Aligned Pulse Compare mode, buffered

- 0101 = Dual Edge Compare mode, buffered

- 0100 = Dual Edge Compare mode

- 0011 = 16-Bit/32-Bit Single Edge mode, toggle output on compare match

- 0010 = 16-Bit/32-Bit Single Edge mode, drive output low on compare match

- 0001 = 16-Bit/32-Bit Single Edge mode, drive output high on compare match

- 0000 = 16-Bit/32-Bit Timer mode, output functions are disabled

- **Note 1:** Clock options are limited in some operating modes. See Table 13-1 for restrictions.

# 19.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR)

Conversion

- Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (internal and external)

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H)

Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU, and a configurable results buffer. There is a legacy 10-bit mode on this A/D to allow the option to run with lower resolution in order to obtain higher throughput. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 19-1.

| R/W-0         | U-0                                                                                                                                                  | R/W-0                                                                                                                                                                                         | U-0                                                                                                                                                                                          | U-0                                                                                                                                                                                 | R/W-0                                                                                                                                                  | R/W-0                                                          | R/W-0      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|

| ADON          |                                                                                                                                                      | ADSIDL                                                                                                                                                                                        |                                                                                                                                                                                              |                                                                                                                                                                                     | MODE12                                                                                                                                                 | FORM1                                                          | FORM0      |

| bit 15        |                                                                                                                                                      |                                                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                     |                                                                                                                                                        |                                                                | bit        |

|               |                                                                                                                                                      |                                                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

| R/W-0         | R/W-0                                                                                                                                                | R/W-0                                                                                                                                                                                         | R/W-0                                                                                                                                                                                        | U-0                                                                                                                                                                                 | R/W-0                                                                                                                                                  | R/W-0, HSC                                                     | R/C-0, HSC |

| SSRC3         | SSRC2                                                                                                                                                | SSRC1                                                                                                                                                                                         | SSRC0                                                                                                                                                                                        |                                                                                                                                                                                     | ASAM                                                                                                                                                   | SAMP                                                           | DONE       |

| bit 7         |                                                                                                                                                      |                                                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                     |                                                                                                                                                        |                                                                | bit        |

| Legend:       |                                                                                                                                                      | C = Clearable                                                                                                                                                                                 | bit                                                                                                                                                                                          | U = Unimplei                                                                                                                                                                        | mented bit, read                                                                                                                                       | d as '0'                                                       |            |

| R = Readable  | e bit                                                                                                                                                | W = Writable                                                                                                                                                                                  | bit                                                                                                                                                                                          | HSC = Hardy                                                                                                                                                                         | ware Settable/C                                                                                                                                        | learable bit                                                   |            |

| -n = Value at | POR                                                                                                                                                  | '1' = Bit is set                                                                                                                                                                              |                                                                                                                                                                                              | '0' = Bit is cle                                                                                                                                                                    | ared                                                                                                                                                   | x = Bit is unkn                                                | iown       |

| bit 15        |                                                                                                                                                      | Operating Mode<br>verter is operat<br>verter is off                                                                                                                                           |                                                                                                                                                                                              |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

| bit 14        | Unimplemen                                                                                                                                           | ted: Read as '                                                                                                                                                                                | )'                                                                                                                                                                                           |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

| bit 13        | ADSIDL: A/D                                                                                                                                          | Stop in Idle Mo                                                                                                                                                                               | ode bit                                                                                                                                                                                      |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

|               |                                                                                                                                                      | ues module op<br>s module opera                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                     | dle mode                                                                                                                                               |                                                                |            |

| bit 12-11     | Unimplemen                                                                                                                                           | ted: Read as '                                                                                                                                                                                | )'                                                                                                                                                                                           |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

| bit 10        | MODE12: 12-                                                                                                                                          | Bit A/D Operat                                                                                                                                                                                | ion Mode bit                                                                                                                                                                                 |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

|               | 1 = 12-bit A/[<br>0 = 10-bit A/[                                                                                                                     |                                                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

| bit 9-8       | FORM<1:0>:                                                                                                                                           | Data Output F                                                                                                                                                                                 | ormat bits (see                                                                                                                                                                              | e the following                                                                                                                                                                     | formats)                                                                                                                                               |                                                                |            |

|               | 10 = Absolute<br>01 = Decimal                                                                                                                        | al result, signe<br>e fractional resu<br>result, signed,<br>e decimal resul                                                                                                                   | IIt, unsigned, I<br>right justified                                                                                                                                                          | -                                                                                                                                                                                   |                                                                                                                                                        |                                                                |            |

| bit 7-4       | SSRC<3:0>:                                                                                                                                           | Sample Clock                                                                                                                                                                                  | Source Select                                                                                                                                                                                | bits                                                                                                                                                                                |                                                                                                                                                        |                                                                |            |

|               | 1111 = Rese                                                                                                                                          | rved                                                                                                                                                                                          |                                                                                                                                                                                              |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

|               | •                                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

|               | •                                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                     |                                                                                                                                                        |                                                                |            |

|               | 1011 = SCCF<br>1010 = MCCI<br>1001 = MCCI<br>1000 = CLC1<br>0111 = Intern<br>0110 = TMR1<br>0101 = TMR1<br>0100 = CTML<br>0011 = SCCF<br>0010 = MCCI | event ends sa<br>P4 Compare Ev<br>P3 Compare Ev<br>P2 Compare Ev<br>event ends sa<br>la counter ends<br>l Sleep mode T<br>l event ends sa<br>P5 Compare Ev<br>P1 Compare Ev<br>event ends sar | ent (CCP4IF)<br>vent (CCP3IF)<br>vent (CCP2IF)<br>mpling and sta<br>s sampling and<br>rigger event e<br>impling and st<br>ampling and st<br>rent (CCP5IF)<br>vent (CCP1IF)<br>npling and sta | ends sampling<br>ends sampling<br>arts conversion<br>d starts conversion<br>arts conversion<br>arts conversion<br>ends sampling<br>ends sampling<br>ends sampling<br>rts conversion | and starts con<br>and starts con<br>sion (auto-conv<br>and starts conven<br>and starts conven<br>and starts conven<br>and starts con<br>and starts con | version<br>version<br>ert)<br>ersion <sup>(1)</sup><br>version |            |

### REGISTER 19-1: AD1CON1: A/DA/D CONTROL REGISTER 1

**Note 1:** This version of the TMR1 Trigger allows A/D conversions to be triggered from TMR1 while the device is operating in Sleep mode. The SSRC<3:0> = 0101 option allows conversions to be triggered in Run or Idle modes only.

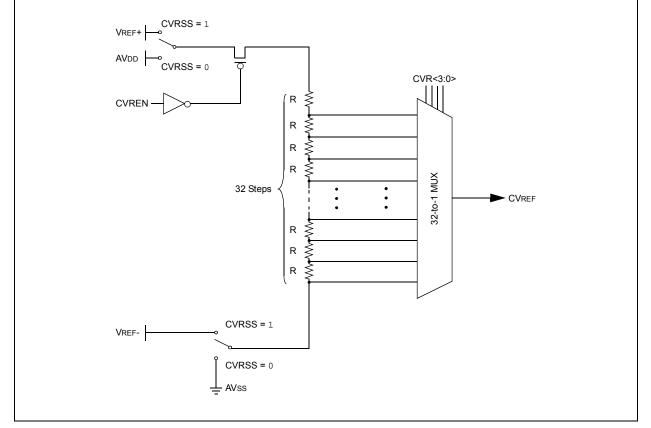

# 23.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator Voltage Reference, refer to the "PIC24F Family Reference Manual", "Comparator Voltage Reference Module" (DS39709).

# 23.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 23-1). The comparator voltage reference provides a range of output voltages with 32 distinct levels.

The comparator voltage reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

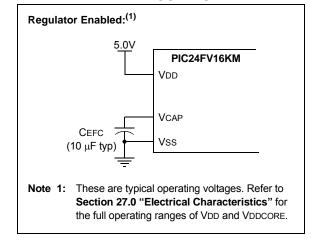

# 25.2 On-Chip Voltage Regulator

All of the PIC24FXXXXX family devices power their core digital logic at a nominal 3.0V. This may create an issue for designs that are required to operate at a higher typical voltage, as high as 5.0V. To simplify system design, all devices in the "FV" family incorporate an on-chip regulator that allows the device core to run at 3.0V, while the I/O is powered by VDD at a higher voltage.

The regulator is always enabled and provides power to the core from the other VDD pins. A low-ESR capacitor (such as ceramic) must be connected to the VCAP pin (Figure 25-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 27.1 "DC Characteristics"** and discussed in detail in **Section 2.0 "Guidelines for Getting Started with 16-Bit Microcontrollers"**.

In all of the "F" family of devices, the regulator is disabled. Instead, the core logic is directly powered from VDD. "F" devices operate at a lower range of VDD voltage, from 1.8V-3.6V.

#### 25.2.1 VOLTAGE REGULATOR TRACKING MODE AND LOW-VOLTAGE DETECTION

For all PIC24FXXXXX devices, the on-chip regulator provides a constant voltage of 3.0V nominal to the digital core logic. The regulator can provide this level from a VDD of about 3.2V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels below 3.2V. In order to prevent "brown out" conditions when the voltage drops too low for the regulator, the regulator enters Tracking mode. In Tracking mode, the regulator output follows VDD with a typical voltage drop of 150 mV.

When the device enters Tracking mode, it is no longer possible to operate at full speed. To provide information about when the device enters Tracking mode, the on-chip High/Low-Voltage Detect (HLVD) module can be used. The HLVD trip point should be configured so that if VDD drops close to the minimum voltage for the operating frequency of the device, the HLVD Interrupt Flag, HLVDIF (IFS4<8>), will occur. This can be used to generate an interrupt and put the application into a low-power operational mode or trigger an orderly shutdown. Refer to **Section 27.1 "DC Characteristics"** for the specifications detailing the maximum operating speed based on the applied VDD voltage.

# FIGURE 25-1:

#### CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR

# 25.2.2 VOLTAGE REGULATOR START-UP TIME

For PIC24FXXXX family devices, it takes a short time, designated as TPM, for the regulator to generate a stable output. During this time, code execution is disabled. TPM is applied every time the device resumes operation after any power-down, including Sleep mode. TPM is specified in Section 27.2 "AC Characteristics and Timing Parameters".

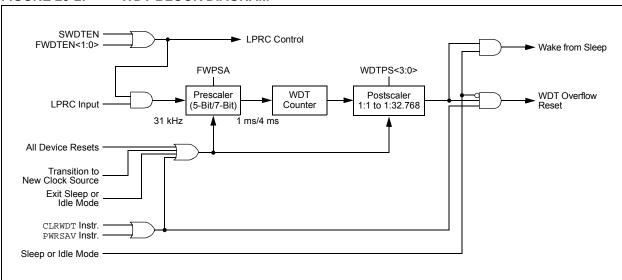

# 25.3 Watchdog Timer (WDT)

For the PIC24FXXXXX family of devices, the WDT is driven by the LPRC Oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT Time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the Configuration bits, WDTPS<3:0> (FWDT<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranges from 1 ms to 131 seconds can be achieved.