Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km202-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-10: MCCP3 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14                                                                                         | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9   | Bit 8       | Bit 7        | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------------------|-------|---------|------------------------------------------------------------------------------------------------|---------|--------|---------|---------|---------|-------------|--------------|--------------|---------|---------|---------|---------|---------|---------|---------------|

| CCP3CON1L <sup>(1)</sup> | 188h  | CCPON   | _                                                                                              | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1 | CLKSEL0     | TMRPS1       | TMRPS0       | T32     | CCSEL   | MOD3    | MOD2    | MOD1    | MOD0    | 0000          |

| CCP3CON1H <sup>(1)</sup> | 18Ah  | OPSSRC  | RTRGEN                                                                                         | _       | _      | IOPS3   | IOPS2   | IOPS1   | IOPS0       | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1   | SYNC0   | 0000          |

| CCP3CON2L <sup>(1)</sup> | 18Ch  | PWMRSEN | ASDGM <u>-</u> SSDG <u>-</u> <u>-</u> <u>-</u> ASDG7 ASDG6 ASDG5 ASDG4 ASDG3 ASDG2 ASDG1 ASDG0 |         |        |         |         |         |             |              |              |         | 0000    |         |         |         |         |               |

| CCP3CON2H <sup>(1)</sup> | 18Eh  | OENSYNC | _                                                                                              | OCFEN   | OCEEN  | OCDEN   | OCCEN   | OCBEN   | OCAEN       | ICGSM1       | ICGSM0       | _       | AUXOUT1 | AUXOUT0 | ICS2    | ICS1    | ICS0    | 0100          |

| CCP3CON3L <sup>(1)</sup> | 190h  | _       | _                                                                                              | _       | _      | _       | _       | _       | _           | _            | _            | DT5     | DT4     | DT3     | DT2     | DT1     | DT0     | 0000          |

| CCP3CON3H <sup>(1)</sup> | 192h  | OETRIG  | OSCNT2                                                                                         | OSCNT1  | OSCNT0 | _       | OUTM2   | OUTM1   | OUTM0       | _            | _            | POLACE  | POLBDF  | PSSACE1 | PSSACE0 | PSSBDF1 | PSSBDF0 | 0000          |

| CCP3STAT <sup>(1)</sup>  | 194h  | _       | _                                                                                              | _       | —      | _       | _       | _       | _           | CCPTRIG      | TRSET        | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV    | ICBNE   | 0000          |

| CCP3TMRL <sup>(1)</sup>  | 198h  |         |                                                                                                |         |        |         |         | MCCF    | P3 Time Bas | se Register  | Low Word     |         |         |         |         | •       | •       | 0000          |

| CCP3TMRH <sup>(1)</sup>  | 19Ah  |         |                                                                                                |         |        |         |         | MCCF    | 3 Time Bas  | e Register   | High Word    |         |         |         |         |         |         | 0000          |

| CCP3PRL <sup>(1)</sup>   | 19Ch  |         |                                                                                                |         |        |         |         | MCCP3 1 | īme Base F  | Period Regis | ster Low Wor | d       |         |         |         |         |         | FFFF          |

| CCP3PRH <sup>(1)</sup>   | 19Eh  |         |                                                                                                |         |        |         |         | МССРЗ Т | ime Base P  | eriod Regis  | ter High Wor | d       |         |         |         |         |         | FFFF          |

| CCP3RAL <sup>(1)</sup>   | 1A0h  |         |                                                                                                |         |        |         |         | Οι      | tput Compa  | are 3 Data \ | Word A       |         |         |         |         |         |         | 0000          |

| CCP3RBL <sup>(1)</sup>   | 1A4h  |         | Output Compare 3 Data Word B                                                                   |         |        |         |         |         |             |              | 0000         |         |         |         |         |         |         |               |

| CCP3BUFL <sup>(1)</sup>  | 1A8h  |         | Input Capture 3 Data Buffer Low Word                                                           |         |        |         |         |         |             |              | 0000         |         |         |         |         |         |         |               |

| CCP3BUFH <sup>(1)</sup>  | 1AAh  |         | Input Capture 3 Data Buffer High Word                                                          |         |        |         |         |         |             |              | 0000         |         |         |         |         |         |         |               |

$\label{eq:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:loge$

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-15: UART1 REGISTER MAP

|           |       | •        |                                  |          |        |        |        |       |       |          |          |           |             |       |        |        |       |               |

|-----------|-------|----------|----------------------------------|----------|--------|--------|--------|-------|-------|----------|----------|-----------|-------------|-------|--------|--------|-------|---------------|

| File Name | Addr. | Bit 15   | Bit 14                           | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE    | 220h  | UARTEN   | —                                | USIDL    | IREN   | RTSMD  | -      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD     | URXINV      | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA     | 222h  | UTXISEL1 | UTXINV                           | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN     | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG   | 224h  | _        | _                                | _        | _      | _      | _      | _     |       |          |          | UART1 Tra | ansmit Regi | ster  |        |        |       | xxxx          |

| U1RXREG   | 226h  | —        | UART1 Receive Register 0         |          |        |        |        |       |       | 0000     |          |           |             |       |        |        |       |               |

| U1BRG     | 228h  |          | Baud Rate Generator Prescaler 00 |          |        |        |        |       |       | 0000     |          |           |             |       |        |        |       |               |

|           |       |          |                                  |          |        |        |        |       |       |          |          |           |             |       |        |        |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-16: UART2 REGISTER MAP

| File Name              | Addr. | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|------------------------|-------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|----------|----------|-----------|-------------|-------|--------|--------|-------|---------------|

| U2MODE <sup>(1)</sup>  | 230h  | UARTEN   | —                             | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD     | URXINV      | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA <sup>(1)</sup>   | 232h  | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN     | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG <sup>(1)</sup> | 234h  | _        | _                             | _        | —      | _      | _      | _     |       |          |          | UART2 Tra | nsmit Regis | ster  |        |        |       | xxxx          |

| U2RXREG <sup>(1)</sup> | 236h  | _        | _                             | _        | —      | _      | _      | _     |       |          |          | UART2 Re  | ceive Regis | ter   |        |        |       | 0000          |

| U2BRG <sup>(1)</sup>   | 238h  |          | Baud Rate Generator Prescaler |          |        |        |        |       |       | 0000     |          |           |             |       |        |        |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

### 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Flash programming, refer to the "PIC24F Family Reference Manual", "Program Memory" (DS39715).

The PIC24FV16KM204 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FXXXXX device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program Mode Entry Voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self-Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

### 5.1 Table Instructions and Flash Programming

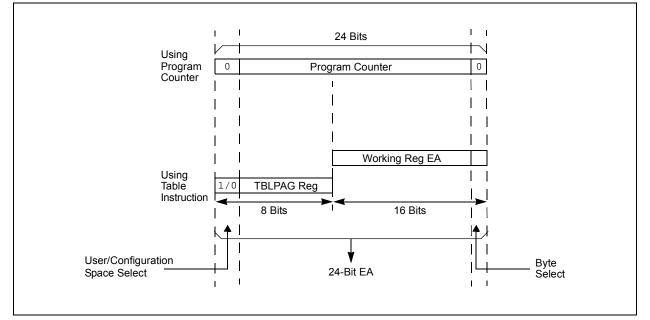

Regardless of the method used, Flash memory programming is done with the Table Read and Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### 7.4.2 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when the BOR is under software con-   |

|-------|--------------------------------------------|

|       | trol, the Brown-out Reset voltage level is |

|       | still set by the BORV<1:0> Configuration   |

|       | bits; it can not be changed in software.   |

#### 7.4.3 DETECTING BOR

When BOR is enabled, the BOR bit (RCON<1>) is always reset to '1' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR and BOR bits are reset to '0' in the software immediately after any POR event. If the BOR bit is '1' while POR is '0', it can be reliably assumed that a BOR event has occurred.

#### 7.4.4 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, BOR remains under hardware control and operates as previously described. However, whenever the device enters Sleep mode, BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

Note: BOR levels differ depending on device type; PIC24FV16KM204 devices are at different levels than those of PIC24F16KM204 devices. See Section 27.0 "Electrical Characteristics" for BOR voltage levels.

#### U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 CNIP2 CNIP1 CNIP0 CMIP2 CMIP1 CMIP0 bit 15 bit 8 U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 BCL1IP2 BCL1IP1 BCL1IP0 SSP1IP2 SSP1IP1 SSP1IP0 \_\_\_\_ \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 Unimplemented: Read as '0' bit 14-12 CNIP<2:0>: Input Change Notification Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 11 Unimplemented: Read as '0' bit 10-8 CMIP<2:0>: Comparator Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled Unimplemented: Read as '0' bit 7 BCL1IP<2:0>: MSSP1 I<sup>2</sup>C<sup>™</sup> Bus Collision Interrupt Priority bits bit 6-4 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 3 Unimplemented: Read as '0' bit 2-0 **SSP1IP<2:0>:** MSSP1 SPI/I<sup>2</sup>C Event Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled

#### REGISTER 8-23: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

#### REGISTER 8-33: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0           | U-0        | U-0              | U-0          | U-0               | U-0              | U-0             | U-0      |

|---------------|------------|------------------|--------------|-------------------|------------------|-----------------|----------|

| —             | —          | —                | —            | —                 | —                | —               | —        |

| bit 15        |            |                  |              |                   |                  |                 | bit 8    |

|               |            |                  |              |                   |                  |                 |          |

| U-0           | U-0        | U-0              | U-0          | U-0               | R/W-1            | R/W-0           | R/W-0    |

| _             | _          | _                | _            | —                 | ULPWUIP2         | ULPWUIP1        | ULPWUIP0 |

| bit 7         |            |                  |              |                   |                  |                 | bit 0    |

| Legend:       |            |                  |              |                   |                  |                 |          |

| R = Readable  | e bit      | W = Writable     | bit          | U = Unimplem      | nented bit, read | l as '0'        |          |

| -n = Value at | POR        | '1' = Bit is set |              | '0' = Bit is clea | ared             | x = Bit is unkr | iown     |

|               |            |                  |              |                   |                  |                 |          |

| bit 15-3      | Unimplemer | ted: Read as '0  | )'           |                   |                  |                 |          |

| bit 2-0       | ULPWUIP<2  | :0>: Ultra Low-F | Power Wake-u | p Interrupt Prior | rity bits        |                 |          |

111 = Interrupt is Priority 7 (highest priority interrupt)

- •

- 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 8-34: IPC24: INTERRUPT PRIORITY CONTROL REGISTER 24

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | CLC2IP2 | CLC2IP1 | CLC2IP0 | —   | CLC1IP2 | CLC1IP1 | CLC1IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 6-4  | CLC2IP<2:0>: CLC2 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

| bit 3    | Unimplemented: Read as '0'                                 |

| bit 2-0  | CLC1IP<2:0>: CLC1 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

|          |                                                            |

#### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24FXXXXX family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator:

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The Primary Oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

#### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 25.1 "Configuration Bits"). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                      | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|------------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler<br>(LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                       | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)                 | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)      | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)      | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                              | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                              | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                              | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 15.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated 16-bit Baud Rate Generator (BRG). The UxBRG register controls the period of a free-running, 16-bit timer. Equation 15-1 provides the formula for computation of the baud rate with BRGH = 0.

### EQUATION 15-1: UARTX BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$   $UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$ Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 15-1 provides the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 15-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 15-2: UARTx BAUD RATE WITH BRGH = $1^{(1)}$

|      | Ba | ud Rate = | $\frac{FCY}{4 \bullet (UxBRG + 1)}$ |          |

|------|----|-----------|-------------------------------------|----------|

|      | Ux | BRG =     | FCY<br>4 • Baud Rate                | - 1      |

| Note | 1: |           | n Fcy = Fosc/2; D<br>are disabled.  | oze mode |

The maximum baud rate (BRGH = 1) possible is FcY/4 (for UxBRG = 0) and the minimum baud rate possible is FcY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

#### EXAMPLE 15-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate    | =   | FCY/(16 (UxBRG + 1))                                                                  |

|----------------------|-----|---------------------------------------------------------------------------------------|

| Solving for UxBRG va | lue | :                                                                                     |

| UxBRG<br>UxBRG       | =   | ((FCY/Desired Baud Rate)/16) – 1<br>((4000000/9600)/16) – 1                           |

| UxBRG                |     | 25                                                                                    |

| Calculated Baud Rate |     | 4000000/(16 (25 + 1))<br>9615                                                         |

| Error                |     | (Calculated Baud Rate – Desired Baud Rate)<br>Desired Baud Rate<br>(9615 – 9600)/9600 |

|                      | =   | 0.16%                                                                                 |

| Note 1: Based on     | Fc  | Y = FOSC/2; Doze mode and PLL are disabled.                                           |

#### REGISTER 15-3: UXTXREG: UARTX TRANSMIT REGISTER

| U-x    | U-x | U-x | U-x | U-x | U-x | U-x | W-x   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | _   | —   | UTX8  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-x   | W-x  | W-x  | W-x  | W-x  | W-x  | W-x  | W-x   |

|-------|------|------|------|------|------|------|-------|

| UTX7  | UTX6 | UTX5 | UTX4 | UTX3 | UTX2 | UTX1 | UTX0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

bit 8 **UTX8:** Data of the Transmitted Character bit (in 9-bit mode)

bit 7-0 UTX<7:0>: Data of the Transmitted Character bits

#### REGISTER 15-4: UxRXREG: UARTx RECEIVE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC |

|--------|-----|-----|-----|-----|-----|-----|----------|

| —      | —   | —   | —   | —   | —   | _   | URX8     |

| bit 15 |     |     |     |     |     |     | bit 8    |

| R-0, HSC |

|----------|----------|----------|----------|----------|----------|----------|----------|

| URX7     | URX6     | URX5     | URX4     | URX3     | URX2     | URX1     | URX0     |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/ | Clearable bit             |                    |

|-------------------|--------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared      | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

bit 8 URX8: Data of the Received Character bit (in 9-bit mode)

bit 7-0 URX<7:0>: Data of the Received Character bits

| REGISTER 16-2: | RTCPWC: RTCC CONFIGURATION REGISTER 2 <sup>(1)</sup> |

|----------------|------------------------------------------------------|

|                |                                                      |

| R/W-0      | R/W-0                                                                                               | R/W-0                                                                    | R/W-0                        | R/W-0                         | R/W-0                  | R/W-0           | R/W-0         |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------|-------------------------------|------------------------|-----------------|---------------|--|--|--|--|

| PWCEN      | PWCPOL                                                                                              | PWCCPRE                                                                  | PWCSPRE                      | RTCCLK1 <sup>(2)</sup>        | RTCCLK0 <sup>(2)</sup> | RTCOUT1         | RTCOUT0       |  |  |  |  |

| bit 15     |                                                                                                     |                                                                          |                              |                               |                        |                 | bit 8         |  |  |  |  |

|            |                                                                                                     |                                                                          |                              |                               |                        |                 |               |  |  |  |  |

| U-0        | U-0                                                                                                 | U-0                                                                      | U-0                          | U-0                           | U-0                    | U-0             | U-0           |  |  |  |  |

|            | —                                                                                                   |                                                                          |                              | _                             | —                      |                 |               |  |  |  |  |

| bit 7      |                                                                                                     |                                                                          |                              |                               |                        |                 | bit (         |  |  |  |  |

| Legend:    |                                                                                                     |                                                                          |                              |                               |                        |                 |               |  |  |  |  |

| R = Reada  | able bit                                                                                            | W = Writable                                                             | bit                          | U = Unimpleme                 | nted bit, read as      | '0'             |               |  |  |  |  |

| -n = Value | at POR                                                                                              | '1' = Bit is set                                                         |                              | '0' = Bit is cleare           | ed                     | x = Bit is unkr | nown          |  |  |  |  |

|            |                                                                                                     |                                                                          |                              |                               |                        |                 |               |  |  |  |  |

| bit 15     | PWCEN: Po                                                                                           | wer Control Er                                                           | able bit                     |                               |                        |                 |               |  |  |  |  |

|            |                                                                                                     | ontrol is enable                                                         |                              |                               |                        |                 |               |  |  |  |  |

|            |                                                                                                     | ontrol is disable                                                        |                              |                               |                        |                 |               |  |  |  |  |

| bit 14     |                                                                                                     | PWCPOL: Power Control Polarity bit                                       |                              |                               |                        |                 |               |  |  |  |  |

|            | <ol> <li>Power control output is active-high</li> <li>Power control output is active-low</li> </ol> |                                                                          |                              |                               |                        |                 |               |  |  |  |  |

| bit 13     |                                                                                                     | Power Control                                                            |                              | caler hits                    |                        |                 |               |  |  |  |  |

|            |                                                                                                     |                                                                          | •                            | by-2 of source R <sup>-</sup> | TCC clock              |                 |               |  |  |  |  |

|            |                                                                                                     |                                                                          |                              | by-1 of source R              |                        |                 |               |  |  |  |  |

| bit 12     | PWCSPRE:                                                                                            | Power Control                                                            | Sample Pres                  | caler bits                    |                        |                 |               |  |  |  |  |

|            |                                                                                                     |                                                                          |                              | by-2 of source RT             |                        |                 |               |  |  |  |  |

| bit 11-10  | RTCCLK<1:                                                                                           | 0>: RTCC Clo                                                             | ck Select bits <sup>(2</sup> | 2)                            |                        |                 |               |  |  |  |  |

|            |                                                                                                     |                                                                          |                              | CC clock, which i             | s used for all RT      | CC timer opera  | ations.       |  |  |  |  |

|            |                                                                                                     | 00 = External Secondary Oscillator (SOSC)                                |                              |                               |                        |                 |               |  |  |  |  |

|            |                                                                                                     | 01 = Internal LPRC Oscillator<br>10 = External power line source – 50 Hz |                              |                               |                        |                 |               |  |  |  |  |

|            |                                                                                                     | al power line so                                                         |                              |                               |                        |                 |               |  |  |  |  |

| bit 9-8    | RTCOUT<1:                                                                                           | : <b>0&gt;:</b> RTCC Out                                                 | put Select bits              | 5                             |                        |                 |               |  |  |  |  |

|            |                                                                                                     | the source of th                                                         | ne RTCC pin c                | output.                       |                        |                 |               |  |  |  |  |

|            | 00 = RTCC a                                                                                         | •                                                                        |                              |                               |                        |                 |               |  |  |  |  |

|            | 01 = RTCC                                                                                           | seconds clock                                                            |                              |                               |                        |                 |               |  |  |  |  |

|            | 11 = Power                                                                                          |                                                                          |                              |                               |                        |                 |               |  |  |  |  |

| bit 7-0    | Unimpleme                                                                                           | nted: Read as                                                            | '0'                          |                               |                        |                 |               |  |  |  |  |

| Note 1:    | The RTCPWC                                                                                          | register is only                                                         | affected by a                | POR                           |                        |                 |               |  |  |  |  |

|            |                                                                                                     |                                                                          | -                            | r bits the Secon              | da Valua ragistar      | should also be  | o urritton to |  |  |  |  |

2: When a new value is written to these register bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

| FIGURE 16-2:                 | ALARM MASK SE            | ITINGS                |                |     |       |         |         |

|------------------------------|--------------------------|-----------------------|----------------|-----|-------|---------|---------|

| Alarm Mas<br>(AMASK          | k Setting<br><<3:0>)     | Day of<br>the<br>Week | Month          | Day | Hours | Minutes | Seconds |

| 0000 - Every<br>0001 - Every |                          |                       |                |     |       |         |         |

| 0010 - Every                 | 10 seconds               |                       |                |     |       |         | s       |

| 0011 - Every                 | minute                   |                       |                |     |       |         | S S     |

| 0100 - Every                 | 10 minutes               |                       |                |     |       | m       | SS      |

| 0101 - Every                 | hour                     |                       |                |     |       | m m :   | SS      |

| 0110 - Every                 | day                      |                       |                |     | h h : | m m :   | s s     |

| 0111 - Every                 | week                     | d                     |                |     | h h : | m m :   | s s     |

| 1000 - Every                 | month                    |                       |                | b   | h h : | m m :   | s s     |

| 1001 - Every                 | year <sup>(1)</sup>      |                       | m m / 0        | b   | h h : | m m :   | s s     |

| Note 1: A                    | nnually, except when cor | ifigured for          | r February 29. |     |       |         |         |

#### 16.5 Power Control

The RTCC includes a power control feature that allows the device to periodically wake-up an external device, wait for the device to be stable before sampling wake-up events from that device and then shut down the external device. This can be done completely autonomously by the RTCC, without the need to wake from the current low-power mode (Sleep, Deep Sleep, etc.).

To enable this feature, the RTCC must be enabled (RTCEN = 1), the PWCEN register bit must be set and the RTCC pin must be driving the PWC control signal (RTCOE = 1 and RTCCLK<1:0> = 11).

The polarity of the PWC control signal may be chosen using the PWCPOL register bit. Active-low or active-high may be used with the appropriate external switch to turn on or off the power to one or more external devices. The active-low setting may also be used in conjunction with an open-drain setting on the RTCC pin. This setting is able to drive the GND pin(s) of the external device directly (with the appropriate external VDD pull-up device), without the need for external switches. Finally, the CHIME bit should be set to enable the PWC periodicity.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 G2D4T G2D4N G2D3T G2D3N G2D2T G2D2N G2D1T G2D1N bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 G1D4T G1D2N G1D4N G1D3T G1D3N G1D2T G1D1T G1D1N bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared x = Bit is unknown '1' = Bit is set bit 15 G2D4T: Gate 2 Data Source 4 True Enable bit 1 = The Data Source 4 inverted signal is enabled for Gate 2 0 = The Data Source 4 inverted signal is disabled for Gate 2 bit 14 G2D4N: Gate 2 Data Source 4 Negated Enable bit 1 = The Data Source 4 inverted signal is enabled for Gate 2 0 = The Data Source 4 inverted signal is disabled for Gate 2 bit 13 G2D3T: Gate 2 Data Source 3 True Enable bit 1 = The Data Source 3 inverted signal is enabled for Gate 2 0 = The Data Source 3 inverted signal is disabled for Gate 2 bit 12 G2D3N: Gate 2 Data Source 3 Negated Enable bit 1 = The Data Source 3 inverted signal is enabled for Gate 2 0 = The Data Source 3 inverted signal is disabled for Gate 2 bit 11 G2D2T: Gate 2 Data Source 2 True Enable bit 1 = The Data Source 2 inverted signal is enabled for Gate 2 0 = The Data Source 2 inverted signal is disabled for Gate 2 bit 10 G2D2N: Gate 2 Data Source 2 Negated Enable bit 1 = The Data Source 2 inverted signal is enabled for Gate 2 0 = The Data Source 2 inverted signal is disabled for Gate 2 bit 9 G2D1T: Gate 2 Data Source 1 True Enable bit 1 = The Data Source 1 inverted signal is enabled for Gate 2 0 = The Data Source 1 inverted signal is disabled for Gate 2 bit 8 G2D1N: Gate 2 Data Source 1 Negated Enable bit 1 = The Data Source 2 inverted signal is enabled for Gate 1 0 = The Data Source 2 inverted signal is disabled for Gate 1 bit 7 G1D4T: Gate 1 Data Source 4 True Enable bit 1 = The Data Source 4 inverted signal is enabled for Gate 1 0 = The Data Source 4 inverted signal is disabled for Gate 1 bit 6 G1D4N: Gate 1 Data Source 4 Negated Enable bit 1 = The Data Source 4 inverted signal is enabled for Gate 1 0 = The Data Source 4 inverted signal is disabled for Gate 1 G1D3T: Gate 1 Data Source 3 True Enable bit bit 5 1 = The Data Source 3 inverted signal is enabled for Gate 1 0 = The Data Source 3 inverted signal is disabled for Gate 1 bit 4 G1D3N: Gate 1 Data Source 3 Negated Enable bit 1 = The Data Source 3 inverted signal is enabled for Gate 1 0 = The Data Source 3 inverted signal is disabled for Gate 1

### 24.3 Pulse Generation and Delay

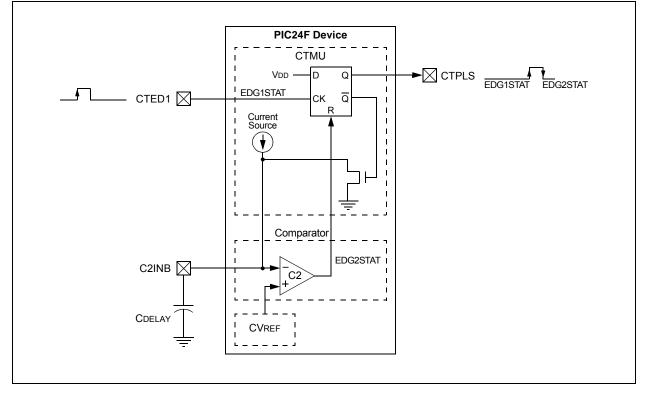

The CTMU module can also generate an output pulse with edges that are not synchronous with the device's system clock. More specifically, it can generate a pulse with a programmable delay from an edge event input to the module.

When the module is configured for pulse generation delay by setting the TGEN bit (CTMUCON1L<12>), the internal current source is connected to the B input of Comparator 2. A Capacitor (CDELAY) is connected to the Comparator 2 pin, C2INB, and the Comparator Voltage Reference, CVREF, is connected to C2INA. CVREF is then configured for a specific trip point. The module begins to charge CDELAY when an edge event is detected. While CVREF is greater than the voltage on CDELAY, the CTPLS pin is high.

When the voltage on CDELAY equals CVREF, CTPLS goes low. With Comparator 2 configured as the second edge, this stops the CTMU from charging. In this state event, the CTMU automatically connects to ground. The IDISSEN bit doesn't need to be set and cleared before the next CTPLS cycle.

Figure 24-3 illustrates the external connections for pulse generation, as well as the relationship of the different analog modules required. While CTED1 is shown as the input pulse source, other options are available. A detailed discussion on pulse generation with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

### FIGURE 24-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE DELAY GENERATION

#### REGISTER 24-1: CTMUCON1L: CTMU CONTROL 1 LOW REGISTER (CONTINUED)

- bit 1-0 IRNG<1:0>: Current Source Range Select bits

- 11 = 100 × Base Current

- 10 = 10 × Base Current

- 01 = Base Current Level (0.55 μA nominal)

- 00 = 1000 × Base Current

| DC CHARACTE   |                | <b>Operating</b><br>temperatu |          | <b>2.0V to</b><br>-40°C ≤ | $\begin{array}{l} \textbf{1.8V to 3.6V (PIC24F16KMXXX)}\\ \textbf{2.0V to 5.5V (PIC24FV16KMXXX)}\\ \textbf{-40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial}}\\ \textbf{-40^{\circ}C \leq TA \leq +125^{\circ}C \text{ for Extended}} \end{array}$ |                              |  |  |

|---------------|----------------|-------------------------------|----------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

| Parameter No. | Device         | Typical                       | Max      | Units                     |                                                                                                                                                                                                                                                                | Conditions                   |  |  |

| IDD Current   |                |                               |          |                           |                                                                                                                                                                                                                                                                |                              |  |  |

| D20           | PIC24FV16KMXXX | 269                           | 450      | μA                        | 2.0V                                                                                                                                                                                                                                                           |                              |  |  |

|               | PIC24F16KMXXX  | 465                           | 830      | μA                        | 5.0V                                                                                                                                                                                                                                                           | 0.5 MIPS,                    |  |  |

|               |                | 200                           | 330      | μA                        | 1.8V                                                                                                                                                                                                                                                           | Fosc = 1 MHz <sup>(1)</sup>  |  |  |

|               |                | 410                           | 750      | μA                        | 3.3V                                                                                                                                                                                                                                                           |                              |  |  |

| DC22          | PIC24FV16KMXXX | 490                           | -90 — μA | μA                        | 2.0V                                                                                                                                                                                                                                                           |                              |  |  |

|               |                | 880                           | _        | μA                        | 5.0V                                                                                                                                                                                                                                                           | 1 MIPS,                      |  |  |

|               | PIC24F16KMXXX  | 407                           |          | μA                        | 1.8V                                                                                                                                                                                                                                                           | Fosc = 2 MHz <sup>(1)</sup>  |  |  |

|               |                | 800                           | _        | μA                        | 3.3V                                                                                                                                                                                                                                                           |                              |  |  |

| DC24          | PIC24FV16KMXXX | 13.0                          | 15.0     | mA                        | 5.0V                                                                                                                                                                                                                                                           | 16 MIPS,                     |  |  |

|               | PIC24F16KMXXX  | 12.0                          | 13.0     | mA                        | 3.3V                                                                                                                                                                                                                                                           | Fosc = 32 MHz <sup>(1)</sup> |  |  |

| DC26          | PIC24FV16KMXXX | 2.0                           | _        | mA                        | 2.0V                                                                                                                                                                                                                                                           |                              |  |  |

|               |                | 3.5                           | _        | mA                        | 5.0V                                                                                                                                                                                                                                                           | FRC (4 MIPS),                |  |  |

|               | PIC24F16KMXXX  | 1.80                          |          | mA                        | 1.8V                                                                                                                                                                                                                                                           | Fosc = 8 MHz                 |  |  |

|               |                | 3.40                          | _        | mA                        | 3.3V                                                                                                                                                                                                                                                           |                              |  |  |

| DC30          | PIC24FV16KMXXX | 48.0                          | 250      | μA                        | 2.0V                                                                                                                                                                                                                                                           |                              |  |  |

|               |                | 75.0                          | 275      | μA                        | 5.0V                                                                                                                                                                                                                                                           | LPRC (15.5 KIPS),            |  |  |

|               | PIC24F16KMXXX  | 8.1                           | 28.0     | μA                        | 1.8V                                                                                                                                                                                                                                                           | Fosc = 31 kHz                |  |  |

|               |                | 13.50                         | 55.00    | μA                        | 3.3V                                                                                                                                                                                                                                                           |                              |  |  |

#### TABLE 27-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Legend:** Unshaded rows represent PIC24F16KMXXX devices and shaded rows represent PIC24FV16KMXXX devices. **Note 1:** The oscillator is in External Clock mode (FOSCSEL<2:0> = 010, FOSC<1:0> = 00).

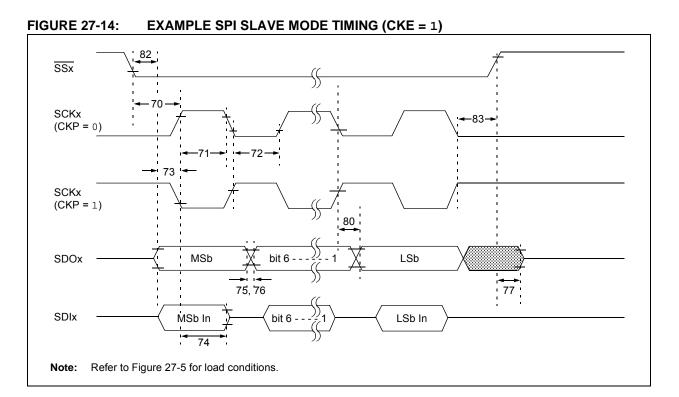

#### TABLE 27-32: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param<br>No. | Symbol                | Characteristic                                                                   | Min          | Max           | Units | Conditions |          |

|--------------|-----------------------|----------------------------------------------------------------------------------|--------------|---------------|-------|------------|----------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input |              | 3 Тсү         |       | ns         |          |

| 70A          | TssL2WB               | SSx to Write to SSPxBUF                                                          |              | 3 TCY         | _     | ns         |          |

| 71           | TscH                  | SCKx Input High Time                                                             | Continuous   | 1.25 Tcy + 30 |       | ns         |          |

| 71A          |                       | (Slave mode)                                                                     | Single Byte  | 40            | —     | ns         | (Note 1) |

| 72           | TscL                  | SCKx Input Low Time                                                              | Continuous   | 1.25 Tcy + 30 | —     | ns         |          |

| 72A          |                       | (Slave mode)                                                                     | 40           | _             | ns    | (Note 1)   |          |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the First                                           | 1.5 Tcy + 40 | —             | ns    | (Note 2)   |          |

| 74           | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SC                                               | Kx Edge      | 40            | _     | ns         |          |

| 75           | TDOR                  | SDOx Data Output Rise Time                                                       |              |               | 25    | ns         |          |

| 76           | TDOF                  | SDOx Data Output Fall Time                                                       |              |               | 25    | ns         |          |

| 77           | TssH2doZ              | SSx ↑ to SDOx Output High-Impeda                                                 | ance         | 10            | 50    | ns         |          |

| 80           | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After SCKx                                                | Edge         | —             | 50    | ns         |          |

| 82           | TssL2DoV              | SDOx Data Output Valid After SSx                                                 | _            | 50            | ns    |            |          |

| 83           | TscH2ssH,<br>TscL2ssH | SSx ↑ After SCKx Edge                                                            |              | 1.5 Tcy + 40  | _     | ns         |          |

|              | FSCK                  | SCKx Frequency                                                                   |              | —             | 10    | MHz        |          |

**Note 1:** Requires the use of Parameter 73A.

2: Only if Parameters 71A and 72A are used.

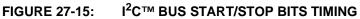

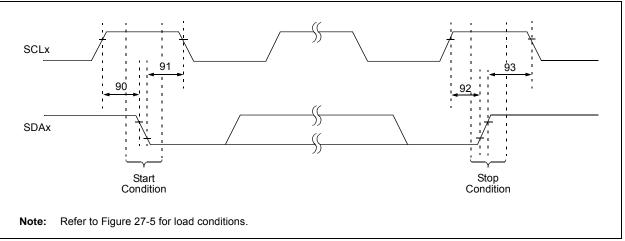

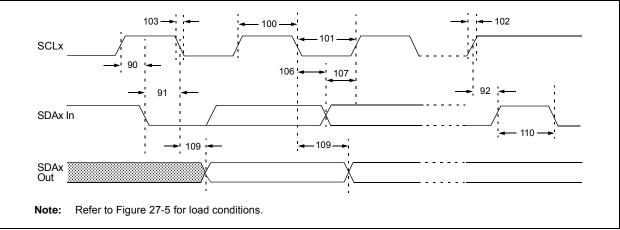

### TABLE 27-33: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characteristic                |              | Min  | Max | Units | Conditions                                            |

|---------------|---------|-------------------------------|--------------|------|-----|-------|-------------------------------------------------------|

| 90            | TSU:STA | Start Condition<br>Setup Time | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated Start condition            |

|               |         |                               | 400 kHz mode | 600  | _   |       |                                                       |

| 91            | THD:STA | Start Condition<br>Hold Time  | 100 kHz mode | 4000 | —   | ns    | After this period, the first clock pulse is generated |

|               |         |                               | 400 kHz mode | 600  | _   |       |                                                       |

| 92            | Tsu:sto | Stop Condition<br>Setup Time  | 100 kHz mode | 4700 | _   | ns    |                                                       |

|               |         |                               | 400 kHz mode | 600  | —   |       |                                                       |

| 93            | THD:STO | Stop Condition<br>Hold Time   | 100 kHz mode | 4000 | _   | ns    |                                                       |

|               |         |                               | 400 kHz mode | 600  | _   |       |                                                       |

#### FIGURE 27-16: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

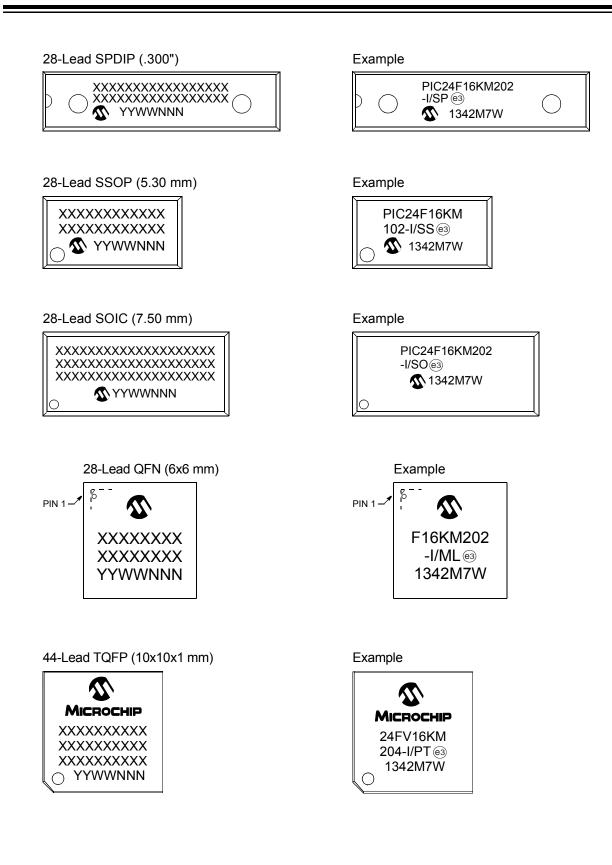

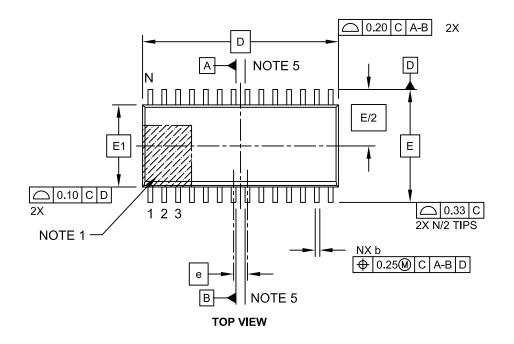

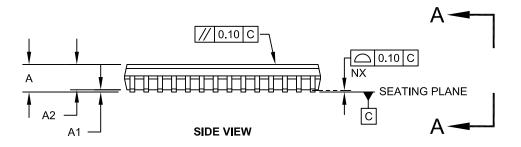

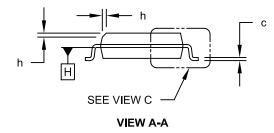

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2