## E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 28-SPDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km202-i-sp |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with Data Memory Space Addressing and makes it possible to access data in the program memory space.

#### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables, located from 000004h to 0000FFh, and 000104h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. **Section 8.1 "Interrupt Vector Table (IVT)**" discusses the Interrupt Vector Tables in more detail.

### 4.1.3 DATA EEPROM

In the PIC24FV16KM204 family, the data EEPROM is mapped to the top of the user program memory space, starting at address, 7FFE00, and expanding up to address, 7FFFF.

The data EEPROM is organized as 16-bit-wide memory and 256 words deep. This memory is accessed using Table Read and Write operations similar to the user code memory.

#### 4.1.4 DEVICE CONFIGURATION WORDS

Table 4-1 provides the addresses of the device Configuration Words for the PIC24FV16KM204 family. Their location in the memory map is displayed in Figure 4-1.

Refer to **Section 25.1** "**Configuration Bits**" for more information on device Configuration Words.

# TABLE 4-1: DEVICE CONFIGURATION WORDS FOR PIC24FXXXXX FAMILY DEVICES

| Configuration Word | Configuration Word<br>Addresses |

|--------------------|---------------------------------|

| FBS                | F80000                          |

| FGS                | F80004                          |

| FOSCSEL            | F80006                          |

| FOSC               | F80008                          |

| FWDT               | F8000A                          |

| FPOR               | F8000C                          |

| FICD               | F8000E                          |

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION msw most significant word least significant word PC Address (Isw Address) Address 16 8 Λ 23 000000h 000001h 00000000 0000000 000002h 000003h 000004h 00000000 000005h 0000000 000006h 000007h Instruction Width Program Memory Phantom' Byte (read as '0')

#### 4.2 **Data Address Space**

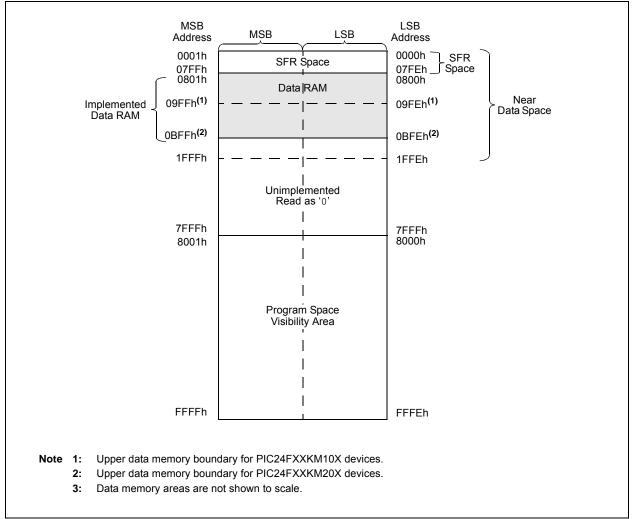

The PIC24F core has a separate, 16-bit-wide data memory space, addressable as a single linear range. The Data Space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The Data Space memory map is displayed in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This gives a Data Space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility").

Depending on the particular device, PIC24FV16KM family devices implement either 512 or 1024 words of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

FIGURE 4-3:

#### 4.2.1 DATA SPACE WIDTH

The data organized memory space is in byte-addressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all the Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

DATA SPACE MEMORY MAP FOR PIC24FXXXXX FAMILY DEVICES<sup>(3)</sup>

| IADLE 4   | -J.   |        | RRUPI   | CONT    | VOLLE   | N NLO  | SILK    |         |         |        |         |         |         |         |          |          |          |              |

|-----------|-------|--------|---------|---------|---------|--------|---------|---------|---------|--------|---------|---------|---------|---------|----------|----------|----------|--------------|

| File Name | Addr. | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7  | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Reset |

| INTCON1   | 80h   | NSTDIS | —       | —       | —       | —      | —       | —       | —       | —      | —       | —       | MATHERR | ADDRERR | STKERR   | OSCFAIL  | —        | 0000         |

| INTCON2   | 82h   | ALTIVT | DISI    | _       | —       | —      | _       | _       | _       | _      | _       | —       | _       | _       | INT2EP   | INT1EP   | INT0EP   | 0000         |

| IFS0      | 84h   | NVMIF  | _       | AD1IF   | U1TXIF  | U1RXIF | _       | _       | CCT2IF  | CCT1IF | CCP4IF  | CCP3IF  | _       | T1IF    | CCP2IF   | CCP1IF   | INT0IF   | 0000         |

| IFS1      | 86h   | U2TXIF | U2RXIF  | INT2IF  | CCT4IF  | CCT3IF | _       | _       | _       | _      | CCP5IF  | _       | INT1IF  | CNIF    | CMIF     | BCL1IF   | SSP1IF   | 0000         |

| IFS2      | 88h   | _      | _       | _       | _       | _      | _       | CCT5IF  | _       | _      | _       | _       | _       | _       | _        | _        | _        | 0000         |

| IFS3      | 8Ah   | _      | RTCIF   | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | BCL2IF   | SSP2IF   | _        | 0000         |

| IFS4      | 8Ch   | DAC2IF | DAC1IF  | CTMUIF  | _       | _      | _       | _       | HLVDIF  | _      | _       | _       | _       | _       | U2ERIF   | U1ERIF   | _        | 0000         |

| IFS5      | 8Eh   | _      | _       | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | _        | _        | ULPWUIF  | 0000         |

| IFS6      | 90h   | _      | _       | _       | _       | —      | _       | _       | _       | _      | _       | _       | —       | _       | _        | CLC2IF   | CLC1IF   | 0000         |

| IEC0      | 94h   | NVMIE  | _       | AD1IE   | U1TXIE  | U1RXIE | _       | _       | CCT2IE  | CCT1IE | CCP4IE  | CCP3IE  | —       | T1IE    | CCP2IE   | CCP1IE   | INT0IE   | 0000         |

| IEC1      | 96h   | U2TXIE | U2RXIE  | INT2IE  | CCT4IE  | CCT3IE | _       | _       | _       | _      | CCP5IE  | _       | INT1IE  | CNIE    | CMIE     | BCL1IE   | SSP1IE   | 0000         |

| IEC2      | 98h   | _      | _       | _       | _       | —      | _       | CCT5IE  | _       | _      | _       | _       | —       | _       | _        | —        | —        | 0000         |

| IEC3      | 9Ah   | _      | RTCIE   | _       | _       | —      | _       | _       | _       | _      | _       | _       | _       | _       | BCL2IE   | SSP2IE   | _        | 0000         |

| IEC4      | 9Ch   | DAC2IE | DAC1IE  | CTMUIE  | —       | _      | -       | _       | HLVDIE  | _      | -       | -       | _       | _       | U2ERIE   | U1ERIE   | _        | 0000         |

| IEC5      | 9Eh   | _      | _       |         | _       | _      |         | _       | _       | _      | -       | -       | _       | _       | _        | _        | ULPWUIE  | 0000         |

| IEC6      | A0h   | _      | _       |         | —       | _      |         | _       | _       | _      | -       | -       | _       | _       | -        | CLC2IE   | CLC1IE   | 0000         |

| IPC0      | A4h   | _      | T1IP2   | T1IP1   | T1IP0   |        | CCP2IP2 | CCP2IP1 | CCP2IP0 | _      | CCP1IP2 | CCP1IP1 | CCP1IP0 | _       | INT0IP2  | INT0IP1  | INT0IP0  | 4444         |

| IPC1      | A6h   | _      | CCT1IP2 | CCT1IP1 | CCT1IP0 | _      | CCP4IP2 | CCP4IP1 | CCP4IP0 | _      | CCP3IP2 | CCP3IP1 | CCP3IP0 | _       | _        | _        | _        | 4440         |

| IPC2      | A8h   | _      | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | -       | _       | _       | _      | _       | _       | _       | _       | CCT2IP2  | CCT2IP1  | CCT2IP0  | 4004         |

| IPC3      | AAh   | _      | NVMIP2  | NVMIP1  | NVMIP0  | _      |         | _       | _       | _      | AD1IP2  | AD1IP1  | AD1IP0  | _       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 4044         |

| IPC4      | ACh   | _      | CNIP2   | CNIP1   | CNIP0   | _      | CMIP2   | CMIP1   | CMIP0   | _      | BCL1IP2 | BCL1IP1 | BCL1IP0 | _       | SSP1IP2  | SSP1IP1  | SSP1IP0  | 4444         |

| IPC5      | AEh   | _      | _       |         | —       | _      | CCP5IP2 | CCP5IP1 | CCP5IP0 | _      | _       | _       | _       | _       | INT1IP2  | INT1IP1  | INT1IP0  | 0404         |

| IPC6      | B0h   | _      | CCT3IP2 | CCT3IP1 | CCT3IP0 | —      | -       | _       | _       | _      |         |         | —       | _       | -        | —        | —        | 4000         |

| IPC7      | B2h   | _      | U2TXIP2 | U2TXIP1 | U2TXIP0 | _      | U2RXIP2 | U2RXIP1 | U2RXIP0 | _      | INT2IP2 | INT2IP1 | INT2IP0 | _       | CCT4IP2  | CCT4IP1  | CCT4IP0  | 4444         |

| IPC10     | B8h   | _      | _       |         | —       | _      | -       | _       | _       | _      | CCT5IP2 | CCT5IP1 | CCT5IP0 | _       | _        | _        | _        | 0040         |

| IPC12     | BCh   | _      | _       | _       | _       | —      | BCL2IP2 | BCL2IP1 | BCL2IP0 | _      | SSP2IP2 | SSP2IP1 | SSP2IP0 | _       | -        | _        | _        | 0440         |

| IPC15     | C2h   | _      | _       | _       | _       | —      | RTCIP2  | RTCIP1  | RTCIP0  | _      | -       |         | —       | _       | -        | _        | _        | 0400         |

| IPC16     | C4h   | _      | _       | _       | _       | —      | U2ERIP2 | U2ERIP1 | U2ERIP0 | _      | U1ERIP2 | U1ERIP1 | U1ERIP0 | _       | _        | _        | _        | 0440         |

| IPC18     | C8h   | _      | _       | _       | _       | —      | —       | —       | —       | _      | —       | —       | —       | _       | HLVDIP2  | HLVDIP1  | HLVDIP0  | 0004         |

| IPC19     | CAh   | _      | DAC2IP2 | DAC2IP1 | DAC2IP0 | —      | DAC1IP2 | DAC1IP1 | DAC1IP0 | _      | CTMUIP2 | CTMUIP1 | CTMUIP0 | _       | —        | —        | —        | 4440         |

| IPC20     | CCh   | _      | _       | —       | —       | —      | _       | _       | —       | _      | —       | —       | —       | _       | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 | 0004         |

| IPC24     | D4h   | _      | _       | _       | _       |        | _       | _       | _       | _      | CLC2IP2 | CLC2IP1 | CLC2IP0 | _       | CLC1IP2  | CLC1IP1  | CLC1IP0  | 0044         |

| INTTREG   | E0h   | CPUIRQ | _       | VHOLD   | _       | ILR3   | ILR2    | ILR1    | ILR0    | _      | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000         |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

#### TABLE 4-6: TIMER1 REGISTER MAP

|           |       |        | -                                                                                                                                                                            | -      |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

|-----------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                                                                                                                                                                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1      | 100h  |        | Timer1 Register xxxx                                                                                                                                                         |        |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

| PR1       | 102h  |        | Timer1 Period Register FFFF                                                                                                                                                  |        |        |        |        |       |       |       |       |       |       | FFFF  |       |       |       |               |

| T1CON     | 104h  | TON    | ON         —         TSIDL         —         —         TECS1         TECS0         —         TGATE         TCKPS0         —         TSYNC         TCS         —         0000 |        |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

| Lanandi   |       |        |                                                                                                                                                                              |        |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-7: CLC1-2 REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CLC1CONL                | 122h  | LCEN   | —      | _      | —      | INTP   | INTN   | —     | —     | LCOE  | LCOUT | LCPOL | —     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC1CONH                | 124h  | _      | _      |        | _      | _      | _      | _     | _     | _     | _     | _     | _     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC1SEL                 | 126h  | _      | DS42   | DS41   | DS40   |        | DS32   | DS31  | DS30  | —     | DS22  | DS21  | DS20  | _     | DS12  | DS11  | DS10  | 0000          |

| CLC1GLSL                | 12Ah  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC1GLSH                | 12Ch  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

| CLC2CONL <sup>(1)</sup> | 12Eh  | LCEN   | _      | -      | _      | INTP   | INTN   | _     | _     | LCOE  | LCOUT | LCPOL | _     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC2CONH <sup>(1)</sup> | 130h  | —      | —      | _      | —      | _      | _      | —     | _     | _     | _     | _     | —     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC2SEL <sup>(1)</sup>  | 132h  | —      | DS42   | DS41   | DS40   | _      | DS32   | DS31  | DS30  | _     | DS22  | DS21  | DS20  | —     | DS12  | DS11  | DS10  | 0000          |

| CLC2GLSL <sup>(1)</sup> | 136h  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC2GLSH <sup>(1)</sup> | 138h  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-9: MCCP2 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14                           | Bit 13               | Bit 12               | Bit 11               | Bit 10               | Bit 9                | Bit 8                | Bit 7        | Bit 6        | Bit 5   | Bit 4                 | Bit 3   | Bit 2   | Bit 1                  | Bit 0      | All<br>Resets |

|-----------|-------|---------|----------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------------|--------------|---------|-----------------------|---------|---------|------------------------|------------|---------------|

| CCP2CON1L | 164h  | CCPON   | _                                | CCPSIDL              | r                    | TMRSYNC              | CLKSEL2              | CLKSEL1              | CLKSEL0              | TMRPS1       | TMRPS0       | T32     | CCSEL                 | MOD3    | MOD2    | MOD1                   | MOD0       | 0000          |

| CCP2CON1H | 166h  | OPSSRC  | RTRGEN                           | _                    | _                    | IOPS3                | IOPS2                | IOPS1                | IOPS0                | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4                 | SYNC3   | SYNC2   | SYNC1                  | SYNC0      | 0000          |

| CCP2CON2L | 168h  | PWMRSEN | ASDGM                            |                      | SSDG                 |                      |                      | _                    | _                    | ASDG7        | ASDG6        | ASDG5   | ASDG4                 | ASDG3   | ASDG2   | ASDG1                  | ASDG0      | 0000          |

| CCP2CON2H | 16Ah  | OENSYNC | -                                | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN                | ICGSM1       | ICGSM0       | _       | AUXOUT1               | AUXOUT0 | ICSEL2  | ICSEL1                 | ICSEL0     | 0100          |

| CCP2CON3L | 16Ch  | _       | _                                | _                    | _                    | _                    | _                    | _                    | _                    | _            |              | DT5     | DT4                   | DT3     | DT2     | DT1                    | DT0        | 0000          |

| CCP2CON3H | 16Eh  | OETRIG  | OSCNT2                           | OSCNT1               | OSCNT0               | _                    | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> | _            | _            | POLACE  | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0(1) | 0000          |

| CCP2STATL | 170h  | _       | -                                |                      | _                    |                      |                      | _                    | _                    | CCPTRIG      | TRSET        | TRCLR   | ASEVT                 | SCEVT   | ICDIS   | ICOV                   | ICBNE      | 0000          |

| CCP2TMRL  | 174h  |         |                                  |                      |                      |                      |                      | MCC                  | P2 Time Ba           | ase Register | r Low Word   |         |                       |         |         |                        |            | 0000          |

| CCP2TMRH  | 176h  |         |                                  |                      |                      |                      |                      | MCC                  | P2 Time Ba           | se Register  | High Word    |         |                       |         |         |                        |            | 0000          |

| CCP2PRL   | 178h  |         |                                  |                      |                      |                      |                      | MCCP2                | Time Base            | Period Regi  | ister Low Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2PRH   | 17Ah  |         |                                  |                      |                      |                      |                      | MCCP2                | Time Base I          | Period Regi  | ster High Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2RAL   | 17Ch  |         |                                  |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word A       |         |                       |         |         |                        |            | 0000          |

| CCP2RBL   | 180h  |         | Output Compare 2 Data Word B 000 |                      |                      |                      |                      |                      |                      |              |              |         | 0000                  |         |         |                        |            |               |

| CCP2BUFL  | 184h  |         |                                  |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | Low Word     |         |                       |         |         |                        |            | 0000          |

| CCP2BUFH  | 186h  |         |                                  |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | High Word    |         |                       |         |         |                        |            | 0000          |

PIC24FV16KM204 FAMILY

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-11: SCCP4 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14                                                                                                                                                                             | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8       | Bit 7         | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|---------|---------|-----------|-------------|---------------|-------------|---------|---------|---------|--------|--------|--------|---------------|

| CCP4CON1L <sup>(1)</sup> | 1ACh  | CCPON   | _                                                                                                                                                                                  | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0     | TMRPS1        | TMRPS0      | T32     | CCSEL   | MOD3    | MOD2   | MOD1   | MOD0   | 0000          |

| CCP4CON1H(1)             | 1AEh  | OPSSRC  | RTRGEN                                                                                                                                                                             | —       | _      | IOPS3   | IOPS2   | IOPS1     | IOPS0       | TRIGEN        | ONESHOT     | ALTSYNC | SYNC4   | SYNC3   | SYNC2  | SYNC1  | SYNC0  | 0000          |

| CCP4CON2L <sup>(1)</sup> | 1B0h  | PWMRSEN | ASDGM                                                                                                                                                                              | _       | SSDG   | _       | _       | _         | _           | ASDG7         | ASDG6       | ASDG5   | ASDG4   | ASDG3   | ASDG2  | ASDG1  | ASDG0  | 0000          |

| CCP4CON2H <sup>(1)</sup> | 1B2h  | OENSYNC | _                                                                                                                                                                                  | _       | _      | _       | _       | _         | OCAEN       | ICGSM1        | ICGSM0      | _       | AUXOUT1 | AUXOUT0 | ICSEL2 | ICSEL1 | ICSEL0 | 0100          |

| CCP4CON3H <sup>(1)</sup> | 1B6h  | OETRIG  | RIG         OSCNT2         OSCNT1         OSCNT0         —         —         —         —         POLACE         —         PSSACE1         PSSACE0         —         —         0000 |         |        |         |         |           |             |               |             | 0000    |         |         |        |        |        |               |

| CCP4STATL <sup>(1)</sup> | 1B8h  | _       |                                                                                                                                                                                    |         |        |         |         |           |             |               |             | 0000    |         |         |        |        |        |               |

| CCP4TMRL <sup>(1)</sup>  | 1BCh  |         |                                                                                                                                                                                    |         |        |         |         | SCCP4     | 1 Time Base | Register Lo   | ow Word     |         |         |         |        |        |        | 0000          |

| CCP4TMRH <sup>(1)</sup>  | 1BEh  |         |                                                                                                                                                                                    |         |        |         |         | SCCP4     | Time Base   | Register Hi   | gh Word     |         |         |         |        |        |        | 0000          |

| CCP4PRL <sup>(1)</sup>   | 1C0h  |         |                                                                                                                                                                                    |         |        |         |         | SCCP4 Tir | ne Base Pe  | riod Registe  | er Low Word |         |         |         |        |        |        | FFFF          |

| CCP4PRH <sup>(1)</sup>   | 1C2h  |         |                                                                                                                                                                                    |         |        |         |         | SCCP4 Tir | ne Base Pe  | riod Registe  | r High Word |         |         |         |        |        |        | FFFF          |

| CCP4RAL <sup>(1)</sup>   | 1C4h  |         |                                                                                                                                                                                    |         |        |         |         | Out       | put Compar  | e 4 Data Wo   | ord A       |         |         |         |        |        |        | 0000          |

| CCP4RBL <sup>(1)</sup>   | 1C8h  |         | Output Compare 4 Data Word B 0000                                                                                                                                                  |         |        |         |         |           |             |               |             |         | 0000    |         |        |        |        |               |

| CCP4BUFL <sup>(1)</sup>  | 1CCh  |         | Input Capture 4 Data Buffer Low Word 0000                                                                                                                                          |         |        |         |         |           |             |               |             |         | 0000    |         |        |        |        |               |

| CCP4BUFH <sup>(1)</sup>  | 1CEh  |         |                                                                                                                                                                                    |         |        |         |         | Input C   | apture 4 Da | ita Buffer Hi | gh Word     |         |         |         |        |        |        | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** These registers are available only on PIC24F(V)16KM2XX devices.

#### 6.4.1 ERASE DATA EEPROM

The data EEPROM can be fully erased, or can be partially erased, at three different sizes: one word, four words or eight words. The bits, NVMOP<1:0> (NVMCON<1:0>), decide the number of words to be erased. To erase partially from the data EEPROM, the following sequence must be followed:

- 1. Configure NVMCON to erase the required number of words: one, four or eight.

- 2. Load TBLPAG and WREG with the EEPROM address to be erased.

- 3. Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 4. Write the key sequence to NVMKEY.

- 5. Set the WR bit to begin the erase cycle.

- 6. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical erase sequence is provided in Example 6-2. This example shows how to do a one-word erase. Similarly, a four-word erase and an eight-word erase can be done. This example uses C library procedures to manage the Table Pointer (builtin\_tblpage and builtin\_tbloffset) and the Erase Page Pointer (builtin\_tblwt1). The memory unlock sequence (builtin\_write\_NVM) also sets the WR bit to initiate the operation and returns control when complete.

#### EXAMPLE 6-2: SINGLE-WORD ERASE

```

int __attribute__ ((space(eedata))) eeData = 0x1234;

/*_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the erase

_____

*/

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0 \times 4058;

// Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData); // Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData);

// Initizlize lower word of address

__builtin_tblwtl(offset, 0);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

__builtin_write_NVM();

// Issue Unlock Sequence & Start Write Cycle

while(NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

**REGISTER 7-1:**

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0, H   | S R/W-0, HS                    | R/W-0                 | R/W-0                | U-0                  | U-0                                 | R/W-0             | R/W-0          |

|------------|--------------------------------|-----------------------|----------------------|----------------------|-------------------------------------|-------------------|----------------|

| TRAPR      |                                | SBOREN                | RETEN <sup>(3)</sup> | _                    | _                                   | СМ                | PMSLP          |

| bit 15     |                                |                       |                      |                      |                                     |                   | bit 8          |

|            |                                |                       |                      |                      |                                     |                   |                |

| R/W-0, H   | S R/W-0, HS                    | R/W-0, HS             | R/W-0, HS            | R/W-0, HS            | R/W-0, HS                           | R/W-1, HS         | R/W-1, HS      |

| EXTR       | SWR                            | SWDTEN <sup>(2)</sup> | WDTO                 | SLEEP                | IDLE                                | BOR               | POR            |

| bit 7      |                                |                       |                      |                      |                                     |                   | bit C          |

|            |                                |                       |                      |                      |                                     |                   |                |

| Legend:    |                                | HS = Hardwar          | e Settable bit       |                      |                                     |                   |                |

| R = Read   | able bit                       | W = Writable t        | pit                  | U = Unimplen         | nented bit, read                    | as '0'            |                |

| -n = Value | e at POR                       | '1' = Bit is set      |                      | '0' = Bit is cle     | ared                                | x = Bit is unkn   | own            |

|            |                                |                       |                      |                      |                                     |                   |                |

| bit 15     | -                              | Reset Flag bit        |                      |                      |                                     |                   |                |

|            | •                              | onflict Reset has     |                      |                      |                                     |                   |                |

| 1.11.4.4   |                                | onflict Reset has     |                      |                      | <b>E</b> 1                          |                   |                |

| bit 14     |                                | gal Opcode or l       |                      |                      | r Flag bit<br>or Uninitialized V    | / register used   | aa an Addraaa  |

|            |                                | aused a Reset         | on, an illegal a     |                      |                                     | v register used   | as an Address  |

|            |                                | opcode or Unir        | nitialized W Re      | set has not oc       | curred                              |                   |                |

| bit 13     | SBOREN: So                     | oftware Enable/D      | Disable of BOF       | R bit                |                                     |                   |                |

|            | 1 = BOR is tu                  | rned on in softw      | are                  |                      |                                     |                   |                |

|            |                                | rned off in softw     |                      |                      |                                     |                   |                |

| bit 12     |                                | ention Sleep Mo       |                      |                      |                                     |                   |                |

|            |                                |                       |                      |                      | Regulator (RETR<br>ge Regulator (VF |                   |                |

| bit 11-10  | -                              | ted: Read as '0       |                      |                      |                                     |                   |                |

| bit 9      | -                              | ation Word Misr       |                      | lag bit              |                                     |                   |                |

|            | -                              | Iration Word Mis      |                      | -                    |                                     |                   |                |

|            | 0 = A Configu                  | ration Word Mis       | match Reset          | has not occurre      | ed                                  |                   |                |

| bit 8      | PMSLP: Prog                    | gram Memory Po        | ower During S        | leep bit             |                                     |                   |                |

|            |                                | memory bias vo        |                      |                      |                                     |                   |                |

|            | 0 = Program<br>Standby         |                       | oltage is pow        | vered down du        | iring Sleep and                     | the voltage re    | gulator enters |

| bit 7      | •                              | nal Reset (MCLF       | R) Pin hit           |                      |                                     |                   |                |

| bit i      |                                | Clear (pin) Rese      |                      | d                    |                                     |                   |                |

|            |                                | Clear (pin) Rese      |                      |                      |                                     |                   |                |

| bit 6      | SWR: Softwa                    | re reset (Instru      | uction) Flag bit     | t                    |                                     |                   |                |

|            |                                | instruction has t     |                      |                      |                                     |                   |                |

|            |                                | instruction has r     |                      |                      |                                     |                   |                |

| bit 5      |                                | oftware Enable/[      | Disable of WD        | l bit <sup>(2)</sup> |                                     |                   |                |

|            | 1 = WDT is ei<br>0 = WDT is di |                       |                      |                      |                                     |                   |                |

|            |                                |                       |                      |                      | <b>-</b>                            |                   |                |

| Note 1:    | All of the Reset               | •                     | be set or clear      | ed in software.      | Setting one of the                  | nese bits in soft | ware does not  |

| 2:         | If the FWDTEN                  |                       | tion bits are '1     | 1' (upprogram        | med) the WDT i                      | is alwavs enabl   | ed renardless  |

| <b>_</b> . | of the SWDTEN                  |                       |                      |                      |                                     | ie amayo chabi    |                |

| -          |                                |                       |                      |                      |                                     |                   |                |

#### 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24FXXXXX family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator:

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The Primary Oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

#### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 25.1 "Configuration Bits"). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                      | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|------------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler<br>(LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                       | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)                 | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)      | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)      | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                              | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                              | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                              | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O ports, refer to the *"PIC24F Family Reference Manual"*, *"I/O Ports with Peripheral Pin Select (PPS)"* (DS39711). Note that the PIC24FV16KM204 family devices do not support Peripheral Pin Select features.

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

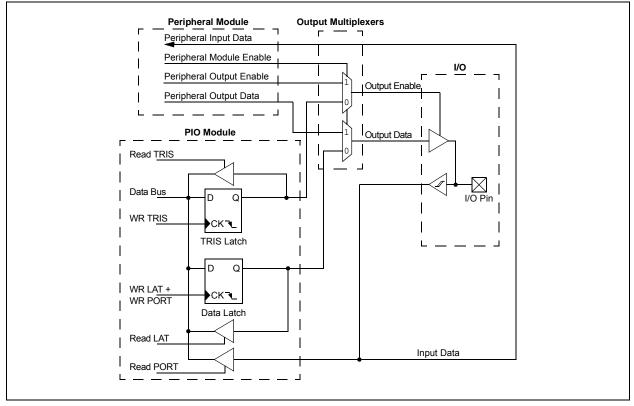

### 11.1 Parallel I/O (PIO) Ports

A Parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the Data Direction register bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LATx), read the latch. Writes to the latch, write the latch. Reads from the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

#### REGISTER 11-2: ANSB: PORTB ANALOG SELECTION REGISTER

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | U-0 | U-0 | R/W-1 | R/W-1 |

|--------|--------|--------|--------|-----|-----|-------|-------|

| ANSB15 | ANSB14 | ANSB13 | ANSB12 | —   |     | ANSB9 | ANSB8 |

| bit 15 |        |        |        |     |     |       | bit 8 |

| R/W-1 | R/W-1                | R/W-1                | R/W-1 | R/W-1                | R/W-1 | R/W-1 | R/W-1 |

|-------|----------------------|----------------------|-------|----------------------|-------|-------|-------|

| ANSB7 | ANSB6 <sup>(1)</sup> | ANSB5 <sup>(1)</sup> | ANSB4 | ANSB3 <sup>(1)</sup> | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |                      |                      |       |                      |       |       | bit 0 |

### Legend

| Legena:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

bit 15-12 **ANSB<15:12>:** Analog Select Control bits 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

- bit 11-10 Unimplemented: Read as '0'

- bit 9-0 ANSB<9:0>: Analog Select Control bits<sup>(1)</sup>

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

- Note 1: The ANSB<6:5,3> bits are not available on 20-pin devices.

#### REGISTER 11-3: ANSC: PORTC ANALOG SELECTION REGISTER

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0                    | U-0                    | U-0                    |

|---------|-----|-----|-----|-----|------------------------|------------------------|------------------------|

| —       | —   | —   | —   | —   | —                      | —                      | —                      |

| bit 15  |     |     |     |     |                        |                        | bit 8                  |

|         |     |     |     |     |                        |                        |                        |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1                  | R/W-1                  | R/W-1                  |

| —       | —   | —   | —   | —   | ANSC2 <sup>(1,2)</sup> | ANSC1 <sup>(1,2)</sup> | ANSC0 <sup>(1,2)</sup> |

| bit 7   |     |     |     |     |                        |                        | bit 0                  |

|         |     |     |     |     |                        |                        |                        |

| Legend: |     |     |     |     |                        |                        |                        |

| Logona.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 ANSC<2:0>: Analog Select Control bits<sup>(1,2)</sup>

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

### REGISTER 13-5: CCPxCON3L: CCPx CONTROL 3 LOW REGISTERS <sup>(1)</sup>

| U-0                                | U-0                                 | U-0                                                                             | U-0                  | U-0                                | U-0                | U-0   | U-0   |  |  |  |

|------------------------------------|-------------------------------------|---------------------------------------------------------------------------------|----------------------|------------------------------------|--------------------|-------|-------|--|--|--|

| _                                  | —                                   | —                                                                               | —                    | —                                  | —                  | —     | —     |  |  |  |

| bit 15                             |                                     |                                                                                 |                      |                                    |                    |       | bit 8 |  |  |  |

|                                    |                                     |                                                                                 |                      |                                    |                    |       |       |  |  |  |

| U-0                                | U-0                                 | R/W-0                                                                           | R/W-0                | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |  |  |

| _                                  | —                                   | DT5                                                                             | DT4                  | DT3                                | DT2                | DT1   | DT0   |  |  |  |

| bit 7                              |                                     | •                                                                               |                      | ·                                  |                    |       | bit 0 |  |  |  |

|                                    |                                     |                                                                                 |                      |                                    |                    |       |       |  |  |  |

| Legend:                            |                                     |                                                                                 |                      |                                    |                    |       |       |  |  |  |

| R = Readab                         | le bit                              | W = Writable                                                                    | bit                  | U = Unimplemented bit, read as '0' |                    |       |       |  |  |  |

| -n = Value at POR '1' = Bit is set |                                     |                                                                                 | '0' = Bit is cleared |                                    | x = Bit is unknown |       |       |  |  |  |

|                                    |                                     |                                                                                 |                      |                                    |                    |       |       |  |  |  |

| bit 15-6                           | Unimplemented: Read as '0'          |                                                                                 |                      |                                    |                    |       |       |  |  |  |

| bit 5-0                            | DT<5:0>: CCPx Dead-Time Select bits |                                                                                 |                      |                                    |                    |       |       |  |  |  |

|                                    | 111111 <b>– I</b> nc                | 111111 - Insert 62 dood time dolow periods between complementary output signals |                      |                                    |                    |       |       |  |  |  |

111111 = Insert 63 dead-time delay periods between complementary output signals

111110 = Insert 62 dead-time delay periods between complementary output signals

000010 = Insert 2 dead-time delay periods between complementary output signals

000001 = Insert 1 dead-time delay period between complementary output signals

000000 = Dead-time logic is disabled

Note 1: This register is implemented in MCCPx modules only.

#### REGISTER 13-7: CCPxSTATL: CCPx STATUS REGISTER

| U-0           | U-0                                                                                                                    | U-0                                    | U-0            | U-0               | U-0              | U-0             | U-0           |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|-------------------|------------------|-----------------|---------------|--|--|--|

| _             | _                                                                                                                      | —                                      | _              | —                 | _                | —               |               |  |  |  |

| bit 15        |                                                                                                                        |                                        |                |                   |                  |                 | bit 8         |  |  |  |

|               |                                                                                                                        |                                        | 5/0.0          | 5/2.2             | 5/0.0            | 5/2.2           | 5/2.2         |  |  |  |

| R-0           | W1-0                                                                                                                   | W1-0<br>TRCLR                          | R/C-0<br>ASEVT | R/C-0<br>SCEVT    | R/C-0<br>ICDIS   | R/C-0           | R/C-0         |  |  |  |

| CCPTRIG       | TRSET                                                                                                                  | ICOV                                   | ICBNE          |                   |                  |                 |               |  |  |  |

| bit 7         |                                                                                                                        |                                        |                |                   |                  |                 | bit 0         |  |  |  |

| Legend:       |                                                                                                                        | C = Clearable                          | bit            |                   |                  |                 |               |  |  |  |

| R = Readabl   | e bit                                                                                                                  | W1 = Write '1'                         | only           | U = Unimplem      | nented bit, read | as '0'          |               |  |  |  |

| -n = Value at | POR                                                                                                                    | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |  |  |  |

|               |                                                                                                                        |                                        |                |                   |                  |                 |               |  |  |  |

| bit 15-8      | Unimplemen                                                                                                             | ted: Read as '0                        | ,              |                   |                  |                 |               |  |  |  |

| bit 7         | CCPTRIG: CCPx Trigger Status bit                                                                                       |                                        |                |                   |                  |                 |               |  |  |  |

|               | 1 = Timer has been triggered and is running                                                                            |                                        |                |                   |                  |                 |               |  |  |  |

| <b>h</b> :# 0 | <ul> <li>0 = Timer has not been triggered and is held in Reset</li> <li>TRSET: CCPx Trigger Set Request bit</li> </ul> |                                        |                |                   |                  |                 |               |  |  |  |

| bit 6         |                                                                                                                        | is location to trig                    |                | when TRIGEN       | = 1 (location a  | wave reade as   | : '∩')        |  |  |  |

| bit 5         |                                                                                                                        | Px Trigger Clear                       |                |                   |                  | ways icaus as   | , , ,         |  |  |  |

| bit o         |                                                                                                                        | is location to ca                      | •              | Trigger when T    | RIGEN = 1 (lo    | cation alwavs r | eads as '0'). |  |  |  |

| bit 4         |                                                                                                                        | x Auto-Shutdow                         |                |                   | - (-             | ,               | ····,         |  |  |  |

|               | 1 = A shutdo                                                                                                           | wn event is in p                       | rogress; CCP   | x outputs are in  | the shutdown     | state           |               |  |  |  |

|               | 0 = CCPx outputs operate normally                                                                                      |                                        |                |                   |                  |                 |               |  |  |  |

| bit 3         | •                                                                                                                      | le Edge Compa                          |                |                   |                  |                 |               |  |  |  |

|               |                                                                                                                        | edge compare e<br>edge compare e       |                |                   |                  |                 |               |  |  |  |

| bit 2         | •                                                                                                                      | Capture x Disat                        |                | occurred          |                  |                 |               |  |  |  |

| Dit Z         | •                                                                                                                      | Input Capture :                        |                | es not generate   | a capture ever   | nt              |               |  |  |  |

|               |                                                                                                                        | Input Capture                          |                |                   |                  |                 |               |  |  |  |

| bit 1         | ICOV: Input Capture x Buffer Overflow Status bit                                                                       |                                        |                |                   |                  |                 |               |  |  |  |

|               |                                                                                                                        | t Capture x FIF                        |                |                   |                  |                 |               |  |  |  |

|               |                                                                                                                        | t Capture x FIF                        |                | ot overflowed     |                  |                 |               |  |  |  |

| bit 0         | •                                                                                                                      | Capture x Buffe                        |                | -  -   -          |                  |                 |               |  |  |  |

|               |                                                                                                                        | apture x buffer h<br>apture x buffer i |                | adie              |                  |                 |               |  |  |  |

|               |                                                                                                                        |                                        | c sinply       |                   |                  |                 |               |  |  |  |

| R/W-0         | U-0                          | R/W-0                                                               | R/W-0                         | R/W-0                                      | U-0                                        | R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup> |  |  |

|---------------|------------------------------|---------------------------------------------------------------------|-------------------------------|--------------------------------------------|--------------------------------------------|----------------------|----------------------|--|--|

| UARTEN        | —                            | USIDL                                                               | IREN <sup>(1)</sup>           | RTSMD                                      | _                                          | UEN1                 | UEN0                 |  |  |

| bit 15        |                              |                                                                     |                               |                                            |                                            |                      | bit 8                |  |  |

| R/C-0, HC     | R/W-0                        | R/W-0, HC                                                           | R/W-0                         | R/W-0                                      | R/W-0                                      | R/W-0                | R/W-0                |  |  |

| WAKE          | LPBACK                       | ABAUD                                                               | URXINV                        | BRGH                                       | PDSEL1                                     | PDSEL0               | STSEL                |  |  |

| bit 7         | LI DAOR                      |                                                                     | UIXIIIV                       | BRGH                                       | TDSELT                                     | T DOLLO              | bit 0                |  |  |

|               |                              |                                                                     |                               |                                            |                                            |                      |                      |  |  |

| Legend:       |                              | C = Clearable                                                       |                               |                                            | are Clearable bi                           |                      |                      |  |  |

| R = Readabl   |                              | W = Writable                                                        | oit                           |                                            | mented bit, read                           |                      |                      |  |  |

| -n = Value at | POR                          | '1' = Bit is set                                                    |                               | '0' = Bit is cle                           | ared                                       | x = Bit is unkn      | iown                 |  |  |

| bit 15        | UARTEN: UA                   | ARTx Enable bit                                                     |                               |                                            |                                            |                      |                      |  |  |

|               |                              | s enabled; all U                                                    |                               | e controlled by l                          | JARTx. as defir                            | ned by UEN<1:        | 0>                   |  |  |

|               |                              | s disabled; all L                                                   |                               |                                            |                                            |                      |                      |  |  |

| bit 14        | Unimplemen                   | ted: Read as 'd                                                     | )'                            |                                            |                                            |                      |                      |  |  |

| bit 13        | USIDL: UAR                   | Tx Stop in Idle N                                                   | /lode bit                     |                                            |                                            |                      |                      |  |  |

|               |                              | nues module op                                                      |                               |                                            | ers Idle mode                              |                      |                      |  |  |

|               |                              | 0 = Continues module operation in Idle mode                         |                               |                                            |                                            |                      |                      |  |  |

| bit 12        |                              | Encoder and D                                                       |                               |                                            |                                            |                      |                      |  |  |

|               |                              | oder and decoo<br>oder and decoo                                    |                               |                                            |                                            |                      |                      |  |  |

| bit 11        | RTSMD: Mod                   | le Selection for                                                    | UxRTS Pin bi                  | t                                          |                                            |                      |                      |  |  |

|               |                              | in is in Simplex<br>in is in Flow Co                                |                               |                                            |                                            |                      |                      |  |  |

| bit 10        | Unimplemen                   | ted: Read as 'd                                                     | )'                            |                                            |                                            |                      |                      |  |  |

| bit 9-8       | UEN<1:0>: U                  | IARTx Enable b                                                      | its <sup>(2)</sup>            |                                            |                                            |                      |                      |  |  |

|               | 10 = UxTX, U<br>01 = UxTX, U | JxRX and UxBC<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins are | nd UxRTS pin<br>S pins are en | is are enabled a<br>abled <u>and us</u> ec | an <u>d used</u><br>I; <u>UxCTS</u> pin is | controlled by p      | ort latches          |  |  |

| bit 7         | WAKE: Wake                   | e-up on Start Bit                                                   | Detect During                 | g Sleep Mode E                             | Enable bit                                 |                      |                      |  |  |

|               | cleared in                   | vill continue to<br>n hardware on t                                 | •                             |                                            | rupt is generate                           | ed on the fallin     | ig edge, bit is      |  |  |

| hit C         |                              | -up is enabled                                                      | Mada Salaat                   | hit                                        |                                            |                      |                      |  |  |

| bit 6         |                              | ARTx Loopback<br>Loopback mode                                      |                               | DIL                                        |                                            |                      |                      |  |  |

|               |                              | k mode is disab                                                     |                               |                                            |                                            |                      |                      |  |  |

| bit 5         | -                            | o-Baud Enable                                                       |                               |                                            |                                            |                      |                      |  |  |

|               | cleared in                   | baud rate meas<br>n hardware upo                                    | n completion                  |                                            | er – requires re                           | ception of a Sy      | nc field (55h);      |  |  |

|               |                              | e measurement                                                       |                               | •                                          |                                            |                      |                      |  |  |

| bit 4         |                              | RTx Receive Po                                                      | plarity Inversio              | n dit                                      |                                            |                      |                      |  |  |

|               | 1 = UxRX IdI<br>0 = UxRX IdI |                                                                     |                               |                                            |                                            |                      |                      |  |  |

| Note 1: Th    | nis feature is is            | only available fo                                                   | or the 16x BR                 | G mode (BRGF                               | <b>I</b> = 0).                             |                      |                      |  |  |