Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km202t-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                            |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  | I                                | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| CN13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I   | ST     | Interrupt-on-Change Inputs |

| CN14     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | Interrupt-on-Change Inputs |

| CN15     | —                                | 22                               | 19            | 9                      | 10             | —                                | 22                               | 19            | 9                      | 10             | I   | ST     | Interrupt-on-Change Inputs |

| CN16     | _                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I   | ST     | Interrupt-on-Change Inputs |

| CN17     | —                                | —                                |               | 3                      | 3              | —                                |                                  | —             | 3                      | 3              | I   | ST     | Interrupt-on-Change Inputs |

| CN18     | —                                | —                                |               | 2                      | 2              | —                                |                                  | —             | 2                      | 2              | I   | ST     | Interrupt-on-Change Inputs |

| CN19     | —                                | —                                |               | 5                      | 5              | —                                |                                  | —             | 5                      | 5              | I   | ST     | Interrupt-on-Change Inputs |

| CN20     | —                                | —                                |               | 4                      | 4              | —                                |                                  | —             | 4                      | 4              | I   | ST     | Interrupt-on-Change Inputs |

| CN21     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | Interrupt-on-Change Inputs |

| CN22     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ST     | Interrupt-on-Change Inputs |

| CN23     | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs |

| CN24     | —                                | 15                               | 12            | 42                     | 46             | —                                | 15                               | 12            | 42                     | 46             | I   | ST     | Interrupt-on-Change Inputs |

| CN25     | _                                | _                                |               | 37                     | 40             | _                                |                                  | _             | 37                     | 40             | I   | ST     | Interrupt-on-Change Inputs |

| CN26     | _                                | _                                |               | 38                     | 41             | _                                |                                  | _             | 38                     | 41             | I   | ST     | Interrupt-on-Change Inputs |

| CN27     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I   | ST     | Interrupt-on-Change Inputs |

| CN28     | —                                | —                                |               | 36                     | 39             | —                                |                                  | —             | 36                     | 39             | I   | ST     | Interrupt-on-Change Inputs |

| CN29     | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | I   | ST     | Interrupt-on-Change Inputs |

| CN30     | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I   | ST     | Interrupt-on-Change Inputs |

| CN31     | —                                | —                                |               | 26                     | 28             | —                                |                                  | —             | 26                     | 28             | I   | ST     | Interrupt-on-Change Inputs |

| CN32     | —                                | —                                |               | 25                     | 27             | —                                |                                  | —             | 25                     | 27             | I   | ST     | Interrupt-on-Change Inputs |

| CN33     | —                                | —                                |               | 32                     | 35             | —                                |                                  | —             | 32                     | 35             | I   | ST     | Interrupt-on-Change Inputs |

| CN34     | _                                | _                                | _             | 35                     | 38             | _                                |                                  | _             | 35                     | 38             | I   | ST     | Interrupt-on-Change Inputs |

| CN35     | _                                | _                                | _             | 12                     | 13             | _                                |                                  | _             | 12                     | 13             | I   | ST     | Interrupt-on-Change Inputs |

| CN36     | _                                | _                                | _             | 13                     | 14             | _                                |                                  | _             | 13                     | 14             | I   | ST     | Interrupt-on-Change Inputs |

| CTCMP    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input      |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

### 2.4 Voltage Regulator Pin (VCAP)

| Note: | This section |          | appli   | applies |    |     | to   |

|-------|--------------|----------|---------|---------|----|-----|------|

|       | PIC24FV16KM  |          | devices | with    | an | on- | chip |

|       | voltage      | regulato | or.     |         |    |     |      |

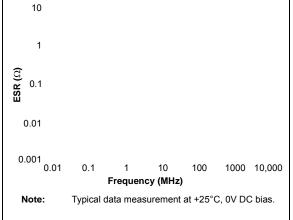

Some of the PIC24FV16KM devices have an internal voltage regulator. These devices have the voltage regulator output brought out on the VCAP pin. On the PIC24F K devices with regulators, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the voltage regulator output. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 27.0** "**Electrical Characteristics**" for additional information. Refer to **Section 27.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

### FIGURE 2-3: FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

### TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance Base Tolerance |      | Rated Voltage | Temp. Range   |

|-----------|--------------------|---------------------------------------|------|---------------|---------------|

| TDK       | C3216X7R1C106K     | 10 µF                                 | ±10% | 16V           | -55 to +125°C |

| TDK       | C3216X5R1C106K     | 10 µF                                 | ±10% | 16V           | -55 to +85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                                 | ±10% | 16V           | -55 to +125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                                 | ±10% | 16V           | -55 to +85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                                 | ±10% | 16V           | -55 to +125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                                 | ±10% | 16V           | -55 to +85°C  |

### 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Flash programming, refer to the "PIC24F Family Reference Manual", "Program Memory" (DS39715).

The PIC24FV16KM204 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FXXXXX device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program Mode Entry Voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self-Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

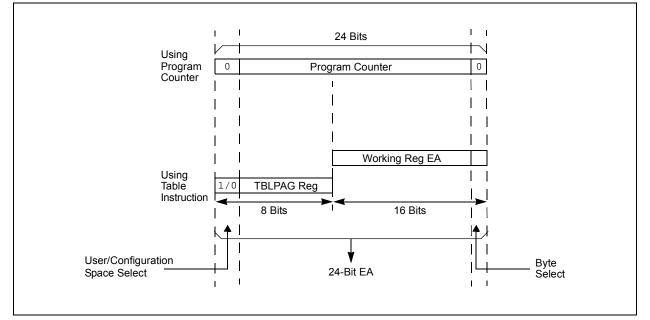

### 5.1 Table Instructions and Flash Programming

Regardless of the method used, Flash memory programming is done with the Table Read and Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | —   | —   | —   | —     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

|            |       |       |                        |     |     |     |       |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearable bit |                  |  |  |

|----------------------|------------------------|-----------------------------|------------------|--|--|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit            | W = Writable bit |  |  |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit, rea  | d as '0'         |  |  |

| bit 15   | WR: Write Control bit                                                                                                                                                                                                        |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Initiates a Flash memory program or erase operation; the operation is self-timed and the bit is                                                                                                                          |

|          | cleared by hardware once the operation is complete                                                                                                                                                                           |

|          | <ul><li>0 = Program or erase operation is complete and inactive</li></ul>                                                                                                                                                    |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                       |

|          | 1 = Enables Flash program/erase operations                                                                                                                                                                                   |

|          | 0 = Inhibits Flash program/erase operations                                                                                                                                                                                  |

| bit 13   | WRERR: Write Sequence Error Flag bit                                                                                                                                                                                         |

|          | 1 = An improper program or erase sequence attempt, or termination has occurred (bit is set automatically                                                                                                                     |

|          | on any set attempt of the WR bit)                                                                                                                                                                                            |

|          | 0 = The program or erase operation completed normally                                                                                                                                                                        |

| bit 12   | PGMONLY: Program Only Enable bit <sup>(4)</sup>                                                                                                                                                                              |

| bit 11-7 | Unimplemented: Read as '0'                                                                                                                                                                                                   |

| bit 6    | ERASE: Erase/Program Enable bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Performs the erase operation specified by the NVMOP&lt;5:0&gt; bits on the next WR command</li> <li>0 = Performs the program operation specified by the NVMOP&lt;5:0&gt; bits on the next WR command</li> </ul> |

| bit 5-0  | NVMOP<5:0>: Programming Operation Command Byte bits <sup>(1)</sup>                                                                                                                                                           |

|          | Erase Operations (when ERASE bit is '1'):                                                                                                                                                                                    |

|          | 1010xx = Erase entire boot block (including code-protected boot block) <sup>(2)</sup>                                                                                                                                        |

|          | 1001xx = Erase entire memory (including boot block, configuration block, general block) <sup>(2)</sup>                                                                                                                       |

|          | 011010 = Erase 4 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                         |

|          | 011001 = Erase 2 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                         |

|          | 011000 = Erase 1 row of Flash memory <sup>(3)</sup>                                                                                                                                                                          |

|          | 0101xx = Erase entire configuration block (except code protection bits)                                                                                                                                                      |

|          | 0100xx = Erase entire data EEPROM <sup>(4)</sup>                                                                                                                                                                             |

|          | 0011xx = Erase entire general memory block programming operations                                                                                                                                                            |

|          | 0001xx = Write 1 row of Flash memory (when ERASE bit is '0') <sup>(3)</sup>                                                                                                                                                  |

| Note 1:  | All other combinations of NVMOP<5:0> are no operation.                                                                                                                                                                       |

| 2:       | Available in ICSP™ mode only. Refer to the device programming specification.                                                                                                                                                 |

| 2.       | The address in the Table Deinter decides which rows will be created                                                                                                                                                          |

- 3: The address in the Table Pointer decides which rows will be erased.

- 4: This bit is used only while accessing data EEPROM.

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| —     | —   | —   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | —     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:       |                              | HS = Hardware Settable bi                                                                                | t                      |                    |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------|------------------------|--------------------|

| R = Readabl   | e bit                        | W = Writable bit                                                                                         | U = Unimplemented bit, | read as '0'        |

| -n = Value at | POR                          | '1' = Bit is set                                                                                         | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15        | 1 = Interru                  | Interrupt Nesting Disable bit<br>Ipt nesting is disabled                                                 |                        |                    |

| bit 14-5      |                              | ipt nesting is enabled<br>nented: Read as '0'                                                            |                        |                    |

| bit 4         | <b>MATHERI</b><br>1 = Overfl | R: Arithmetic Error Trap Status t<br>ow trap has occurred<br>ow trap has not occurred                    | bit                    |                    |

| bit 3         | 1 = Addre                    | R: Address Error Trap Status bit<br>ss error trap has occurred<br>ss error trap has not occurred         |                        |                    |

| bit 2         | 1 = Stack                    | Stack Error Trap Status bit<br>error trap has occurred<br>error trap has not occurred                    |                        |                    |

| bit 1         | 1 = Oscilla                  | Oscillator Failure Trap Status t<br>ator failure trap has occurred<br>ator failure trap has not occurred |                        |                    |

| bit 0         | Unimplen                     | nented: Read as '0'                                                                                      |                        |                    |

| U-0          | R/W-1                                                                          | R/W-0                                | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|--------------|--------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|---------|--|--|--|

| —            | CCT1IP2                                                                        | CCT1IP1                              | CCT1IP0        | —                 | CCP4IP2          | CCP4IP1         | CCP4IP0 |  |  |  |

| bit 15       |                                                                                |                                      |                |                   |                  |                 | bit 8   |  |  |  |

| U-0          | R/W-1                                                                          | R/W-0                                | R/W-0          | U-0               | U-0              | U-0             | U-0     |  |  |  |

|              | CCP3IP2                                                                        | CCP3IP1                              | CCP3IP0        |                   |                  |                 |         |  |  |  |

| bit 7        | 0010112                                                                        |                                      |                |                   |                  |                 | bit 0   |  |  |  |

|              |                                                                                |                                      |                |                   |                  |                 |         |  |  |  |

| Legend:      |                                                                                |                                      |                |                   |                  |                 |         |  |  |  |

| R = Readab   | ole bit                                                                        | W = Writable                         | bit            | U = Unimplen      | nented bit, read | l as '0'        |         |  |  |  |

| -n = Value a | at POR                                                                         | '1' = Bit is set                     |                | '0' = Bit is cle  | ared             | x = Bit is unkn | iown    |  |  |  |

|              |                                                                                |                                      |                |                   |                  |                 |         |  |  |  |

| bit 15       | -                                                                              | ted: Read as '                       |                |                   |                  |                 |         |  |  |  |

| bit 14-12    | CCT1IP<2:0>                                                                    | : Capture/Com                        | pare 1 Timer I | nterrupt Priority | / bits           |                 |         |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                     |                                      |                |                   |                  |                 |         |  |  |  |

|              | •                                                                              |                                      |                |                   |                  |                 |         |  |  |  |

|              | •                                                                              |                                      |                |                   |                  |                 |         |  |  |  |

|              | 001 = Interrupt is Priority 1                                                  |                                      |                |                   |                  |                 |         |  |  |  |

|              | •                                                                              | pt source is dis                     |                |                   |                  |                 |         |  |  |  |

| bit 11       | -                                                                              | ted: Read as '                       |                |                   |                  |                 |         |  |  |  |

| bit 10-8     | CCP4IP<2:0>: Capture/Compare 4 Event Interrupt Priority bits                   |                                      |                |                   |                  |                 |         |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                     |                                      |                |                   |                  |                 |         |  |  |  |

|              | •                                                                              |                                      |                |                   |                  |                 |         |  |  |  |

|              | •                                                                              |                                      |                |                   |                  |                 |         |  |  |  |

|              | 001 = Interrupt is Priority 1                                                  |                                      |                |                   |                  |                 |         |  |  |  |

|              | -                                                                              | pt source is dis                     |                |                   |                  |                 |         |  |  |  |

| bit 7        | -                                                                              | ted: Read as '                       |                |                   |                  |                 |         |  |  |  |

| bit 6-4      | CCP3IP<2:0>: Capture/Compare 3 Event Interrupt Priority bits                   |                                      |                |                   |                  |                 |         |  |  |  |

|              | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul> |                                      |                |                   |                  |                 |         |  |  |  |

|              | •                                                                              |                                      |                |                   |                  |                 |         |  |  |  |

|              | •                                                                              |                                      |                |                   |                  |                 |         |  |  |  |

|              | 001 = Interru                                                                  | pt is Priority 1<br>pt source is dis | ablad          |                   |                  |                 |         |  |  |  |

| bit 3-0      | •                                                                              | ted: Read as '                       |                |                   |                  |                 |         |  |  |  |

| DIL 3-0      | Unimplemen                                                                     | ieu: Reau as                         | J              |                   |                  |                 |         |  |  |  |

### REGISTER 8-20: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

|              |                                                                                        |                                                                                                                                                                                                                                                                                                 | -                          |                   |                  |                 |         |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

| U-0          | U-0                                                                                    | U-0                                                                                                                                                                                                                                                                                             | U-0                        | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

| _            | _                                                                                      | _                                                                                                                                                                                                                                                                                               | _                          | _                 | BCL2IP2          | BCL2IP1         | BCL2IP0 |  |  |  |  |  |

| oit 15       |                                                                                        | BCL2IP2BCL2IP1R/W-0R/W-0U-0U-0U-02SSP2IP1SSP2IP0W = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknowmented: Read as '0'2:0>: MSSP2 I <sup>2</sup> CTM Bus Collision Interrupt Priority bitserrupt is Priority 7 (highest priority interrupt) | bit 8                      |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                        |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

| U-0          | R/W-1                                                                                  | R/W-0                                                                                                                                                                                                                                                                                           | R/W-0                      | U-0               | U-0              | U-0             | U-0     |  |  |  |  |  |

| —            | SSP2IP2                                                                                | SSP2IP1                                                                                                                                                                                                                                                                                         | SSP2IP0                    |                   | —                | —               | —       |  |  |  |  |  |

| bit 7        |                                                                                        |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 | bit 0   |  |  |  |  |  |

|              |                                                                                        |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

| Legend:      |                                                                                        |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

| R = Readab   | ole bit                                                                                | W = Writable                                                                                                                                                                                                                                                                                    | bit                        | U = Unimplei      | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a | at POR                                                                                 | '1' = Bit is set                                                                                                                                                                                                                                                                                |                            | '0' = Bit is cle  | eared            | x = Bit is unkr | nown    |  |  |  |  |  |

|              |                                                                                        |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

| bit 15-11    | Unimplemented: Read as '0'                                                             |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

| bit 10-8     | BCL2IP<2:0>: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Priority bits |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

|              | 111 = Interru                                                                          | pt is Priority 7(                                                                                                                                                                                                                                                                               | highest priority           | / interrupt)      |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                                          |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

|              | 000 = Interru                                                                          | pt source is dis                                                                                                                                                                                                                                                                                | abled                      |                   |                  |                 |         |  |  |  |  |  |

| bit 7        | Unimplemen                                                                             | nted: Read as '                                                                                                                                                                                                                                                                                 | o'                         |                   |                  |                 |         |  |  |  |  |  |

| bit 6-4      | SSP2IP<2:0>                                                                            | SPI/I SPI/I                                                                                                                                                                                                                                                                                     | <sup>2</sup> C Event Inter | rupt Priority bit | ts               |                 |         |  |  |  |  |  |

|              | 111 = Interru                                                                          | pt is Priority 7 (                                                                                                                                                                                                                                                                              | highest priority           | / interrupt)      |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interru                                                                          | pt is Priority 1                                                                                                                                                                                                                                                                                |                            |                   |                  |                 |         |  |  |  |  |  |

|              | 000 = Interru                                                                          | pt source is dis                                                                                                                                                                                                                                                                                | abled                      |                   |                  |                 |         |  |  |  |  |  |

| bit 3-0      | Unimplemen                                                                             | ted: Read as '                                                                                                                                                                                                                                                                                  | כ'                         |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                        |                                                                                                                                                                                                                                                                                                 |                            |                   |                  |                 |         |  |  |  |  |  |

### REGISTER 8-28: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0                          | U-0                                      | U-0                                                                                                                                     | U-0                             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|---------|

| _                            |                                          |                                                                                                                                         |                                 |                  | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| oit 15                       |                                          |                                                                                                                                         | •                               |                  |                  | •               | bit 8   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| U-0                          | R/W-1                                    | R/W-0                                                                                                                                   | R/W-0                           | U-0              | U-0              | U-0             | U-0     |

| —                            | U1ERIP2                                  | U1ERIP1                                                                                                                                 | U1ERIP0                         | —                | —                | —               | —       |

| bit 7                        |                                          |                                                                                                                                         |                                 |                  |                  |                 | bit 0   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| Legend:                      |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| R = Readab                   | ole bit                                  | W = Writable                                                                                                                            | bit                             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value a                 | at POR                                   | '1' = Bit is set                                                                                                                        |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8<br>bit 7<br>bit 6-4 | <pre>111 = Interru </pre>                | >: UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>>: UART1 Error<br>pt is Priority 7 ( | highest priority<br>abled<br>o' | interrupt)       |                  |                 |         |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '                                                             | abled                           | interrupt)       |                  |                 |         |

### REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0        | U-0                                 | U-0                                                  | U-0              | U-0                              | U-0              | U-0               | U-0      |  |  |  |  |  |

|------------|-------------------------------------|------------------------------------------------------|------------------|----------------------------------|------------------|-------------------|----------|--|--|--|--|--|

| _          | _                                   |                                                      | _                | _                                | —                | _                 |          |  |  |  |  |  |

| bit 15     | ·                                   |                                                      | ·                |                                  |                  |                   | bit      |  |  |  |  |  |

|            |                                     |                                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

| R/W-0      |                                     | R-0                                                  | R-0              | R-0                              | R-0              | R-0               | R-0      |  |  |  |  |  |

| SMP        | CKE                                 | D/A                                                  | P <sup>(1)</sup> | S <sup>(1)</sup>                 | R/W              | UA                | BF       |  |  |  |  |  |

| bit 7      |                                     |                                                      |                  |                                  |                  |                   | bit      |  |  |  |  |  |

| Legend:    |                                     |                                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

| R = Read   | able bit                            | W = Writable                                         | bit              | U = Unimpler                     | nented bit, read | d as '0'          |          |  |  |  |  |  |

| -n = Value | at POR                              | '1' = Bit is se                                      | t                | '0' = Bit is cle                 | ared             | x = Bit is unkn   | iown     |  |  |  |  |  |

|            |                                     |                                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

| bit 15-8   | Unimplemen                          | ted: Read as                                         | 0'               |                                  |                  |                   |          |  |  |  |  |  |

| bit 7      | SMP: Slew R                         | ate Control bit                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

|            | In Master or S                      |                                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

|            |                                     |                                                      |                  | ard Speed mode                   |                  | I 1 MHz)          |          |  |  |  |  |  |

| bit 6      | CKE: SMBus                          |                                                      |                  |                                  | (0 KHZ)          |                   |          |  |  |  |  |  |

| DIL O      | In Master or S                      |                                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

|            |                                     | SMBus-specific                                       | c inputs         |                                  |                  |                   |          |  |  |  |  |  |

|            | 0 = Disables                        | 0 = Disables SMBus-specific inputs                   |                  |                                  |                  |                   |          |  |  |  |  |  |

| bit 5      | D/A: Data/Ad                        | D/A: Data/Address bit                                |                  |                                  |                  |                   |          |  |  |  |  |  |

|            | <u>In Master mo</u><br>Reserved.    | <u>de:</u>                                           |                  |                                  |                  |                   |          |  |  |  |  |  |

|            | In Slave mod                        |                                                      | (                |                                  |                  |                   |          |  |  |  |  |  |

|            |                                     |                                                      |                  | transmitted wa<br>transmitted wa |                  |                   |          |  |  |  |  |  |

| bit 4      | P: Stop bit <sup>(1)</sup>          |                                                      |                  |                                  | 5 4441055        |                   |          |  |  |  |  |  |

| bit 4      |                                     | 1 = Indicates that a Stop bit has been detected last |                  |                                  |                  |                   |          |  |  |  |  |  |

|            |                                     | vas not detecte                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

| bit 3      | S: Start bit <sup>(1)</sup>         |                                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

|            |                                     | that a Start bit<br>vas not detecte                  |                  | ected last                       |                  |                   |          |  |  |  |  |  |

| bit 2      | R/W: Read/W                         | Vrite Informatio                                     | n bit            |                                  |                  |                   |          |  |  |  |  |  |

|            | In Slave mod                        | <u>e:</u> (2)                                        |                  |                                  |                  |                   |          |  |  |  |  |  |

|            | 1 = Read                            |                                                      |                  |                                  |                  |                   |          |  |  |  |  |  |

|            | 0 = Write<br>In Master mo           | do.(3)                                               |                  |                                  |                  |                   |          |  |  |  |  |  |

|            |                                     | is in progress                                       |                  |                                  |                  |                   |          |  |  |  |  |  |

|            |                                     | is not in progre                                     | ess              |                                  |                  |                   |          |  |  |  |  |  |

| bit 1      | UA: Update /                        | Address bit (10                                      | -Bit Slave mod   | le only)                         |                  |                   |          |  |  |  |  |  |

|            |                                     | that the user r<br>does not need                     |                  | e the address ir                 | the SSPxADE      | ) register        |          |  |  |  |  |  |

| Note 1:    | This bit is cleared                 | d on Reset and                                       | when SSPEN       | is cleared.                      |                  |                   |          |  |  |  |  |  |

| 2:         | This bit holds the address match to |                                                      |                  |                                  | ss match. This   | bit is only valid | from the |  |  |  |  |  |

| 3:         | ORing this bit wit                  | h SEN, RSEN,                                         | PEN. RCEN        | or ACKEN will in                 | ndicate if the M | SSPx is in Activ  | ve mode  |  |  |  |  |  |

### REGISTER 14-2: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

### 15.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated 16-bit Baud Rate Generator (BRG). The UxBRG register controls the period of a free-running, 16-bit timer. Equation 15-1 provides the formula for computation of the baud rate with BRGH = 0.

### EQUATION 15-1: UARTX BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$   $UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$ Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 15-1 provides the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 15-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 15-2: UARTx BAUD RATE WITH BRGH = $1^{(1)}$

|      | Ba | ud Rate = | $\frac{FCY}{4 \bullet (UxBRG + 1)}$ |          |

|------|----|-----------|-------------------------------------|----------|

|      | Ux | BRG =     | FCY<br>4 • Baud Rate                | - 1      |

| Note | 1: |           | n Fcy = Fosc/2; D<br>are disabled.  | oze mode |

The maximum baud rate (BRGH = 1) possible is FcY/4 (for UxBRG = 0) and the minimum baud rate possible is FcY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

### EXAMPLE 15-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate    | =   | FCY/(16 (UxBRG + 1))                                                                  |

|----------------------|-----|---------------------------------------------------------------------------------------|

| Solving for UxBRG va | lue | :                                                                                     |

| UxBRG<br>UxBRG       | =   | ((FCY/Desired Baud Rate)/16) – 1<br>((4000000/9600)/16) – 1                           |

| UxBRG                |     | 25                                                                                    |

| Calculated Baud Rate |     | 4000000/(16 (25 + 1))<br>9615                                                         |

| Error                |     | (Calculated Baud Rate – Desired Baud Rate)<br>Desired Baud Rate<br>(9615 – 9600)/9600 |

|                      | =   | 0.16%                                                                                 |

| Note 1: Based on     | Fc  | Y = FOSC/2; Doze mode and PLL are disabled.                                           |

### REGISTER 16-11: RTCCSWT: RTCC CONTROL/SAMPLE WINDOW TIMER REGISTER<sup>(1)</sup>

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSTAB7 | PWCSTAB6 | PWCSTAB5 | PWCSTAB4 | PWCSTAB3 | PWCSTAB2 | PWCSTAB1 | PWCSTAB0 |

| bit 15   | •        |          |          |          |          |          | bit 8    |

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSAMP7 | PWCSAMP6 | PWCSAMP5 | PWCSAMP4 | PWCSAMP3 | PWCSAMP2 | PWCSAMP1 | PWCSAMP0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| 01010-8 | PWCSTAB<7:0>: PWW Stability Window Timer bits                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11111111 = Stability window is 255 TPWCCLK clock periods                                                                                                                                                    |

|         |                                                                                                                                                                                                             |

|         |                                                                                                                                                                                                             |

|         |                                                                                                                                                                                                             |

|         | 00000000 = Stability window is 0 TPWCCLK clock periods                                                                                                                                                      |

|         | The sample window starts when the alarm event triggers. The stability window timer starts counting from every alarm event when PWCEN = 1.                                                                   |

| bit 7-0 | PWCSAMP<7:0>: PWM Sample Window Timer bits                                                                                                                                                                  |

|         | 11111111 = Sample window is always enabled, even when PWCEN = 0                                                                                                                                             |

|         | 11111110 = Sample window is 254 TPWCCLK clock periods                                                                                                                                                       |

|         |                                                                                                                                                                                                             |

|         |                                                                                                                                                                                                             |

|         |                                                                                                                                                                                                             |

|         | 00000000 = Sample window is 0 TPWCCLK clock periods                                                                                                                                                         |

|         | The sample window timer starts counting at the end of the stability window when PWCEN = 1. If $PWCSTAB<7:0> = 00000000$ , the sample window timer starts counting from every alarm event when $PWCEN = 1$ . |

|         |                                                                                                                                                                                                             |

### 16.3 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value, loaded into the lower half of RCFGCAL, is multiplied by four and will be either added or subtracted from the RTCC timer, once every minute. Refer to the steps below for RTCC calibration:

- 1. Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- 2. Once the error is known, it must be converted to the number of error clock pulses per minute.

- 3. a) If the oscillator is faster than ideal (negative result from Step 2), the RCFGCAL register value must be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

b) If the oscillator is slower than ideal (positive result from Step 2), the RCFGCAL register value must be positive. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

### EQUATION 16-1:

| (Ideal Frequency <sup>†</sup> – Measured Frequency) * |  |

|-------------------------------------------------------|--|

| 60 = Clocks per Minute                                |  |

| † Ideal Frequency = 32,768 Hz                         |  |

Writes to the lower half of the RCFGCAL register should only occur when the timer is turned off, or immediately after the rising edge of the seconds pulse, except when SECONDS = 00, 15, 30 or 45. This is due to the auto-adjust of the RTCC at 15 second intervals.

**Note:** It is up to the user to include, in the error value, the initial error of the crystal: drift due to temperature and drift due to crystal aging.

### 16.4 Alarm

- Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>)

- One-time alarm and repeat alarm options are available

### 16.4.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVAL should only take place when ALRMEN = 0.

As shown in Figure 16-2, the interval selection of the alarm is configured through the AMASKx bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The amount of times this occurs, once the alarm is enabled, is stored in the ARPT<7:0> bits (ALCFGRPT<7:0>). When the value of the ARPTx bits equals 00h and the CHIME bit (ALCFGRPT<14>) is cleared, the repeat function is disabled, and only a single alarm will occur. The alarm can be repeated up to 255 times by loading ARPT<7:0> with FFh.

After each alarm is issued, the value of the ARPTx bits is decremented by one. Once the value has reached 00h, the alarm will be issued one last time, after which, the ALRMEN bit will be cleared automatically and the alarm will turn off.

Indefinite repetition of the alarm can occur if the CHIME bit = 1. Instead of the alarm being disabled when the value of the ARPTx bits reaches 00h, it rolls over to FFh and continues counting indefinitely while CHIME is set.

### 16.4.2 ALARM INTERRUPT

At every alarm event, an interrupt is generated. In addition, an alarm pulse output is provided that operates at half the frequency of the alarm. This output is completely synchronous to the RTCC clock and can be used as a Trigger clock to other peripherals.

Note: Changing any of the registers, other than the RCFGCAL and ALCFGRPT registers, and the CHIME bit while the alarm is enabled (ALRMEN = 1), can result in a false alarm event leading to a false alarm interrupt. To avoid a false alarm event, the timer and alarm values should only be changed while the alarm is disabled (ALRMEN = 0). It is recommended that the ALCFGRPT register and CHIME bit be changed when RTCSYNC = 0.

| FIGURE 16-2:                 | ALARM MASK SE            | ITINGS                |                |     |       |         |         |

|------------------------------|--------------------------|-----------------------|----------------|-----|-------|---------|---------|

| Alarm Mas<br>(AMASK          | k Setting<br><<3:0>)     | Day of<br>the<br>Week | Month          | Day | Hours | Minutes | Seconds |

| 0000 - Every<br>0001 - Every |                          |                       |                |     |       |         |         |

| 0010 - Every                 | 10 seconds               |                       |                |     |       |         | s       |

| 0011 - Every                 | minute                   |                       |                |     |       |         | SS      |