Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                              |

|---------------------------|------------------------------------------------------------------------------|

| Product Status            | Active                                                                       |

| Core Processor            | PIC                                                                          |

| Core Size                 | 16-Bit                                                                       |

| Speed                     | 32MHz                                                                        |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| eripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| lumber of I/O             | 38                                                                           |

| rogram Memory Size        | 16KB (5.5K x 24)                                                             |

| ogram Memory Type         | FLASH                                                                        |

| EPROM Size                | 512 x 8                                                                      |

| AM Size                   | 2K x 8                                                                       |

| oltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| ata Converters            | A/D 22x10b/12b; D/A 2x8b                                                     |

| scillator Type            | Internal                                                                     |

| perating Temperature      | -40°C ~ 125°C (TA)                                                           |

| ounting Type              | Surface Mount                                                                |

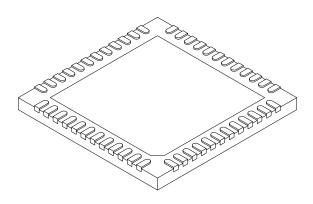

| ackage / Case             | 48-UFQFN Exposed Pad                                                         |

| upplier Device Package    | 48-UQFN (6x6)                                                                |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km204-e-mv |

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| _     | _   | _   | _   | IPL3 <sup>(1)</sup> | PSV   | _   |       |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settat  | HSC = Hardware Settable/Clearable bit |  |  |  |  |

|-------------------|-------------------|------------------------|---------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'                           |  |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown                    |  |  |  |  |

bit 15-4 **Unimplemented:** Read as '0'

bit 3 **IPL3:** CPU Interrupt Priority Level Status bit<sup>(1)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

bit 2 **PSV:** Program Space Visibility in Data Space Enable bit

1 = Program space is visible in Data Space0 = Program space is not visible in Data Space

bit 1-0 **Unimplemented:** Read as '0'

**Note 1:** User interrupts are disabled when IPL3 = 1.

### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### TABLE 4-9: MCCP2 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14                       | Bit 13               | Bit 12               | Bit 11               | Bit 10               | Bit 9                | Bit 8                | Bit 7       | Bit 6        | Bit 5   | Bit 4                 | Bit 3   | Bit 2   | Bit 1                  | Bit 0                  | All<br>Resets |

|-----------|-------|---------|------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------------|--------------|---------|-----------------------|---------|---------|------------------------|------------------------|---------------|

| CCP2CON1L | 164h  | CCPON   |                              | CCPSIDL              | r                    | TMRSYNC              | CLKSEL2              | CLKSEL1              | CLKSEL0              | TMRPS1      | TMRPS0       | T32     | CCSEL                 | MOD3    | MOD2    | MOD1                   | MOD0                   | 0000          |

| CCP2CON1H | 166h  | OPSSRC  | RTRGEN                       | ĺ                    | 1                    | IOPS3                | IOPS2                | IOPS1                | IOPS0                | TRIGEN      | ONESHOT      | ALTSYNC | SYNC4                 | SYNC3   | SYNC2   | SYNC1                  | SYNC0                  | 0000          |

| CCP2CON2L | 168h  | PWMRSEN | ASDGM                        | ĺ                    | SSDG                 | 1                    | _                    | _                    | 1                    | ASDG7       | ASDG6        | ASDG5   | ASDG4                 | ASDG3   | ASDG2   | ASDG1                  | ASDG0                  | 0000          |

| CCP2CON2H | 16Ah  | OENSYNC | 1                            | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN                | ICGSM1      | ICGSM0       | 1       | AUXOUT1               | AUXOUT0 | ICSEL2  | ICSEL1                 | ICSEL0                 | 0100          |

| CCP2CON3L | 16Ch  | -       | 1                            | ĺ                    | 1                    | 1                    | _                    | _                    | 1                    | 1           |              | DT5     | DT4                   | DT3     | DT2     | DT1                    | DT0                    | 0000          |

| CCP2CON3H | 16Eh  | OETRIG  | OSCNT2                       | OSCNT1               | OSCNT0               | 1                    | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> | 1           | _            | POLACE  | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> | 0000          |

| CCP2STATL | 170h  | -       | 1                            | ĺ                    | 1                    | 1                    | _                    | _                    | 1                    | CCPTRIG     | TRSET        | TRCLR   | ASEVT                 | SCEVT   | ICDIS   | ICOV                   | ICBNE                  | 0000          |

| CCP2TMRL  | 174h  |         |                              |                      |                      |                      |                      | MCC                  | P2 Time Ba           | se Registe  | r Low Word   |         |                       |         |         |                        |                        | 0000          |

| CCP2TMRH  | 176h  |         |                              |                      |                      |                      |                      | MCC                  | P2 Time Ba           | se Register | High Word    |         |                       |         |         |                        |                        | 0000          |

| CCP2PRL   | 178h  |         |                              |                      |                      |                      |                      | MCCP2                | Time Base            | Period Regi | ister Low Wo | rd      |                       |         |         |                        |                        | FFFF          |

| CCP2PRH   | 17Ah  |         |                              |                      |                      |                      |                      | MCCP2                | Time Base I          | Period Regi | ster High Wo | rd      |                       |         |         |                        |                        | FFFF          |

| CCP2RAL   | 17Ch  |         |                              |                      |                      |                      |                      | 0                    | utput Comp           | are 2 Data  | Word A       |         |                       |         |         |                        |                        | 0000          |

| CCP2RBL   | 180h  |         | Output Compare 2 Data Word B |                      |                      |                      |                      |                      |                      |             |              |         | 0000                  |         |         |                        |                        |               |

| CCP2BUFL  | 184h  |         |                              |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer | Low Word     |         |                       |         |         |                        |                        | 0000          |

| CCP2BUFH  | 186h  |         |                              |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer | High Word    |         |                       |         |         |                        |                        | 0000          |

PIC24FV16KM204 FAMILY

**Legend:** x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

#### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|---------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY | _   | _   | _   |       |

| bit 15     |       |       |         |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|--------|--------|--------|--------|--------|--------|

| _     | ERASE | NVMOP5 | NVMOP4 | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 |

| bit 7 |       |        |        |        |        |        | bit 0  |

| Legend:           | HC = Hardware Clearable bit U = Unimplemented bit, read as '0' |                       | ead as '0'         |

|-------------------|----------------------------------------------------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit                                               | S = Settable Only bit |                    |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 WR: Write Control bit (program or erase)

1 = Initiates a data EEPROM erase or write cycle (can be set, but not cleared in software)

0 = Write cycle is complete (cleared automatically by hardware)

bit 14 WREN: Write Enable bit (erase or program)

1 = Enables an erase or program operation

0 = No operation allowed (device clears this bit on completion of the write/erase operation)

bit 13 WRERR: Flash Error Flag bit

1 = A write operation is prematurely terminated (any MCLR or WDT Reset during programming operation)

0 = The write operation completed successfully

bit 12 **PGMONLY:** Program Only Enable bit

1 = Write operation is executed without erasing target address(es) first

0 = Automatic erase-before-write

Write operations are preceded automatically by an erase of the target address(es).

bit 11-7 **Unimplemented:** Read as '0'

bit 6 **ERASE:** Erase Operation Select bit

1 = Performs an erase operation when WR is set

0 = Performs a write operation when WR is set

bit 5-0 **NVMOP<5:0>:** Programming Operation Command Byte bits

Erase Operations (when ERASE bit is '1'):

011010 = Erase 8 words

011001 = Erase 4 words

011000 **= Erase 1 word**

0100xx = Erase entire data EEPROM

Programming Operations (when ERASE bit is '0'):

0001xx = Write 1 word

#### 6.4.1.1 Data EEPROM Bulk Erase

To erase the entire data EEPROM (bulk erase), the address registers do not need to be configured because this operation affects the entire data EEPROM. The following sequence helps in performing a bulk erase:

- 1. Configure NVMCON to Bulk Erase mode.

- Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 3. Write the key sequence to NVMKEY.

- 4. Set the WR bit to begin the erase cycle.

- 5. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical bulk erase sequence is provided in Example 6-3.

#### 6.4.2 SINGLE-WORD WRITE

To write a single word in the data EEPROM, the following sequence must be followed:

- Erase one data EEPROM word (as mentioned in the previous section) if the PGMONLY bit (NVMCON<12>) is set to '1'.

- 2. Write the data word into the data EEPROM latch.

- 3. Program the data word into the EEPROM:

- Configure the NVMCON register to program one EEPROM word (NVMCON<5:0> = 0001xx).

- Clear the NVMIF status bit and enable the NVM interrupt (optional).

- Write the key sequence to NVMKEY.

- Set the WR bit to begin the erase cycle.

- Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

- To get cleared, wait until NVMIF is set.

A typical single-word write sequence is provided in Example 6-4.

#### **EXAMPLE 6-3: DATA EEPROM BULK ERASE**

```

// Set up NVMCON to bulk erase the data EEPROM

NVMCON = 0x4050;

// Disable Interrupts For 5 Instructions

asm volatile ("disi #5");

// Issue Unlock Sequence and Start Erase Cycle

__builtin_write_NVM();

```

#### EXAMPLE 6-4: SINGLE-WORD WRITE TO DATA EEPROM

```

int __attribute__ ((space(eedata))) eeData = 0x1234;

// New data to write to EEPROM

int newData;

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the write

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0x4004;

// Set up a pointer to the EEPROM location to be erased

// Initizlize lower word of address

offset = __builtin_tbloffset(&eeData);

__builtin_tblwtl(offset, newData);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

__builtin_write_NVM();

// Issue Unlock Sequence & Start Write Cycle

while(NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

### 7.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 7-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. For more information, see **Section 9.0 "Oscillator Configuration"**.

TABLE 7-2: OSCILLATOR SELECTION vs.

TYPE OF RESET (CLOCK

SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | FNOSC<2:0> Configuration bits |

| BOR        | (FOSCSEL<2:0>)                |

| MCLR       | COSC<2:0> Control bits        |

| WDTO       | (OSCCON<14:12>)               |

| SWR        |                               |

#### 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

TABLE 7-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

| Reset Type         | Clock Source | SYSRST Delay | System Clock<br>Delay | Notes      |

|--------------------|--------------|--------------|-----------------------|------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT | _                     | 1, 2       |

|                    | FRC, FRCDIV  | TPOR + TPWRT | TFRC                  | 1, 2, 3    |

|                    | LPRC         | TPOR + TPWRT | TLPRC                 | 1, 2, 3    |

|                    | ECPLL        | TPOR + TPWRT | TLOCK                 | 1, 2, 4    |

|                    | FRCPLL       | TPOR + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4 |

|                    | XT, HS, SOSC | TPOR+ TPWRT  | Tost                  | 1, 2, 5    |

|                    | XTPLL, HSPLL | TPOR + TPWRT | Tost + Tlock          | 1, 2, 4, 5 |

| BOR                | EC           | TPWRT        | _                     | 2          |

|                    | FRC, FRCDIV  | TPWRT        | TFRC                  | 2, 3       |

|                    | LPRC         | TPWRT        | TLPRC                 | 2, 3       |

|                    | ECPLL        | TPWRT        | TLOCK                 | 2, 4       |

|                    | FRCPLL       | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

|                    | XT, HS, SOSC | TPWRT        | Tost                  | 2, 5       |

|                    | XTPLL, HSPLL | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

| All Others         | Any Clock    | _            | _                     | None       |

**Note 1:** TPOR = Power-on Reset delay.

- 2: TPWRT = 64 ms nominal if the Power-up Timer is enabled; otherwise, it is zero.

- 3: TFRC and TLPRC = RC Oscillator start-up times.

- 4: TLOCK = PLL Lock time.

- **5:** Tost = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

- **6:** If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 27.0 "Electrical Characteristics".

#### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | R/W-0, HS |

|-----------|-----------|-----------|-----|-----|-----|-----|-----------|

| DAC2IF    | DAC1IF    | CTMUIF    | _   | _   | _   | _   | HLVDIF    |

| bit 15    |           |           |     |     |     |     | bit 8     |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| _     | _   | _   | _   | _   | U2ERIF    | U1ERIF    | _     |

| bit 7 |     |     |     |     |           |           | bit 0 |

**Legend:** HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 DAC2IF: Digital-to-Analog Converter 2 Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 14 DAC1IF: Digital-to-Analog Converter 1 Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 13 CTMUIF: CTMU Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 12-9 **Unimplemented:** Read as '0'

bit 8 **HLVDIF:** High/Low-Voltage Detect Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 7-3 Unimplemented: Read as '0'

bit 2 U2ERIF: UART2 Error Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 U1ERIF: UART1 Error Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 **Unimplemented:** Read as '0'

#### REGISTER 8-33: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | -   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1    | R/W-0    | R/W-0    |

|-------|-----|-----|-----|-----|----------|----------|----------|

| _     | _   | _   | _   | _   | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 |

| bit 7 |     |     |     |     |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 Unimplemented: Read as '0'

bit 2-0 **ULPWUIP<2:0>:** Ultra Low-Power Wake-up Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 8-34: IPC24: INTERRUPT PRIORITY CONTROL REGISTER 24

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| _     | CLC2IP2 | CLC2IP1 | CLC2IP0 | _   | CLC1IP2 | CLC1IP1 | CLC1IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-4 **CLC2IP<2:0>:** CLC2 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 **CLC1IP<2:0>:** CLC1 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 25.0 "Special Features"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

# 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically, as follows:

- The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware

if it is not currently running. If a crystal oscillator

must be turned on, the hardware will wait until

the OST expires. If the new source is using the

PLL, then the hardware waits until a PLL lock is

detected (LOCK = 1).

- The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT, FSCM or RTCC with LPRC as a clock source is enabled) or SOSC (if SOSCEN remains enabled).

- **Note 1:** The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

#### REGISTER 11-2: ANSB: PORTB ANALOG SELECTION REGISTER

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | U-0 | U-0 | R/W-1 | R/W-1 |

|--------|--------|--------|--------|-----|-----|-------|-------|

| ANSB15 | ANSB14 | ANSB13 | ANSB12 | _   | _   | ANSB9 | ANSB8 |

| bit 15 |        |        |        |     |     |       | bit 8 |

| R/W-1 | R/W-1                | R/W-1                | R/W-1 | R/W-1                | R/W-1 | R/W-1 | R/W-1 |

|-------|----------------------|----------------------|-------|----------------------|-------|-------|-------|

| ANSB7 | ANSB6 <sup>(1)</sup> | ANSB5 <sup>(1)</sup> | ANSB4 | ANSB3 <sup>(1)</sup> | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |                      |                      |       |                      |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 ANSB<15:12>: Analog Select Control bits

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

bit 11-10 Unimplemented: Read as '0'

bit 9-0 ANSB<9:0>: Analog Select Control bits<sup>(1)</sup>

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

**Note 1:** The ANSB<6:5,3> bits are not available on 20-pin devices.

#### REGISTER 11-3: ANSC: PORTC ANALOG SELECTION REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1                  | R/W-1                  | R/W-1                  |

|-------|-----|-----|-----|-----|------------------------|------------------------|------------------------|

| _     | _   | _   | _   | _   | ANSC2 <sup>(1,2)</sup> | ANSC1 <sup>(1,2)</sup> | ANSC0 <sup>(1,2)</sup> |

| bit 7 |     |     |     |     |                        |                        | bit 0                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0'

bit 2-0 ANSC<2:0>: Analog Select Control bits<sup>(1,2)</sup>

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

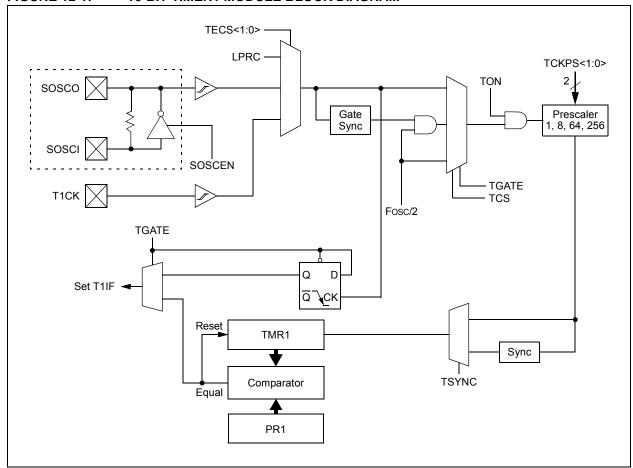

### 12.0 TIMER1

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on timers, refer to the "PIC24F Family Reference Manual", "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- · 16-Bit Timer

- · 16-Bit Synchronous Counter

- · 16-Bit Asynchronous Counter

Timer1 also supports these features:

- · Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- Set the TON bit (= 1).

- Select the timer prescaler ratio using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- Load the timer period value into the PR1 register.

- If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### REGISTER 13-2: CCPxCON1H: CCPx CONTROL 1 HIGH REGISTERS

| R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

|-----------------------|-----------------------|-----|-----|---------------------|---------------------|---------------------|---------------------|

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup> | _   | _   | OPS3 <sup>(3)</sup> | OPS2 <sup>(3)</sup> | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |

| bit 15                |                       |     |     |                     |                     |                     | bit 8               |

| R/W-0                 | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------------------|---------|---------|-------|-------|-------|-------|-------|

| TRIGEN <sup>(4)</sup> | ONESHOT | ALTSYNC | SYNC4 | SYNC3 | SYNC2 | SYNC1 | SYNC0 |

| bit 7                 |         |         |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **OPSSRC:** Output Postscaler Source Select bit<sup>(1)</sup>

1 = Output postscaler scales module Trigger output events

0 = Output postscaler scales time base interrupt events

bit 14 RTRGEN: Retrigger Enable bit<sup>(2)</sup>

1 = Time base can be retriggered when TRIGEN bit = 1

0 = Time base may not be retriggered when TRIGEN bit = 1

bit 13-12 **Unimplemented:** Read as '0'

bit 11-8 **OPS3<3:0>:** CCPx Interrupt Output Postscale Select bits<sup>(3)</sup>

1111 = Interrupt every 16th time base period match

1110 = Interrupt every 15th time base period match

• • •

0100 = Interrupt every 5th time base period match

0011 = Interrupt every 4th time base period match or 4th input capture event

0010 = Interrupt every 3rd time base period match or 3rd input capture event

0001 = Interrupt every 2nd time base period match or 2nd input capture event

0000 = Interrupt after each time base period match or input capture event

bit 7 TRIGEN: CCPx Trigger Enable bit<sup>(4)</sup>

1 = Trigger operation of time base is enabled

0 = Trigger operation of time base is disabled

bit 6 ONESHOT: One-Shot Mode Enable bit

1 = One-Shot Trigger mode is enabled; Trigger duration is set by OSCNT<2:0>

0 = One-Shot Trigger mode IS disabled

bit 5 ALTSYNC: CCPx Clock Select bits

1 = An alternate signal is used as the module synchronization output signal

0 = The module synchronization output signal is the Time Base Reset/rollover event

bit 4-0 SYNC<4:0>: CCPx Synchronization Source Select bits

See Table 13-6 for the definition of inputs.

Note 1: This control bit has no function in Input Capture modes.

2: This control bit has no function when TRIGEN = 0.

3: Output postscale settings from 1:5 to 1:16 (0100-1111) will result in a FIFO buffer overflow for Input Capture modes

4: Clock source options are limited when Trigger operation is enabled; refer to Table 13-1.

#### REGISTER 13-4: CCPxCON2H: CCPx CONTROL 2 HIGH REGISTERS

| R/W-0   | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0 |

|---------|-----|----------------------|----------------------|----------------------|----------------------|----------------------|-------|

| OENSYNC | _   | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN |

| bit 15  |     |                      |                      |                      |                      |                      | bit 8 |

| R/W-0  | R/W-0  | U-0 | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-----|---------|---------|-------|-------|-------|

| ICGSM1 | ICGSM0 | _   | AUXOUT1 | AUXOUT0 | ICS2  | ICS1  | ICS0  |

| bit 7  |        |     |         |         |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 **OENSYNC:** Output Enable Synchronization bit

1 = Update by output enable bits occurs on the next Time Base Reset or rollover

0 = Update by output enable bits occurs immediately

bit 14 Unimplemented: Read as '0'

bit 13-8 OC<F:A>EN: Output Enable/Steering Control bits<sup>(1)</sup>

1 = OCx pin is controlled by the CCPx module and produces an output compare or PWM signal

0 = OCx pin is not controlled by the CCPx module; the pin is available to the port logic or another peripheral multiplexed on the pin

bit 7-6 ICGSM<1:0>: Input Capture Gating Source Mode Control bits

11 = Reserved

10 = One-Shot mode: Falling edge from gating source disables future capture events (ICDIS = 1)

01 = One-Shot mode: Rising edge from gating source enables future capture events (ICDIS = 0)

00 = Level-Sensitive mode: A high level from gating source will enable future capture events; a low level will disable future capture events

bit 5 **Unimplemented:** Read as '0'

bit 4-3 AUXOUT<1:0>: Auxiliary Output Signal on Event Selection bits

11 = Input capture or output compare event; no signal in Timer mode

10 = Signal output is defined by module operating mode (see Table 13-5)

01 = Time base rollover event (all modes)

00 = Disabled

bit 2-0 ICS<2:0>: Input Capture Source Select bits

111 = Unused

110 = CLC2 output

101 = CLC1 output

100 = Unused

011 = Comparator 3 output

010 = Comparator 2 output

001 = Comparator 1 output

000 = Input Capture x (ICx) I/O pin

Note 1: OCFEN through OCBEN (bits<13:9>) are implemented in MCCPx modules only.

### REGISTER 16-2: RTCPWC: RTCC CONFIGURATION REGISTER 2<sup>(1)</sup>

| R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0                  | R/W-0                  | R/W-0   | R/W-0   |

|--------|--------|---------|---------|------------------------|------------------------|---------|---------|

| PWCEN  | PWCPOL | PWCCPRE | PWCSPRE | RTCCLK1 <sup>(2)</sup> | RTCCLK0 <sup>(2)</sup> | RTCOUT1 | RTCOUT0 |

| bit 15 |        |         |         |                        |                        |         | bit 8   |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **PWCEN:** Power Control Enable bit

1 = Power control is enabled

0 = Power control is disabled

bit 14 **PWCPOL:** Power Control Polarity bit

1 = Power control output is active-high

0 = Power control output is active-low

bit 13 PWCCPRE: Power Control/Stability Prescaler bits

1 = PWC stability window clock is divide-by-2 of source RTCC clock

0 = PWC stability window clock is divide-by-1 of source RTCC clock

bit 12 **PWCSPRE:** Power Control Sample Prescaler bits

1 = PWC sample window clock is divide-by-2 of source RTCC clock

0 = PWC sample window clock is divide-by-1 of source RTCC clock

bit 11-10 RTCCLK<1:0>: RTCC Clock Select bits(2)

Determines the source of the internal RTCC clock, which is used for all RTCC timer operations.

00 = External Secondary Oscillator (SOSC)

01 = Internal LPRC Oscillator

10 = External power line source - 50 Hz

11 = External power line source - 60 Hz

bit 9-8 RTCOUT<1:0>: RTCC Output Select bits

Determines the source of the RTCC pin output.

00 = RTCC alarm pulse

01 = RTCC seconds clock

10 = RTCC clock

11 = Power control

bit 7-0 **Unimplemented:** Read as '0'

**Note 1:** The RTCPWC register is only affected by a POR.

**2:** When a new value is written to these register bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

### REGISTER 16-6: WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| _      | _   |     | 1   | 1   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits

Contains a value from 0 to 6.

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits

Contains a value from 0 to 2.

bit 3-0 HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 16-7: MINSEC: MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| _      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits

Contains a value from 0 to 5.

bit 11-8 MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits

Contains a value from 0 to 9.

bit 7 **Unimplemented:** Read as '0'

bit 6-4 SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits

Contains a value from 0 to 5.

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits

Contains a value from 0 to 9.

#### REGISTER 18-1: **HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER**

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| HLVDEN | _   | HLSIDL | _   | _   | _   | _   | _     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-----|--------|--------|--------|--------|

| VDIR  | BGVST | IRVST | _   | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 |

| bit 7 |       |       |     |        |        |        | bit 0  |

Legend:

R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 HLVDEN: High/Low-Voltage Detect Power Enable bit

> 1 = HLVD is enabled 0 = HLVD is disabled

bit 14 Unimplemented: Read as '0'

bit 13 **HLSIDL:** HLVD Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 VDIR: Voltage Change Direction Select bit

1 = Event occurs when voltage equals or exceeds trip point (HLVDL<3:0>)

0 = Event occurs when voltage equals or falls below trip point (HLVDL<3:0>)

bit 6 **BGVST:** Band Gap Voltage Stable Flag bit

1 = Indicates that the band gap voltage is stable

0 = Indicates that the band gap voltage is unstable

bit 5 IRVST: Internal Reference Voltage Stable Flag bit

1 = Indicates that the internal reference voltage is stable and the High-Voltage Detect logic generates

the interrupt flag at the specified voltage range

0 = Indicates that the internal reference voltage is unstable and the High-Voltage Detect logic will not generate the interrupt flag at the specified voltage range, and the HLVD interrupt should not be

enabled

bit 4 Unimplemented: Read as '0'

bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits

1111 = External analog input is used (input comes from the HLVDIN pin)

1110 = Trip Point 1<sup>(1)</sup>

1101 = Trip Point 2<sup>(1)</sup>

1100 = Trip Point 3<sup>(1)</sup>

0000 = Trip Point 15<sup>(1)</sup>

Note 1: For the actual trip point, see Section 27.0 "Electrical Characteristics".

#### REGISTER 25-7: FICD: IN-CIRCUIT DEBUGGER CONFIGURATION REGISTER

| R/P-1 | U-0 | U-0 | U-0 | U-0 | U-0 | R/P-1 | R/P-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| DEBUG | _   | _   | _   | _   | _   | FICD1 | FICD0 |

| bit 7 |     |     |     |     |     |       | bit 0 |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **DEBUG:** Background Debugger Enable bit

1 = Background debugger is disabled

0 = Background debugger functions are enabled

bit 6-2 **Unimplemented:** Read as '0'

bit 1-0 FICD<1:0:>: ICD Pin Select bits

11 = PGEC1/PGED1 are used for programming and debugging the device

10 = PGEC2/PGED2 are used for programming and debugging the device

01 = PGEC3/PGED3 are used for programming and debugging the device

00 = Reserved; do not use

TABLE 27-12: DC CHARACTERISTICS: DATA EEPROM MEMORY

| DC CHA       | RACTER | RISTICS                                                 |         | d Operatino |     | / to 3.6V (PIC24F16KM204) / to 5.5V (PIC24FV16KM204) °C ≤ TA ≤ +85°C for Industrial °C ≤ TA ≤ +125°C for Extended |                                               |

|--------------|--------|---------------------------------------------------------|---------|-------------|-----|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Param<br>No. | Sym    | n Characteristic Min Typ <sup>(1)</sup> Max Units       |         |             |     |                                                                                                                   | Conditions                                    |

|              |        | Data EEPROM Memory                                      |         |             |     |                                                                                                                   |                                               |

| D140         | EPD    | Cell Endurance                                          | 100,000 | _           | _   | E/W                                                                                                               |                                               |

| D141         | VPRD   | VDD for Read                                            | VMIN    | _           | 3.6 | V                                                                                                                 | Vмін = Minimum operating<br>voltage           |

| D143A        | TIWD   | Self-Timed Write Cycle<br>Time                          | _       | 4           | _   | ms                                                                                                                |                                               |

| D143B        | TREF   | Number of Total<br>Write/Erase Cycles Before<br>Refresh | _       | 10M         | _   | E/W                                                                                                               |                                               |

| D144         | TRETDD | Characteristic Retention                                | 40      | _           | _   | Year                                                                                                              | Provided no other specifications are violated |

| D145         | IDDPD  | Supply Current During<br>Programming                    | _       | 7           | _   | mA                                                                                                                |                                               |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

### **TABLE 27-13: DC CHARACTERISTICS: COMPARATOR**

| DC CHARACTERISTICS |        |                             | Standard Operating Conditions: 1.8V to 3.6V (PIC24F16KM204) 2.0V to 5.5V (PIC24FV16KM204) Operating temperature $ \begin{array}{c} -40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C for Industrial} \\ -40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C for Extende} \end{array} $ |     |     |       |            |  |

|--------------------|--------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic              | Min                                                                                                                                                                                                                                                                                                     | Тур | Max | Units | Conditions |  |

| D300               | VIOFF  | Input Offset Voltage        | _                                                                                                                                                                                                                                                                                                       | 20  | 40  | mV    |            |  |

| D301               | VICM   | Input Common-Mode Voltage   | 0                                                                                                                                                                                                                                                                                                       | _   | VDD | V     |            |  |

| D302               | CMRR   | Common-Mode Rejection Ratio | 55                                                                                                                                                                                                                                                                                                      | _   | _   | dB    |            |  |

### TABLE 27-14: DC CHARACTERISTICS: COMPARATOR VOLTAGE REFERENCE

| DC CHARACTERISTICS |        |                         | Standard ( |     | re     | 1.8V to 3.6V (PIC24F16KM204) 2.0V to 5.5V (PIC24FV16KM204) $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                  |  |

|--------------------|--------|-------------------------|------------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| Param<br>No.       | Symbol | Characteristic          | Min        | Тур | Max    | Units                                                                                                                                                                                                           | Conditions       |  |

| VRD310             | CVRES  | Resolution              | _          | _   | VDD/32 | LSb                                                                                                                                                                                                             |                  |  |

| VRD311             | CVRAA  | Absolute Accuracy       | _          |     | 1      | LSb                                                                                                                                                                                                             | AVDD = 3.3V-5.5V |  |

| VRD312             | CVRur  | Unit Resistor Value (R) | _          | 2k  |        | Ω                                                                                                                                                                                                               |                  |  |

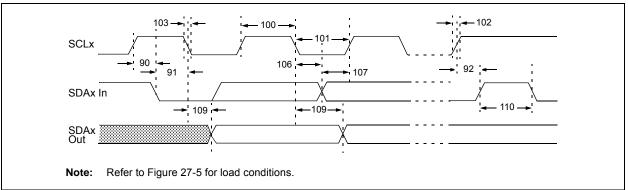

### FIGURE 27-18: MSSPx I<sup>2</sup>C™ BUS DATA TIMING

### TABLE 27-36: I<sup>2</sup>C™ BUS DATA REQUIREMENTS (MASTER MODE)

| Param.<br>No. | Symbol  | Characteristic                 |              | Min              | Max  | Units | Conditions                                |  |

|---------------|---------|--------------------------------|--------------|------------------|------|-------|-------------------------------------------|--|

| 100           | THIGH   | Clock High Time                | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

|               |         |                                | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

| 101           | TLOW    | Clock Low Time                 | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

|               |         |                                | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

| 102           | TR      | SDAx and SCLx<br>Rise Time     | 100 kHz mode | _                | 1000 | ns    | CB is specified to be from                |  |

|               |         |                                | 400 kHz mode | 20 + 0.1 CB      | 300  | ns    | 10 to 400 pF                              |  |

| 103           | TF      | SDAx and SCLx<br>Fall Time     | 100 kHz mode | _                | 300  | ns    | CB is specified to be from                |  |

|               |         |                                | 400 kHz mode | 20 + 0.1 CB      | 300  | ns    | 10 to 400 pF                              |  |

| 90            | Tsu:sta | Start Condition<br>Setup Time  | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | Only relevant for Repeate Start condition |  |

|               |         |                                | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

| 91            | THD:STA | A Start Condition<br>Hold Time | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | After this period, the first              |  |

|               |         |                                | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     | clock pulse is generated                  |  |

| 106 T         | THD:DAT | T Data Input<br>Hold Time      | 100 kHz mode | 0                | _    | ns    |                                           |  |

|               |         |                                | 400 kHz mode | 0                | 0.9  | μS    |                                           |  |

| 107           | TSU:DAT | Data Input                     | 100 kHz mode | 250              | _    | ns    | (Note 1)                                  |  |

|               |         | Setup Time                     | 400 kHz mode | 100              | _    | ns    |                                           |  |

| 92            | Тѕи:ѕто | Stop Condition                 | 100 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

|               |         | Setup Time                     | 400 kHz mode | 2(Tosc)(BRG + 1) | _    | _     |                                           |  |

| 109           | TAA     | Output Valid from Clock        | 100 kHz mode | _                | 3500 | ns    |                                           |  |

|               |         |                                | 400 kHz mode | _                | 1000 | ns    |                                           |  |

| 110           | TBUF    | F Bus Free Time                | 100 kHz mode | 4.7              | _    | μS    | Time the bus must be free                 |  |

|               |         |                                | 400 kHz mode | 1.3              | _    | μS    | before a new transmission can start       |  |

| D102          | Св      | Bus Capacitive Loading         |              |                  | 400  | pF    |                                           |  |

Note 1: A Fast mode I²C bus device can be used in a Standard mode I²C bus system, but Parameter 107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, Parameter 102 + Parameter 107 = 1000 + 250 = 1250 ns (for 100 kHz mode), before the SCLx line is released.

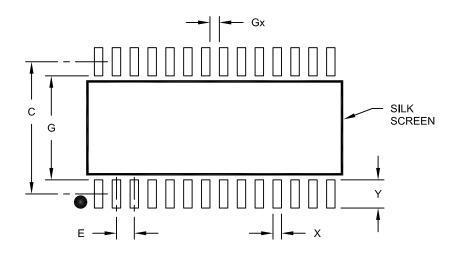

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**bte:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension Limits         |             | MIN      | NOM  | MAX  |

| Contact Pitch            | Е           | 1.27 BSC |      |      |

| Contact Pad Spacing      | С           |          | 9.40 |      |

| Contact Pad Width (X28)  | Х           |          |      | 0.60 |

| Contact Pad Length (X28) | Υ           |          |      | 2.00 |

| Distance Between Pads    | Gx          | 0.67     |      |      |

| Distance Between Pads    | G           | 7.40     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units        |          |          | MILLIMETERS |  |  |  |

|------------------------|--------------|----------|----------|-------------|--|--|--|

| Dimension Limits       |              | MIN      | NOM      | MAX         |  |  |  |

| Number of Pins         | N 48         |          |          |             |  |  |  |

| Pitch                  | е            |          | 0.40 BSC |             |  |  |  |

| Overall Height         | Α            | 0.45     | 0.50     | 0.55        |  |  |  |

| Standoff               | A1           | 0.00     | 0.02     | 0.05        |  |  |  |

| Contact Thickness      | A3 0.127 REF |          |          |             |  |  |  |

| Overall Width          | П            | 6.00 BSC |          |             |  |  |  |

| Exposed Pad Width      | E2           | 4.45     | 4.60     | 4.75        |  |  |  |

| Overall Length         | Д            | 6.00 BSC |          |             |  |  |  |

| Exposed Pad Length     | D2           | 4.45     | 4.60     | 4.75        |  |  |  |

| Contact Width          | b            | 0.15     | 0.20     | 0.25        |  |  |  |

| Contact Length         | L            | 0.30     | 0.40     | 0.50        |  |  |  |

| Contact-to-Exposed Pad | K            | 0.20     | ı        | -           |  |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2