Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

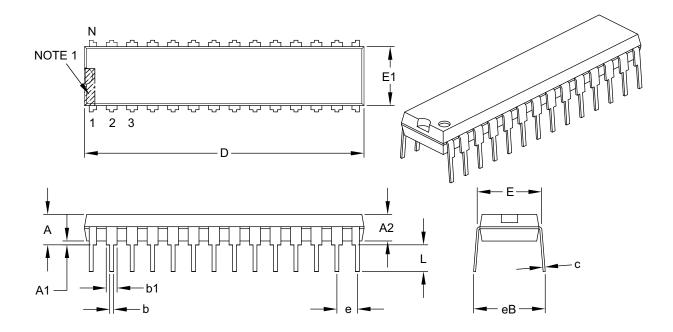

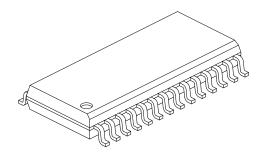

| Mounting Type              | Surface Mount                                                                |

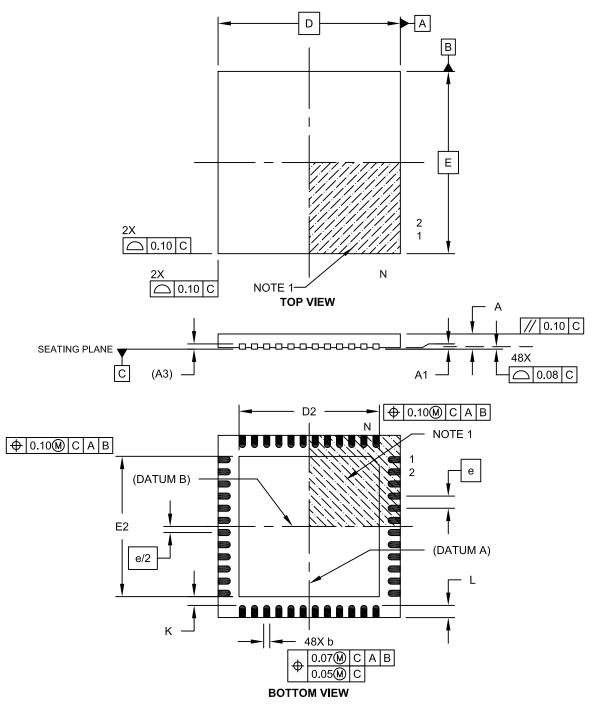

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km204-e-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                 |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------|

|          |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                                 |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                     |

| RB9      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | ST     | PORTB Pins                      |

| RB10     | —                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I/O | ST     | PORTB Pins                      |

| RB11     | —                                | 22                               | 19            | 9                      | 10             | _                                | 22                               | 19            | 9                      | 10             | I/O | ST     | PORTB Pins                      |

| RB12     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I/O | ST     | PORTB Pins                      |

| RB13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I/O | ST     | PORTB Pins                      |

| RB14     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I/O | ST     | PORTB Pins                      |

| RB15     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I/O | ST     | PORTB Pins                      |

| RC0      | —                                | _                                |               | 25                     | 27             | _                                |                                  |               | 25                     | 27             | I/O | ST     | PORTC Pins                      |

| RC1      | —                                | _                                | _             | 26                     | 28             | _                                | _                                | _             | 26                     | 28             | I/O | ST     | PORTC Pins                      |

| RC2      | —                                | _                                | _             | 27                     | 29             | _                                | _                                | _             | 27                     | 29             | I/O | ST     | PORTC Pins                      |

| RC3      | —                                | _                                | _             | 36                     | 39             | _                                | _                                | _             | 36                     | 39             | I/O | ST     | PORTC Pins                      |

| RC4      | —                                | _                                | _             | 37                     | 40             | _                                | _                                | _             | 37                     | 40             | I/O | ST     | PORTC Pins                      |

| RC5      | —                                | _                                | _             | 38                     | 41             | _                                | _                                | _             | 38                     | 41             | I/O | ST     | PORTC Pins                      |

| RC6      | —                                | _                                | _             | 2                      | 2              | _                                | _                                | _             | 2                      | 2              | I/O | ST     | PORTC Pins                      |

| RC7      | —                                | _                                | _             | 3                      | 3              | _                                | _                                | _             | 3                      | 3              | I/O | ST     | PORTC Pins                      |

| RC8      | —                                | _                                | _             | 4                      | 4              | _                                | _                                | _             | 4                      | 4              | I/O | ST     | PORTC Pins                      |

| RC9      | —                                | _                                | _             | 5                      | 5              | _                                | _                                | _             | 5                      | 5              | I/O | ST     | PORTC Pins                      |

| REFO     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | 0   | _      | Reference Clock Output          |

| RTCC     | —                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | _      | Real-Time Clock/Calendar Output |

| SCK1     | 15                               | 22                               | 19            | 9                      | 10             | 15                               | 22                               | 19            | 9                      | 10             | I/O | ST     | MSSP1 SPI Clock                 |

| SDI1     | 17                               | 21                               | 18            | 8                      | 9              | 17                               | 21                               | 18            | 8                      | 9              | Ι   | ST     | MSSP1 SPI Data Input            |

| SDO1     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   |        | MSSP1 SPI Data Output           |

| SS1      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | MSSP1 SPI Slave Select Input    |

| SCK2     | —                                | 14                               | 11            | 38                     | 41             | _                                | 14                               | 11            | 38                     | 41             | I/O | ST     | MSSP2 SPI Clock                 |

| SDI2     | —                                | 19                               | 16            | 36                     | 39             | _                                | 19                               | 16            | 36                     | 39             | Ι   | ST     | MSSP2 SPI Data Input            |

| SDO2     | —                                | 15                               | 12            | 37                     | 40             | —                                | 15                               | 12            | 37                     | 40             | 0   |        | MSSP2 SPI Data Output           |

| SS2      | —                                | 23                               | 20            | 35                     | 38             | _                                | 23                               | 20            | 35                     | 38             | Ι   | ST     | MSSP2 SPI Slave Select Input    |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

### TABLE 4-9: MCCP2 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13               | Bit 12               | Bit 11               | Bit 10               | Bit 9                | Bit 8                | Bit 7        | Bit 6        | Bit 5   | Bit 4                 | Bit 3   | Bit 2   | Bit 1                  | Bit 0      | All<br>Resets |

|-----------|-------|---------|--------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------------|--------------|---------|-----------------------|---------|---------|------------------------|------------|---------------|

| CCP2CON1L | 164h  | CCPON   | _      | CCPSIDL              | r                    | TMRSYNC              | CLKSEL2              | CLKSEL1              | CLKSEL0              | TMRPS1       | TMRPS0       | T32     | CCSEL                 | MOD3    | MOD2    | MOD1                   | MOD0       | 0000          |

| CCP2CON1H | 166h  | OPSSRC  | RTRGEN | _                    | _                    | IOPS3                | IOPS2                | IOPS1                | IOPS0                | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4                 | SYNC3   | SYNC2   | SYNC1                  | SYNC0      | 0000          |

| CCP2CON2L | 168h  | PWMRSEN | ASDGM  |                      | SSDG                 |                      |                      | _                    | _                    | ASDG7        | ASDG6        | ASDG5   | ASDG4                 | ASDG3   | ASDG2   | ASDG1                  | ASDG0      | 0000          |

| CCP2CON2H | 16Ah  | OENSYNC | -      | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN                | ICGSM1       | ICGSM0       | _       | AUXOUT1               | AUXOUT0 | ICSEL2  | ICSEL1                 | ICSEL0     | 0100          |

| CCP2CON3L | 16Ch  | _       | _      | _                    | _                    | _                    | _                    | _                    | _                    | _            |              | DT5     | DT4                   | DT3     | DT2     | DT1                    | DT0        | 0000          |

| CCP2CON3H | 16Eh  | OETRIG  | OSCNT2 | OSCNT1               | OSCNT0               | _                    | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> | _            | _            | POLACE  | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0(1) | 0000          |

| CCP2STATL | 170h  | _       | -      |                      | _                    |                      |                      | _                    | _                    | CCPTRIG      | TRSET        | TRCLR   | ASEVT                 | SCEVT   | ICDIS   | ICOV                   | ICBNE      | 0000          |

| CCP2TMRL  | 174h  |         |        |                      |                      |                      |                      | MCC                  | P2 Time Ba           | ase Register | r Low Word   |         |                       |         |         |                        |            | 0000          |

| CCP2TMRH  | 176h  |         |        |                      |                      |                      |                      | MCC                  | P2 Time Ba           | se Register  | High Word    |         |                       |         |         |                        |            | 0000          |

| CCP2PRL   | 178h  |         |        |                      |                      |                      |                      | MCCP2                | Time Base            | Period Regi  | ister Low Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2PRH   | 17Ah  |         |        |                      |                      |                      |                      | MCCP2                | Time Base I          | Period Regi  | ster High Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2RAL   | 17Ch  |         |        |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word A       |         |                       |         |         |                        |            | 0000          |

| CCP2RBL   | 180h  |         |        |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word B       |         |                       |         |         |                        |            | 0000          |

| CCP2BUFL  | 184h  |         |        |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | Low Word     |         |                       |         |         |                        |            | 0000          |

| CCP2BUFH  | 186h  |         |        |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | High Word    |         |                       |         |         |                        |            | 0000          |

PIC24FV16KM204 FAMILY

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as displayed in Example 5-5.

| EXAMPLE 5-1: | ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE |

|--------------|-------------------------------------------------------|

|              |                                                       |

| ; Set up NVMCON fo | or row erase operation               |                                     |

|--------------------|--------------------------------------|-------------------------------------|

| MOV #0x            | x4058, WO ;                          |                                     |

| MOV W0,            | , NVMCON ;                           | Initialize NVMCON                   |

| ; Init pointer to  | row to be ERASED                     |                                     |

| MOV #tk            | <pre>blpage(PROG_ADDR), W0 ;</pre>   |                                     |

| MOV W0,            | , TBLPAG ;                           | Initialize PM Page Boundary SFR     |

| MOV #tk            | <pre>bloffset(PROG_ADDR), W0 ;</pre> | Initialize in-page EA[15:0] pointer |

| TBLWTL W0,         | , [WO] ;                             | Set base address of erase block     |

| DISI #5            | ;                                    | Block all interrupts                |

|                    |                                      | for next 5 instructions             |

| MOV #0×            | x55, WO                              |                                     |

| MOV W0,            | , NVMKEY ;                           | Write the 55 key                    |

| MOV #0×            | xAA, W1 ;                            |                                     |

| MOV W1,            | , NVMKEY ;                           | Write the AA key                    |

| BSET NVM           | MCON, #WR ;                          | Start the erase sequence            |

| NOP                | ;                                    | Insert two NOPs after the erase     |

| NOP                | ;                                    | command is asserted                 |

|                    |                                      |                                     |

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

// Variable located in Pgm Memory, declared as a

int __attribute__ ((space(auto_psv))) progAddr = 0x1234;

// global variable

unsigned int offset;

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

__builtin_tblwtl(offset, 0x0000);

// Set base address of erase block

// with dummy latch write

NVMCON = 0 \times 4058;

// Initialize NVMCON

asm("DISI #5");

// Block all interrupts for next 5 instructions

_builtin_write_NVM();

\ensuremath{{//}} C30 function to perform unlock

// sequence and set WR

```

### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| ; | Set up NVMCO  | N for row programming operation | ns  |                                       |

|---|---------------|---------------------------------|-----|---------------------------------------|

|   | MOV           | #0x4004, W0                     | ;   |                                       |

|   | MOV           | W0, NVMCON                      | ;   | Initialize NVMCON                     |

| ; | Set up a poir | nter to the first program memor | ry  | location to be written                |

| ; | program memo: | ry selected, and writes enabled | b   |                                       |

|   | MOV           | #0x0000, W0                     | ;   |                                       |

|   | MOV           | W0, TBLPAG                      | ;   | Initialize PM Page Boundary SFR       |

|   | MOV           | #0x1500, W0                     | ;   | An example program memory address     |

| ; | Perform the   | TBLWT instructions to write the | e . | latches                               |

| ; | 0th_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_0, W2                 | ;   |                                       |

|   | MOV           | <pre>#HIGH_BYTE_0, W3</pre>     | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | lst_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_1, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_1, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | 2nd_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_2, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_2, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

| ; | 32nd_program  | —                               |     |                                       |

|   |               | #LOW_WORD_31, W2                | ;   |                                       |

|   |               | #HIGH_BYTE_31, W3               | ;   |                                       |

|   |               | W2, [W0]                        |     | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0]                        | ;   | Write PM high byte into program latch |

| 1 |               |                                 |     |                                       |

### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234 // Variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

// Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

// Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

// Write to address low word

__builtin_tblwtl(offset, progData[i++]);

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

### 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the Table Read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location, followed by a TBLRDL instruction.

A typical read sequence, using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and Table Read (builtin\_tblrd1) procedures from the C30 compiler library, is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

### EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

| <pre>intattribute ((space(eedata))) eeData = 0x1234;</pre> |                                       |

|------------------------------------------------------------|---------------------------------------|

| int data;                                                  | // Data read from EEPROM              |

| /*                                                         |                                       |

| The variable eeData must be a Global variable declared     | d outside of any method               |

| the code following this comment can be written inside      | the method that will execute the read |

| */                                                         |                                       |

| unsigned int offset;                                       |                                       |

| // Set up a pointer to the EEPROM location to be e         | erased                                |

| <pre>TBLPAG =builtin_tblpage(&amp;eeData);</pre>           | // Initialize EE Data page pointer    |

| offset =builtin_tbloffset(&eeData);                        | // Initizlize lower word of address   |

| <pre>data =builtin_tblrdl(offset);</pre>                   | // Write EEPROM data to write latch   |

|                                                            |                                       |

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

### TABLE 8-1:TRAP VECTOR DETAILS

### TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS

|                                         |               |             | ΑΙντ    | Interrupt Bit Locations |          |              |  |  |

|-----------------------------------------|---------------|-------------|---------|-------------------------|----------|--------------|--|--|

| Interrupt Source                        | Vector Number | IVT Address | Address | Flag                    | Enable   | Priority     |  |  |

| ADC1 – ADC1 Convert Done                | 13            | 00002Eh     | 00012Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>    |  |  |

| CLC1                                    | 96            | 0000D4h     | 0001D4h | IFS6<0>                 | IEC6<0>  | IPC24<2:0>   |  |  |

| CLC2                                    | 97            | 0000D6h     | 0001D6h | IFS6<1>                 | IEC6<1>  | IPC24<6:4>   |  |  |

| Comparator Interrupt                    | 18            | 000038h     | 000138h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>   |  |  |

| СТМИ                                    | 77            | 0000AEh     | 0001AEh | IFS4<13>                | IEC4<13> | IPC19<6:4>   |  |  |

| DAC1 – Buffer Update                    | 78            | 0000B0h     | 0001B0h | IFS4<14>                | IEC4<14> | IPC19<10:8>  |  |  |

| DAC2 – Buffer Update                    | 79            | 0000B2h     | 0001B2h | IFS4<15>                | IEC4<15> | IPC19<14:12> |  |  |

| HLVD – High/Low-Voltage Detect          | 72            | 0000A4h     | 0001A4h | IFS4<8>                 | IEC4<8>  | IPC18<2:0>   |  |  |

| ICN – Input Change Notification         | 19            | 00003Ah     | 00013Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12>  |  |  |

| INT0 – External Interrupt 0             | 0             | 000014h     | 000114h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>    |  |  |

| INT1 – External Interrupt 1             | 20            | 00003Ch     | 00013Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>    |  |  |

| INT2 – External Interrupt 2             | 29            | 00004Eh     | 00014Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>    |  |  |

| MCCP1 – Capture/Compare                 | 1             | 000016h     | 000116h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>    |  |  |

| MCCP1 – Time Base                       | 7             | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |  |  |

| MCCP2 – Capture/Compare                 | 2             | 000018h     | 000118h | IFS0<2>                 | IEC0<2>  | IPC0<10:8>   |  |  |

| MCCP2 – Time Base                       | 8             | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |  |  |

| MCCP3 – Capture/Compare                 | 5             | 00001Eh     | 00011Eh | IFS0<5>                 | IEC0<5>  | IPC1<6:4>    |  |  |

| MCCP3 – Time Base                       | 27            | 00004Ah     | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |  |  |

| MSSP1 – Bus Collision Interrupt         | 17            | 000036h     | 000136h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>    |  |  |

| MSSP1 – I <sup>2</sup> C™/SPI Interrupt | 16            | 000034h     | 000134h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>    |  |  |

| MSSP2 – Bus Collision Interrupt         | 50            | 000078h     | 000178h | IFS3<2>                 | IEC3<2>  | IPC12<10:8>  |  |  |

| MSSP2 – I <sup>2</sup> C/SPI Interrupt  | 49            | 000076h     | 000176h | IFS3<1>                 | IEC3<1>  | IPC12<6:4>   |  |  |

| NVM – NVM Write Complete                | 15            | 000032h     | 000132h | IFS0<15>                | IEC0<15> | IPC3<14:12>  |  |  |

| RTCC – Real-Time Clock/Calendar         | 62            | 000090h     | 000190h | IFS3<14>                | IEC3<14> | IPC15<10:8>  |  |  |

| SCCP4 – Capture/Compare                 | 6             | 000020h     | 000120h | IFS0<6>                 | IEC0<6>  | IPC1<10:8>   |  |  |

| SCCP4 – Time Base                       | 28            | 00004Ch     | 00014Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |  |  |

| SCCP5 – Capture/Compare                 | 22            | 000040h     | 000140h | IFS1<6>                 | IEC1<6>  | IPC5<10:8>   |  |  |

| SCCP5 – Time Base                       | 41            | 000066h     | 000166h | IFS2<9>                 | IEC2<9>  | IPC10<6:4>   |  |  |

| TMR1 – Timer1                           | 3             | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |  |  |

| UART1 Error                             | 65            | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |  |  |

| UART2 Error                             | 66            | 000098h     | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |  |  |

| UART1RX – UART1 Receiver                | 11            | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |  |  |

| UART1TX – UART1 Transmitter             | 12            | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |  |  |

| UART2RX – UART2 Receiver                | 30            | 000050h     | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |  |  |

| UART2TX – UART2 Transmitter             | 31            | 000052h     | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |  |  |

| ULPWU – Ultra Low-Power Wake-up         | 80            | 0000B4h     | 0001B4h | IFS5<0>                 | IEC5<0>  | IPC20<2:0>   |  |  |

| R/W-0         | R/W-0                                                | R/W-0                                                                      | R/W-0             | R/W-0             | U-0              | U-0             | U-0    |  |  |  |  |  |  |

|---------------|------------------------------------------------------|----------------------------------------------------------------------------|-------------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|--|

| U2TXIE        | U2RXIE                                               | INT2IE                                                                     | CCT4IE            | CCT3IE            |                  | _               | _      |  |  |  |  |  |  |

| bit 15        |                                                      |                                                                            |                   |                   |                  |                 | bit 8  |  |  |  |  |  |  |

|               | DAMA                                                 |                                                                            | <b>D</b> 444 0    | DAVA              | DAMA             | DAMA            | DANO   |  |  |  |  |  |  |

| U-0           | R/W-0                                                | U-0                                                                        | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |  |

|               | CCP5IE                                               | —                                                                          | INT1IE            | CNIE              | CMIE             | BCL1IE          | SSP1IE |  |  |  |  |  |  |

| bit 7         |                                                      |                                                                            |                   |                   |                  |                 | bit    |  |  |  |  |  |  |

| Legend:       |                                                      |                                                                            |                   |                   |                  |                 |        |  |  |  |  |  |  |

| R = Readable  | e bit                                                | W = Writable                                                               | bit               | U = Unimplen      | nented bit, read | d as '0'        |        |  |  |  |  |  |  |

| -n = Value at | POR                                                  | '1' = Bit is set                                                           |                   | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |  |  |  |  |  |  |

|               |                                                      |                                                                            |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 15        | U2TXIE: UA                                           | RT2 Transmitte                                                             | r Interrupt Enat  | ole bit           |                  |                 |        |  |  |  |  |  |  |

|               | 1 = Interrupt request is enabled                     |                                                                            |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | 0 = Interrupt                                        | request is not e                                                           | enabled           |                   |                  |                 |        |  |  |  |  |  |  |

| bit 14        |                                                      | RT2 Receiver II                                                            | •                 | e bit             |                  |                 |        |  |  |  |  |  |  |

|               |                                                      | request is enab                                                            |                   |                   |                  |                 |        |  |  |  |  |  |  |

| L:1 10        | -                                                    | request is not e                                                           |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 13        |                                                      | NT2IE: External Interrupt 2 Enable bit<br>. = Interrupt request is enabled |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | 0 = Interrupt request is enabled                     |                                                                            |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 12        | •                                                    | oture/Compare                                                              |                   | pt Enable bit     |                  |                 |        |  |  |  |  |  |  |

|               | •                                                    | 1 = Interrupt request is enabled                                           |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | 0 = Interrupt                                        | request is not e                                                           | enabled           |                   |                  |                 |        |  |  |  |  |  |  |

| bit 11        | CCT3IE: Cap                                          | oture/Compare                                                              | 3 Timer Interru   | pt Enable bit     |                  |                 |        |  |  |  |  |  |  |

|               |                                                      | request is enab<br>request is not e                                        |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 10-7      | Unimplemer                                           | nted: Read as '                                                            | 0'                |                   |                  |                 |        |  |  |  |  |  |  |

| bit 6         | CCP5IE: Capture/Compare 5 Event Interrupt Enable bit |                                                                            |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | •                                                    | request is enab<br>request is not e                                        |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 5         | Unimplemer                                           | nted: Read as '                                                            | 0'                |                   |                  |                 |        |  |  |  |  |  |  |

| bit 4         | INT1IE: Exte                                         | rnal Interrupt 1                                                           | Enable bit        |                   |                  |                 |        |  |  |  |  |  |  |

|               |                                                      | request is enab<br>request is not e                                        |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 3         | CNIE: Input (                                        | Change Notifica                                                            | ation Interrupt E | Enable bit        |                  |                 |        |  |  |  |  |  |  |

|               | 1 = Interrupt                                        | request is enab                                                            | led               |                   |                  |                 |        |  |  |  |  |  |  |

| bit 2         | •                                                    | arator Interrupt                                                           |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | 1 = Interrupt                                        | request is enab<br>request is not e                                        | led               |                   |                  |                 |        |  |  |  |  |  |  |

| bit 1         |                                                      | SP1 I <sup>2</sup> C™ Bus                                                  |                   | unt Enable bit    |                  |                 |        |  |  |  |  |  |  |

|               |                                                      | request is enab                                                            |                   | טאנ בוומטוכ טונ   |                  |                 |        |  |  |  |  |  |  |

|               |                                                      | request is not e                                                           |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | •                                                    |                                                                            |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 0         | SSP1IE: MS                                           | SP1 SPI/I <sup>2</sup> C Ev                                                | ent Interrupt E   | nable bit         |                  |                 |        |  |  |  |  |  |  |

| bit 0         |                                                      | SP1 SPI/I <sup>2</sup> C Ev<br>request is enab                             | •                 | nable bit         |                  |                 |        |  |  |  |  |  |  |

| U-0          | R/W-1         | R/W-0                                | R/W-0            | U-0                | R/W-1            | R/W-0           | R/W-0   |

|--------------|---------------|--------------------------------------|------------------|--------------------|------------------|-----------------|---------|

| —            | CCT1IP2       | CCT1IP1                              | CCT1IP0          | —                  | CCP4IP2          | CCP4IP1         | CCP4IP0 |

| bit 15       |               |                                      |                  |                    |                  |                 | bit 8   |

| U-0          | R/W-1         | R/W-0                                | R/W-0            | U-0                | U-0              | U-0             | U-0     |

|              | CCP3IP2       | CCP3IP1                              | CCP3IP0          |                    |                  |                 |         |

| bit 7        | 0010112       |                                      |                  |                    |                  |                 | bit 0   |

|              |               |                                      |                  |                    |                  |                 |         |

| Legend:      |               |                                      |                  |                    |                  |                 |         |

| R = Readab   | ole bit       | W = Writable                         | bit              | U = Unimplen       | nented bit, read | l as '0'        |         |

| -n = Value a | at POR        | '1' = Bit is set                     |                  | '0' = Bit is cle   | ared             | x = Bit is unkn | iown    |

|              |               |                                      |                  |                    |                  |                 |         |

| bit 15       | -             | ted: Read as '                       |                  |                    |                  |                 |         |

| bit 14-12    | CCT1IP<2:0>   | : Capture/Com                        | pare 1 Timer I   | nterrupt Priority  | / bits           |                 |         |

|              | 111 = Interru | pt is Priority 7(                    | highest priority | interrupt)         |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | 001 = Interru |                                      |                  |                    |                  |                 |         |

|              | •             | pt source is dis                     |                  |                    |                  |                 |         |

| bit 11       | -             | ted: Read as '                       |                  |                    |                  |                 |         |

| bit 10-8     |               | •                                    | •                | Interrupt Priority | y bits           |                 |         |

|              | 111 = Interru | pt is Priority 7(                    | highest priority | interrupt)         |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | 001 = Interru |                                      |                  |                    |                  |                 |         |

|              | -             | pt source is dis                     |                  |                    |                  |                 |         |

| bit 7        | -             | ted: Read as '                       |                  |                    |                  |                 |         |

| bit 6-4      |               | •                                    | •                | Interrupt Priority | y bits           |                 |         |

|              | 111 = Interru | pt is Priority 7(                    | nignest priority | (interrupt)        |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | •             |                                      |                  |                    |                  |                 |         |

|              | 001 = Interru | pt is Priority 1<br>pt source is dis | ablad            |                    |                  |                 |         |

| bit 3-0      | •             | ted: Read as '                       |                  |                    |                  |                 |         |

| DIL 3-0      | Unimplemen    | ieu: Reau as                         | J                |                    |                  |                 |         |

### REGISTER 8-20: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC Oscillator by a fixed amount.

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                    | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit          |                                    |                    |  |  |

|----------------------------|------------------------------------------------|------------------------------------|--------------------|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit SO = Settable Only bit |                                    |                    |  |  |

| R = Readable bit           | W = Writable bit                               | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR          | '1' = Bit is set                               | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| Note 1:   | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:        | This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                |

**3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

### REGISTER 14-10: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0          | U-0         | U-0                                | U-0                          | R/W-0                  | R/W-0                  | R/W-0           | R/W-0              |  |  |

|--------------|-------------|------------------------------------|------------------------------|------------------------|------------------------|-----------------|--------------------|--|--|

|              | —           |                                    | _                            | SDO2DIS <sup>(1)</sup> | SCK2DIS <sup>(1)</sup> | SDO1DIS         | SCK1DIS            |  |  |

| bit 15       |             |                                    |                              |                        |                        |                 | bit                |  |  |

|              |             |                                    |                              |                        |                        |                 |                    |  |  |

| U-0          | U-0         | U-0                                | U-0                          | U-0                    | U-0                    | U-0             | U-0                |  |  |

|              | —           |                                    |                              |                        | —                      | _               | —                  |  |  |

| bit 7        |             |                                    |                              |                        |                        |                 | bit (              |  |  |

|              |             |                                    |                              |                        |                        |                 |                    |  |  |

| Legend:      |             |                                    |                              |                        |                        |                 |                    |  |  |

| R = Readabl  | e bit       | W = Writable b                     | pit                          | U = Unimplem           | nented bit, read       | as '0'          |                    |  |  |

| n = Value at | POR         | '1' = Bit is set                   |                              | '0' = Bit is clea      | ared                   | x = Bit is unkn | a = Bit is unknown |  |  |

|              |             |                                    |                              |                        |                        |                 |                    |  |  |

| bit 15-12    | Unimplemen  | ted: Read as '0                    | ,                            |                        |                        |                 |                    |  |  |

| bit 11       | SDO2DIS: MS | SSP2 SDO2 Pir                      | n Disable bit <sup>(1)</sup> | )                      |                        |                 |                    |  |  |

|              |             | output data (SD                    | ,                            | •                      |                        |                 |                    |  |  |

|              |             | output data (SD                    |                              |                        | e pin                  |                 |                    |  |  |

| bit 10       |             | SSP2 SCK2 Pir                      |                              |                        |                        |                 |                    |  |  |

|              |             | clock (SCK2) of<br>clock (SCK2) of |                              |                        | נ                      |                 |                    |  |  |

| bit 9        |             | SSP1 SDO1 Pir                      |                              |                        |                        |                 |                    |  |  |

|              |             | output data (SD                    |                              | 1 to the pin is d      | isabled                |                 |                    |  |  |

|              |             | output data (SD                    | ,                            |                        |                        |                 |                    |  |  |

| bit 8        | SCK1DIS: MS | CK1DIS: MSSP1 SCK1 Pin Disable bit |                              |                        |                        |                 |                    |  |  |

|              | 1 = The SPI | clock (SCK1) of                    | MSSP1 to the                 | e pin is disabled      | t                      |                 |                    |  |  |

|              | 0 = The SPI | clock (SCK1) of                    | MSSP1 is ou                  | tput to the pin        |                        |                 |                    |  |  |

| bit 7-0      | Unimplemen  | ted: Read as '0                    | ,                            |                        |                        |                 |                    |  |  |

|              |             |                                    |                              |                        |                        |                 |                    |  |  |

**Note 1:** These bits are implemented only on PIC24FXXKM20X devices.

### REGISTER 16-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

- **Note 1:** The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

REGISTER 18-1:

#### U-0 R/W-0 R/W-0 U-0 U-0 U-0 U-0 U-0 HLVDEN HLSIDL \_\_\_\_\_ \_\_\_\_ \_\_\_\_\_ \_\_\_\_\_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 VDIR BGVST **IRVST** HLVDL3 HLVDL2 HLVDL1 HLVDL0 bit 7 bit 0 Legend: R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 HLVDEN: High/Low-Voltage Detect Power Enable bit 1 = HLVD is enabled 0 = HLVD is disabled bit 14 Unimplemented: Read as '0' bit 13 HLSIDL: HLVD Stop in Idle Mode bit 1 = Discontinues module operation when device enters Idle mode 0 = Continues module operation in Idle mode bit 12-8 Unimplemented: Read as '0' bit 7 VDIR: Voltage Change Direction Select bit 1 = Event occurs when voltage equals or exceeds trip point (HLVDL<3:0>) 0 = Event occurs when voltage equals or falls below trip point (HLVDL<3:0>) bit 6 BGVST: Band Gap Voltage Stable Flag bit 1 = Indicates that the band gap voltage is stable 0 = Indicates that the band gap voltage is unstable bit 5 **IRVST:** Internal Reference Voltage Stable Flag bit 1 = Indicates that the internal reference voltage is stable and the High-Voltage Detect logic generates the interrupt flag at the specified voltage range 0 = Indicates that the internal reference voltage is unstable and the High-Voltage Detect logic will not generate the interrupt flag at the specified voltage range, and the HLVD interrupt should not be enabled bit 4 Unimplemented: Read as '0' bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits 1111 = External analog input is used (input comes from the HLVDIN pin) 1110 = Trip Point 1<sup>(1)</sup> 1101 = Trip Point 2<sup>(1)</sup> 1100 = Trip Point 3<sup>(1)</sup> 0000 = Trip Point 15<sup>(1)</sup>

HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| U-0    | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | U-0   | U-0   |

|--------|-------|-------|----------------------|----------------------|-------|-------|-------|

| _      | CSS30 | CSS29 | CSS28                | CSS27                | CSS26 | —     | —     |

| bit 15 |       |       |                      |                      |       |       | bit 8 |

|        |       |       |                      |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| CSS23  | CSS22 | CSS21 | CSS20 <sup>(2)</sup> | CSS19 <sup>(2)</sup> | CSS18 | CSS17 | CSS16 |

| bit 7  |       |       |                      |                      |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

- bit 14-10CSS<30:26>: A/D Input Scan Selection bits1 = Includes the corresponding channel for input scan0 = Skips the channel for input scanbit 9-8Unimplemented: Read as '0'bit 7-0CSS<23:16>: A/D Input Scan Selection bits<sup>(2)</sup>1 = Includes the corresponding channel for input scan0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<20:19> bits are not implemented in 20-pin devices.

### REGISTER 19-9: AD1CSSL: A/D INPUT SCAN SELECT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                 | R/W-0               | R/W-0                      | R/W-0                                  | R/W-0                                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                                                                                                              |

|-----------------------|---------------------|----------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| CSS14                 | CSS13               | CSS12                      | CSS11                                  | CSS10                                                                                                     | CSS9                                                                                                                                  | CSS8 <sup>(2,3)</sup>                                                                                                                              |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       | bit 8                                                                                                                                              |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       |                                                                                                                                                    |

| R/W-0                 | R/W-0               | R/W-0                      | R/W-0                                  | R/W-0                                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                                                                                                              |

| CSS6 <sup>(2,3)</sup> | CSS5 <sup>(2)</sup> | CSS4                       | CSS3                                   | CSS2                                                                                                      | CSS1                                                                                                                                  | CSS0                                                                                                                                               |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       | bit 0                                                                                                                                              |

|                       | R/W-0               | CSS14 CSS13<br>R/W-0 R/W-0 | CSS14 CSS13 CSS12<br>R/W-0 R/W-0 R/W-0 | CSS14         CSS13         CSS12         CSS11           R/W-0         R/W-0         R/W-0         R/W-0 | CSS14         CSS13         CSS12         CSS11         CSS10           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0 | CSS14         CSS13         CSS12         CSS11         CSS10         CSS9           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CSS<15:0>: A/D Input Scan Selection bits<sup>(2,3)</sup>

1 = Includes the corresponding ANx input for scan

- 0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<8:5> bits are not implemented in 20-pin devices.

- 3: The CSS<8:6> bits are not implemented in 28-pin devices.

| R/W-0         | U-0                                                                                                                   | R/W-0                                | R/W-0          | U-0               | U-0              | U-0             | U-0     |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|---------|--|--|--|

| AMPEN         |                                                                                                                       | AMPSIDL                              | AMPSLP         |                   |                  |                 |         |  |  |  |

| bit 15        |                                                                                                                       |                                      | •              |                   |                  |                 | bit 8   |  |  |  |

|               |                                                                                                                       |                                      |                |                   |                  |                 |         |  |  |  |

| R/W-0         | U-0                                                                                                                   | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| SPDSEL        | —                                                                                                                     | NINSEL2                              | NINSEL1        | NINSEL0           | PINSEL2          | PINSEL1         | PINSEL0 |  |  |  |

| bit 7         |                                                                                                                       |                                      |                |                   |                  |                 | bit 0   |  |  |  |

| Legend:       |                                                                                                                       |                                      |                |                   |                  |                 |         |  |  |  |

| R = Readabl   | e bit                                                                                                                 | W = Writable                         | bit            | U = Unimplen      | nented bit, read | 1 as '0'        |         |  |  |  |

| -n = Value at | POR                                                                                                                   | '1' = Bit is set                     |                | '0' = Bit is clea |                  | x = Bit is unkr | nown    |  |  |  |

|               |                                                                                                                       |                                      |                |                   |                  |                 | -       |  |  |  |

| bit 15        | AMPEN: Op                                                                                                             | Amp x Control                        | Module Enable  | e bit             |                  |                 |         |  |  |  |