Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

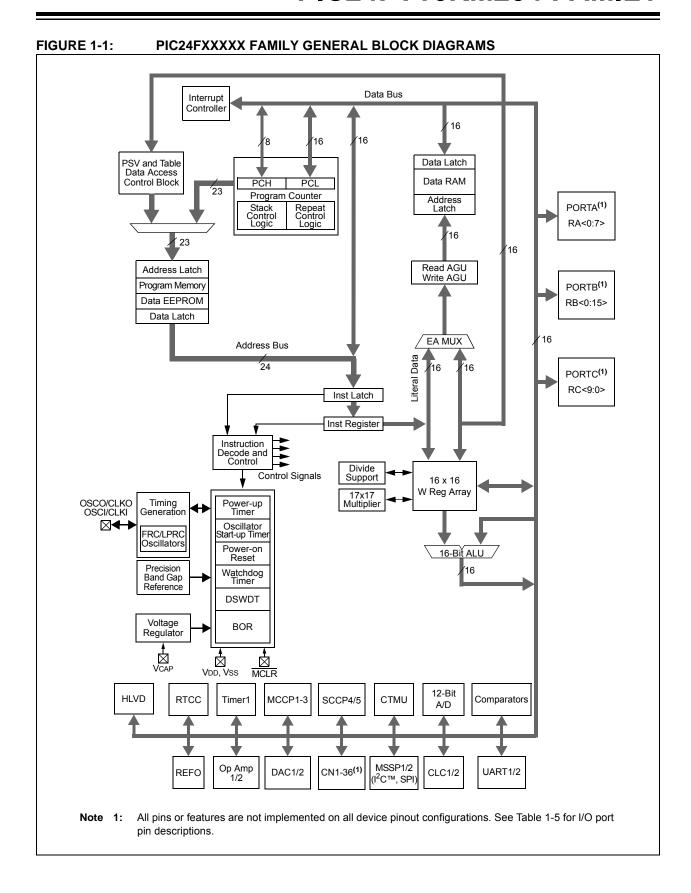

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km204-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-4: DEVICE FEATURES FOR THE PIC24FV16KM104 FAMILY

| TABLE 1-4: DEVICE FEATURES FOR                   | N THE PICZ4FVT                                                                                                                                | ONIVITUA FAIVII    |                       |                                          |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|------------------------------------------|--|--|

| Features                                         | PIC24FV16KM104                                                                                                                                | PIC24FV16KM102     | PIC24FV08KM102        | PIC24FV08KM101                           |  |  |

| Operating Frequency                              |                                                                                                                                               | DC-3               | 2 MHz                 |                                          |  |  |

| Program Memory (bytes)                           | 16K                                                                                                                                           | 16K                | 8K                    | 8K                                       |  |  |

| Program Memory (instructions)                    | 5632                                                                                                                                          | 5632               | 2816                  | 2816                                     |  |  |

| Data Memory (bytes)                              |                                                                                                                                               | 10                 | )24                   |                                          |  |  |

| Data EEPROM Memory (bytes)                       |                                                                                                                                               | 5                  | 12                    |                                          |  |  |

| Interrupt Sources (soft vectors/NMI traps)       |                                                                                                                                               | 25 (               | 21/4)                 |                                          |  |  |

| Voltage Range                                    |                                                                                                                                               | 2.0-               | 5.5V                  |                                          |  |  |

| I/O Ports                                        | PORTA<11:7,5:0><br>PORTB<15:0><br>PORTC<9:0>                                                                                                  | PORTA<<br>PORTB    |                       | PORTA<5:0><br>PORTB<15:12,9:7,<br>4,2:0> |  |  |

| Total I/O Pins                                   | 37                                                                                                                                            | 23 17              |                       |                                          |  |  |

| Timers                                           | (One 16-bit timer, t                                                                                                                          |                    | 5<br>Ps with up to tv | vo 16/32 timers each)                    |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP      |                                                                                                                                               |                    | 1<br>1                |                                          |  |  |

| Serial Communications MSSP UART                  |                                                                                                                                               |                    | 1<br>1                |                                          |  |  |

| Input Change Notification Interrupt              | 36                                                                                                                                            | 22                 | 2                     | 16                                       |  |  |

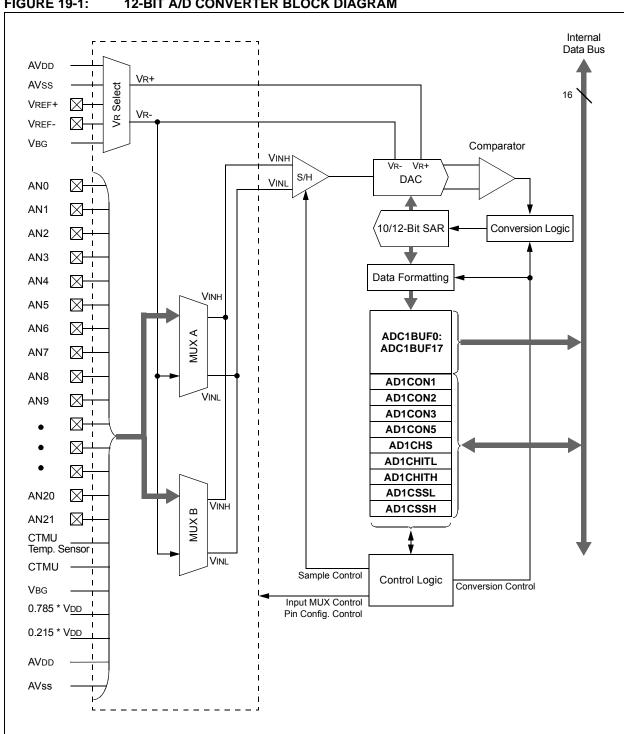

| 12-Bit Analog-to-Digital Module (input channels) | 22                                                                                                                                            | 19                 | )                     | 16                                       |  |  |

| Analog Comparators                               |                                                                                                                                               |                    | 1                     |                                          |  |  |

| 8-Bit Digital-to-Analog Converters               |                                                                                                                                               | -                  | _                     |                                          |  |  |

| Operational Amplifiers                           |                                                                                                                                               | -                  | _                     |                                          |  |  |

| Charge Time Measurement Unit (CTMU)              |                                                                                                                                               | Y                  | es                    |                                          |  |  |

| Real-Time Clock and Calendar (RTCC)              |                                                                                                                                               | -                  |                       |                                          |  |  |

| Configurable Logic Cell (CLC)                    | 1                                                                                                                                             |                    |                       |                                          |  |  |

| Resets (and delays)                              | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode, REPEAT Instruction, Hardware Traps, Configuration Word Mismatch (PWRT, OST, PLL Lock) |                    |                       |                                          |  |  |

| Instruction Set                                  | 76 Base Inst                                                                                                                                  | ructions, Multiple | e Addressing N        | Node Variations                          |  |  |

| Packages                                         | 44-Pin<br>QFN/TQFP,<br>48-Pin UQFN                                                                                                            | 28-F<br>SPDIP/SSOP |                       | 20-Pin<br>SOIC/SSOP/PDIP                 |  |  |

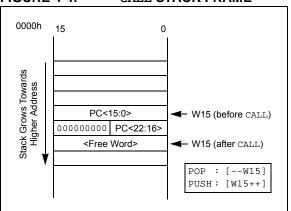

#### 4.2.5 SOFTWARE STACK

In addition to its use as a working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as depicted in Figure 4-4.

For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

Note: A PC push during exception processing will concatenate the SRL register to the MSB of the PC prior to the push.

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6 in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 4-4: CALL STACK FRAME

## 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit-wide program space and 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the Data Space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

#### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

See Table 4-35 and Figure 4-5 to know how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a Data Space word.

#### REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0, HS | R/W-0, HS | R/W-0  | R/W-0                | U-0 | U-0 | R/W-0 | R/W-0 |

|-----------|-----------|--------|----------------------|-----|-----|-------|-------|

| TRAPR     | IOPUWR    | SBOREN | RETEN <sup>(3)</sup> | _   | _   | СМ    | PMSLP |

| bit 15    |           |        |                      |     |     |       | bit 8 |

| R/W-0, HS | R/W-0, HS | R/W-0, HS             | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-1, HS | R/W-1, HS |

|-----------|-----------|-----------------------|-----------|-----------|-----------|-----------|-----------|

| EXTR      | SWR       | SWDTEN <sup>(2)</sup> | WDTO      | SLEEP     | IDLE      | BOR       | POR       |

| bit 7     |           |                       |           |           |           |           | bit 0     |

**Legend:** HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 TRAPR: Trap Reset Flag bit

1 = A Trap Conflict Reset has occurred

0 = A Trap Conflict Reset has not occurred

bit 14 IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit

1 = An illegal opcode detection, an illegal address mode or Uninitialized W register used as an Address Pointer caused a Reset

0 = An illegal opcode or Uninitialized W Reset has not occurred

bit 13 SBOREN: Software Enable/Disable of BOR bit

1 = BOR is turned on in software

0 = BOR is turned off in software

bit 12 **RETEN:** Retention Sleep Mode<sup>(3)</sup>

1 = Regulated voltage supply provided by the Retention Regulator (RETREG) during Sleep

0 = Regulated voltage supply provided by the main Voltage Regulator (VREG) during Sleep

bit 11-10 Unimplemented: Read as '0'

bit 9 CM: Configuration Word Mismatch Reset Flag bit

1 = A Configuration Word Mismatch Reset has occurred

0 = A Configuration Word Mismatch Reset has not occurred

bit 8 **PMSLP:** Program Memory Power During Sleep bit

1 = Program memory bias voltage remains powered during Sleep

0 = Program memory bias voltage is powered down during Sleep and the voltage regulator enters Standby mode

bit 7 **EXTR:** External Reset (MCLR) Pin bit

1 = A Master Clear (pin) Reset has occurred

0 = A Master Clear (pin) Reset has not occurred

bit 6 SWR: Software RESET (Instruction) Flag bit

1 = A RESET instruction has been executed

0 = A RESET instruction has not been executed

bit 5 SWDTEN: Software Enable/Disable of WDT bit(2)

1 = WDT is enabled

0 = WDT is disabled

**Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

#### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC          |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| _      | _   | _   | _   | _   | _   | _   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0, HSC            | R/W-0, HSC            | R/W-0, HSC            | R-0, HSC          | R/W-0, HSC       | R/W-0, HSC        | R/W-0, HSC       | R/W-0, HSC       |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           | HSC = Hardware Settable/0 | HSC = Hardware Settable/Clearable bit   |  |  |  |  |  |

|-------------------|---------------------------|-----------------------------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'      |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |  |

bit 15-9 Unimplemented: Read as '0'

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled

110 = CPU Interrupt Priority Level is 6 (14)

101 = CPU Interrupt Priority Level is 5 (13)

100 = CPU Interrupt Priority Level is 4 (12)

011 = CPU Interrupt Priority Level is 3 (11)

010 = CPU Interrupt Priority Level is 2 (10)

001 = CPU Interrupt Priority Level is 1 (9)

000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

3: The IPLx Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

#### **REGISTER 8-2: CORCON: CPU CONTROL REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0              | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|--------------------|-----|-------|

| _     | _   | _   | _   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | _   |       |

| bit 7 |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settable/Clearable bit |                    |  |

|-------------------|-------------------|---------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read           | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared                  | x = Bit is unknown |  |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 70 = CPU Interrupt Priority Level is 7 or less

bit 1-0 **Unimplemented:** Read as '0'

Note 1: See Register 3-2 for the description of this bit, which is not dedicated to interrupt control functions.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

Note: Bit 2 is described in Section 3.0 "CPU".

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| _     | _   | _   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | _     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 NSTDIS: Interrupt Nesting Disable bit

1 = Interrupt nesting is disabled0 = Interrupt nesting is enabled

bit 14-5 **Unimplemented:** Read as '0'

bit 4 MATHERR: Arithmetic Error Trap Status bit

1 = Overflow trap has occurred0 = Overflow trap has not occurred

bit 3 ADDRERR: Address Error Trap Status bit

1 = Address error trap has occurred0 = Address error trap has not occurred

bit 2 STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred0 = Stack error trap has not occurred

bit 1 OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred0 = Oscillator failure trap has not occurred

bit 0 Unimplemented: Read as '0'

#### REGISTER 8-13: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | U-0 | U-0   |

|--------|--------|--------|--------|--------|-----|-----|-------|

| U2TXIE | U2RXIE | INT2IE | CCT4IE | CCT3IE | _   | _   |       |

| bit 15 |        |        |        |        |     |     | bit 8 |

| U-0   | R/W-0  | U-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

|-------|--------|-----|--------|-------|-------|--------|--------|

| _     | CCP5IE | _   | INT1IE | CNIE  | CMIE  | BCL1IE | SSP1IE |

| bit 7 |        |     |        |       |       |        | bit 0  |

| Legena: |

|---------|

|---------|

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **U2TXIE:** UART2 Transmitter Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 14 **U2RXIE:** UART2 Receiver Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 13 INT2IE: External Interrupt 2 Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 12 CCT4IE: Capture/Compare 4 Timer Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 11 CCT3IE: Capture/Compare 3 Timer Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 10-7 Unimplemented: Read as '0'

bit 6 **CCP5IE:** Capture/Compare 5 Event Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 5 **Unimplemented:** Read as '0'

bit 4 INT1IE: External Interrupt 1 Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 3 CNIE: Input Change Notification Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 2 CMIE: Comparator Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 1 **BCL1IE:** MSSP1 I<sup>2</sup>C™ Bus Collision Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 0 SSP1IE: MSSP1 SPI/I<sup>2</sup>C Event Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### REGISTER 8-22: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0    | R/W-1  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|--------|-----|-----|-----|-------|

| _      | NVMIP2 | NVMIP1 | NVMIP0 | _   | _   | _   | _     |

| bit 15 |        |        |        |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|--------|--------|--------|-----|---------|---------|---------|

| _     | AD1IP2 | AD1IP1 | AD1IP0 | _   | U1TXIP2 | U1TXIP1 | U1TXIP0 |

| bit 7 |        |        |        |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **NVMIP<2:0>:** NVM Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11-7 **Unimplemented:** Read as '0'

bit 6-4 AD1IP<2:0>: A/D Conversion Complete Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

The following code sequence for a clock switch is recommended:

- Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON

in two back-to-back instructions.

- Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1 and Example 9-2.

# EXAMPLE 9-1: ASSEMBLY CODE SEQUENCE FOR CLOCK SWITCHING

```

;Place the new oscillator selection in WO

;OSCCONH (high byte) Unlock Sequence

MOV

#OSCCONH, w1

#0x78, w2

MOV

MOV

#0x9A, w3

MOV.b

w2, [w1]

MOV.b

w3, [w1]

;Set new oscillator selection

MOV.b

WREG, OSCCONH

;OSCCONL (low byte) unlock sequence

MOV

#OSCCONL, w1

MOV

#0x46, w2

#0x57, w3

MOV

MOV.b

w2, [w1]

MOV.b

w3, [w1]

;Start oscillator switch operation

BSET

OSCCON,#0

```

# EXAMPLE 9-2: BASIC 'C' CODE SEQUENCE FOR CLOCK SWITCHING

```

//Use compiler built-in function to write

new clock setting

__builtin_write_OSCCONH(0x01); //0x01

switches to FRCPLL

//Use compiler built-in function to set the

OSWEN bit.

__builtin_write_OSCCONL(OSCCONL | 0x01);

//Optional: Wait for clock switch sequence

to complete

while(OSCCONbits.OSWEN == 1);

```

#### 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FXXXXX family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIV<3:0> bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the ROSEL bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

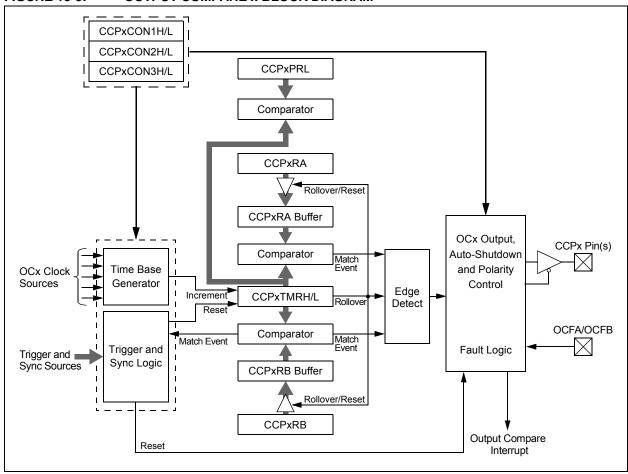

#### 13.3 Output Compare Mode

Output Compare mode compares the Timer register value with the value of one or two Compare registers, depending on its mode of operation. The Output Compare x module on compare match events has the ability to generate a single output transition or a train of output

pulses. Like most PIC® MCU peripherals, the Output Compare x module can also generate interrupts on a compare match event.

Table 13-3 shows the various modes available in Output Compare modes.

TABLE 13-3: OUTPUT COMPARE/PWM MODES

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                         |                  |  |  |

|------------------------------|-----------------------|----------------------------------------|------------------|--|--|

| 0001                         | 0                     | Output High on Compare (16-bit)        |                  |  |  |

| 0001                         | 1                     | Output High on Compare (32-bit)        | ]                |  |  |

| 0010                         | 0                     | Output Low on Compare (16-bit)         | Cinale Edge Mede |  |  |

| 0010                         | 1                     | Output Low on Compare (32-bit)         | Single Edge Mode |  |  |

| 0011                         | 0                     | Output Toggle on Compare (16-bit)      |                  |  |  |

| 0011                         | 1                     | Output Toggle on Compare (32-bit)      |                  |  |  |

| 0100                         | 0                     | Dual Edge Compare (16-bit)             | Dual Edge Mode   |  |  |

| 0101                         | 0                     | Dual Edge Compare (16-bit buffered)    | PWM Mode         |  |  |

| 0110                         | 0                     | Center-Aligned Pulse (16-bit buffered) | Center PWM       |  |  |

| 0111                         | 0                     | Variable Frequency Pulse (16-bit)      |                  |  |  |

| 0111                         | 1                     | Variable Frequency Pulse (32-bit)      |                  |  |  |

FIGURE 13-5: OUTPUT COMPARE x BLOCK DIAGRAM

#### REGISTER 14-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0              | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|--------------------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE <sup>(1)</sup> | D/Ā | Р   | S   | R/W | UA  | BF    |

| bit 7 |                    |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7 SMP: Sample bit

SPI Master mode:

1 = Input data is sampled at the end of data output time0 = Input data is sampled at the middle of data output time

SPI Slave mode:

SMP must be cleared when SPI is used in Slave mode.

bit 6 **CKE:** SPI Clock Select bit<sup>(1)</sup>

1 = Transmit occurs on transition from active to Idle clock state 0 = Transmit occurs on transition from Idle to active clock state

bit 5 D/A: Data/Address bit

Used in  $I^2C^{TM}$  mode only.

bit 4 **P:** Stop bit

Used in I<sup>2</sup>C mode only. This bit is cleared when the MSSPx module is disabled; SSPEN bit is cleared.

bit 3 S: Start bit

Used in I<sup>2</sup>C mode only.

bit 2 R/W: Read/Write Information bit

Used in I<sup>2</sup>C mode only.

bit 1 UA: Update Address bit

Used in I<sup>2</sup>C mode only.

bit 0 BF: Buffer Full Status bit

1 = Receive is complete, SSPxBUF is full

0 = Receive is not complete, SSPxBUF is empty

Note 1: Polarity of clock state is set by the CKP bit (SSPxCON1<4>).

NOTES:

#### 16.2.6 ALRMVAL REGISTER MAPPINGS

#### REGISTER 16-8: ALMTHDY: ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | _   | _   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit

Contains a value of '0' or '1'.

bit 11-8 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits

Contains a value from 0 to 9.

bit 7-6 Unimplemented: Read as '0'

bit 5-4 DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits

Contains a value from 0 to 3.

bit 3-0 DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 16-9: ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER(1)

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| _      | _   | _   | _   | _   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 Unimplemented: Read as '0'

bit 10-8 WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits

Contains a value from 0 to 6.

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits

Contains a value from 0 to 2.

bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### **REGISTER 25-8: DEVID: DEVICE ID REGISTER**

| U-0           | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|---------------|-----|-----|-----|-----|-----|-----|-----|--|

| _             | _   | _   | _   | _   | _   | _   | _   |  |

| bit 23 bit 16 |     |     |     |     |     |     |     |  |

| R      | R      | R      | R      | R      | R      | R      | R      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 | FAMID1 | FAMID0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV7  | DEV6 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-16 Unimplemented: Read as '0'

bit 15-8 **FAMID<7:0>:** Device Family Identifier bits

01000101 = PIC24FV16KM204 family

bit 7-0 **DEV<7:0>:** Individual Device Identifier bits

00011111 = PIC24FV16KM204

00011011 = PIC24FV16KM202

00010111 = PIC24FV08KM204

00010011 = PIC24FV08KM202

00001111 = PIC24FV16KM104

00001111 = PIC24FV16KM102

00000011 = PIC24FV08KM102

00000001 = PIC24FV08KM101

00011110 = PIC24F16KM204

00011010 = PIC24F16KM202

00010110 = PIC24F08KM204

00010010 = PIC24F08KM202

00001110 = PIC24F16KM104

00001010 = PIC24F16KM102

00000010 = PIC24F08KM102

00000000 = PIC24F08KM101

TABLE 27-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CHARACTERISTICS  |       | Standard Operating te                                                                                               |                                                     |                       | 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +125°C for Extended |             |                                            |

|---------------------|-------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------|

| Param<br>No.        | Sym   | Characteristic                                                                                                      | Min                                                 | Typ <sup>(1)</sup>    | Max                                                                                                                                    | Units       | Conditions                                 |

|                     | VIL   | Input Low Voltage <sup>(4)</sup>                                                                                    |                                                     |                       |                                                                                                                                        |             |                                            |

| DI10                |       | I/O Pins                                                                                                            | Vss                                                 | _                     | 0.2 VDD                                                                                                                                | V           |                                            |

| DI15                |       | MCLR                                                                                                                | Vss                                                 | _                     | 0.2 VDD                                                                                                                                | V           |                                            |

| DI16                |       | OSCI (XT mode)                                                                                                      | Vss                                                 | _                     | 0.2 VDD                                                                                                                                | V           |                                            |

| DI17                |       | OSCI (HS mode)                                                                                                      | Vss                                                 | _                     | 0.2 VDD                                                                                                                                | V           |                                            |

| DI18                |       | I/O Pins with I <sup>2</sup> C™ Buffer                                                                              | Vss                                                 | _                     | 0.3 VDD                                                                                                                                | V           | SMBus disabled                             |

| DI19                |       | I/O Pins with SMBus Buffer                                                                                          | Vss                                                 | _                     | 8.0                                                                                                                                    | V           | SMBus enabled                              |

| DI20 DI25 DI26 DI27 | VIH   | Input High Voltage <sup>(4,5)</sup> I/O Pins: with Analog Functions Digital Only MCLR OSCI (XT mode) OSCI (HS mode) | 0.8 VDD<br>0.8 VDD<br>0.8 VDD<br>0.7 VDD<br>0.7 VDD | _<br>_<br>_<br>_<br>_ | VDD<br>VDD<br>VDD<br>VDD<br>VDD                                                                                                        | V<br>V<br>V |                                            |

| DI28<br>DI29        |       | I/O Pins with I <sup>2</sup> C Buffer:<br>with Analog Functions<br>Digital Only<br>I/O Pins with SMBus              | 0.7 VDD<br>0.7 VDD<br>2.1                           | _<br>_<br>_           | VDD<br>VDD<br>VDD                                                                                                                      | V<br>V<br>V | 2.5V ≤ VPIN ≤ VDD                          |

| DI30                | ICNPU | CNx Pull-up Current                                                                                                 | 50                                                  | 250                   | 500                                                                                                                                    | μΑ          | VDD = 3.3V, VPIN = VSS                     |

| DI31                | IPU   | Maximum Load Current for                                                                                            | _                                                   | _                     | 30                                                                                                                                     | μΑ          | VDD = 2.0V                                 |

|                     |       | Digital High Detection w/Internal Pull-up                                                                           | _                                                   | _                     | 1000                                                                                                                                   | μА          | VDD = 3.3V                                 |

|                     | lı∟   | Input Leakage Current <sup>(2,3)</sup>                                                                              |                                                     |                       |                                                                                                                                        |             |                                            |

| DI50                |       | I/O Ports                                                                                                           | _                                                   | 0.050                 | ±0.100                                                                                                                                 | μА          | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance |

| DI51                |       | Pins with OAxOUT Functions (RB15 and RB3)                                                                           | _                                                   | 0.100                 | ±0.200                                                                                                                                 | μА          | VSS ≤ VPIN ≤ VDD,<br>Pin at high-impedance |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: Refer to Table 1-4 and Table 1-5 for I/O pin buffer types.

- **5:** VIH requirements are met when the internal pull-ups are enabled.

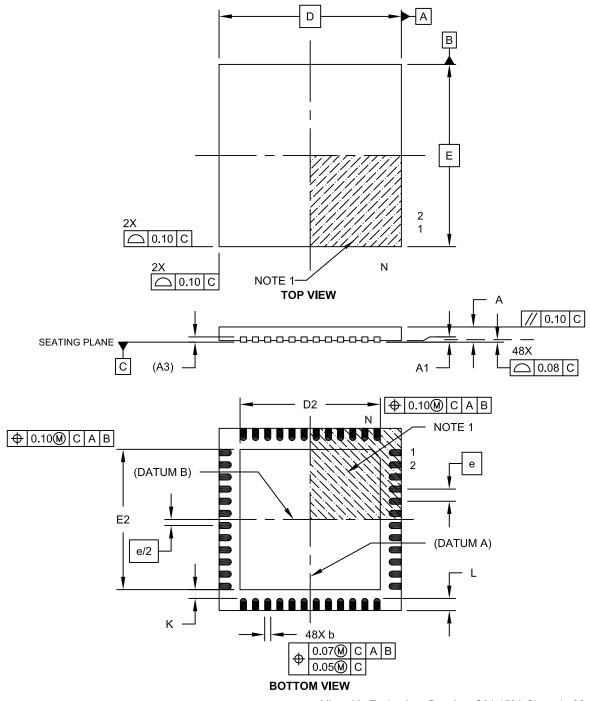

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

#### Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252

Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631

Fax: 91-11-4160-8632

**India - Pune** Tel: 91-20-2566-1512

Fax: 91-20-2566-1513 Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or

82-2-558-5934 Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859 Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340 **Spain - Madrid**

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 **UK - Wokingham**

Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12