Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 48-UQFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km204-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                 |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------|

|          |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                                 |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                     |

| RB9      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | ST     | PORTB Pins                      |

| RB10     | —                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I/O | ST     | PORTB Pins                      |

| RB11     | —                                | 22                               | 19            | 9                      | 10             | _                                | 22                               | 19            | 9                      | 10             | I/O | ST     | PORTB Pins                      |

| RB12     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I/O | ST     | PORTB Pins                      |

| RB13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I/O | ST     | PORTB Pins                      |

| RB14     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I/O | ST     | PORTB Pins                      |

| RB15     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I/O | ST     | PORTB Pins                      |

| RC0      | —                                | _                                |               | 25                     | 27             | _                                |                                  |               | 25                     | 27             | I/O | ST     | PORTC Pins                      |

| RC1      | —                                | _                                | _             | 26                     | 28             | _                                | _                                | _             | 26                     | 28             | I/O | ST     | PORTC Pins                      |

| RC2      | —                                | _                                | _             | 27                     | 29             | _                                | _                                | _             | 27                     | 29             | I/O | ST     | PORTC Pins                      |

| RC3      | —                                | _                                | _             | 36                     | 39             | _                                | _                                | _             | 36                     | 39             | I/O | ST     | PORTC Pins                      |

| RC4      | —                                | _                                | _             | 37                     | 40             | _                                | _                                | _             | 37                     | 40             | I/O | ST     | PORTC Pins                      |

| RC5      | —                                | _                                | _             | 38                     | 41             | _                                | _                                | _             | 38                     | 41             | I/O | ST     | PORTC Pins                      |

| RC6      | —                                | _                                | _             | 2                      | 2              | _                                | _                                | _             | 2                      | 2              | I/O | ST     | PORTC Pins                      |

| RC7      | —                                | _                                | _             | 3                      | 3              | _                                | _                                | _             | 3                      | 3              | I/O | ST     | PORTC Pins                      |

| RC8      | —                                | _                                | _             | 4                      | 4              | _                                | _                                | _             | 4                      | 4              | I/O | ST     | PORTC Pins                      |

| RC9      | —                                | _                                | _             | 5                      | 5              | _                                | _                                | _             | 5                      | 5              | I/O | ST     | PORTC Pins                      |

| REFO     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | 0   | _      | Reference Clock Output          |

| RTCC     | —                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | _      | Real-Time Clock/Calendar Output |

| SCK1     | 15                               | 22                               | 19            | 9                      | 10             | 15                               | 22                               | 19            | 9                      | 10             | I/O | ST     | MSSP1 SPI Clock                 |

| SDI1     | 17                               | 21                               | 18            | 8                      | 9              | 17                               | 21                               | 18            | 8                      | 9              | Ι   | ST     | MSSP1 SPI Data Input            |

| SDO1     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   |        | MSSP1 SPI Data Output           |

| SS1      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | MSSP1 SPI Slave Select Input    |

| SCK2     | —                                | 14                               | 11            | 38                     | 41             | _                                | 14                               | 11            | 38                     | 41             | I/O | ST     | MSSP2 SPI Clock                 |

| SDI2     | —                                | 19                               | 16            | 36                     | 39             | _                                | 19                               | 16            | 36                     | 39             | Ι   | ST     | MSSP2 SPI Data Input            |

| SDO2     | —                                | 15                               | 12            | 37                     | 40             | —                                | 15                               | 12            | 37                     | 40             | 0   |        | MSSP2 SPI Data Output           |

| SS2      | —                                | 23                               | 20            | 35                     | 38             | _                                | 23                               | 20            | 35                     | 38             | Ι   | ST     | MSSP2 SPI Slave Select Input    |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

|  | REGISTER 3-2: | CORCON: CPU CONTROL REGISTER |

|--|---------------|------------------------------|

|--|---------------|------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   |     | —   |     | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   |     | —   | IPL3 <sup>(1)</sup> | PSV   | —   | —     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settable   | e/Clearable bit                    |  |  |  |

|-------------------|-------------------|---------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown                 |  |  |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in Data Space                                                                                    |

|          | 0 = Program space is not visible in Data Space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

## 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on data EEPROM, refer to the *"PIC24F Family Reference Manual"*, **"Data EEPROM"** (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFh. The size of the data EEPROM is 256 words in PIC24FXXXXX devices.

The data EEPROM is organized as 16-bit-wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

## 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

## 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

|                | rrupts For 5 instruc | ctions |

|----------------|----------------------|--------|

| asm volatile   | ("disi #5");         |        |

| //Issue Unlock | Sequence             |        |

| asm volatile   | ("mov #0x55, W0      | \n"    |

|                | "mov W0, NVMKEY      | \n"    |

|                | "mov #0xAA, W1       | \n"    |

|                | "mov W1, NVMKEY      | \n");  |

| // Perform Wri | te/Erase operations  |        |

| asm volatile   | ("bset NVMCON, #WR   | \n"    |

|                | "nop                 | \n"    |

|                | "nop                 | \n");  |

|                |                      |        |

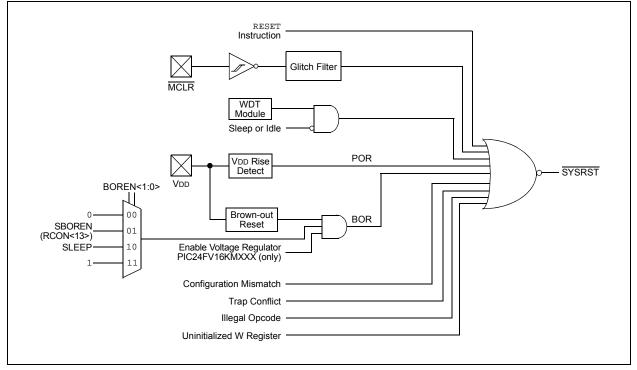

## 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "PIC24F Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- LPBOR: Low-Power BOR

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on Power-on Reset (POR) and unchanged by all other Resets.

Note: Refer to the specific peripheral or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A Power-on Reset will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

## FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

## TABLE 8-1:TRAP VECTOR DETAILS

## TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS

|                                         |               |             | ΑΙΥΤ    | Interrupt Bit Locations |          |              |  |

|-----------------------------------------|---------------|-------------|---------|-------------------------|----------|--------------|--|

| Interrupt Source                        | Vector Number | IVT Address | Address | Flag                    | Enable   | Priority     |  |

| ADC1 – ADC1 Convert Done                | 13            | 00002Eh     | 00012Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>    |  |

| CLC1                                    | 96            | 0000D4h     | 0001D4h | IFS6<0>                 | IEC6<0>  | IPC24<2:0>   |  |

| CLC2                                    | 97            | 0000D6h     | 0001D6h | IFS6<1>                 | IEC6<1>  | IPC24<6:4>   |  |

| Comparator Interrupt                    | 18            | 000038h     | 000138h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>   |  |

| СТМИ                                    | 77            | 0000AEh     | 0001AEh | IFS4<13>                | IEC4<13> | IPC19<6:4>   |  |

| DAC1 – Buffer Update                    | 78            | 0000B0h     | 0001B0h | IFS4<14>                | IEC4<14> | IPC19<10:8>  |  |

| DAC2 – Buffer Update                    | 79            | 0000B2h     | 0001B2h | IFS4<15>                | IEC4<15> | IPC19<14:12> |  |

| HLVD – High/Low-Voltage Detect          | 72            | 0000A4h     | 0001A4h | IFS4<8>                 | IEC4<8>  | IPC18<2:0>   |  |

| ICN – Input Change Notification         | 19            | 00003Ah     | 00013Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12>  |  |

| INT0 – External Interrupt 0             | 0             | 000014h     | 000114h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>    |  |

| INT1 – External Interrupt 1             | 20            | 00003Ch     | 00013Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>    |  |

| INT2 – External Interrupt 2             | 29            | 00004Eh     | 00014Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>    |  |

| MCCP1 – Capture/Compare                 | 1             | 000016h     | 000116h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>    |  |

| MCCP1 – Time Base                       | 7             | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |  |

| MCCP2 – Capture/Compare                 | 2             | 000018h     | 000118h | IFS0<2>                 | IEC0<2>  | IPC0<10:8>   |  |

| MCCP2 – Time Base                       | 8             | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |  |

| MCCP3 – Capture/Compare                 | 5             | 00001Eh     | 00011Eh | IFS0<5>                 | IEC0<5>  | IPC1<6:4>    |  |

| MCCP3 – Time Base                       | 27            | 00004Ah     | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |  |

| MSSP1 – Bus Collision Interrupt         | 17            | 000036h     | 000136h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>    |  |

| MSSP1 – I <sup>2</sup> C™/SPI Interrupt | 16            | 000034h     | 000134h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>    |  |

| MSSP2 – Bus Collision Interrupt         | 50            | 000078h     | 000178h | IFS3<2>                 | IEC3<2>  | IPC12<10:8>  |  |

| MSSP2 – I <sup>2</sup> C/SPI Interrupt  | 49            | 000076h     | 000176h | IFS3<1>                 | IEC3<1>  | IPC12<6:4>   |  |

| NVM – NVM Write Complete                | 15            | 000032h     | 000132h | IFS0<15>                | IEC0<15> | IPC3<14:12>  |  |

| RTCC – Real-Time Clock/Calendar         | 62            | 000090h     | 000190h | IFS3<14>                | IEC3<14> | IPC15<10:8>  |  |

| SCCP4 – Capture/Compare                 | 6             | 000020h     | 000120h | IFS0<6>                 | IEC0<6>  | IPC1<10:8>   |  |

| SCCP4 – Time Base                       | 28            | 00004Ch     | 00014Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |  |

| SCCP5 – Capture/Compare                 | 22            | 000040h     | 000140h | IFS1<6>                 | IEC1<6>  | IPC5<10:8>   |  |

| SCCP5 – Time Base                       | 41            | 000066h     | 000166h | IFS2<9>                 | IEC2<9>  | IPC10<6:4>   |  |

| TMR1 – Timer1                           | 3             | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |  |

| UART1 Error                             | 65            | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |  |

| UART2 Error                             | 66            | 000098h     | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |  |

| UART1RX – UART1 Receiver                | 11            | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |  |

| UART1TX – UART1 Transmitter             | 12            | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |  |

| UART2RX – UART2 Receiver                | 30            | 000050h     | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |  |

| UART2TX – UART2 Transmitter             | 31            | 000052h     | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |  |

| ULPWU – Ultra Low-Power Wake-up         | 80            | 0000B4h     | 0001B4h | IFS5<0>                 | IEC5<0>  | IPC20<2:0>   |  |

### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC          |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| —      | —   | —   | —   | —   | —   |     | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0, HSC            | R/W-0, HSC            | R/W-0, HSC            | R-0, HSC          | R/W-0, HSC       | R/W-0, HSC        | R/W-0, HSC       | R/W-0, HSC       |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           | HSC = Hardware Settable/0 | HSC = Hardware Settable/Clearable bit   |  |  |  |  |

|-------------------|---------------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

bit 15-9 Unimplemented: Read as '0'

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

|         |                                                                            |

Note 1: See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

- 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- 3: The IPLx Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

## REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

|        | —   | —   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0              | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|--------------------|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | —   | —     |

| bit 7 |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settal  | HSC = Hardware Settable/Clearable bit |  |  |

|-------------------|-------------------|------------------------|---------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | U = Unimplemented bit, read as '0'    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown                    |  |  |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 1-0 Unimplemented: Read as '0'

**Note 1:** See Register 3-2 for the description of this bit, which is not dedicated to interrupt control functions.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

Note: Bit 2 is described in Section 3.0 "CPU".

| U-0                 | R/W-1                                    | R/W-0                                                                       | R/W-0            | U-0                                | U-0              | U-0             | U-0     |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------|------------------|------------------------------------|------------------|-----------------|---------|

| 0-0                 | NVMIP2                                   | NVMIP1                                                                      | NVMIP0           | 0-0                                | 0-0              | 0-0             | 0-0     |

| <br>bit 15          |                                          |                                                                             |                  | —                                  | _                | _               | <br>bit |

|                     |                                          |                                                                             |                  |                                    |                  |                 | bit     |

| U-0                 | R/W-1                                    | R/W-0                                                                       | R/W-0            | U-0                                | R/W-1            | R/W-0           | R/W-0   |

| _                   | AD1IP2                                   | AD1IP1                                                                      | AD1IP0           |                                    | U1TXIP2          | U1TXIP1         | U1TXIP0 |

| bit 7               |                                          |                                                                             |                  |                                    |                  |                 | bit     |

| Legend:             |                                          |                                                                             |                  |                                    |                  |                 |         |

| R = Readab          | ole bit                                  | W = Writable                                                                | bit              | U = Unimplem                       | nented bit, read | 1 as '0'        |         |

| -n = Value a        | at POR                                   | '1' = Bit is set                                                            |                  | '0' = Bit is clea                  | ared             | x = Bit is unkr | nown    |

| =                   |                                          |                                                                             |                  |                                    |                  |                 |         |

| bit 15<br>bit 14-12 | -                                        | ited: Read as '<br>: NVM Interrup                                           |                  |                                    |                  |                 |         |

|                     | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                   | abled            | .,                                 |                  |                 |         |

| bit 11-7            | -                                        | ted: Read as '                                                              |                  |                                    |                  |                 |         |

| bit 6-4             | 111 = Interru<br>•<br>•<br>001 = Interru | A/D Conversic<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis | highest priority | terrupt Priority I<br>/ interrupt) | bits             |                 |         |

| bit 3               | Unimplemen                               | ted: Read as '                                                              | 0'               |                                    |                  |                 |         |

| bit 2-0             |                                          | ➤: UART1 Trans<br>pt is Priority 7 (                                        |                  |                                    |                  |                 |         |

|                     |                                          | pt is Priority 1<br>pt source is dis                                        | abled            |                                    |                  |                 |         |

## REGISTER 8-22: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| R-0           | U-0                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0              | R-0              | R-0               | R-0               | R-0              |

|---------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|------------------|

| CPUIRQ        |                     | VHOLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | ILR3             | ILR2              | ILR1              | ILR0             |

| bit 15        |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   | bit 8            |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| U-0           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   | R-0               |                  |

| <br>bit 7     | VECNUM6             | VECNUM5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VECNUM4          | VECNUM3          | VECNUM2           | VECNUM1           | VECNUM0<br>bit 0 |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   | 511 0            |

| Legend:       |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| R = Readable  | e bit               | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit              | U = Unimpler     | nented bit, read  | l as '0'          |                  |

| -n = Value at | POR                 | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | '0' = Bit is cle | ared              | x = Bit is unkr   | nown             |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  |                   |                   |                  |

| bit 15        |                     | errupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                |                  |                   |                   |                  |

|               |                     | upt request have the version of the |                  |                  | been Acknowl      | eagea by the      | CPU (this will   |

|               |                     | upt request is l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                  | (independency)    |                   |                  |

| bit 14        | Unimplemen          | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0'               |                  |                   |                   |                  |

| bit 13        | VHOLD: Vect         | or Hold bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |                  |                   |                   |                  |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                  | rupt is Stored ir |                   |                  |

|               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ntain the value  | e of the highe   | st priority pend  | ding interrupt, i | instead of the   |