Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

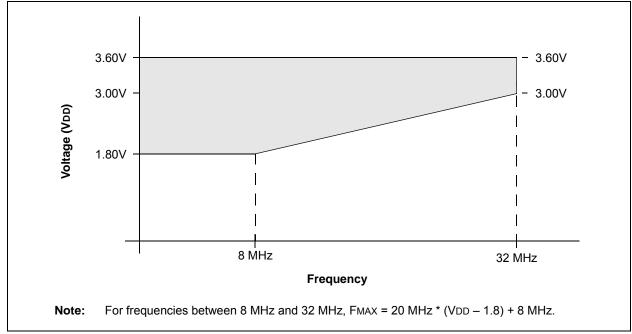

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

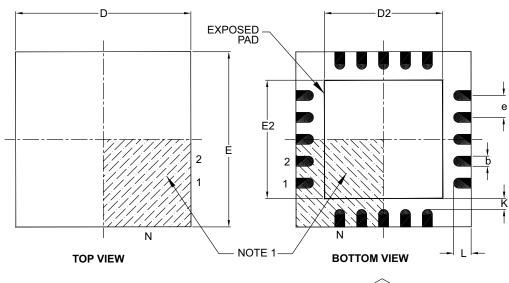

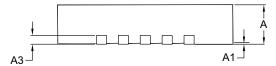

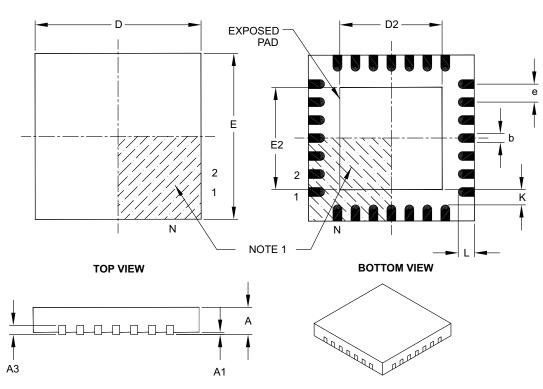

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km204t-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                             |       |

|-------|-------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 29    |

| 3.0   | CPU                                                         | 35    |

| 4.0   | Memory Organization                                         | 41    |

| 5.0   | Flash Program Memory                                        | 67    |

| 6.0   | Data EEPROM Memory                                          | 73    |

| 7.0   | Resets                                                      | 79    |

| 8.0   | Interrupt Controller                                        | 85    |

| 9.0   | Oscillator Configuration                                    | . 121 |

| 10.0  | Power-Saving Features                                       | . 131 |

| 11.0  | I/O Ports                                                   | . 137 |

| 12.0  | Timer1                                                      |       |

| 13.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)           | . 143 |

| 14.0  | Master Synchronous Serial Port (MSSP)                       |       |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART)          | . 173 |

| 16.0  | Real-Time Clock and Calendar (RTCC)                         | . 181 |

| 17.0  | Configurable Logic Cell (CLC)                               | . 195 |

| 18.0  | High/Low-Voltage Detect (HLVD)                              | . 207 |

|       | 12-Bit A/D Converter with Threshold Detect                  |       |

| 20.0  | 8-Bit Digital-to-Analog Converter (DAC)                     | . 229 |

| 21.0  | Dual Operational Amplifier Module                           | . 233 |

| 22.0  | Comparator Module                                           |       |

| 23.0  | Comparator Voltage Reference                                | . 239 |

| 24.0  | Charge Time Measurement Unit (CTMU)                         | . 241 |

| 25.0  | Special Features                                            | . 249 |

| 26.0  | Development Support                                         | . 261 |

| 27.0  | Electrical Characteristics                                  | . 265 |

| 28.0  | Packaging Information                                       | . 297 |

| Appe  | ndix A: Revision History                                    | . 325 |

| Index | · · · · · · · · · · · · · · · · · · ·                       | 327   |

|       | /icrochip Web Site                                          |       |

| Custo | omer Change Notification Service                            | . 333 |

| Custo | omer Support                                                | . 333 |

| Produ | Jct Identification System                                   | . 335 |

# TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

| TADLE 1-5. |                                  |                                  | F             |                        |                |                                  | ,                                | FV            | ,                      |                |     |        |                                             |

|------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|            |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                | -   |        |                                             |

| Function   | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CTED1      | 11                               | 20                               | 17            | 7                      | 7              | 11                               | 2                                | 27            | 19                     | 21             | Ι   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2      | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED3      | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED4      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED5      | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED6      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED7      | _                                |                                  | _             | 5                      | 5              |                                  |                                  | _             | 5                      | 5              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED8      | —                                |                                  | _             | 13                     | 14             |                                  |                                  | —             | 13                     | 14             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED9      | _                                | 22                               | 19            | 9                      | 10             |                                  | 22                               | 19            | 9                      | 10             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED10     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED11     | —                                | 21                               | 18            | 8                      | 9              |                                  | 21                               | 18            | 8                      | 9              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED12     | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED13     | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTPLS      | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   | _      | CTMU Pulse Output                           |

| CVREF      | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | 0   | ANA    | Comparator Voltage Reference Output         |

| CVREF+     | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | Ι   | ANA    | Comparator Voltage Reference Positive Input |

| CVREF-     | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | Comparator Voltage Reference Negative Input |

| DAC1OUT    | —                                | 23                               | 20            | 10                     | 11             |                                  | 23                               | 20            | 10                     | 11             | 0   | ANA    | DAC1 Output                                 |

| DAC1REF+   | _                                | 2                                | 27            | 19                     | 21             |                                  | 2                                | 27            | 19                     | 21             | I   | ANA    | DAC1 Positive Voltage Reference Input       |

| DAC2OUT    | —                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | ANA    | DAC2 Output                                 |

| DAC2REF+   | —                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | Ι   | ANA    | DAC2 Positive Voltage Reference Input       |

| HLVDIN     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | Ι   | ANA    | External High/Low-Voltage Detect Input      |

| IC1        | 14                               | 19                               | 16            | 6                      | 6              | 11                               | 19                               | 16            | 6                      | 6              | Ι   | ST     | MCCP1 Input Capture Input                   |

| IC2        | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | MCCP2 Input Capture Input                   |

| IC3        | —                                | 23                               | 20            | 13                     | 14             | _                                | 23                               | 20            | 13                     | 14             | Ι   | ST     | MCCP3 Input Capture Input                   |

| IC4        | _                                | 14                               | 11            | 5                      | 5              | _                                | 14                               | 11            | 5                      | 5              | I   | ST     | SCCP4 Input Capture Input                   |

| IC5        | _                                | 15                               | 12            | 12                     | 13             |                                  | 15                               | 12            | 12                     | 13             | Ι   | ST     | SCCP5 Input Capture Input                   |

| INT0       | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ST     | External Interrupt 0 Input                  |

| INT1       | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | External Interrupt 1 Input                  |

| INT2       | 14                               | 20                               | 17            | 7                      | 7              | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | External Interrupt 2 Input                  |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

# TABLE 4-25: A/D REGISTER MAP

| File Name | -25:<br>Addr. | Bit 15  | Bit 14                                                                                   | Bit 13                                                                                   | Bit 12  | Bit 11   | Bit 10       | Bit 9      | Bit 8                 | Bit 7                 | Bit 6                 | Bit 5                 | Bit 4                  | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | All    |

|-----------|---------------|---------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------|----------|--------------|------------|-----------------------|-----------------------|-----------------------|-----------------------|------------------------|------------------------|---------|---------|---------|--------|

|           |               | 2.1.10  |                                                                                          | 2                                                                                        | 2.4.12  | 2        | 20.10        | 2          | 2                     |                       | 2                     | 2                     |                        | 2                      |         |         | 2.10    | Resets |

| ADC1BUF0  | 300h          |         |                                                                                          |                                                                                          |         | A/D Da   | ata Buffer 0 | /Threshold | for Channel 0/        | Threshold for         | Channel 0 & 1         | 2 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF1  | 302h          |         | A/D Data Buffer 1/Threshold for Channel 1/Threshold for Channel 1 & 13 in Window Compare |                                                                                          |         |          |              |            |                       |                       |                       |                       |                        |                        |         |         |         |        |

| ADC1BUF2  | 304h          |         |                                                                                          |                                                                                          |         | A/D Da   | ata Buffer 2 | /Threshold | for Channel 2/        | Threshold for         | Channel 2 & 1         | 4 in Window           | Compare                |                        |         |         |         | XXXX   |

| ADC1BUF3  | 306h          |         |                                                                                          |                                                                                          |         | A/D Da   | ata Buffer 3 | /Threshold | for Channel 3/        | Threshold for         | Channel 3 & 1         | 5 in Window           | Compare                |                        |         |         |         | XXXX   |

| ADC1BUF4  | 308h          |         |                                                                                          |                                                                                          |         | A/D Da   | ata Buffer 4 | /Threshold | for Channel 4/        | Threshold for         | Channel 4 & 1         | 6 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF5  | 30Ah          |         | A/D Data Buffer 5/Threshold for Channel 5/Threshold for Channel 5 & 17 in Window Compare |                                                                                          |         |          |              |            |                       |                       |                       |                       |                        | xxxx                   |         |         |         |        |

| ADC1BUF6  | 30Ch          |         | A/D Data Buffer 6/Threshold for Channel 6/Threshold for Channel 6 & 18 in Window Compare |                                                                                          |         |          |              |            |                       |                       |                       |                       |                        |                        |         |         |         |        |

| ADC1BUF7  | 30Eh          |         | A/D Data Buffer 7/Threshold for Channel 7/Threshold for Channel 7 & 19 in Window Compare |                                                                                          |         |          |              |            |                       |                       |                       |                       |                        |                        |         |         |         |        |

| ADC1BUF8  | 310h          |         |                                                                                          | A/D Data Buffer 8/Threshold for Channel 8/Threshold for Channel 8 & 20 in Window Compare |         |          |              |            |                       |                       |                       |                       |                        |                        |         |         |         |        |

| ADC1BUF9  | 312h          |         |                                                                                          |                                                                                          |         | A/D Da   | ata Buffer 9 | /Threshold | for Channel 9/        | Threshold for         | Channel 9 & 2         | 1 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF10 | 314h          |         |                                                                                          |                                                                                          |         | A/D Data | a Buffer 10/ | Threshold  | for Channel 10        | /Threshold for        | r Channel 10 &        | 22 in Window          | w Compare              |                        |         |         |         | xxxx   |

| ADC1BUF11 | 316h          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 11/ | Threshold  | for Channel 11        | /Threshold for        | Channel 11 &          | 23 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF12 | 318h          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 12  | /Threshold | for Channel 12        | 2/Threshold fo        | r Channel 0 &         | 12 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF13 | 31Ah          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 13  | /Threshold | for Channel 13        | 3/Threshold fo        | r Channel 1 &         | 13 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF14 | 31Ch          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 14  | /Threshold | for Channel 14        | 4/Threshold fo        | r Channel 2 &         | 14 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF15 | 31Eh          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 15  | /Threshold | for Channel 1         | 5/Threshold fo        | r Channel 3 &         | 15 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF16 | 320h          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 16  | /Threshold | for Channel 1         | 6/Threshold fo        | r Channel 4 &         | 16 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF17 | 322h          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 17  | /Threshold | for Channel 1         | 7/Threshold fo        | r Channel 5 &         | 17 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF18 | 324h          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 18  | /Threshold | for Channel 18        | 8/Threshold fo        | r Channel 6 &         | 18 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF19 | 326h          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 19  | /Threshold | for Channel 19        | 9/Threshold fo        | r Channel 7 &         | 19 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF20 | 328h          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 20  | /Threshold | for Channel 20        | 0/Threshold fo        | r Channel 8 &         | 20 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF21 | 32Ah          |         |                                                                                          |                                                                                          |         | A/D Dat  | a Buffer 21  | /Threshold | for Channel 2         | 1/Threshold fo        | r Channel 9 &         | 21 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF22 | 32Ch          |         |                                                                                          |                                                                                          |         | A/D Data | a Buffer 22/ | Threshold  | for Channel 22        | 2/Threshold for       | r Channel 10 &        | 22 in Window          | w Compare              |                        |         |         |         | xxxx   |

| ADC1BUF23 | 32Eh          |         |                                                                                          |                                                                                          |         | A/D Data | a Buffer 23/ | Threshold  | for Channel 23        | 3/Threshold for       | r Channel 11 &        | 23 in Window          | w Compare              |                        |         |         |         | xxxx   |

| AD1CON1   | 340h          | ADON    | _                                                                                        | ADSIDL                                                                                   | _       | _        | MODE12       | FORM1      | FORM0                 | SSRC3                 | SSRC2                 | SSRC1                 | SSRC0                  | _                      | ASAM    | SAMP    | DONE    | 0000   |

| AD1CON2   | 342h          | PVCFG1  | PVCFG0                                                                                   | NVCFG0                                                                                   | _       | BUFREGEN | CSCNA        | _          | _                     | BUFS                  | SMPI4                 | SMPI3                 | SMPI2                  | SMPI1                  | SMPI0   | BUFM    | ALTS    | 0000   |

| AD1CON3   | 344h          | ADRC    | EXTSAM                                                                                   |                                                                                          | SAMC4   | SAMC3    | SAMC2        | SAMC1      | SAMC0                 | ADCS7                 | ADCS6                 | ADCS5                 | ADCS4                  | ADCS3                  | ADCS2   | ADCS1   | ADCS0   | 0000   |

| AD1CHS    | 348h          | CH0NB2  | CH0NB1                                                                                   | CH0NB0                                                                                   | CH0SB4  | CH0SB3   | CH0SB2       | CH0SB1     | CH0SB0                | CH0NA2                | CH0NA1                | CH0NA0                | CH0SA4                 | CH0SA3                 | CH0SA2  | CH0SA1  | CH0SA0  | 0000   |

| AD1CSSH   | 34Eh          | _       | CSS30                                                                                    | CSS29                                                                                    | CSS28   | CSS27    | CSS26        | _          | _                     | CSS23                 | CSS22                 | CSS21                 | CSS20 <sup>(1)</sup>   | CSS19 <sup>(1)</sup>   | CSS18   | CSS17   | CSS16   | 0000   |

| AD1CSSL   | 350h          | CSS15   | CSS14                                                                                    | CSS13                                                                                    | CSS12   | CSS11    | CSS10        | CSS9       | CSS8 <sup>(1,2)</sup> | CSS7 <sup>(1,2)</sup> | CSS6 <sup>(1,2)</sup> | CSS5 <sup>(1)</sup>   | CSS4                   | CSS3                   | CSS2    | CSS1    | CSS0    | 0000   |

| AD1CON5   | 354h          | ASEN    | LPEN                                                                                     | CTMREQ                                                                                   | BGREQ   | r        | _            | ASINT1     | ASINT0                | _                     | _                     | —                     | _                      | WM1                    | WM0     | CM1     | CM0     | 0000   |

| AD1CHITH  | 356h          | _       | —                                                                                        | —                                                                                        | —       | _        | _            | —          | —                     | CHH23                 | CHH22                 | CHH21                 | CHH20 <sup>(1)</sup>   | CHH19 <sup>(1)</sup>   | CHH18   | CHH17   | CHH16   | 0000   |

| AD1CHITL  | 358h          | CHH15   | CHH14                                                                                    | CHH13                                                                                    | CHH12   | CHH11    | CHH10        | CHH9       | CHH8 <sup>(1,2)</sup> | CHH7 <sup>(1,2)</sup> | CHH6 <sup>(1,2)</sup> | CHH5 <sup>(1)</sup>   | CHH4                   | CHH3                   | CHH2    | CHH1    | CHH0    | 0000   |

| AD1CTMENH | 360h          | _       | —                                                                                        | —                                                                                        | _       | _        | _            | —          | —                     | CTMEN23               | CTMEN22               | CTMEN21               | CTMEN20 <sup>(1)</sup> | CTMEN19 <sup>(1)</sup> | CTMEN18 | CTMEN17 | CTMEN16 | 0000   |

| AD1CTMENL | 362h          | CTMEN15 | CTMEN14                                                                                  | CTMEN13                                                                                  | CTMEN12 | CTMEN11  | CTMEN10      | CTMEN9     | CTMEN8((1,2)          | CTMEN7(1,2)           | CTMEN6(1,2)           | CTMEN5 <sup>(1)</sup> | CTMEN4                 | CTMEN3                 | CTMEN2  | CTMEN1  | CTMEN0  | 0000   |

$\label{eq:Legend: Legend: Legend: u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.$

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

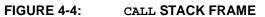

### 4.2.5 SOFTWARE STACK

In addition to its use as a working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as depicted in Figure 4-4.

For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6 in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

# 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit-wide program space and 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the Data Space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

See Table 4-35 and Figure 4-5 to know how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a Data Space word.

| REGISTER      |                                                                                                                                        |                                                                                                                                |                    | KI CONTRO        | LREGISTE       | ĸ              |        |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|----------------|----------------|--------|--|--|--|--|--|

| R/SO-0, HC    | R/W-0                                                                                                                                  | R/W-0                                                                                                                          | R/W-0              | U-0              | U-0            | U-0            | U-0    |  |  |  |  |  |

| WR            | WREN                                                                                                                                   | WRERR                                                                                                                          | PGMONLY            | _                | _              | _              | _      |  |  |  |  |  |

| bit 15        | •                                                                                                                                      |                                                                                                                                |                    | ·                |                |                | bit 8  |  |  |  |  |  |

|               |                                                                                                                                        |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

| U-0           | R/W-0                                                                                                                                  | R/W-0                                                                                                                          | R/W-0              | R/W-0            | R/W-0          | R/W-0          | R/W-0  |  |  |  |  |  |

| _             | ERASE                                                                                                                                  | NVMOP5                                                                                                                         | NVMOP4             | NVMOP3           | NVMOP2         | NVMOP1         | NVMOP0 |  |  |  |  |  |

| bit 7         |                                                                                                                                        |                                                                                                                                |                    |                  |                |                | bit 0  |  |  |  |  |  |

|               |                                                                                                                                        |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

| Legend:       |                                                                                                                                        | HC = Hardware                                                                                                                  | Clearable bit      | U = Unimple      | mented bit, re | ead as '0'     |        |  |  |  |  |  |

| R = Readable  | bit                                                                                                                                    | W = Writable bit                                                                                                               |                    | S = Settable     | Only bit       |                |        |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set                                                                                                               |                    | '0' = Bit is cle | eared          | x = Bit is unk | nown   |  |  |  |  |  |

| bit 15        | WR: Write Control bit (program or erase)<br>1 = Initiates a data EEPROM erase or write cycle (can be set, but not cleared in software) |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

|               | 0 = Write cycle is complete (cleared automatically by hardware)                                                                        |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

| bit 14        | WREN: Write Enable bit (erase or program)                                                                                              |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

|               | 1 = Enables a                                                                                                                          | an erase or progra                                                                                                             | m operation        |                  |                |                |        |  |  |  |  |  |

|               | 0 = No operat                                                                                                                          | tion allowed (devic                                                                                                            | ce clears this bit | on completion    | of the write/e | erase operatio | on)    |  |  |  |  |  |

| bit 13        |                                                                                                                                        | sh Error Flag bit                                                                                                              |                    |                  |                |                |        |  |  |  |  |  |

|               | 1 = A write operation is prematurely terminated (any MCLR or WDT Reset during programming                                              |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

|               | operation<br>0 = The write                                                                                                             | )<br>operation comple                                                                                                          | eted successfully  | /                |                |                |        |  |  |  |  |  |

| bit 12        |                                                                                                                                        | Program Only Enal                                                                                                              | ,                  | ,                |                |                |        |  |  |  |  |  |

| 511 12        |                                                                                                                                        | • •                                                                                                                            |                    | a target addres  | s(es) first    |                |        |  |  |  |  |  |

|               |                                                                                                                                        | <ul> <li>Write operation is executed without erasing target address(es) first</li> <li>Automatic erase-before-write</li> </ul> |                    |                  |                |                |        |  |  |  |  |  |

|               | Write operation                                                                                                                        | ons are preceded                                                                                                               | automatically by   | an erase of th   | e target addr  | ess(es).       |        |  |  |  |  |  |

| bit 11-7      | Unimplemen                                                                                                                             | ted: Read as '0'                                                                                                               |                    |                  |                |                |        |  |  |  |  |  |

| bit 6         |                                                                                                                                        | e Operation Selec                                                                                                              |                    |                  |                |                |        |  |  |  |  |  |

|               |                                                                                                                                        | an erase operation                                                                                                             |                    |                  |                |                |        |  |  |  |  |  |

|               |                                                                                                                                        | a write operation                                                                                                              |                    |                  |                |                |        |  |  |  |  |  |

| bit 5-0       | <b>NVMOP&lt;5:0&gt;:</b> Programming Operation Command Byte bits<br><u>Erase Operations (when ERASE bit is '1'):</u>                   |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

|               | $\frac{\text{Erase Operations (when ERASE bit is 1).}}{011010 = \text{Erase 8 words}}$                                                 |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

|               | 011001 = Erase 4 words                                                                                                                 |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

|               | 011000 = Era                                                                                                                           |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

|               |                                                                                                                                        | ase entire data EE                                                                                                             | -                  |                  |                |                |        |  |  |  |  |  |

|               | • •                                                                                                                                    | Operations (when                                                                                                               | n ERASE bit is '   | <u>0'):</u>      |                |                |        |  |  |  |  |  |

|               | 0001xx = Wr                                                                                                                            | ite 1 word                                                                                                                     |                    |                  |                |                |        |  |  |  |  |  |

|               |                                                                                                                                        |                                                                                                                                |                    |                  |                |                |        |  |  |  |  |  |

## REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

| R/W-0                                 | R-0, HSC                                                                                              | U-0               | U-0             | U-0               | U-0              | U-0             | U-0    |  |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------|-----------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| ALTIVT                                | DISI                                                                                                  | —                 | —               | —                 | —                | —               | —      |  |  |  |  |

| bit 15                                |                                                                                                       |                   |                 |                   |                  |                 | bit 8  |  |  |  |  |

|                                       |                                                                                                       |                   |                 |                   |                  |                 |        |  |  |  |  |

| U-0                                   | U-0                                                                                                   | U-0               | U-0             | U-0               | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| —                                     | —                                                                                                     | —                 | —               | —                 | INT2EP           | INT1EP          | INT0EP |  |  |  |  |

| bit 7                                 |                                                                                                       |                   |                 |                   |                  |                 | bit 0  |  |  |  |  |

|                                       |                                                                                                       |                   |                 |                   |                  |                 |        |  |  |  |  |

| Legend:                               |                                                                                                       | HSC = Hardw       | are Settable/C  | learable bit      |                  |                 |        |  |  |  |  |

| R = Readab                            | le bit                                                                                                | W = Writable b    | oit             | U = Unimplem      | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value a                          | t POR                                                                                                 | '1' = Bit is set  |                 | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |  |  |  |  |

|                                       |                                                                                                       |                   |                 |                   |                  |                 |        |  |  |  |  |

| bit 15                                | ALTIVT: Enat                                                                                          | ole Alternate Int | errupt Vector 7 | Table bit         |                  |                 |        |  |  |  |  |

|                                       |                                                                                                       | rnate Interrupt   | •               | ,                 |                  |                 |        |  |  |  |  |

|                                       |                                                                                                       | ndard (default) I | •               | r Table (IVT)     |                  |                 |        |  |  |  |  |

| bit 14                                | 21011 2101                                                                                            | struction Status  |                 |                   |                  |                 |        |  |  |  |  |

|                                       | 1 = DISI instruction is active<br>0 = DISI instruction is not active                                  |                   |                 |                   |                  |                 |        |  |  |  |  |

| bit 13-3                              |                                                                                                       | ted: Read as '0   |                 |                   |                  |                 |        |  |  |  |  |

| bit 2                                 | •                                                                                                     |                   |                 | Polarity Solact k | ait              |                 |        |  |  |  |  |

|                                       | INT2EP: External Interrupt 2 Edge Detect Polarity Select bit<br>1 = Interrupt is on the negative edge |                   |                 |                   |                  |                 |        |  |  |  |  |

|                                       | 0 = Interrupt is on the positive edge                                                                 |                   |                 |                   |                  |                 |        |  |  |  |  |

| bit 1                                 | <b>INT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit                                   |                   |                 |                   |                  |                 |        |  |  |  |  |

|                                       | 1 = Interrupt is on the negative edge                                                                 |                   |                 |                   |                  |                 |        |  |  |  |  |

| 0 = Interrupt is on the positive edge |                                                                                                       |                   |                 |                   |                  |                 |        |  |  |  |  |

| bit 0                                 | INT0EP: External Interrupt 0 Edge Detect Polarity Select bit                                          |                   |                 |                   |                  |                 |        |  |  |  |  |

|                                       |                                                                                                       | s on the negativ  | U U             |                   |                  |                 |        |  |  |  |  |

|                                       | 0 = Interrupt i                                                                                       | s on the positive | e edge          |                   |                  |                 |        |  |  |  |  |

### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0                          | U-0                                      | U-0                                                                                                                                     | U-0                             | U-0              | R/W-1            | R/W-0              | R/W-0   |  |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|--------------------|---------|--|

| _                            |                                          |                                                                                                                                         |                                 | _                | U2ERIP2          | U2ERIP1            | U2ERIP0 |  |

| oit 15                       |                                          |                                                                                                                                         | •                               |                  |                  |                    | bit 8   |  |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                    |         |  |

| U-0                          | R/W-1                                    | R/W-0                                                                                                                                   | R/W-0                           | U-0              | U-0              | U-0                | U-0     |  |

| —                            | U1ERIP2                                  | U1ERIP1                                                                                                                                 | U1ERIP0                         | —                | —                | —                  | —       |  |

| bit 7                        |                                          |                                                                                                                                         |                                 |                  |                  |                    | bit 0   |  |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                    |         |  |

| Legend:                      |                                          |                                                                                                                                         |                                 |                  |                  |                    |         |  |

| R = Readab                   | ole bit                                  | W = Writable                                                                                                                            | bit                             | U = Unimpler     | mented bit, read | d as '0'           |         |  |

| -n = Value at POR            |                                          | '1' = Bit is set                                                                                                                        |                                 | '0' = Bit is cle | ared             | x = Bit is unknown |         |  |

| bit 10-8<br>bit 7<br>bit 6-4 | <pre>111 = Interru </pre>                | >: UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>>: UART1 Error<br>pt is Priority 7 ( | highest priority<br>abled<br>o' | interrupt)       |                  |                    |         |  |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '                                                             | abled                           | interrupt)       |                  |                    |         |  |

### REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

## 8.4 Interrupt Setup Procedures

### 8.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

## 8.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR (Interrupt Service Routine) and initialize the IVT with the correct vector address depends on the programming language (i.e., C or assembly), and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

## 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, 0Eh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period. Level 7 interrupt sources are not disabled by the DISI instruction.

# **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, "Power-Saving Features with VBAT" (DS30622).

This FRM describes some features which

are not implemented in this device. Sections related to the VBAT pin and Deep Sleep do not apply to the PIC24FV16KM204 family.

The PIC24FV16KM204 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

# 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

## 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The 'C' syntax of the  $\ensuremath{\mathtt{PWRSAV}}$  instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as the clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification on the I/O ports or peripherals that use an External Clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: 'C' POWER-SAVING ENTRY

# REGISTER 15-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                 |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                          |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                         |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                     |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                    |

|       | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul> |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                               |

|       | 1 = Receive buffer has overflowed                                                                                                                                             |

|       | 0 = Receive buffer has not overflowed (clearing a previously set OERR bit ( $1 \rightarrow 0$ transition) will reset the receiver buffer and the RSR to the empty state)      |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                    |

|       | <ul> <li>1 = Receive buffer has data; at least one more characters can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                |

© 2013 Microchip Technology Inc.

#### 16.2.5 RTCVAL REGISTER MAPPINGS

### REGISTER 16-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _      | —   | _   | —   | —   | —   | —   | —     |