Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

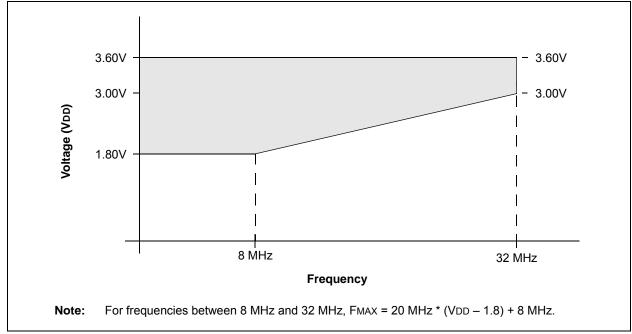

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16km204t-i-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Pin Diagrams**

| 20-Pin PDIP/SSOP/SOIC | RA5       1       20       VDD         RA0       2       19       VSs         RA1       3       18       RB15         RB0       4       17       RB14         RB1       5       RB12         RA2       6       9       16         RA3       8       20       15         RB4       9       12       RB8         RA4       10       11       RB7 |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dia | Pin Features           PIC24F08KM101         PIC24FVKM08KM101                    |                                                                      |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| Pin |                                                                                  |                                                                      |  |  |  |  |  |

| 1   | MCLR/Vpp/RA5                                                                     |                                                                      |  |  |  |  |  |

| 2   | PGEC2/CVREF+/VREF+/AN0/CN2/RA0                                                   |                                                                      |  |  |  |  |  |

| 3   | PGED2/CVREF-/VREF-/AN1/CN3/RA1                                                   |                                                                      |  |  |  |  |  |

| 4   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0                                         |                                                                      |  |  |  |  |  |

| 5   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                                                   |                                                                      |  |  |  |  |  |

| 6   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                                                    |                                                                      |  |  |  |  |  |

| 7   | OSCI/CLKI/AN13/C1INB/CN30/RA2                                                    |                                                                      |  |  |  |  |  |

| 8   | OSCO/CLKO/AN14/C1INA/CN29/RA3                                                    |                                                                      |  |  |  |  |  |

| 9   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4                                                  |                                                                      |  |  |  |  |  |

| 10  | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/                                       | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/RA4                        |  |  |  |  |  |

| 11  | AN19/U1TX/CTED1/INT0/CN23/RB7                                                    | AN19/U1TX/CTED1/INT0/CN23/RB7 AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7 |  |  |  |  |  |

| 12  | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8                                             |                                                                      |  |  |  |  |  |

| 13  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4                                      | /CN21/RB9                                                            |  |  |  |  |  |

| 14  | IC1/OC1A/INT2/CN8/RA6                                                            | VCAP OR VDDCORE                                                      |  |  |  |  |  |

| 15  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12 AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |                                                                      |  |  |  |  |  |

| 16  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13                                              |                                                                      |  |  |  |  |  |

| 17  | CVREF/AN10/SDI1/C10UT/OCFA/CTED5/INT1/CN12/RB14                                  |                                                                      |  |  |  |  |  |

| 18  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15                                               |                                                                      |  |  |  |  |  |

| 19  | Vss/AVss                                                                         |                                                                      |  |  |  |  |  |

| 20  | Vdd/AVdd                                                                         |                                                                      |  |  |  |  |  |

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                | FV                               |                                  |               |                        |                |            |     |                                               |  |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|------------|-----|-----------------------------------------------|--|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |            |     |                                               |  |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O Buffer |     | Description                                   |  |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O        | I2C | MSSP1 I <sup>2</sup> C Clock                  |  |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O        | I2C | MSSP1 I <sup>2</sup> C Data                   |  |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O        | I2C | MSSP2 I <sup>2</sup> C Clock                  |  |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O        | I2C | MSSP2 I <sup>2</sup> C Data                   |  |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι          | ST  | Secondary Clock Digital Input                 |  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι          | ANA | Secondary Oscillator Input                    |  |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι          | ANA | Secondary Oscillator Output                   |  |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι          | ST  | Timer1 Digital Input Cock                     |  |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι          | ST  | MCCP/SCCP Time Base Clock Input A             |  |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι          | ST  | MCCP/SCCP Time Base Clock Input B             |  |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι          | ST  | UART1 Clear-To-Send Input                     |  |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0          | _   | UART1 Request-To-Send Output                  |  |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0          | —   | UART1 16x Baud Rate Clock Output              |  |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι          | ST  | UART1 Receive                                 |  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0          | _   | UART1 Transmit                                |  |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I          | ST  | UART2 Clear-To-Send Input                     |  |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0          | _   | UART2 Request-To-Send Output                  |  |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0          | —   | UART2 16x Baud Rate Clock Output              |  |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι          | ST  | UART2 Receive                                 |  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0          | _   | UART2 Transmit                                |  |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι          | ANA | Ultra Low-Power Wake-up Input                 |  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р          | —   | Regulator External Filter Capacitor Connectio |  |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р          | —   | Device Positive Supply Voltage                |  |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р          | —   | Microcontroller Core Supply Voltage           |  |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р          | —   | High-Voltage Programming Pin                  |  |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I          | ANA | A/D Reference Voltage Positive Input          |  |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι          | ANA | A/D Reference Voltage Negative Input          |  |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р          | —   | Device Ground Return Voltage                  |  |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

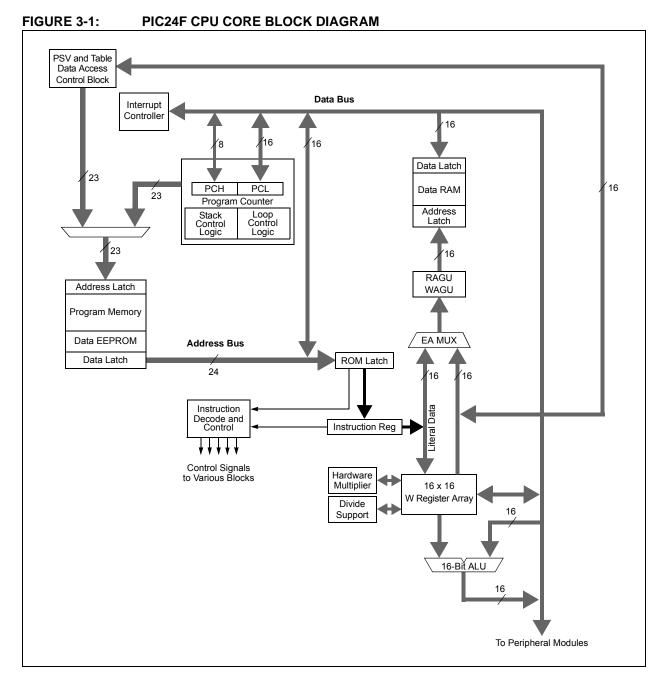

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

|  | REGISTER 3-2: | CORCON: CPU CONTROL REGISTER |

|--|---------------|------------------------------|

|--|---------------|------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   |     | —   |     | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   |     | —   | IPL3 <sup>(1)</sup> | PSV   | —   | —     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settable   | e/Clearable bit    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in Data Space                                                                                    |

|          | 0 = Program space is not visible in Data Space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with Data Memory Space Addressing and makes it possible to access data in the program memory space.

### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables, located from 000004h to 0000FFh, and 000104h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. **Section 8.1 "Interrupt Vector Table (IVT)**" discusses the Interrupt Vector Tables in more detail.

### 4.1.3 DATA EEPROM

In the PIC24FV16KM204 family, the data EEPROM is mapped to the top of the user program memory space, starting at address, 7FFE00, and expanding up to address, 7FFFF.

The data EEPROM is organized as 16-bit-wide memory and 256 words deep. This memory is accessed using Table Read and Write operations similar to the user code memory.

### 4.1.4 DEVICE CONFIGURATION WORDS

Table 4-1 provides the addresses of the device Configuration Words for the PIC24FV16KM204 family. Their location in the memory map is displayed in Figure 4-1.

Refer to **Section 25.1** "**Configuration Bits**" for more information on device Configuration Words.

# TABLE 4-1: DEVICE CONFIGURATION WORDS FOR PIC24FXXXXX FAMILY DEVICES

| Configuration Word | Configuration Word<br>Addresses |

|--------------------|---------------------------------|

| FBS                | F80000                          |

| FGS                | F80004                          |

| FOSCSEL            | F80006                          |

| FOSC               | F80008                          |

| FWDT               | F8000A                          |

| FPOR               | F8000C                          |

| FICD               | F8000E                          |

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION msw most significant word least significant word PC Address (Isw Address) Address 16 8 Λ 23 000000h 000001h 00000000 0000000 000002h 000003h 000004h 00000000 000005h 0000000 000006h 000007h Instruction Width Program Memory Phantom' Byte (read as '0')

| R/W-0         | U-0                                                                                    | R/W-0                                  | R/W-0                     | R/W-0             | U-0              | U-0             | R/W-0  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------|----------------------------------------|---------------------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| NVMIE         |                                                                                        | AD1IE                                  | U1TXIE                    | U1RXIE            |                  | _               | CCT2IE |  |  |  |  |

| bit 15        | +                                                                                      |                                        |                           | •                 | •                |                 | bit    |  |  |  |  |

| R/W-0         | R/W-0                                                                                  | R/W-0                                  | U-0                       | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| CCT1IE        | CCP4IE                                                                                 | CCP3IE                                 | <u> </u>                  | T1IE              | CCP2IE           | CCP1IE          | INTOIE |  |  |  |  |

| bit 7         |                                                                                        |                                        |                           | 1.112             |                  |                 | bit    |  |  |  |  |

|               |                                                                                        |                                        |                           |                   |                  |                 |        |  |  |  |  |

| Legend:       |                                                                                        |                                        |                           |                   |                  |                 |        |  |  |  |  |

| R = Readabl   |                                                                                        | W = Writable                           |                           | •                 | nented bit, read |                 |        |  |  |  |  |

| -n = Value at | POR                                                                                    | '1' = Bit is set                       |                           | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |  |  |  |  |

| bit 15        | NVMIE: NVM                                                                             | Interrupt Enat                         | ole bit                   |                   |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt r                                                                        | equest is enab                         | oled                      |                   |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt r                                                                        | request is not e                       | enabled                   |                   |                  |                 |        |  |  |  |  |

| bit 14        | Unimplemen                                                                             | ted: Read as '                         | 0'                        |                   |                  |                 |        |  |  |  |  |

| bit 13        | AD1IE: A/D C                                                                           | Conversion Cor                         | nplete Interrup           | t Enable bit      |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enat                        |                           |                   |                  |                 |        |  |  |  |  |

|               | -                                                                                      | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 12        |                                                                                        |                                        | r Interrupt Ena           | ble bit           |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enab                        |                           |                   |                  |                 |        |  |  |  |  |

| L:1 44        | -                                                                                      | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 11        | <b>U1RXIE:</b> UART1 Receiver Interrupt Enable bit<br>1 = Interrupt request is enabled |                                        |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enaction of equest is not e |                           |                   |                  |                 |        |  |  |  |  |

| bit 10-9      | •                                                                                      | ted: Read as '                         |                           |                   |                  |                 |        |  |  |  |  |

| bit 8         | CCT2IE: Capture/Compare 2 Timer Interrupt Enable bit                                   |                                        |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enab                        |                           |                   |                  |                 |        |  |  |  |  |

| bit 7         | •                                                                                      | request is not e<br>ture/Compare       | nabled<br>1 Timer Interru | nt Enable bit     |                  |                 |        |  |  |  |  |

|               | •                                                                                      | request is enat                        |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 6         | CCP4IE: Cap                                                                            | ture/Compare                           | 4 Event Interru           | ipt Enable bit    |                  |                 |        |  |  |  |  |

|               |                                                                                        | equest is enab                         |                           |                   |                  |                 |        |  |  |  |  |

|               | -                                                                                      | request is not e                       |                           |                   |                  |                 |        |  |  |  |  |

| bit 5         | CCP3IE: Cap                                                                            | ture/Compare                           | 3 Event Interru           | ipt Enable bit    |                  |                 |        |  |  |  |  |

|               |                                                                                        | equest is enab                         |                           |                   |                  |                 |        |  |  |  |  |

|               | -                                                                                      | equest is not e                        |                           |                   |                  |                 |        |  |  |  |  |

| bit 4         | -                                                                                      | ted: Read as '                         |                           |                   |                  |                 |        |  |  |  |  |

| bit 3         |                                                                                        | Interrupt Enab                         |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enat<br>request is not e    |                           |                   |                  |                 |        |  |  |  |  |

| bit 2         | -                                                                                      | -                                      | 2 Event Interru           | unt Enchlo hit    |                  |                 |        |  |  |  |  |

| DIL Z         | •                                                                                      | •                                      |                           | ipt Enable bit    |                  |                 |        |  |  |  |  |

|               |                                                                                        | request is enat<br>request is not e    |                           |                   |                  |                 |        |  |  |  |  |

| bit 1         | -                                                                                      | -                                      | 1 Event Interru           | ipt Enable bit    |                  |                 |        |  |  |  |  |

|               | -                                                                                      | equest is enab                         |                           |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | equest is not e                        |                           |                   |                  |                 |        |  |  |  |  |

| bit 0         | INT0IE: Exter                                                                          | nal Interrupt 0                        | Enable bit                |                   |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt r                                                                        | equest is enab                         | oled                      |                   |                  |                 |        |  |  |  |  |

|               |                                                                                        | equest is not e                        | mahlad                    |                   |                  |                 |        |  |  |  |  |

### REGISTER 8-12: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

NOTES:

| R/W-0                             | R/W-0                        | U-0                                 | R/W-0                          | U-0                                                  | U-0           | U-0             | U-0             |

|-----------------------------------|------------------------------|-------------------------------------|--------------------------------|------------------------------------------------------|---------------|-----------------|-----------------|

| PWMRSEN                           | ASDGM                        | —                                   | SSDG                           | —                                                    | —             | _               | —               |

| bit 15                            |                              |                                     |                                |                                                      |               |                 | bit 8           |

|                                   |                              |                                     |                                |                                                      |               |                 |                 |

| R/W-0                             | R/W-0                        | R/W-0                               | R/W-0                          | R/W-0                                                | R/W-0         | R/W-0           | R/W-0           |

| ASDG7                             | ASDG6                        | ASDG5                               | ASDG4                          | ASDG3                                                | ASDG2         | ASDG1           | ASDG0           |

| bit 7                             |                              |                                     |                                |                                                      |               |                 | bit C           |

| Legend:                           |                              |                                     |                                |                                                      |               |                 |                 |

| R = Readable bit W = Writable bit |                              | bit                                 | U = Unimplem                   | nented bit, read                                     | d as '0'      |                 |                 |

| -n = Value at                     | POR                          | '1' = Bit is set                    |                                | '0' = Bit is clea                                    | ared          | x = Bit is unkr | nown            |

| bit 14                            | ASDGM: CCI<br>1 = Wait until | Px Auto-Shutdo                      | own Gate Mode<br>Base Reset or | e to resume PW<br>e Enable bit<br>r rollover for shu |               |                 |                 |

| bit 13                            |                              | ted: Read as '                      | -                              |                                                      |               |                 |                 |

| bit 12                            | •                            | Software Shut                       |                                | ontrol bit                                           |               |                 |                 |

|                                   | •                            | force auto-sh<br>bit still applies) |                                | clock gate or                                        | input capture | signal gate evo | ent (setting of |

|                                   | 0 = Normal n                 | nodule operatio                     | n                              |                                                      |               |                 |                 |

| bit 11-8                          |                              | tod. Pood as "                      | י'                             |                                                      |               |                 |                 |

| DIL II-O                          | Unimplemen                   | leu. Reau as                        |                                |                                                      |               |                 |                 |

| bit 7-0                           | •                            |                                     |                                | g Source Enable                                      | e bits        |                 |                 |

### REGISTER 13-3: CCPxCON2L: CCPx CONTROL 2 LOW REGISTERS

#### TABLE 13-7: AUTO-SHUTDOWN AND GATING SOURCES

| ASDG<7:0> Bits | Auto-Shutdown/Gating Source |

|----------------|-----------------------------|

| 0              | Comparator 1 Output         |

| 1              | Comparator 2 Output         |

| 2              | Comparator 3 Output         |

| 3              | SCCP4 Output Compare        |

| 4              | SCCP5 Output Compare        |

| 5              | CLC1 Output                 |

| 6              | OCFA Fault Input            |

| 7              | OCFB Fault Input            |

#### 16.2.6 ALRMVAL REGISTER MAPPINGS

### REGISTER 16-8: ALMTHDY: ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0      | U-0 | U-0     | R/W-x   | R/W-x            | R/W-x            | R/W-x   | R/W-x            |

|----------|-----|---------|---------|------------------|------------------|---------|------------------|

| —        | —   | —       | MTHTEN0 | MTHONE3          | MTHONE2          | MTHONE1 | MTHONE0          |

| bit 15   |     |         |         |                  |                  |         | bit 8            |

|          |     |         |         |                  |                  |         |                  |

| 11.0     |     | D/1/    |         |                  |                  |         |                  |

| U-0      | U-0 | R/W-x   | R/W-x   | R/W-x            | R/W-x            | R/W-x   | R/W-x            |

| <u> </u> |     | DAYTEN1 | DAYTEN0 | R/W-X<br>DAYONE3 | R/W-X<br>DAYONE2 | DAYONE1 | R/W-x<br>DAYONE0 |

### Legend:

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13<br>bit 12 | <b>Unimplemented:</b> Read as '0'<br><b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit<br>Contains a value of '0' or '1'. |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8            | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits<br>Contains a value from 0 to 9.                                          |

| bit 7-6             | Unimplemented: Read as '0'                                                                                                                   |

| bit 5-4             | <b>DAYTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Day's Tens Digit bits<br>Contains a value from 0 to 3.                               |

| bit 3-0             | <b>DAYONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Day's Ones Digit bits<br>Contains a value from 0 to 9.                               |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 16-9: ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0    | U-0    | U-0    | R/W-x  | R/W-x  | R/W-x  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | —      | —      | —      | WDAY2  | WDAY1  | WDAY0  |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

| —      | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits<br>Contains a value from 0 to 6. |

|           |                                                                                              |

| bit 7-6   | Unimplemented: Read as '0'                                                                   |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits                             |

|           | Contains a value from 0 to 2.                                                                |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits                             |

|           | Contains a value from 0 to 9.                                                                |

|           |                                                                                              |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 G2D4T G2D4N G2D3T G2D3N G2D2T G2D2N G2D1T G2D1N bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 G1D4T G1D2N G1D4N G1D3T G1D3N G1D2T G1D1T G1D1N bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared x = Bit is unknown '1' = Bit is set bit 15 G2D4T: Gate 2 Data Source 4 True Enable bit 1 = The Data Source 4 inverted signal is enabled for Gate 2 0 = The Data Source 4 inverted signal is disabled for Gate 2 bit 14 G2D4N: Gate 2 Data Source 4 Negated Enable bit 1 = The Data Source 4 inverted signal is enabled for Gate 2 0 = The Data Source 4 inverted signal is disabled for Gate 2 bit 13 G2D3T: Gate 2 Data Source 3 True Enable bit 1 = The Data Source 3 inverted signal is enabled for Gate 2 0 = The Data Source 3 inverted signal is disabled for Gate 2 bit 12 G2D3N: Gate 2 Data Source 3 Negated Enable bit 1 = The Data Source 3 inverted signal is enabled for Gate 2 0 = The Data Source 3 inverted signal is disabled for Gate 2 bit 11 G2D2T: Gate 2 Data Source 2 True Enable bit 1 = The Data Source 2 inverted signal is enabled for Gate 2 0 = The Data Source 2 inverted signal is disabled for Gate 2 bit 10 G2D2N: Gate 2 Data Source 2 Negated Enable bit 1 = The Data Source 2 inverted signal is enabled for Gate 2 0 = The Data Source 2 inverted signal is disabled for Gate 2 bit 9 G2D1T: Gate 2 Data Source 1 True Enable bit 1 = The Data Source 1 inverted signal is enabled for Gate 2 0 = The Data Source 1 inverted signal is disabled for Gate 2 bit 8 G2D1N: Gate 2 Data Source 1 Negated Enable bit 1 = The Data Source 2 inverted signal is enabled for Gate 1 0 = The Data Source 2 inverted signal is disabled for Gate 1 bit 7 G1D4T: Gate 1 Data Source 4 True Enable bit 1 = The Data Source 4 inverted signal is enabled for Gate 1 0 = The Data Source 4 inverted signal is disabled for Gate 1 bit 6 G1D4N: Gate 1 Data Source 4 Negated Enable bit 1 = The Data Source 4 inverted signal is enabled for Gate 1 0 = The Data Source 4 inverted signal is disabled for Gate 1 G1D3T: Gate 1 Data Source 3 True Enable bit bit 5 1 = The Data Source 3 inverted signal is enabled for Gate 1 0 = The Data Source 3 inverted signal is disabled for Gate 1 bit 4 G1D3N: Gate 1 Data Source 3 Negated Enable bit 1 = The Data Source 3 inverted signal is enabled for Gate 1 0 = The Data Source 3 inverted signal is disabled for Gate 1

To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs and/or select band gap reference inputs (ANSx registers).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- e) Configure the MODE12 bit to select A/D resolution (AD1CON1<10>).

- f) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- g) Select the interrupt rate (AD1CON2<6:2>).

- h) Turn on the A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

To perform an A/D sample and conversion using Threshold Detect scanning:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs (ANSx registers).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- e) Configure the MODE12 bit to select A/D resolution (AD1CON1<10>).

- f) Select how the conversion results are presented in the buffer (AD1CON1<9:8>).

- g) Select the interrupt rate (AD1CON2<6:2>).

- 2. Configure the threshold compare channels:

- a) Enable auto-scan; set the ASEN bit (AD1CON5<15>).

- b) Select the Compare mode, "Greater Than, Less Than or Windowed"; set the CMx bits (AD1CON5<1:0>).

- c) Select the threshold compare channels to be scanned (AD1CSSH, AD1CSSL).

- d) If the CTMU is required as a current source for a threshold compare channel, enable the corresponding CTMU channel (AD1CTMENH, AD1CTMENL).

- e) Write the threshold values into the corresponding ADC1BUFx registers.

- f) Turn on the A/D module (AD1CON1<15>).

- Note: If performing an A/D sample and conversion, using Threshold Detect in Sleep Mode, the RC A/D clock source must be selected before entering into Sleep mode.

- 3. Configure the A/D interrupt (OPTIONAL):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

| PVCFG<br>bit 15<br>R/W-0 | 1 PVCFG0                                                                                 | 1                                                   |                     |                                         |                 |                     |            |

|--------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------|-----------------------------------------|-----------------|---------------------|------------|

|                          |                                                                                          | NVCFG0                                              |                     | BUFREGEN                                | CSCNA           | —                   | _          |

|                          |                                                                                          |                                                     |                     |                                         |                 |                     | bit        |

| R/W-U                    | R/W-0                                                                                    | R/W-0                                               | R/W-0               | R/W-0                                   | R/W-0           | R/W-0               | R/W-0      |

| BUFS <sup>(1</sup>       | ) SMPI4                                                                                  | SMPI3                                               | SMPI2               | SMPI1                                   | SMPI0           | BUFM <sup>(1)</sup> | ALTS       |

| oit 7                    | •                                                                                        |                                                     |                     | · ·                                     |                 | · · ·               | bit        |

| _egend:                  |                                                                                          |                                                     |                     |                                         |                 |                     |            |

| R = Reada                | able bit                                                                                 | W = Writable b                                      | pit                 | U = Unimpleme                           | ented bit, read | d as '0'            |            |

| n = Value                | at POR                                                                                   | '1' = Bit is set                                    |                     | '0' = Bit is clear                      | red             | x = Bit is unkno    | own        |

| bit 15-14                | <b>PVCFG&lt;1:0&gt;</b><br>11 = 4 * Inter<br>10 = 2 * Inter<br>01 = Externa<br>00 = AVDD | rnal V <sub>BG</sub> (2)<br>rnal VBG <sup>(3)</sup> | r Positive Volt     | age Reference C                         | configuration I | bits                |            |

| oit 13                   | <b>NVCFG0:</b> A/I<br>1 = External<br>0 = AVss                                           |                                                     | gative Voltage      | Reference Conf                          | iguration bits  |                     |            |

| oit 12                   | Unimplemen                                                                               | ted: Read as '0                                     | ,                   |                                         |                 |                     |            |

| oit 11                   | -                                                                                        | A/D Buffer Reg                                      |                     | oit                                     |                 |                     |            |

|                          | 1 = Conversi                                                                             | -                                                   | led into a buff     | er location deterr                      | nined by the    | converted chanr     | nel        |

| oit 10                   | CSCNA: Sca                                                                               | n Input Selectio                                    | ns for CH0+ S       | S/H Input for MUX                       | K A Setting bi  | t                   |            |

|                          | 1 = Scans in<br>0 = Does not                                                             |                                                     |                     |                                         |                 |                     |            |

| oit 9-8                  | Unimplemen                                                                               | ted: Read as '0                                     | ,                   |                                         |                 |                     |            |

| oit 7                    | BUFS: A/D B                                                                              | uffer Fill Status                                   | bit <sup>(1)</sup>  |                                         |                 |                     |            |

|                          |                                                                                          | • • • •                                             |                     | er; user should ac<br>r; user should ac |                 |                     |            |

| oit 6-2                  | SMPI<4:0>:                                                                               | Interrupt Sample                                    | e Rate Select       | bits                                    |                 |                     |            |

|                          |                                                                                          | •                                                   | •                   | e conversion for<br>e conversion for    |                 | •                   |            |

|                          | 00000 = Inte                                                                             | errupts at the co                                   | mpletion of th      | e conversion for<br>e conversion for    |                 | ample               |            |

| bit 1                    | 1 = Starts filli<br>interrupt<br>0 = Starts fill                                         | (Split Buffer mo                                    | address, ADC<br>de) | 1BUF0, on the fin                       | -               |                     |            |

| oit O                    | •                                                                                        | ate Input Sampl                                     | e Mode Selec        | t bit                                   |                 |                     |            |

|                          | 1 = Uses cha                                                                             |                                                     | cts for Sample      | e A on the first sa                     | mple and Sa     | mple B on the n     | ext sample |

| Note 1:<br>2:            | This is only applid<br>used when BUFM<br>PIC24FV16KMX                                    | <b>/</b> = 1.                                       |                     |                                         |                 |                     |            |

### REGISTER 22-1: CMxCON: COMPARATOR x CONTROL REGISTERS

| R/W-0                 | R/W-0                                                                                             | R/W-0                                | R/W-0            | U-0                            | U-0                                   | R/W-0            | R-0              |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------|--------------------------------------|------------------|--------------------------------|---------------------------------------|------------------|------------------|--|--|--|

| CON                   | COE                                                                                               | CPOL                                 | CLPWR            | _                              |                                       | CEVT             | COUT             |  |  |  |

| bit 15                | •                                                                                                 |                                      |                  |                                |                                       |                  | bit 8            |  |  |  |

| R/W-0                 | R/W-0                                                                                             | U-0                                  | R/W-0            | R/W-0                          | U-0                                   | R/W-0            | R/W-0            |  |  |  |

| EVPOL1 <sup>(2)</sup> | EVPOL0 <sup>(2)</sup>                                                                             | _                                    | CREF1            | CREF0                          | _                                     | CCH1             | CCH0             |  |  |  |

| bit 7                 |                                                                                                   |                                      | UNL I            | UNLI U                         |                                       | 00111            | bit (            |  |  |  |

| Legend:               |                                                                                                   |                                      |                  |                                |                                       |                  |                  |  |  |  |

| R = Readable          | e bit                                                                                             | W = Writable                         | bit              | U = Unimplen                   | nented bit, read                      | d as '0'         |                  |  |  |  |

| -n = Value at         | POR                                                                                               | '1' = Bit is set                     |                  | '0' = Bit is clea              |                                       | x = Bit is unkr  | nown             |  |  |  |

|                       |                                                                                                   |                                      |                  |                                |                                       |                  |                  |  |  |  |

| bit 15                | CON: Compa                                                                                        | rator x Enable                       | bit              |                                |                                       |                  |                  |  |  |  |

|                       |                                                                                                   | tor is enabled                       |                  |                                |                                       |                  |                  |  |  |  |

| bit 11                | •                                                                                                 | tor is disabled                      | Enchlo hit       |                                |                                       |                  |                  |  |  |  |

| bit 14                | •                                                                                                 | rator x Output<br>itor output is pr  |                  | vOLIT nin                      |                                       |                  |                  |  |  |  |

|                       |                                                                                                   | itor output is pr                    |                  |                                |                                       |                  |                  |  |  |  |

| bit 13                | CPOL: Comp                                                                                        | arator x Outpu                       | t Polarity Selec | ct bit                         |                                       |                  |                  |  |  |  |

|                       |                                                                                                   | tor output is in                     |                  |                                |                                       |                  |                  |  |  |  |

|                       | •                                                                                                 | tor output is no                     |                  |                                |                                       |                  |                  |  |  |  |

| bit 12                | <b>CLPWR:</b> Comparator x Low-Power Mode Select bit<br>1 = Comparator operates in Low-Power mode |                                      |                  |                                |                                       |                  |                  |  |  |  |

|                       | •                                                                                                 | tor operates in<br>tor does not op   |                  |                                |                                       |                  |                  |  |  |  |

| bit 11-10             | -                                                                                                 | ted: Read as '                       |                  | owermode                       |                                       |                  |                  |  |  |  |

| bit 9                 | -                                                                                                 | arator x Event                       |                  |                                |                                       |                  |                  |  |  |  |

|                       | •                                                                                                 |                                      |                  | <1:0>, has occu                | irred; subseque                       | ent Triggers and | d interrupts are |  |  |  |

|                       | disabled                                                                                          | until the bit is c                   | leared           |                                |                                       | 00               | ·                |  |  |  |

|                       | -                                                                                                 | tor event has r                      |                  |                                |                                       |                  |                  |  |  |  |

| bit 8                 |                                                                                                   | arator x Outpu                       | t bit            |                                |                                       |                  |                  |  |  |  |

|                       | $\frac{\text{When CPOL}}{1 = \text{VIN} + > \text{VI}}$                                           |                                      |                  |                                |                                       |                  |                  |  |  |  |

|                       | 0 = VIN + < VI                                                                                    |                                      |                  |                                |                                       |                  |                  |  |  |  |

|                       | When CPOL                                                                                         |                                      |                  |                                |                                       |                  |                  |  |  |  |

|                       | 1 = VIN + < VI $0 = VIN + > VI$                                                                   |                                      |                  |                                |                                       |                  |                  |  |  |  |

| bit 7-6               |                                                                                                   |                                      | Interrupt Pola   | rity Select bits <sup>(2</sup> | 2)                                    |                  |                  |  |  |  |

| DIL 7-0               |                                                                                                   | 00                                   |                  | n any change o                 |                                       | or output (while | $\sim CEVT = 0$  |  |  |  |

|                       |                                                                                                   |                                      |                  | n the high-to-lo               |                                       |                  |                  |  |  |  |

|                       |                                                                                                   |                                      |                  | n the low-to-hig               | h transition of                       | the comparator   | output           |  |  |  |

|                       |                                                                                                   | event/interrupt                      | •                | lisabled                       |                                       |                  |                  |  |  |  |

| bit 5                 | •                                                                                                 | ted: Read as '                       |                  |                                |                                       |                  |                  |  |  |  |

| bit 4-3               |                                                                                                   | -                                    |                  | ect bits (non-inv              | erting input)                         |                  |                  |  |  |  |

|                       |                                                                                                   | erting input cor<br>erting input cor |                  |                                |                                       |                  |                  |  |  |  |

|                       | 01 = Non-inve                                                                                     | erting input cor                     | nects to the in  | ternal CVREF vo                | oltage                                |                  |                  |  |  |  |

|                       | 00 = Non-inve                                                                                     | erting input cor                     | nects to the C   | xINA pin                       |                                       |                  |                  |  |  |  |

| Note 1: BC            | GBUF1 voltage                                                                                     | is configured b                      | y BUFREF1<1      | :0> (BUFCON                    | 0<1:0>).                              |                  |                  |  |  |  |

| <b>•</b> 161          |                                                                                                   | ·                                    |                  |                                | · · · · · · · · · · · · · · · · · · · |                  |                  |  |  |  |

2: If the EVPOL<1:0> bits are set to a value other than '00', the first interrupt generated will occur on any transition of COUT. Subsequent interrupts will occur based on the EVPOLx bits setting.

| R/P-1        | R/P-1                                                                                                                                                                                 | R/P-1                             | R/P-1           | R/P-1             | R/P-1            | R/P-1           | R/P-1  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| FWDTEN1      | WINDIS                                                                                                                                                                                | FWDTEN0                           | FWPSA           | WDTPS3            | WDTPS2           | WDTPS1          | WDTPS0 |  |  |  |  |

| bit 7        |                                                                                                                                                                                       |                                   |                 |                   |                  |                 | bit (  |  |  |  |  |

| Legend:      |                                                                                                                                                                                       |                                   |                 |                   |                  |                 |        |  |  |  |  |

| R = Readab   | ole bit                                                                                                                                                                               | P = Programn                      | nable bit       | U = Unimplen      | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                                                | '1' = Bit is set                  |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |  |  |  |  |

| bit 7,5      | FWDTEN<1:0                                                                                                                                                                            | >: Watchdog Ti                    | mer Enable bi   | ts                |                  |                 |        |  |  |  |  |

|              |                                                                                                                                                                                       | enabled in hardw                  |                 |                   |                  |                 |        |  |  |  |  |