#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km101-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.1.4 EASY MIGRATION

The PIC24FV16KM204 family devices have two variants. The KM20X variant provides the full feature set of the device, while the KM10X offers a reduced peripheral set, allowing for the balance of features and cost (refer to Table 1-1). Both variants allow for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, different die variants, or even moving from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple to the powerful and complex, yet still selecting a Microchip device.

### 1.2 Other Special Features

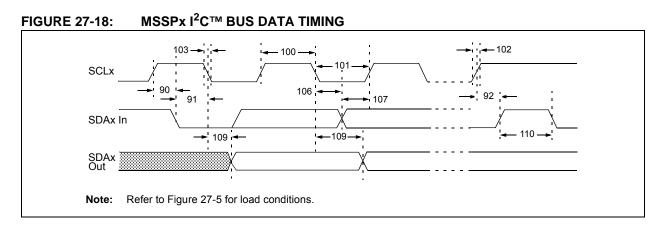

- Communications: The PIC24FV16KM204 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an MSSP module which implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24FV16KM204 family include two 8-bit Digital-to-Analog Converters which offer support in Idle mode, and left and right justified input data, as well as up to two operational amplifiers with selectable power and speed modes.

- Real-Time Clock/Calendar (RTCC): This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

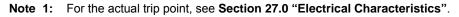

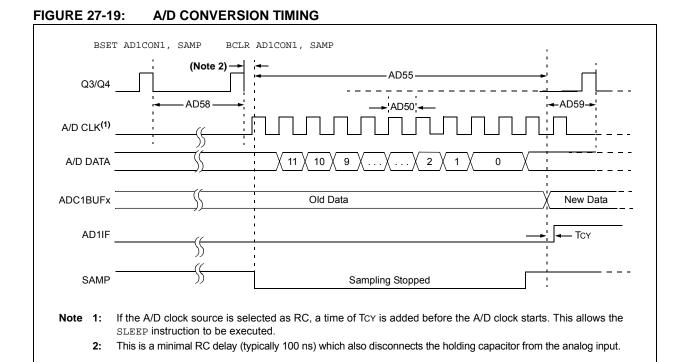

- 12-Bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep, to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24FV16KM204 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing, and also for precision time measurement and pulse generation. The CTMU can also be connected to the operational amplifiers to provide active guarding, which provides increased robustness in the presence of noise in capacitive touch applications.

### 1.3 Details on Individual Family Members

Devices in the PIC24FV16KM204 family are available in 20-pin, 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

Members of the PIC24FV16KM204 family are available as both standard and high-voltage devices. High-voltage devices, designated with an "FV" in the part number (such as PIC24FV16KM204), accommodate an operating VDD range of 2.0V to 5.5V and have an on-board voltage regulator that powers the core. Peripherals operate at VDD.

Standard devices, designated by "F" (such as PIC24F16KM204), function over a lower VDD range of 1.8V to 3.6V. These parts do not have an internal regulator, and both the core and peripherals operate directly from VDD.

The PIC24FV16KM204 family may be thought of as two different device groups, both offering slightly different sets of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The number of external analog channels available

- The number of Digital-to-Analog Converters

- · The number of operational amplifiers

- The number of analog comparators

- The presence of a Real-Time Clock and Calendar (RTCC)

- The number and type of CCP modules (i.e., MCCP vs. SCCP)

- The number of serial communication modules (both MSSPs and UARTs)

- The number of Configurable Logic Cell (CLC) modules

The general differences between the different sub-families are shown in Table 1-1 and Table 1-2.

A list of the pin features available on the PIC24FV16KM204 family devices, sorted by function, is provided in Table 1-5.

| TABLE 1-3: DEVICE FEATURES FOR                                                                                                                                                | R THE PIC24FV1                                                              |                    |                               |                         |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------|-------------------------------|-------------------------|--|--|--|--|

| Features                                                                                                                                                                      | PIC24FV16KM204                                                              | PIC24FV08KM204     | PIC24FV16KM202                | PIC24FV08KM202          |  |  |  |  |

| Operating Frequency                                                                                                                                                           |                                                                             | DC-3               | 2 MHz                         |                         |  |  |  |  |

| Program Memory (bytes)                                                                                                                                                        | 16K                                                                         | 8K                 | 16K                           | 8K                      |  |  |  |  |

| Program Memory (instructions)                                                                                                                                                 | 5632                                                                        | 2816               | 5632                          | 2816                    |  |  |  |  |

| Data Memory (bytes)                                                                                                                                                           |                                                                             | 20                 | )48                           | I                       |  |  |  |  |

| Data EEPROM Memory (bytes)                                                                                                                                                    |                                                                             | 5                  | 12                            |                         |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)                                                                                                                                    |                                                                             | 40 (               | 36/4)                         |                         |  |  |  |  |

| Voltage Range                                                                                                                                                                 |                                                                             | 2.0-               | -5.5V                         |                         |  |  |  |  |

| I/O Ports                                                                                                                                                                     | PORTA<1<br>PORTB<<br>PORTC                                                  | :15:0>             |                               | RTA<7,5:0><br>RTB<15:0> |  |  |  |  |

| Total I/O Pins                                                                                                                                                                | 37                                                                          |                    |                               | 23                      |  |  |  |  |

| Timers                                                                                                                                                                        | 11<br>(One 16-bit timer, five MCCPs/SCCPs with up to two 16/32 timers each) |                    |                               |                         |  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP                                                                                                                                   |                                                                             |                    | 3<br>2                        |                         |  |  |  |  |

| Serial Communications<br>MSSP<br>UART                                                                                                                                         |                                                                             |                    | 2<br>2                        |                         |  |  |  |  |

| Input Change Notification Interrupt                                                                                                                                           | 36                                                                          |                    |                               | 22                      |  |  |  |  |

| 12-Bit Analog-to-Digital Module<br>(input channels)                                                                                                                           | 22                                                                          |                    |                               | 19                      |  |  |  |  |

| Analog Comparators                                                                                                                                                            |                                                                             |                    | 3                             |                         |  |  |  |  |

| 8-Bit Digital-to-Analog Converters                                                                                                                                            |                                                                             |                    | 2                             |                         |  |  |  |  |

| Operational Amplifiers                                                                                                                                                        |                                                                             |                    | 2                             |                         |  |  |  |  |

| Charge Time Measurement Unit (CTMU)                                                                                                                                           |                                                                             | Y                  | íes 🛛                         |                         |  |  |  |  |

| Real-Time Clock and Calendar (RTCC)                                                                                                                                           |                                                                             | Y                  | 'es                           |                         |  |  |  |  |

| Configurable Logic Cell (CLC)                                                                                                                                                 | 2                                                                           |                    |                               |                         |  |  |  |  |

| Resets (and delays)       POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,         REPEAT Instruction, Hardware Traps, Configuration Word Mismat (PWRT, OST, PLL Lock) |                                                                             |                    |                               |                         |  |  |  |  |

| Instruction Set                                                                                                                                                               | 76 Base Inst                                                                | ructions, Multiple | e Addressing N                | Iode Variations         |  |  |  |  |

| Packages                                                                                                                                                                      | 44-Pin QFI<br>48-Pin U                                                      |                    | 28-Pin<br>SPDIP/SSOP/SOIC/QFN |                         |  |  |  |  |

#### TABLE 1-3: DEVICE FEATURES FOR THE PIC24FV16KM204 FAMILY

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |                   |                                   |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|-------------------|-----------------------------------|

|          |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |                   |                                   |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer            | Description                       |

| AN0      | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA               | A/D Analog Inputs                 |

| AN1      | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | I   | ANA               | A/D Analog Inputs                 |

| AN2      | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I   | ANA               | A/D Analog Inputs                 |

| AN3      | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | Ι   | ANA               | A/D Analog Inputs                 |

| AN4      | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I   | ANA               | A/D Analog Inputs                 |

| AN5      | _                                | 7                                | 4             | 24                     | 26             | —                                | 7                                | 4             | 24                     | 26             | I   | ANA               | A/D Analog Inputs                 |

| AN6      | _                                | —                                | —             | 25                     | 27             | —                                | —                                |               | 25                     | 27             | I   | ANA               | A/D Analog Inputs                 |

| AN7      | _                                | —                                | —             | 26                     | 28             | —                                | —                                |               | 26                     | 28             | I   | ANA               | A/D Analog Inputs                 |

| AN8      | _                                | —                                | —             | 27                     | 29             | —                                | —                                |               | 27                     | 29             | I   | ANA               | A/D Analog Inputs                 |

| AN9      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ANA               | A/D Analog Inputs                 |

| AN10     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ANA               | A/D Analog Inputs                 |

| AN11     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | -   | ANA               | A/D Analog Inputs                 |

| AN12     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | Ι   | ANA               | A/D Analog Inputs                 |

| AN13     | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | Ι   | ANA               | A/D Analog Inputs                 |

| AN14     | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | Ι   | ANA               | A/D Analog Inputs                 |

| AN15     | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | I   | ANA               | A/D Analog Inputs                 |

| AN16     | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA               | A/D Analog Inputs                 |

| AN17     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I   | ANA               | A/D Analog Inputs                 |

| AN18     | _                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | I   | ANA               | A/D Analog Inputs                 |

| AN19     | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ANA               | A/D Analog Inputs                 |

| AN20     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ANA               | A/D Analog Inputs                 |

| AN21     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ANA               | A/D Analog Inputs                 |

| ASCL1    | _                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | I/O | I <sup>2</sup> C™ | Alternate I2C1 Clock Input/Output |

| ASDA1    | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I/O | l <sup>2</sup> C  | Alternate I2C1 Data Input/Output  |

| AVDD     | 20                               | 28                               | 25            | 17                     | 18             | 20                               | 28                               | 25            | 17                     | 18             | Р   |                   | A/D Supply Pins                   |

| AVss     | 19                               | 27                               | 24            | 16                     | 17             | 19                               | 27                               | 24            | 16                     | 17             | Р   |                   | A/D Supply Pins                   |

| C1INA    | 8                                | 7                                | 4             | 24                     | 26             | 8                                | 7                                | 4             | 24                     | 26             | I   | ANA               | Comparator 1 Input A (+)          |

| C1INB    | 7                                | 6                                | 3             | 23                     | 25             | 7                                | 6                                | 3             | 23                     | 25             | I   | ANA               | Comparator 1 Input B (-)          |

| C1INC    | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I   | ANA               | Comparator 1 Input C (+)          |

| C1IND    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA               | Comparator 1 Input D (-)          |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

DS30003030B-page 20

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

| TABLE 1-5. |                                  |                                  | F             |                        |                |                                  | <u> </u>                         | FV            | ,                      |                |     |        |                             |

|------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|-----------------------------|

|            |                                  | I                                | Pin Numb      | er                     |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                             |

| Function   | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                 |

| OSCI       | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | Ι   | ANA    | Primary Oscillator Input    |

| OSCO       | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | 0   | ANA    | Primary Oscillator Output   |

| PGEC1      | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I/O | ST     | ICSP Clock 1                |

| PGED1      | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I/O | ST     | ICSP Data 1                 |

| PGEC2      | 2                                | 22                               | 19            | 9                      | 10             | 2                                | 22                               | 19            | 9                      | 10             | I/O | ST     | ICSP Clock 2                |

| PGED2      | 3                                | 21                               | 18            | 8                      | 9              | 3                                | 21                               | 18            | 8                      | 9              | I/O | ST     | ICSP Data 2                 |

| PGEC3      | 10                               | 15                               | 12            | 42                     | 46             | 10                               | 15                               | 12            | 42                     | 46             | I/O | ST     | ICSP Clock 3                |

| PGED3      | 9                                | 14                               | 11            | 41                     | 45             | 9                                | 14                               | 11            | 41                     | 45             | I/O | ST     | ICSP Data 3                 |

| PWRLCLK    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | RTCC Power Line Clock Input |

| RA0        | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I/O | ST     | PORTA Pins                  |

| RA1        | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | I/O | ST     | PORTA Pins                  |

| RA2        | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I/O | ST     | PORTA Pins                  |

| RA3        | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | I/O | ST     | PORTA Pins                  |

| RA4        | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | I/O | ST     | PORTA Pins                  |

| RA5        | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | I/O | ST     | PORTA Pins                  |

| RA6        | 14                               | 20                               | 17            | 7                      | 7              | _                                |                                  | _             | _                      | _              | I/O | ST     | PORTA Pins                  |

| RA7        | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | I/O | ST     | PORTA Pins                  |

| RA8        | —                                | —                                |               | 32                     | 35             | —                                |                                  | —             | 32                     | 35             | I/O | ST     | PORTA Pins                  |

| RA9        | —                                | —                                |               | 35                     | 38             | —                                |                                  | —             | 35                     | 38             | I/O | ST     | PORTA Pins                  |

| RA10       | _                                | _                                | _             | 12                     | 13             | _                                | _                                | —             | 12                     | 13             | I/O | ST     | PORTA Pins                  |

| RA11       | _                                | _                                | _             | 13                     | 14             | _                                | _                                | —             | 13                     | 14             | I/O | ST     | PORTA Pins                  |

| RB0        | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I/O | ST     | PORTB Pins                  |

| RB1        | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I/O | ST     | PORTB Pins                  |

| RB2        | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I/O | ST     | PORTB Pins                  |

| RB3        | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | ST     | PORTB Pins                  |

| RB4        | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | I/O | ST     | PORTB Pins                  |

| RB5        | —                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I/O | ST     | PORTB Pins                  |

| RB6        | —                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | I/O | ST     | PORTB Pins                  |

| RB7        | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I/O | ST     | PORTB Pins                  |

| RB8        | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | ST     | PORTB Pins                  |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

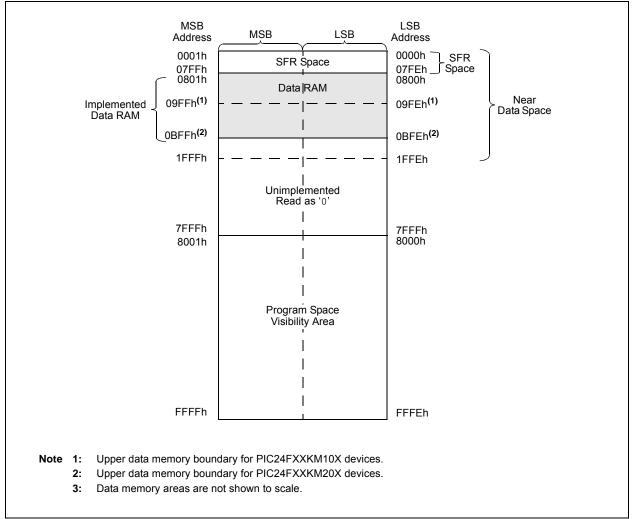

#### 4.2 **Data Address Space**

The PIC24F core has a separate, 16-bit-wide data memory space, addressable as a single linear range. The Data Space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The Data Space memory map is displayed in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This gives a Data Space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility").

Depending on the particular device, PIC24FV16KM family devices implement either 512 or 1024 words of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

FIGURE 4-3:

#### 4.2.1 DATA SPACE WIDTH

The data organized memory space is in byte-addressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all the Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

DATA SPACE MEMORY MAP FOR PIC24FXXXXX FAMILY DEVICES<sup>(3)</sup>

#### TABLE 4-12: SCCP5 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14                          | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8       | Bit 7         | Bit 6      | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|---------|---------------------------------|---------|--------|---------|---------|-----------|-------------|---------------|------------|---------|---------|---------|---------|--------|--------|---------------|

| CCP5CON1L <sup>(1)</sup> | 1D0h  | CCPON   | _                               | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0     | TMRPS1        | TMRPS0     | T32     | CCSEL   | MOD3    | MOD2    | MOD1   | MOD0   | 0000          |

| CCP5CON1H(1)             | 1D2h  | OPSSRC  | RTRGEN                          | _       | _      | IOPS3   | IOPS2   | IOPS1     | IOPS0       | TRIGEN        | ONESHOT    | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1  | SYNC0  | 0000          |

| CCP5CON2L <sup>(1)</sup> | 1D4h  | PWMRSEN | ASDGM                           | _       | SSDG   | _       | _       | _         | _           | ASDG7         | ASDG6      | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1  | ASDG0  | 0000          |

| CCP5CON2H(1)             | 1D6h  | OENSYNC | _                               | _       | _      | _       | _       | _         | OCAEN       | ICGSM1        | ICGSM0     | _       | AUXOUT1 | AUXOUT0 | ICSEL2  | ICSEL1 | ICSEL0 | 0100          |

| CCP5CON3H <sup>(1)</sup> | 1DAh  | OETRIG  | OSCNT2                          | OSCNT1  | OSCNT0 | -       | _       | _         | _           | _             | _          | POLACE  | _       | PSSACE1 | PSSACE0 | _      | _      | 0000          |

| CCP5STATL <sup>(1)</sup> | 1DCh  | -       | _                               | _       | —      | -       | _       | _         | _           | CCPTRIG       | TRSET      | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV   | ICBNE  | 0000          |

| CCP5TMRL <sup>(1)</sup>  | 1E0h  |         |                                 |         |        |         |         | SCCP5     | i Time Base | Register Lo   | w Word     |         |         |         |         |        |        | 0000          |

| CCP5TMRH <sup>(1)</sup>  | 1E2h  |         |                                 |         |        |         |         | SCCP5     | Time Base   | Register Hig  | gh Word    |         |         |         |         |        |        | 0000          |

| CCP5PRL <sup>(1)</sup>   | 1E4h  |         |                                 |         |        |         |         | SCCP5 Tir | ne Base Pe  | iod Register  | r Low Word |         |         |         |         |        |        | FFFF          |

| CCP5PRH <sup>(1)</sup>   | 1E6h  |         |                                 |         |        |         |         | SCCP5 Tin | ne Base Per | iod Register  | High Word  |         |         |         |         |        |        | FFFF          |

| CCP5RAL <sup>(1)</sup>   | 1E8h  |         |                                 |         |        |         |         | Out       | put Compar  | e 5 Data Wo   | rd A       |         |         |         |         |        |        | 0000          |

| CCP5RBL <sup>(1)</sup>   | 1ECh  |         | Output Compare 5 Data Word B 00 |         |        |         |         |           |             |               | 0000       |         |         |         |         |        |        |               |

| CCP5BUFL <sup>(1)</sup>  | 1F0h  |         |                                 |         |        |         |         | Input C   | apture 5 Da | ta Buffer Lo  | w Word     |         |         |         |         |        |        | 0000          |

| CCP5BUFH <sup>(1)</sup>  | 1F2h  |         |                                 |         |        |         |         | Input C   | apture 5 Da | ta Buffer Hig | h Word     |         |         |         |         |        |        | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### REGISTER 8-33: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0           | U-0        | U-0              | U-0          | U-0               | U-0              | U-0             | U-0      |

|---------------|------------|------------------|--------------|-------------------|------------------|-----------------|----------|

| —             | —          | —                | —            | —                 | —                | —               | —        |

| bit 15        |            |                  |              |                   |                  |                 | bit 8    |

|               |            |                  |              |                   |                  |                 |          |

| U-0           | U-0        | U-0              | U-0          | U-0               | R/W-1            | R/W-0           | R/W-0    |

| _             | _          | _                | _            | —                 | ULPWUIP2         | ULPWUIP1        | ULPWUIP0 |

| bit 7         |            |                  |              |                   |                  |                 | bit 0    |

| Legend:       |            |                  |              |                   |                  |                 |          |

| R = Readable  | e bit      | W = Writable     | bit          | U = Unimplem      | nented bit, read | l as '0'        |          |

| -n = Value at | POR        | '1' = Bit is set |              | '0' = Bit is clea | ared             | x = Bit is unkr | iown     |

|               |            |                  |              |                   |                  |                 |          |

| bit 15-3      | Unimplemer | ted: Read as '0  | )'           |                   |                  |                 |          |

| bit 2-0       | ULPWUIP<2  | :0>: Ultra Low-F | Power Wake-u | p Interrupt Prior | rity bits        |                 |          |

111 = Interrupt is Priority 7 (highest priority interrupt)

- •

- 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

### REGISTER 8-34: IPC24: INTERRUPT PRIORITY CONTROL REGISTER 24

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | CLC2IP2 | CLC2IP1 | CLC2IP0 | —   | CLC1IP2 | CLC1IP1 | CLC1IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 6-4  | CLC2IP<2:0>: CLC2 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

| bit 3    | Unimplemented: Read as '0'                                 |

| bit 2-0  | CLC1IP<2:0>: CLC1 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

|          |                                                            |

#### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC Oscillator by a fixed amount.

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                    | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/C                      | HSC = Hardware Settable/Clearable bit |                    |  |  |  |  |

|----------------------------|------------------------------------------------|---------------------------------------|--------------------|--|--|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit SO = Settable Only bit |                                       |                    |  |  |  |  |

| R = Readable bit           | W = Writable bit                               | U = Unimplemented bit, read as '0'    |                    |  |  |  |  |

| -n = Value at POR          | '1' = Bit is set                               | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| Note 1:   | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:        | This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                |

**3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REGISTER     | 9-2: CLKL                                                                                                                                                                                                                                                        | DIV: CLOCK L                                                                                                                                                                                                                                                                                                                   |                                                                                                                       | GISTER               |                  |                  |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------|

| bit 15       bit         U-0       U-0       U-0       U-0       U-0       U-0                  bit       7                                                                                                 <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0        | R/W-0                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                          | R/W-1                                                                                                                 |                      | R/W-0            | R/W-0            | R/W-1  |

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ROI          | DOZE2                                                                                                                                                                                                                                                            | DOZE1                                                                                                                                                                                                                                                                                                                          | DOZE0                                                                                                                 | DOZEN <sup>(1)</sup> | RCDIV2           | RCDIV1           | RCDIV0 |

| -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15       |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |                      |                  |                  | bit 8  |

| -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11.0         | 11.0                                                                                                                                                                                                                                                             | 11.0                                                                                                                                                                                                                                                                                                                           | 11.0                                                                                                                  | 11.0                 | 11.0             | 11.0             |        |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>11 = 1:128<br>110 = 1:52<br>100 = 1:6<br>111 = 1:128<br>100 = 1:16<br>011 = 1:32<br>100 = 1:16<br>011 = 1:32<br>100 = 1:1<br>DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE<:0> bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE<:0> bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10 -8 RCDIV-2:0>: FRC Postscaler Select bits<br>When COSC<:2:0> (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-32)<br>100 = 2 MHz (divide-by-4)<br>011 = 1 MHz (divide-by-4)<br>011 = 1.96 kHz (divide-by-4)<br>101 = 15.52 kHz (divide-by-4)<br>101 = 15.52 kHz (divide-by-26)<br>101 = 15.52 kHz (divide-by-26)<br>101 = 15.52 kHz (divide-by-26)<br>101 = 15.52 kHz (divide-by-27) - default<br>001 = 41 kLz (divide-by-28)<br>102 = 256 kHz (divide-by-29) - default<br>103 = 15.52 kHz (divide-by-24)<br>104 = 15.52 kHz (divide-by-24)<br>105 = 15.52 kHz (divide-by-24)<br>105 = 15.52 kHz (divide-by-27) - default<br>106 = 125 kHz (divide-by-27) - default<br>107 = 125 kHz (divide-by-27) - default<br>108 = 125 kHz (divide-by-27) - default<br>109 = 200 kHz (divide-by-27) - default<br>100 = 125 kHz (divide-by-27) - default<br>101 = 125 kHz (divide-by-27) - default<br>102 = 125 kHz (divide-by-27) - default<br>103 = 125 kHz (divide-by-27) - default<br>104 = 125 kHz (divide-by-27) - default<br>105 = 200 kHz (divide-by-27) - default<br>105 = 200 kHz (divide-by-27) - default<br>106 = 000 kHz (divide-by-27) - default<br>107 = 250 kHz (divide-by-27) - default<br>108 = 125 kHz (divide-by-27) - default<br>109 = 500 kHz (divide-by-27) - default<br>100 = 500 kHz (divide-by-27) - default<br>100 = 500 kH              | 0-0          | 0-0                                                                                                                                                                                                                                                              | 0-0                                                                                                                                                                                                                                                                                                                            | 0-0                                                                                                                   | 0-0                  | 0-0              | 0-0              | 0-0    |