Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                             |

| Program Memory Size        | 8KB (2.75K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 20-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km101t-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g.,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ ).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

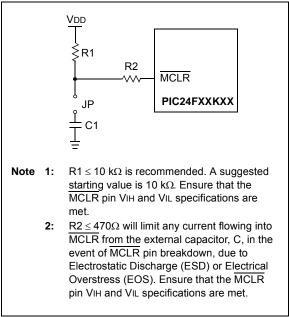

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

### TABLE 4-11: SCCP4 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8        | Bit 7         | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|---------|--------|---------|--------|---------|---------|-----------|--------------|---------------|-------------|---------|---------|---------|---------|--------|--------|---------------|

| CCP4CON1L <sup>(1)</sup> | 1ACh  | CCPON   | _      | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0      | TMRPS1        | TMRPS0      | T32     | CCSEL   | MOD3    | MOD2    | MOD1   | MOD0   | 0000          |

| CCP4CON1H(1)             | 1AEh  | OPSSRC  | RTRGEN | —       | _      | IOPS3   | IOPS2   | IOPS1     | IOPS0        | TRIGEN        | ONESHOT     | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1  | SYNC0  | 0000          |

| CCP4CON2L <sup>(1)</sup> | 1B0h  | PWMRSEN | ASDGM  | _       | SSDG   | _       | _       | _         | _            | ASDG7         | ASDG6       | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1  | ASDG0  | 0000          |

| CCP4CON2H <sup>(1)</sup> | 1B2h  | OENSYNC | _      | _       | _      | _       | _       | _         | OCAEN        | ICGSM1        | ICGSM0      | _       | AUXOUT1 | AUXOUT0 | ICSEL2  | ICSEL1 | ICSEL0 | 0100          |

| CCP4CON3H <sup>(1)</sup> | 1B6h  | OETRIG  | OSCNT2 | OSCNT1  | OSCNT0 | _       | _       | _         | —            | _             | _           | POLACE  | _       | PSSACE1 | PSSACE0 | _      | —      | 0000          |

| CCP4STATL <sup>(1)</sup> | 1B8h  | _       | _      | _       |        | -       | _       | _         | _            | CCPTRIG       | TRSET       | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV   | ICBNE  | 0000          |

| CCP4TMRL <sup>(1)</sup>  | 1BCh  |         |        |         |        |         |         | SCCP4     | 1 Time Base  | Register Lo   | ow Word     |         |         |         |         |        |        | 0000          |

| CCP4TMRH <sup>(1)</sup>  | 1BEh  |         |        |         |        |         |         | SCCP4     | Time Base    | Register Hi   | gh Word     |         |         |         |         |        |        | 0000          |

| CCP4PRL <sup>(1)</sup>   | 1C0h  |         |        |         |        |         |         | SCCP4 Tir | ne Base Pe   | riod Registe  | er Low Word |         |         |         |         |        |        | FFFF          |

| CCP4PRH <sup>(1)</sup>   | 1C2h  |         |        |         |        |         |         | SCCP4 Tir | ne Base Pe   | riod Registe  | r High Word |         |         |         |         |        |        | FFFF          |

| CCP4RAL <sup>(1)</sup>   | 1C4h  |         |        |         |        |         |         | Out       | put Compar   | e 4 Data Wo   | ord A       |         |         |         |         |        |        | 0000          |

| CCP4RBL <sup>(1)</sup>   | 1C8h  |         |        |         |        |         |         | Out       | put Compar   | e 4 Data Wo   | ord B       |         |         |         |         |        |        | 0000          |

| CCP4BUFL <sup>(1)</sup>  | 1CCh  |         |        |         |        |         |         | Input C   | Capture 4 Da | ata Buffer Lo | w Word      |         |         |         |         |        |        | 0000          |

| CCP4BUFH <sup>(1)</sup>  | 1CEh  |         |        |         |        |         |         | Input C   | apture 4 Da  | ita Buffer Hi | gh Word     |         |         |         |         |        |        | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** These registers are available only on PIC24F(V)16KM2XX devices.

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as displayed in Example 5-5.

| EXAMPLE 5-1: | ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE |

|--------------|-------------------------------------------------------|

|              |                                                       |

| ; Set up NVMCON fo | or row erase operation               |                                     |

|--------------------|--------------------------------------|-------------------------------------|

| MOV #0x            | x4058, WO ;                          |                                     |

| MOV W0,            | , NVMCON ;                           | Initialize NVMCON                   |

| ; Init pointer to  | row to be ERASED                     |                                     |

| MOV #tk            | <pre>blpage(PROG_ADDR), W0 ;</pre>   |                                     |

| MOV W0,            | , TBLPAG ;                           | Initialize PM Page Boundary SFR     |

| MOV #tk            | <pre>bloffset(PROG_ADDR), W0 ;</pre> | Initialize in-page EA[15:0] pointer |

| TBLWTL W0,         | , [WO] ;                             | Set base address of erase block     |

| DISI #5            | ;                                    | Block all interrupts                |

|                    |                                      | for next 5 instructions             |

| MOV #0×            | x55, WO                              |                                     |

| MOV W0,            | , NVMKEY ;                           | Write the 55 key                    |

| MOV #0×            | xAA, W1 ;                            |                                     |

| MOV W1,            | , NVMKEY ;                           | Write the AA key                    |

| BSET NVM           | MCON, #WR ;                          | Start the erase sequence            |

| NOP                | ;                                    | Insert two NOPs after the erase     |

| NOP                | ;                                    | command is asserted                 |

|                    |                                      |                                     |

#### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

// Variable located in Pgm Memory, declared as a

int __attribute__ ((space(auto_psv))) progAddr = 0x1234;

// global variable

unsigned int offset;

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

__builtin_tblwtl(offset, 0x0000);

// Set base address of erase block

// with dummy latch write

NVMCON = 0 \times 4058;

// Initialize NVMCON

asm("DISI #5");

// Block all interrupts for next 5 instructions

_builtin_write_NVM();

\ensuremath{{//}} C30 function to perform unlock

// sequence and set WR

```

#### REGISTER 8-19: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

|                  | R/W-1                                                                                                                                                               | R/W-0                                                                                                                                                                                     | R/W-0                                                                                        | U-0                         | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------------|---------|--|--|--|--|--|

| _                | T1IP2                                                                                                                                                               | T1IP1                                                                                                                                                                                     | T1IP0                                                                                        | _                           | CCP2IP2          | CCP2IP1         | CCP2IP0 |  |  |  |  |  |

| bit 15           |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 | bit 8   |  |  |  |  |  |

|                  |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

| U-0              | R/W-1                                                                                                                                                               | R/W-0                                                                                                                                                                                     | R/W-0                                                                                        | U-0                         | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|                  | CCP1IP2                                                                                                                                                             | CCP1IP1                                                                                                                                                                                   | CCP1IP0                                                                                      |                             | INT0IP2          | INT0IP1         | INT0IP0 |  |  |  |  |  |

| bit 7            |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 | bit C   |  |  |  |  |  |

| Legend:          |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

| R = Readab       | ole bit                                                                                                                                                             | W = Writable                                                                                                                                                                              | bit                                                                                          | U = Unimplen                | nented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a     | at POR                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                          |                                                                                              | '0' = Bit is clea           | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

| bit 15           | Unimplemen                                                                                                                                                          | ted: Read as '(                                                                                                                                                                           | )'                                                                                           |                             |                  |                 |         |  |  |  |  |  |

| bit 14-12        | -                                                                                                                                                                   | imer1 Interrupt                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

|                  |                                                                                                                                                                     | ot is Priority 7 (h                                                                                                                                                                       | -                                                                                            | interrupt)                  |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

|                  | 001 = Interrup                                                                                                                                                      | 001 = Interrupt is Priority 1                                                                                                                                                             |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

|                  |                                                                                                                                                                     | ot source is disa                                                                                                                                                                         | abled                                                                                        |                             |                  |                 |         |  |  |  |  |  |

| bit 11           | Unimplemen                                                                                                                                                          | ted: Read as '(                                                                                                                                                                           | )'                                                                                           |                             |                  |                 |         |  |  |  |  |  |

| bit 10-8         | CCP2IP<2:0>                                                                                                                                                         | Capture/Com                                                                                                                                                                               | pare 2 Event                                                                                 | Interrupt Priority          | y bits           |                 |         |  |  |  |  |  |

|                  | 111 = Interrup                                                                                                                                                      | ot is Priority 7 (h                                                                                                                                                                       | ighest priority                                                                              | interrupt)                  |                  |                 |         |  |  |  |  |  |

|                  |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

|                  | •                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

|                  | •<br>•                                                                                                                                                              |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

|                  | •<br>•<br>001 = Interrup<br>000 = Interrup                                                                                                                          | ot is Priority 1<br>ot source is disa                                                                                                                                                     | abled                                                                                        |                             |                  |                 |         |  |  |  |  |  |

| bit 7            | 000 = Interrup                                                                                                                                                      |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |  |  |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interrup<br><b>Unimplemen</b>                                                                                                                                 | ot source is disa<br>ted: Read as '(                                                                                                                                                      | )'                                                                                           | Interrupt Priority          | y bits           |                 |         |  |  |  |  |  |

|                  | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0>                                                                                                                         | ot source is disa<br>ted: Read as '(                                                                                                                                                      | )'<br>ipare 1 Event                                                                          |                             | y bits           |                 |         |  |  |  |  |  |

|                  | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0>                                                                                                                         | ot source is disa<br>t <b>ed:</b> Read as '(<br>>: Capture/Com                                                                                                                            | )'<br>ipare 1 Event                                                                          |                             | y bits           |                 |         |  |  |  |  |  |

|                  | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0>                                                                                                                         | ot source is disa<br>t <b>ed:</b> Read as '(<br>>: Capture/Com                                                                                                                            | )'<br>ipare 1 Event                                                                          |                             | y bits           |                 |         |  |  |  |  |  |

|                  | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0>                                                                                                                         | ot source is disa<br>ted: Read as '(<br>>: Capture/Com<br>ot is Priority 7 (h                                                                                                             | )'<br>ipare 1 Event                                                                          |                             | y bits           |                 |         |  |  |  |  |  |

|                  | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>•<br>001 = Interrup                                                                      | ot source is disa<br>ted: Read as '(<br>>: Capture/Com<br>ot is Priority 7 (h                                                                                                             | ) <sup>,</sup><br>Ipare 1 Event<br>Iighest priority                                          |                             | y bits           |                 |         |  |  |  |  |  |

|                  | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup                                                         | ot source is disa<br>ted: Read as '(<br>>: Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1                                                                                         | <sub>)'</sub><br>npare 1 Event<br>nighest priority<br>abled                                  |                             | y bits           |                 |         |  |  |  |  |  |

| bit 6-4          | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>                            | ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1<br>ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> External Interr | )'<br>Ipare 1 Event<br>Iighest priority<br>abled<br>)'<br>upt 0 Interrupt                    | interrupt)<br>Priority bits | y bits           |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>                            | ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> Capture/Comot<br>ot is Priority 7 (h<br>ot is Priority 1<br>ot source is disa<br><b>ted:</b> Read as '(                           | )'<br>Ipare 1 Event<br>Iighest priority<br>abled<br>)'<br>upt 0 Interrupt                    | interrupt)<br>Priority bits | y bits           |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>                            | ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1<br>ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> External Interr | )'<br>Ipare 1 Event<br>Iighest priority<br>abled<br>)'<br>upt 0 Interrupt                    | interrupt)<br>Priority bits | y bits           |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>                            | ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1<br>ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> External Interr | )'<br>Ipare 1 Event<br>Iighest priority<br>abled<br>)'<br>upt 0 Interrupt                    | interrupt)<br>Priority bits | y bits           |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>:<br>111 = Interrup<br>001 = Interrup | ot source is disa<br>ted: Read as '(<br>: Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1<br>tot source is disa<br>ted: Read as '(<br>: External Interr<br>pt is Priority 7 (      | )'<br>ipare 1 Event<br>ighest priority<br>abled<br>)'<br>upt 0 Interrupt<br>highest priority | interrupt)<br>Priority bits | y bits           |                 |         |  |  |  |  |  |

### REGISTER 8-27: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | CCT5IP2 | CCT5IP1 | CCT5IP0 |     | _   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

| Legend:          |            |                                 |                              |                    |

|------------------|------------|---------------------------------|------------------------------|--------------------|

| R = Readable bit |            | W = Writable bit                | U = Unimplemented bit        | , read as '0'      |

| -n = Value       | at POR     | '1' = Bit is set                | '0' = Bit is cleared         | x = Bit is unknown |

|                  |            |                                 |                              |                    |

| bit 15-7         | Unimpler   | mented: Read as '0'             |                              |                    |

| bit 6-4          | CCT5IP<    | 2:0>: Capture/Compare 5 Ti      | imer Interrupt Priority bits |                    |

|                  | 111 = Inte | errupt is Priority 7 (highest p | riority interrupt)           |                    |

|                  | •          |                                 |                              |                    |

|                  | •          |                                 |                              |                    |

|                  | •          |                                 |                              |                    |

|                  | 001 = Inte | errupt is Priority 1            |                              |                    |

- 000 = Interrupt source is disabled

- bit 3-0 Unimplemented: Read as '0'

### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC Oscillator by a fixed amount.

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                    | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit |                        |                    |  |  |

|----------------------------|---------------------------------------|------------------------|--------------------|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit               | SO = Settable Only bit |                    |  |  |

| R = Readable bit           | W = Writable bit                      | U = Unimplemented bit  | , read as '0'      |  |  |

| -n = Value at POR          | '1' = Bit is set                      | '0' = Bit is cleared   | x = Bit is unknown |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| Note 1:   | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:        | This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                |

**3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

## 13.4 Input Capture Mode

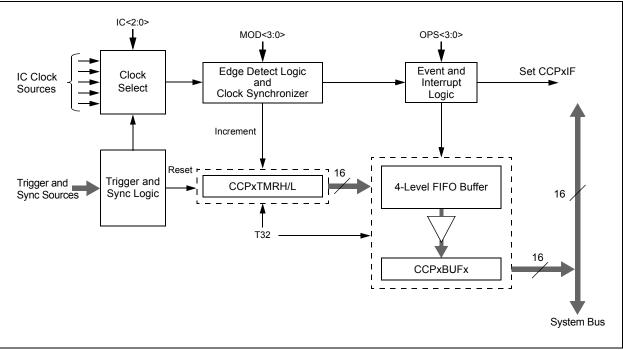

Input Capture mode is used to capture a timer value from an independent timer base upon an event on an input pin or other internal Trigger source. The input capture features are useful in applications requiring frequency (time period) and pulse measurement. Figure 13-6 depicts a simplified block diagram of Input Capture mode. Input Capture mode uses a dedicated 16/32-bit, synchronous, up counting timer for the capture function. The timer value is written to the FIFO when a capture event occurs. The internal value may be read (with a synchronization delay) using the CCPxTMRH/L register.

To use Input Capture mode, the CCSEL bit (CCPxCON1L<4>) must be set. The T32 and the MOD<3:0> bits are used to select the proper Capture mode, as shown in Table 13-4.

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                     |

|------------------------------|-----------------------|------------------------------------|

| 0000                         | 0                     | Edge Detect (16-bit capture)       |

| 0000                         | 1                     | Edge Detect (32-bit capture)       |

| 0001                         | 0                     | Every Rising (16-bit capture)      |

| 0001                         | 1                     | Every Rising (32-bit capture)      |

| 0010                         | 0                     | Every Falling (16-bit capture)     |

| 0010                         | 1                     | Every Falling (32-bit capture)     |

| 0011                         | 0                     | Every Rise/Fall (16-bit capture)   |

| 0011                         | 1                     | Every Rise/Fall (32-bit capture)   |

| 0100                         | 0                     | Every 4th Rising (16-bit capture)  |

| 0100                         | 1                     | Every 4th Rising (32-bit capture)  |

| 0101                         | 0                     | Every 16th Rising (16-bit capture) |

| 0101                         | 1                     | Every 16th Rising (32-bit capture) |

#### TABLE 13-4: INPUT CAPTURE MODES

## REGISTER 14-3: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0                | R/W-0                    | R/W-0 | R/W-0                | R/W-0                | R/W-0                                     | R/W-0 |  |

|-------|----------------------|--------------------------|-------|----------------------|----------------------|-------------------------------------------|-------|--|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> CKP |       | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> SSPM0 <sup>(3)</sup> |       |  |

| bit 7 |                      |                          |       |                      |                      |                                           | bit 0 |  |

| Legend:           |                   |                                 |                                                                                   |                                                |

|-------------------|-------------------|---------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------|

| R = Read          | able bit          | W = Writable bit                | U = Unimplemented bit                                                             | , read as '0'                                  |

| -n = Value at POR |                   | '1' = Bit is set                | '0' = Bit is cleared                                                              | x = Bit is unknown                             |

|                   |                   |                                 |                                                                                   |                                                |

| bit 15-8          | Unimple           | mented: Read as '0'             |                                                                                   |                                                |

| bit 7             | WCOL: \           | Vrite Collision Detect bit      |                                                                                   |                                                |

|                   |                   | •                               | while it is still transmitting the                                                | previous word (must be cleared in              |

|                   | softw<br>0 = No c | ,                               |                                                                                   |                                                |

| bit 6             |                   |                                 | Port Receive Overflow Indicate                                                    | or bit(1)                                      |

| bit 0             | SPI Slav          |                                 |                                                                                   |                                                |

|                   |                   |                                 | SPxBUF register is still holding                                                  | g the previous data. In case of over-          |

|                   |                   |                                 |                                                                                   | ave mode. The user must read the               |

|                   | 0 = No c          |                                 | g data, to avoid setting overflo                                                  | w (must be cleared in software).               |

| bit 5             |                   | Master Synchronous Serial F     | Port Enable bit(2)                                                                |                                                |

| DIL 5             |                   | •                               | ures SCKx, SDOx, SDIx and                                                         | SSx as serial nort nins                        |

|                   |                   |                                 | jures these pins as I/O port pi                                                   | · ·                                            |

| bit 4             | CKP: Clo          | ock Polarity Select bit         |                                                                                   |                                                |

|                   | 1 = Idle s        | state for clock is a high level |                                                                                   |                                                |

|                   |                   | state for clock is a low level  |                                                                                   |                                                |

| bit 3-0           | SSPM<3            | :0>: Master Synchronous Se      | rial Port Mode Select bits <sup>(3)</sup>                                         |                                                |

|                   |                   | SPI Master mode, Clock = Fo     |                                                                                   |                                                |

|                   |                   |                                 | x pin; <u>SSx</u> pin control is disabl<br>(x pin; <u>SSx</u> pin control is enab | ed, $\overline{SSx}$ can be used as an I/O pin |

|                   |                   | SPI Master mode, Clock = TM     |                                                                                   |                                                |

|                   |                   | SPI Master mode, Clock = Fo     | •                                                                                 |                                                |

|                   |                   | PI Master mode, Clock = Fo      |                                                                                   |                                                |

|                   | 0000 = 5          | SPI Master mode, Clock = Fo     | SC/2                                                                              |                                                |

| Note 1:           | In Master mo      | de, the overflow bit is not set | t since each new reception (a                                                     | nd transmission) is initiated by               |

|                   | writing to the    | SSPxBUF register.               |                                                                                   |                                                |

- 2: When enabled, these pins must be properly configured as inputs or outputs.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

#### 16.2.6 ALRMVAL REGISTER MAPPINGS

## REGISTER 16-8: ALMTHDY: ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0          | U-0 | U-0       | R/W-x   | R/W-x            | R/W-x            | R/W-x   | R/W-x            |  |  |  |  |

|--------------|-----|-----------|---------|------------------|------------------|---------|------------------|--|--|--|--|

| —            | —   | — MTHTEN0 |         | MTHONE3          | MTHONE2          | MTHONE1 | MTHONE0          |  |  |  |  |

| bit 15 bit 8 |     |           |         |                  |                  |         |                  |  |  |  |  |

|              |     |           |         |                  |                  |         |                  |  |  |  |  |

| 11.0         |     | D/1/      |         | R/W-x R/W-x      |                  |         |                  |  |  |  |  |

| U-0          | U-0 | R/W-x     | R/W-x   | R/W-X            | R/W-X            | R/W-x   | R/W-x            |  |  |  |  |

| <u> </u>     |     | DAYTEN1   | DAYTEN0 | R/W-X<br>DAYONE3 | R/W-X<br>DAYONE2 | DAYONE1 | R/W-x<br>DAYONE0 |  |  |  |  |

#### Legend:

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13<br>bit 12 | <b>Unimplemented:</b> Read as '0'<br><b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit<br>Contains a value of '0' or '1'. |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8            | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits<br>Contains a value from 0 to 9.                                          |

| bit 7-6             | Unimplemented: Read as '0'                                                                                                                   |

| bit 5-4             | <b>DAYTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Day's Tens Digit bits<br>Contains a value from 0 to 3.                               |

| bit 3-0             | <b>DAYONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Day's Ones Digit bits<br>Contains a value from 0 to 9.                               |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## REGISTER 16-9: ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0          | U-0 | U-0    | U-0 U-0 |        | R/W-x  | R/W-x  | R/W-x  |  |  |  |  |

|--------------|-----|--------|---------|--------|--------|--------|--------|--|--|--|--|

| —            | —   | —      | —       | —      | WDAY2  | WDAY1  | WDAY0  |  |  |  |  |

| bit 15 bit 8 |     |        |         |        |        |        |        |  |  |  |  |

|              |     |        |         |        |        |        |        |  |  |  |  |

| U-0          | U-0 | R/W-x  | R/W-x   | R/W-x  | R/W-x  | R/W-x  | R/W-x  |  |  |  |  |

| —            | —   | HRTEN1 | HRTEN0  | HRONE3 | HRONE2 | HRONE1 | HRONE0 |  |  |  |  |

| bit 7        |     |        |         |        |        |        | bit 0  |  |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits<br>Contains a value from 0 to 6. |

|           |                                                                                              |

| bit 7-6   | Unimplemented: Read as '0'                                                                   |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits                             |

|           | Contains a value from 0 to 2.                                                                |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits                             |

|           | Contains a value from 0 to 9.                                                                |

|           |                                                                                              |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## REGISTER 17-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER (CONTINUED)

| bit 3 | G1D2T: Gate 1 Data Source 2 True Enable bit                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = The Data Source 2 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 2 inverted signal is disabled for Gate 1</li> </ul> |

| bit 2 | G1D2N: Gate 1 Data Source 2 Negated Enable bit                                                                                                        |

|       | <ul> <li>1 = The Data Source 2 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 2 inverted signal is disabled for Gate 1</li> </ul> |

| bit 1 | G1D1T: Gate 1 Data Source 1 True Enable bit                                                                                                           |

|       | <ul> <li>1 = The Data Source 1 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 1 inverted signal is disabled for Gate 1</li> </ul> |

| bit 0 | G1D1N: Gate 1 Data Source 1 Negated Enable bit                                                                                                        |

|       | <ul> <li>1 = The Data Source 1 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 1 inverted signal is disabled for Gate 1</li> </ul> |

## 19.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR)

Conversion

- Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (internal and external)

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H)

Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU, and a configurable results buffer. There is a legacy 10-bit mode on this A/D to allow the option to run with lower resolution in order to obtain higher throughput. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 19-1.

### **19.4 Buffer Data Formats**

The A/D conversions are fully differential 12-bit values when MODE12 = 1 (AD1CON1<10>) and 10-bit values when MODE12 = 0. When absolute fractional or absolute integer formats are used, the results are 12 or 10 bits wide, respectively. When signed decimal formatting is used, the conversion also includes a Sign bit, making 12-bit conversions 13 bits wide and 10-bit conversions 11 bits wide. The signed decimal format yields 12-bit and 10-bit values, respectively. The Sign bit (bit 12 or bit 10) is sign-extended to fill the buffer. The FORM<1:0> bits (AD1CON1<9:8>) select the format. Figure 19-4 and Figure 19-5 show the data output formats that can be selected. Table 19-1 through Table 19-4 show the numerical equivalents for the various conversion result codes.

### FIGURE 19-4: A/D OUTPUT DATA FORMATS (12-BIT)

| RAM Contents:            |     |     |     |     | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Read to Bus:             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Integer                  | 0   | 0   | 0   | 0   | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     | r   |     |     |     |     |     |     |     |     |     | r   | 1   |

| Signed Integer           | s0  | s0  | s0  | s0  | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Fractional (1.15)        | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional (1.15) | s0  | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   |

## TABLE 19-1:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>12-BIT INTEGER FORMATS

| VIN/VREF   | 12-Bit Differential<br>Output Code<br>(13-bit result) | 16-Bit Integer Format/<br>Equivalent Decimal Value | 16-Bit Signed Integer Format/<br>Equivalent Decimal Value |                     |       |  |  |  |  |  |

|------------|-------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|---------------------|-------|--|--|--|--|--|

| +4095/4096 | 0 1111 1111 1111                                      | 0000 1111 1111 1111                                | +4095                                                     | 0000 1111 1111 1111 | +4095 |  |  |  |  |  |

| +4094/4096 | 0 1111 1111 1110                                      | 0000 1111 1111 1110                                | +4094                                                     | 0000 1111 1111 1110 | +4094 |  |  |  |  |  |

| • • •      |                                                       |                                                    |                                                           |                     |       |  |  |  |  |  |

| +1/4096    | 0 1000 0000 0001                                      | 0000 0000 0000 0001                                | +1                                                        | 0000 0000 0000 0001 | +1    |  |  |  |  |  |

| 0/4096     | 0 0000 0000 0000                                      | 0000 0000 0000 0000                                | 0                                                         | 0000 0000 0000 0000 | 0     |  |  |  |  |  |

| -1/4096    | 1 0111 1111 1111                                      | 0000 0000 0000 0000                                | 0                                                         | 1111 1111 1111 1111 | -1    |  |  |  |  |  |

| •••        |                                                       |                                                    |                                                           |                     |       |  |  |  |  |  |

| -4095/4096 | 1 0000 0000 0001                                      | 0000 0000 0000 0000                                | 0                                                         | 1111 0000 0000 0001 | -4095 |  |  |  |  |  |

| -4096/4096 | 1 0000 0000 0000                                      | 0000 0000 0000 0000                                | 0                                                         | 1111 0000 0000 0000 | -4096 |  |  |  |  |  |

| R/W-0             | U-0                                                                                                                                                                                                        | R/W-0                                               | R/W-0    | R/W-0                                 | U-0      | R/W-0   | R/W-0   |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------|---------------------------------------|----------|---------|---------|--|--|--|--|

| DACEN             |                                                                                                                                                                                                            | DACSIDL                                             | DACSLP   | DACFM                                 |          | SRDIS   | DACTRIG |  |  |  |  |

| bit 15            |                                                                                                                                                                                                            |                                                     | 27.002   |                                       |          | 0.12.0  | bit 8   |  |  |  |  |

| R/W-0             | R/W-0                                                                                                                                                                                                      | R/W-0                                               | R/W-0    | R/W-0                                 | R/W-0    | R/W-0   | R/W-0   |  |  |  |  |

| DACOE             | DACTSEL4                                                                                                                                                                                                   | DACTSEL3                                            | DACTSEL2 | DACTSEL1                              | DACTSEL0 | DACREF1 | DACREF0 |  |  |  |  |

| bit 7             |                                                                                                                                                                                                            |                                                     |          |                                       |          |         | bit 0   |  |  |  |  |

| Legend:           |                                                                                                                                                                                                            |                                                     |          |                                       |          |         |         |  |  |  |  |

| R = Readab        | le bit                                                                                                                                                                                                     | W = Writable bit U = Unimplemented bit, read as '0' |          |                                       |          |         |         |  |  |  |  |

| -n = Value at POR |                                                                                                                                                                                                            | '1' = Bit is set                                    |          | 0' = Bit is cleared x = Bit is unknow |          |         | nown    |  |  |  |  |

|                   |                                                                                                                                                                                                            |                                                     |          |                                       |          |         | -       |  |  |  |  |

| bit 15            | DACEN: DAC                                                                                                                                                                                                 | x Enable bit                                        |          |                                       |          |         |         |  |  |  |  |

|                   | 1 = Module is enabled                                                                                                                                                                                      |                                                     |          |                                       |          |         |         |  |  |  |  |

|                   | 0 = Module is disabled                                                                                                                                                                                     |                                                     |          |                                       |          |         |         |  |  |  |  |

| bit 14            | Unimplemented: Read as '0'                                                                                                                                                                                 |                                                     |          |                                       |          |         |         |  |  |  |  |

| bit 13            | DACSIDL: DACx Stop in Idle Mode bit                                                                                                                                                                        |                                                     |          |                                       |          |         |         |  |  |  |  |

|                   | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                    |                                                     |          |                                       |          |         |         |  |  |  |  |

| bit 12            | DACSLP: DACx Enable Peripheral During Sleep bit                                                                                                                                                            |                                                     |          |                                       |          |         |         |  |  |  |  |

|                   | <ul> <li>1 = DACx continues to output the most recent value of DACxDAT during Sleep mode</li> <li>0 = DACx is powered down in Sleep mode; DACxOUT pin is controlled by the TRISx and LATx bits</li> </ul>  |                                                     |          |                                       |          |         |         |  |  |  |  |

| bit 11            | DACFM: DACx Data Format Select bit                                                                                                                                                                         |                                                     |          |                                       |          |         |         |  |  |  |  |

|                   | <ul> <li>1 = Data is left justified (data stored in DACxDAT&lt;15:8&gt;)</li> <li>0 = Data is right justified (data stored in DACxDAT&lt;7:0&gt;)</li> </ul>                                               |                                                     |          |                                       |          |         |         |  |  |  |  |

| bit 10            | Unimplemented: Read as '0'                                                                                                                                                                                 |                                                     |          |                                       |          |         |         |  |  |  |  |

| bit 9             | SRDIS: Soft Reset Disable bit                                                                                                                                                                              |                                                     |          |                                       |          |         |         |  |  |  |  |

|                   | <ul> <li>1 = DACxCON and DACxDAT SFRs reset only on a POR or BOR Reset</li> <li>0 = DACxCON and DACxDAT SFRs reset on any type of device Reset</li> </ul>                                                  |                                                     |          |                                       |          |         |         |  |  |  |  |

| bit 8             | DACTRIG: DACx Trigger Input Enable bit                                                                                                                                                                     |                                                     |          |                                       |          |         |         |  |  |  |  |