Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km102-e-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                            |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  | I                                | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| CN13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I   | ST     | Interrupt-on-Change Inputs |

| CN14     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | Interrupt-on-Change Inputs |

| CN15     | —                                | 22                               | 19            | 9                      | 10             | —                                | 22                               | 19            | 9                      | 10             | I   | ST     | Interrupt-on-Change Inputs |

| CN16     | _                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I   | ST     | Interrupt-on-Change Inputs |

| CN17     | —                                | —                                |               | 3                      | 3              | —                                |                                  | —             | 3                      | 3              | I   | ST     | Interrupt-on-Change Inputs |

| CN18     | —                                | —                                |               | 2                      | 2              | —                                |                                  | —             | 2                      | 2              | I   | ST     | Interrupt-on-Change Inputs |

| CN19     | —                                | —                                |               | 5                      | 5              | —                                |                                  | —             | 5                      | 5              | I   | ST     | Interrupt-on-Change Inputs |

| CN20     | —                                | —                                |               | 4                      | 4              | —                                |                                  | —             | 4                      | 4              | I   | ST     | Interrupt-on-Change Inputs |

| CN21     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | Interrupt-on-Change Inputs |

| CN22     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ST     | Interrupt-on-Change Inputs |

| CN23     | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs |

| CN24     | —                                | 15                               | 12            | 42                     | 46             | —                                | 15                               | 12            | 42                     | 46             | I   | ST     | Interrupt-on-Change Inputs |

| CN25     | _                                | _                                |               | 37                     | 40             | _                                |                                  | _             | 37                     | 40             | I   | ST     | Interrupt-on-Change Inputs |

| CN26     | _                                | _                                |               | 38                     | 41             | _                                |                                  | _             | 38                     | 41             | I   | ST     | Interrupt-on-Change Inputs |

| CN27     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I   | ST     | Interrupt-on-Change Inputs |

| CN28     | —                                | —                                |               | 36                     | 39             | —                                |                                  | —             | 36                     | 39             | I   | ST     | Interrupt-on-Change Inputs |

| CN29     | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | I   | ST     | Interrupt-on-Change Inputs |

| CN30     | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I   | ST     | Interrupt-on-Change Inputs |

| CN31     | —                                | —                                |               | 26                     | 28             | —                                |                                  | —             | 26                     | 28             | I   | ST     | Interrupt-on-Change Inputs |

| CN32     | —                                | —                                |               | 25                     | 27             | —                                |                                  | —             | 25                     | 27             | I   | ST     | Interrupt-on-Change Inputs |

| CN33     | —                                | —                                |               | 32                     | 35             | —                                |                                  | —             | 32                     | 35             | I   | ST     | Interrupt-on-Change Inputs |

| CN34     | _                                | _                                | _             | 35                     | 38             | _                                |                                  | _             | 35                     | 38             | I   | ST     | Interrupt-on-Change Inputs |

| CN35     | _                                | _                                | _             | 12                     | 13             | _                                |                                  | _             | 12                     | 13             | I   | ST     | Interrupt-on-Change Inputs |

| CN36     | _                                | _                                | _             | 13                     | 14             | _                                |                                  | _             | 13                     | 14             | I   | ST     | Interrupt-on-Change Inputs |

| CTCMP    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input      |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

# TABLE 4-13: MSSP1 (I<sup>2</sup>C<sup>™</sup>/SPI) REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                                                                                                    | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-------|-------|-------|-------|---------------|

| SSP1BUF   | 200h  | —      | _      | _      | —      | —      | —      | _     | —     | MSSP1 Receive Buffer/Transmit Register                                                                                   |         |       |       |       |       | 00xx  |       |               |

| SSP1CON1  | 202h  | _      | _      | _      | _      | _      | _      | _     | _     | WCOL                                                                                                                     | SSPOV   | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | 0000          |

| SSP1CON2  | 204h  | _      | _      | _      | _      | _      | _      | _     | _     | GCEN                                                                                                                     | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 0000          |

| SSP1CON3  | 206h  | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM                                                                                                                   | PCIE    | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  | 0000          |

| SSP1STAT  | 208h  | _      | _      | _      | _      | _      | _      | —     | _     | SMP                                                                                                                      | CKE     | D/A   | Р     | S     | R/W   | UA    | BF    | 0000          |

| SSP1ADD   | 20Ah  | —      | _      | _      | —      | _      | —      |       |       | MSSP1 Address Register in I <sup>2</sup> C Slave Mode<br>MSSP1 Baud Rate Reload Register in I <sup>2</sup> C Master Mode |         |       |       |       | 0000  |       |       |               |

| SSP1MSK   | 20Ch  | _      | _      | _      | _      | _      | _      |       | _     | MSK7                                                                                                                     | MSK6    | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  | OOFF          |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

# TABLE 4-14: MSSP2 (I<sup>2</sup>C<sup>™</sup>/SPI) REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                                                                                                    | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-------|-------|-------|-------|---------------|

| SSP2BUF <sup>(1)</sup>  | 210h  | —      | _      | —      | —      |        | _      |       | _     | MSSP2 Receive Buffer/Transmit Register                                                                                   |         |       |       |       | 00xx  |       |       |               |

| SSP2CON1 <sup>(1)</sup> | 212h  | _      | _      | _      | _      | _      | _      | _     | _     | WCOL                                                                                                                     | SSPOV   | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | 0000          |

| SSP2CON2 <sup>(1)</sup> | 214h  | _      | _      | _      | _      | _      | _      | _     | _     | GCEN                                                                                                                     | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 0000          |

| SSP2CON3 <sup>(1)</sup> | 216h  | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM                                                                                                                   | PCIE    | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  | 0000          |

| SSP2STAT <sup>(1)</sup> | 218h  | _      | _      | _      | _      | _      | _      | _     | _     | SMP                                                                                                                      | CKE     | D/A   | Р     | S     | R/W   | UA    | BF    | 0000          |

| SSP2ADD <sup>(1)</sup>  | 21Ah  | —      | _      | —      | —      | _      | —      | _     | _     | MSSP2 Address Register in I <sup>2</sup> C Slave Mode<br>MSSP2 Baud Rate Reload Register in I <sup>2</sup> C Master Mode |         |       |       | 0000  |       |       |       |               |

| SSP2MSK <sup>(1)</sup>  | 21Ch  | —      | _      | _      | _      |        | _      | _     | _     | MSK7                                                                                                                     | MSK6    | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  | 00FF          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| ; | Set up NVMCO  | N for row programming operation | ns  |                                       |

|---|---------------|---------------------------------|-----|---------------------------------------|

|   | MOV           | #0x4004, W0                     | ;   |                                       |

|   | MOV           | W0, NVMCON                      | ;   | Initialize NVMCON                     |

| ; | Set up a poir | nter to the first program memor | ry  | location to be written                |

| ; | program memo: | ry selected, and writes enabled | b   |                                       |

|   | MOV           | #0x0000, W0                     | ;   |                                       |

|   | MOV           | W0, TBLPAG                      | ;   | Initialize PM Page Boundary SFR       |

|   | MOV           | #0x1500, W0                     | ;   | An example program memory address     |

| ; | Perform the   | TBLWT instructions to write the | e . | latches                               |

| ; | 0th_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_0, W2                 | ;   |                                       |

|   | MOV           | <pre>#HIGH_BYTE_0, W3</pre>     | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | lst_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_1, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_1, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

| ; | 2nd_program_  | word                            |     |                                       |

|   | MOV           | #LOW_WORD_2, W2                 | ;   |                                       |

|   | MOV           | #HIGH_BYTE_2, W3                | ;   |                                       |

|   | TBLWTL        | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                      | ;   | Write PM high byte into program latch |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

|   | •             |                                 |     |                                       |

| ; | 32nd_program  | —                               |     |                                       |

|   |               | #LOW_WORD_31, W2                | ;   |                                       |

|   |               | #HIGH_BYTE_31, W3               | ;   |                                       |

|   |               | W2, [W0]                        |     | Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0]                        | ;   | Write PM high byte into program latch |

| 1 |               |                                 |     |                                       |

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234 // Variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

// Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

// Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

// Write to address low word

__builtin_tblwtl(offset, progData[i++]);

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

## 8.3 Interrupt Control and Status Registers

The PIC24FV16KM204 family of devices implements a total of 33 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS6

- · IEC0 through IEC6

- IPC0 through IPC7, IPC10, IPC12, IPC15, IPC16, IPC18 through IPC20 and IPC24

- INTTREG

Global Interrupt Enable (GIE) control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIVT.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

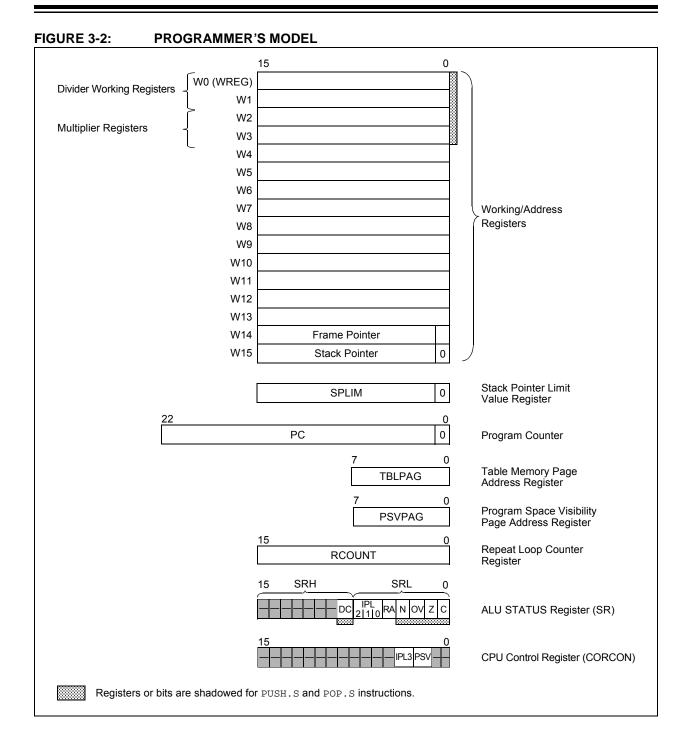

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU Interrupt Priority Level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All Interrupt registers are described in Register 8-1 through Register 8-35, in the following sections.

|                       | R/W-1                                                                                     | R/W-0                                                                                                                                          | R/W-0                                                                 | U-0                                         | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------|------------------|-----------------|---------|--|--|--|

| —                     | U2TXIP2                                                                                   | U2TXIP1                                                                                                                                        | U2TXIP0                                                               |                                             | U2RXIP2          | U2RXIP1         | U2RXIP0 |  |  |  |

| bit 15                |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 | bit     |  |  |  |

| U-0                   | R/W-1                                                                                     | R/W-0                                                                                                                                          | R/W-0                                                                 | U-0                                         | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|                       | INT2IP2                                                                                   | INT2IP1                                                                                                                                        | INT2IP0                                                               | _                                           | CCT4IP2          | CCT4IP1         | CCT4IP0 |  |  |  |

| bit 7                 |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 | bit     |  |  |  |

|                       |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |

| Legend:<br>R = Readat | ole hit                                                                                   | W = Writable                                                                                                                                   | hit                                                                   | II = Unimple                                | mented bit, read | 1 as '0'        |         |  |  |  |

| -n = Value a          |                                                                                           | '1' = Bit is set                                                                                                                               |                                                                       | '0' = Bit is cle                            |                  | x = Bit is unkr | iown    |  |  |  |

|                       |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |

| bit 15                | Unimplemen                                                                                | ted: Read as 'o                                                                                                                                | )'                                                                    |                                             |                  |                 |         |  |  |  |

| bit 14-12             |                                                                                           | : UART2 Trans                                                                                                                                  |                                                                       |                                             |                  |                 |         |  |  |  |

|                       | 111 = Interru                                                                             | pt is Priority 7(                                                                                                                              | highest priority                                                      | interrupt)                                  |                  |                 |         |  |  |  |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |

|                       | 001 = Interru                                                                             | pt is Priority 1<br>pt source is dis                                                                                                           | abled                                                                 |                                             |                  |                 |         |  |  |  |

| bit 11                | Unimplemented: Read as '0'                                                                |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |

| bit 10-8              | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits                                       |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |

|                       |                                                                                           | pt is Priority 7 (                                                                                                                             |                                                                       |                                             |                  |                 |         |  |  |  |

|                       | •                                                                                         | · · · ·                                                                                                                                        | • • •                                                                 |                                             |                  |                 |         |  |  |  |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |

|                       | 001 = Interru                                                                             | pt is Priority 1                                                                                                                               |                                                                       |                                             |                  |                 |         |  |  |  |

|                       | 000 = Interru                                                                             | pt source is dis                                                                                                                               | abled                                                                 |                                             |                  |                 |         |  |  |  |

| bit 7                 | Unimplemen                                                                                | ted: Read as 'o                                                                                                                                |                                                                       |                                             |                  |                 |         |  |  |  |

|                       |                                                                                           |                                                                                                                                                | )'                                                                    |                                             |                  |                 |         |  |  |  |

| bit 6-4               |                                                                                           | External Interr                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |  |  |  |

|                       | 111 = Interru                                                                             |                                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |  |  |  |

|                       |                                                                                           | External Interr                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |  |  |  |

|                       | 111 = Interru<br>•<br>•                                                                   | External Interr<br>pt is Priority 7(                                                                                                           | upt 2 Priority b                                                      |                                             |                  |                 |         |  |  |  |

|                       | 111 = Interru<br>•<br>•<br>001 = Interru                                                  | External Interr<br>pt is Priority 7(<br>pt is Priority 1                                                                                       | upt 2 Priority t<br>highest priority                                  |                                             |                  |                 |         |  |  |  |

| bit 6-4               | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru                                 | External Interr<br>pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                                                                   | upt 2 Priority b<br>highest priority<br>abled                         |                                             |                  |                 |         |  |  |  |

| bit 6-4<br>bit 3      | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                   | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                        | upt 2 Priority b<br>highest priority<br>abled<br>)'                   | v interrupt)                                | av hits          |                 |         |  |  |  |

|                       | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>-: Capture/Com                      | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |  |  |  |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                        | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |  |  |  |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>-: Capture/Com                      | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |  |  |  |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Capture/Com<br>pt is Priority 7 ( | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | ty bits          |                 |         |  |  |  |

## REGISTER 8-26: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

## REGISTER 10-1: ULPWCON: ULPWU CONTROL REGISTER

| R/W-0                                                                      | U-0                        | R/W-0            | U-0              | U-0 | U-0       | U-0 | R/W-0   |  |  |  |

|----------------------------------------------------------------------------|----------------------------|------------------|------------------|-----|-----------|-----|---------|--|--|--|

| ULPEN                                                                      |                            | ULPSIDL          | _                | —   | _         | _   | ULPSINK |  |  |  |

| bit 15                                                                     |                            |                  |                  |     |           |     | bit 8   |  |  |  |

|                                                                            |                            |                  |                  |     |           |     |         |  |  |  |

| U-0                                                                        | U-0                        | U-0              | U-0              | U-0 | U-0       | U-0 | U-0     |  |  |  |

| _                                                                          | _                          | —                |                  | —   | _         | _   | —       |  |  |  |

| bit 7                                                                      | ·                          | · · ·            |                  |     |           |     | bit 0   |  |  |  |

|                                                                            |                            |                  |                  |     |           |     |         |  |  |  |

| Legend:                                                                    |                            |                  |                  |     |           |     |         |  |  |  |

| R = Readabl                                                                |                            |                  |                  |     |           |     |         |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                            |                  |                  |     |           |     |         |  |  |  |

|                                                                            |                            |                  |                  |     |           |     |         |  |  |  |

| bit 15                                                                     | ULPEN: ULF                 | PWU Module En    | able bit         |     |           |     |         |  |  |  |

|                                                                            | 1 = Module i               |                  |                  |     |           |     |         |  |  |  |

|                                                                            | 0 = Module i               | s disabled       |                  |     |           |     |         |  |  |  |

| bit 14                                                                     | Unimpleme                  | nted: Read as '0 | ,                |     |           |     |         |  |  |  |

| bit 13                                                                     | ULPSIDL: U                 | LPWU Stop in Ic  | lle Select bit   |     |           |     |         |  |  |  |

|                                                                            |                            | nues module ope  |                  |     | Idle mode |     |         |  |  |  |

|                                                                            | 0 = Continue               | es module operat | tion in Idle mod | e   |           |     |         |  |  |  |

| bit 12-9                                                                   | Unimplemented: Read as '0' |                  |                  |     |           |     |         |  |  |  |

| bit 8                                                                      | ULPSINK: U                 | ILPWU Current S  | Sink Enable bit  |     |           |     |         |  |  |  |

|                                                                            | 1 = Current                | sink is enabled  |                  |     |           |     |         |  |  |  |

|                                                                            | 0 = Current s              | sink is disabled |                  |     |           |     |         |  |  |  |

| bit 7-0                                                                    | Unimpleme                  | nted: Read as '0 | 3                |     |           |     |         |  |  |  |

| -                     |                                                                                                                                                                                             |                                       |                                                 |                                                                                     |                                    |                     | ,                   |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------|---------------------|---------------------|--|--|

| R/W-0                 | R/W-0                                                                                                                                                                                       | U-0                                   | U-0                                             | R/W-0                                                                               | R/W-0                              | R/W-0               | R/W-0               |  |  |

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup>                                                                                                                                                                       |                                       | —                                               | OPS3 <sup>(3)</sup>                                                                 | OPS2 <sup>(3)</sup>                | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |  |  |

| bit 15                |                                                                                                                                                                                             |                                       |                                                 |                                                                                     |                                    |                     | bit 8               |  |  |

|                       |                                                                                                                                                                                             |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

| R/W-0                 | R/W-0                                                                                                                                                                                       | R/W-0                                 | R/W-0                                           | R/W-0                                                                               | R/W-0                              | R/W-0               | R/W-0               |  |  |

| TRIGEN <sup>(4)</sup> | ONESHOT                                                                                                                                                                                     | ALTSYNC                               | SYNC4                                           | SYNC3                                                                               | SYNC2                              | SYNC1               | SYNC0               |  |  |

| bit 7                 |                                                                                                                                                                                             |                                       |                                                 |                                                                                     |                                    |                     | bit 0               |  |  |

|                       |                                                                                                                                                                                             |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

| Legend:               |                                                                                                                                                                                             |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

| R = Readable          |                                                                                                                                                                                             | W = Writable I                        | oit                                             | -                                                                                   | nented bit, read                   | l as '0'            |                     |  |  |

| -n = Value at         | POR                                                                                                                                                                                         | '1' = Bit is set                      |                                                 | '0' = Bit is clea                                                                   | ared                               | x = Bit is unkr     | iown                |  |  |

|                       |                                                                                                                                                                                             |                                       |                                                 | (1)                                                                                 |                                    |                     |                     |  |  |

| bit 15                |                                                                                                                                                                                             | tput Postscaler                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

|                       |                                                                                                                                                                                             | ostscaler scales                      |                                                 | er output event                                                                     | IS                                 |                     |                     |  |  |

| bit 14                |                                                                                                                                                                                             | trigger Enable                        |                                                 |                                                                                     |                                    |                     |                     |  |  |

|                       |                                                                                                                                                                                             | e can be retrig                       |                                                 | RIGEN bit = 1                                                                       |                                    |                     |                     |  |  |

|                       |                                                                                                                                                                                             |                                       |                                                 | en TRIGEN bit =                                                                     | = 1                                |                     |                     |  |  |

| bit 13-12             | Unimplement                                                                                                                                                                                 | ted: Read as 'o                       | )'                                              |                                                                                     |                                    |                     |                     |  |  |

| bit 11-8              | <b>OPS3&lt;3:0&gt;:</b> CCPx Interrupt Output Postscale Select bits <sup>(3)</sup>                                                                                                          |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

|                       | <pre>1111 = Interrupt every 16th time base period match 1110 = Interrupt every 15th time base period match</pre>                                                                            |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

|                       | 0011 = Interru<br>0010 = Interru<br>0001 = Interru                                                                                                                                          | upt every 3rd tir<br>upt every 2nd ti | ne base perio<br>ne base perio<br>me base perio | d match<br>d match or 4th i<br>d match or 3rd<br>od match or 2nc<br>od match or inp | input capture e<br>l input capture | event<br>event      |                     |  |  |

| bit 7                 | TRIGEN: CCF                                                                                                                                                                                 | Px Trigger Enal                       | ole bit <sup>(4)</sup>                          |                                                                                     |                                    |                     |                     |  |  |

|                       |                                                                                                                                                                                             | peration of time<br>peration of time  |                                                 |                                                                                     |                                    |                     |                     |  |  |

| bit 6                 | ONESHOT: One-Shot Mode Enable bit                                                                                                                                                           |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

|                       | <ul> <li>1 = One-Shot Trigger mode is enabled; Trigger duration is set by OSCNT&lt;2:0&gt;</li> <li>0 = One-Shot Trigger mode IS disabled</li> </ul>                                        |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

| bit 5                 | ALTSYNC: CCPx Clock Select bits                                                                                                                                                             |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

|                       | <ul> <li>1 = An alternate signal is used as the module synchronization output signal</li> <li>0 = The module synchronization output signal is the Time Base Reset/rollover event</li> </ul> |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

|                       |                                                                                                                                                                                             | -                                     |                                                 |                                                                                     | Base Reset/ro                      | ollover event       |                     |  |  |

| bit 4-0               |                                                                                                                                                                                             | CCPx Synchroi                         |                                                 | e Select bits                                                                       |                                    |                     |                     |  |  |

|                       | See lable 13-                                                                                                                                                                               | 6 for the definit                     | ion of inputs.                                  |                                                                                     |                                    |                     |                     |  |  |

| Note 1: Th            | nis control bit ha                                                                                                                                                                          | is no function ir                     | Input Capture                                   | e modes.                                                                            |                                    |                     |                     |  |  |

|                       | nis control bit ha                                                                                                                                                                          |                                       |                                                 |                                                                                     |                                    |                     |                     |  |  |

|                       | utput postscale s<br>odes.                                                                                                                                                                  | settings from 1:8                     | 5 to 1:16 (0100                                 | )-1111) will resu                                                                   | ult in a FIFO but                  | ffer overflow for   | Input Capture       |  |  |

### REGISTER 13-2: CCPxCON1H: CCPx CONTROL 1 HIGH REGISTERS

4: Clock source options are limited when Trigger operation is enabled; refer to Table 13-1.

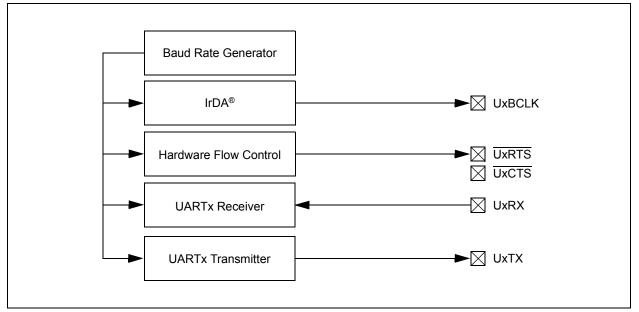

# 15.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features of  |

|-------|---------------------------------------------|

|       | this group of PIC24F devices. It is not     |

|       | intended to be a comprehensive reference    |

|       | source. For more information on the Univer- |

|       | sal Asynchronous Receiver Transmitter,      |

|       | refer to the "PIC24F Family Reference       |

|       | Manual", " <b>UART"</b> (DS39708).          |

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 15-1. The UARTx module consists of these important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

- Note: Throughout this section, references to register and bit names that may be associated with a specific USART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the USART Status register for either USART1 or USART2.

## FIGURE 15-1: UARTX MODULE SIMPLIFIED BLOCK DIAGRAM

#### 16.2.5 RTCVAL REGISTER MAPPINGS

### REGISTER 16-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _      | —   | _   | —   | —   | —   | —   | —     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| YRTEN3 | YRTEN2 | YRTEN1 | YRTEN0 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  | •      |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

## **REGISTER 16-5:** MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'.

- bit 11-8 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9.

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **DAYTEN<1:0>:** Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.

- bit 3-0 **DAYONE<3:0>:** Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# REGISTER 17-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER (CONTINUED)

| bit 3 | G1D2T: Gate 1 Data Source 2 True Enable bit                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = The Data Source 2 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 2 inverted signal is disabled for Gate 1</li> </ul> |

|       | -                                                                                                                                                     |

| bit 2 | G1D2N: Gate 1 Data Source 2 Negated Enable bit                                                                                                        |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 1                                                                                           |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 1                                                                                          |

| bit 1 | G1D1T: Gate 1 Data Source 1 True Enable bit                                                                                                           |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 1                                                                                           |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 1                                                                                          |

| bit 0 | G1D1N: Gate 1 Data Source 1 Negated Enable bit                                                                                                        |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 1                                                                                           |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 1                                                                                          |

To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs and/or select band gap reference inputs (ANSx registers).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- e) Configure the MODE12 bit to select A/D resolution (AD1CON1<10>).

- f) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- g) Select the interrupt rate (AD1CON2<6:2>).

- h) Turn on the A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

To perform an A/D sample and conversion using Threshold Detect scanning:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs (ANSx registers).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- e) Configure the MODE12 bit to select A/D resolution (AD1CON1<10>).

- f) Select how the conversion results are presented in the buffer (AD1CON1<9:8>).

- g) Select the interrupt rate (AD1CON2<6:2>).

- 2. Configure the threshold compare channels:

- a) Enable auto-scan; set the ASEN bit (AD1CON5<15>).

- b) Select the Compare mode, "Greater Than, Less Than or Windowed"; set the CMx bits (AD1CON5<1:0>).

- c) Select the threshold compare channels to be scanned (AD1CSSH, AD1CSSL).

- d) If the CTMU is required as a current source for a threshold compare channel, enable the corresponding CTMU channel (AD1CTMENH, AD1CTMENL).

- e) Write the threshold values into the corresponding ADC1BUFx registers.

- f) Turn on the A/D module (AD1CON1<15>).

- Note: If performing an A/D sample and conversion, using Threshold Detect in Sleep Mode, the RC A/D clock source must be selected before entering into Sleep mode.

- 3. Configure the A/D interrupt (OPTIONAL):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

## REGISTER 19-1: AD1CON1: A/DA/D CONTROL REGISTER 1 (CONTINUED)

- bit 3

Unimplemented: Read as '0'

bit 2

ASAM: A/D Sample Auto-Start bit

1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set

0 = Sampling begins when the SAMP bit is manually set

bit 1

SAMP: A/D Sample Enable bit

1 = A/D Sample-and-Hold amplifiers are sampling

0 = A/D Sample-and-Hold amplifiers are holding

- bit 0 DONE: A/D Conversion Status bit

- 1 = A/D conversion cycle has completed

- 0 = A/D conversion cycle has not started or is in progress