#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km102-e-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

| REGISTER                                  |                                                                                              |                                                                      |                   | KI CONTRO        | LREGISTE       | ĸ              |             |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|------------------|----------------|----------------|-------------|--|--|

| R/SO-0, HC                                | R/W-0                                                                                        | R/W-0                                                                | R/W-0             | U-0              | U-0            | U-0            | U-0         |  |  |

| WR                                        | WREN                                                                                         | WRERR                                                                | PGMONLY           | _                | _              | —              | _           |  |  |

| bit 15                                    | •                                                                                            |                                                                      |                   | ·                |                |                | bit 8       |  |  |

|                                           |                                                                                              |                                                                      |                   |                  |                |                |             |  |  |

| U-0                                       | R/W-0                                                                                        | R/W-0                                                                | R/W-0             | R/W-0            | R/W-0          | R/W-0          | R/W-0       |  |  |

| _                                         | ERASE                                                                                        | NVMOP5                                                               | NVMOP4            | NVMOP3           | NVMOP2         | NVMOP1         | NVMOP0      |  |  |

| bit 7                                     |                                                                                              |                                                                      |                   |                  |                |                | bit 0       |  |  |

|                                           |                                                                                              |                                                                      |                   |                  |                |                |             |  |  |

| Legend:                                   |                                                                                              | HC = Hardware                                                        | Clearable bit     | U = Unimple      | mented bit, re | ead as '0'     |             |  |  |

| R = Readable                              | bit                                                                                          | W = Writable bit                                                     |                   | S = Settable     | Only bit       |                |             |  |  |

| -n = Value at                             | POR                                                                                          | '1' = Bit is set                                                     |                   | '0' = Bit is cle | eared          | x = Bit is unk | nown        |  |  |

| bit 15                                    |                                                                                              | ontrol bit (program<br>a data EEPROM e                               |                   | cle (can be set  | . but not clea | red in softwar | e)          |  |  |

|                                           |                                                                                              | le is complete (cle                                                  |                   |                  |                |                | -,          |  |  |

| bit 14                                    | WREN: Write                                                                                  | Enable bit (erase                                                    | or program)       |                  |                |                |             |  |  |

| 1 = Enables an erase or program operation |                                                                                              |                                                                      |                   |                  |                |                |             |  |  |

|                                           | 0 = No operation allowed (device clears this bit on completion of the write/erase operation) |                                                                      |                   |                  |                |                |             |  |  |

| bit 13                                    |                                                                                              | sh Error Flag bit                                                    |                   |                  |                |                |             |  |  |

|                                           |                                                                                              | operation is prem                                                    | aturely terminat  | ted (any MCL     | R or WDT F     | Reset during   | programming |  |  |

|                                           | operation<br>0 = The write                                                                   | )<br>operation comple                                                | eted successfully | /                |                |                |             |  |  |

| bit 12                                    |                                                                                              | Program Only Enal                                                    | ,                 | ,                |                |                |             |  |  |

| 511 12                                    |                                                                                              | Nrite operation is executed without erasing target address(es) first |                   |                  |                |                |             |  |  |

|                                           |                                                                                              | c erase-before-wr                                                    | -                 | ,                | -()            |                |             |  |  |

|                                           | Write operation                                                                              | ons are preceded                                                     | automatically by  | an erase of th   | e target addr  | ess(es).       |             |  |  |

| bit 11-7                                  | Unimplemen                                                                                   | ted: Read as '0'                                                     |                   |                  |                |                |             |  |  |

| bit 6                                     |                                                                                              | e Operation Selec                                                    |                   |                  |                |                |             |  |  |

|                                           |                                                                                              | an erase operation                                                   |                   |                  |                |                |             |  |  |

|                                           |                                                                                              | a write operation                                                    |                   |                  |                |                |             |  |  |

| bit 5-0                                   |                                                                                              | Programming O                                                        | -                 | and byte bits    |                |                |             |  |  |

|                                           | Erase Operations (when ERASE bit is '1'):<br>011010 = Erase 8 words                          |                                                                      |                   |                  |                |                |             |  |  |

|                                           | 011001 = Era                                                                                 |                                                                      |                   |                  |                |                |             |  |  |

|                                           | 011000 = Era                                                                                 |                                                                      |                   |                  |                |                |             |  |  |

|                                           |                                                                                              | ase entire data EE                                                   | -                 |                  |                |                |             |  |  |

|                                           | • •                                                                                          | Operations (when                                                     | n ERASE bit is '  | <u>0'):</u>      |                |                |             |  |  |

|                                           | 0001xx = Wr                                                                                  | ite 1 word                                                           |                   |                  |                |                |             |  |  |

|                                           |                                                                                              |                                                                      |                   |                  |                |                |             |  |  |

### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

## 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "PIC24F Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

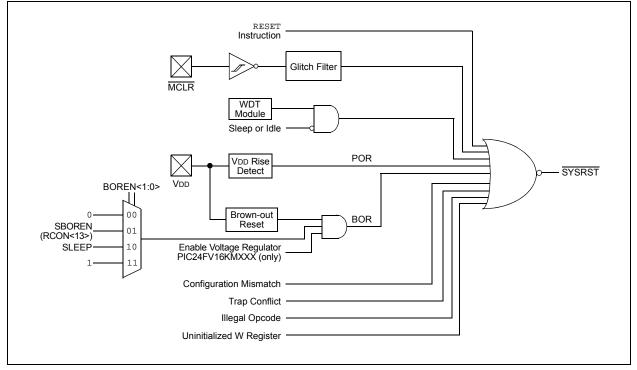

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- LPBOR: Low-Power BOR

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on Power-on Reset (POR) and unchanged by all other Resets.

Note: Refer to the specific peripheral or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A Power-on Reset will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

## FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

### REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

|        | —   | —   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0              | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|--------------------|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | —   | —     |

| bit 7 |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settal  | ble/Clearable bit  |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 1-0 Unimplemented: Read as '0'

**Note 1:** See Register 3-2 for the description of this bit, which is not dedicated to interrupt control functions.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

Note: Bit 2 is described in Section 3.0 "CPU".

### REGISTER 8-17: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0     |

|---------|-----|-----|-----|-----|-----|-----|---------|

| —       | —   | —   | —   | —   | —   | —   | —       |

| bit 15  |     |     |     |     |     |     | bit 8   |

|         |     |     |     |     |     |     |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

| —       | —   | —   | —   | —   | —   | —   | ULPWUIE |

| bit 7   |     |     |     |     |     |     | bit 0   |

|         |     |     |     |     |     |     |         |

| Legend: |     |     |     |     |     |     |         |

| Logena.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

### REGISTER 8-18: IEC6: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | —   | —   | _   | CLC2IE | CLC1IE |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IE: Configurable Logic Cell 2 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 0 CLC1IE: Configurable Logic Cell 1 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

| U-0          | U-0                                                        | U-0                                                        | U-0          | U-0               | R/W-1            | R/W-0              | R/W-0   |  |  |  |  |

|--------------|------------------------------------------------------------|------------------------------------------------------------|--------------|-------------------|------------------|--------------------|---------|--|--|--|--|

| —            | —                                                          | —                                                          | _            | —                 | CCP5IP2          | CCP5IP1            | CCP5IP0 |  |  |  |  |

| bit 15       |                                                            |                                                            |              |                   |                  | -                  | bit 8   |  |  |  |  |

|              |                                                            |                                                            |              |                   |                  |                    |         |  |  |  |  |

| U-0          | U-0                                                        | U-0                                                        | U-0          | U-0               | R/W-1            | R/W-0              | R/W-0   |  |  |  |  |

| _            | —                                                          | —                                                          |              | —                 | INT1IP2          | INT1IP1            | INT1IP0 |  |  |  |  |

| bit 7        |                                                            |                                                            |              |                   |                  |                    | bit 0   |  |  |  |  |

| Legend:      |                                                            |                                                            |              |                   |                  |                    |         |  |  |  |  |

| R = Readat   | ole hit                                                    | W = Writable b                                             | hit          | II = Unimpler     | nented bit, read | 1 as '0'           |         |  |  |  |  |

| -n = Value a |                                                            | '1' = Bit is set                                           |              | '0' = Bit is cle  |                  | x = Bit is unknown |         |  |  |  |  |

|              |                                                            |                                                            |              |                   |                  |                    |         |  |  |  |  |

| bit 15-11    | Unimplemer                                                 | nted: Read as '0                                           | '            |                   |                  |                    |         |  |  |  |  |

| bit 10-8     | CCP5IP<2:0                                                 | >: Capture/Com                                             | pare 5 Event | Interrupt Priorit | y bits           |                    |         |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt) |                                                            |              |                   |                  |                    |         |  |  |  |  |

|              | •                                                          | •                                                          |              |                   |                  |                    |         |  |  |  |  |

|              | •                                                          |                                                            |              |                   |                  |                    |         |  |  |  |  |

|              |                                                            | 001 = Interrupt is Priority 1                              |              |                   |                  |                    |         |  |  |  |  |

|              |                                                            | pt source is disa                                          |              |                   |                  |                    |         |  |  |  |  |

| bit 7-3      | Unimplemer                                                 | nted: Read as '0                                           | '            |                   |                  |                    |         |  |  |  |  |

| bit 2-0      |                                                            | : External Interru                                         |              |                   |                  |                    |         |  |  |  |  |

|              | 111 = Interru                                              | 111 = Interrupt is Priority 7 (highest priority interrupt) |              |                   |                  |                    |         |  |  |  |  |

|              | •                                                          |                                                            |              |                   |                  |                    |         |  |  |  |  |

|              | •                                                          |                                                            |              |                   |                  |                    |         |  |  |  |  |

|              |                                                            | 001 = Interrupt is Priority 1                              |              |                   |                  |                    |         |  |  |  |  |

|              | 000 = interru                                              | pt source is disa                                          | adied        |                   |                  |                    |         |  |  |  |  |

### REGISTER 8-24: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

### 11.2.2 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation, and a read operation of the same port. Typically, this instruction would be a NOP.

### 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC24FXXXXX family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 37 external signals (CN0 through CN36) that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the CN module. The CNEN1 and CNEN3 registers contain the interrupt enable control bits for each of the CNx input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CNx pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU3 registers, which contain the control bits for each of the CNx pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately using the CNPD1 and CNPD3 registers, which contain the control bits for each of the CNx pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

Note: Pull-ups and pull-downs on Change Notification (CN) pins should always be disabled whenever the port pin is configured as a digital output.

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0;<br>MOV W0, TRISB;                                                 | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs                                                                                          |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP ;                                                                             | //Delay 1 cycle                                                                                                                                      |

| BTSS PORTB, #13;                                                                  | //Next Instruction                                                                                                                                   |

| <pre>Equivalent `C' Code TRISB = 0xFF00; NOP(); if(PORTBbits.RB13 == 1) { }</pre> | <pre>//Configure PORTB&lt;15:8&gt; as inputs and PORTB&lt;7:0&gt; as outputs //Delay 1 cycle // execute following code if PORTB pin 13 is set.</pre> |

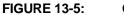

## 13.3 Output Compare Mode

Output Compare mode compares the Timer register value with the value of one or two Compare registers, depending on its mode of operation. The Output Compare x module on compare match events has the ability to generate a single output transition or a train of output

pulses. Like most PIC<sup>®</sup> MCU peripherals, the Output Compare x module can also generate interrupts on a compare match event.

Table 13-3 shows the various modes available in Output Compare modes.

| TABLE 13-3: | OUTPUT COMPARE/PWM MODES |

|-------------|--------------------------|

|-------------|--------------------------|

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) |                                        |                  |  |

|------------------------------|-----------------------|----------------------------------------|------------------|--|

| 0001                         | 0                     | Output High on Compare (16-bit)        |                  |  |

| 0001                         | 1                     | Output High on Compare (32-bit)        |                  |  |

| 0010                         | 0                     | Output Low on Compare (16-bit)         | Single Edge Mede |  |

| 0010                         | 1                     | Output Low on Compare (32-bit)         | Single Edge Mode |  |

| 0011                         | 0                     | Output Toggle on Compare (16-bit)      |                  |  |

| 0011                         | 1                     | Output Toggle on Compare (32-bit)      |                  |  |

| 0100                         | 0                     | Dual Edge Compare (16-bit)             | Dual Edge Mode   |  |

| 0101                         | 0                     | Dual Edge Compare (16-bit buffered)    | PWM Mode         |  |

| 0110                         | 0                     | Center-Aligned Pulse (16-bit buffered) | Center PWM       |  |

| 0111                         | 0                     | Variable Frequency Pulse (16-bit)      |                  |  |

| 0111                         | 1                     | Variable Frequency Pulse (32-bit)      |                  |  |

### OUTPUT COMPARE x BLOCK DIAGRAM

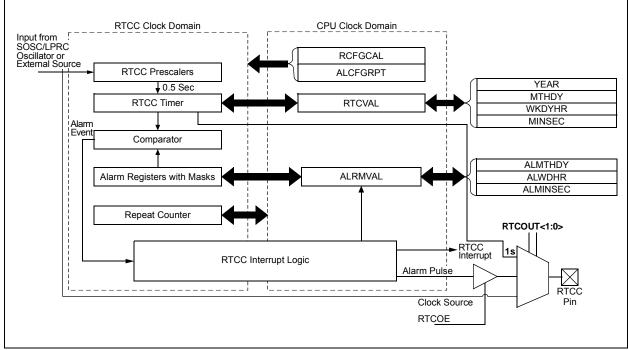

## 16.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Sleep and Retention Sleep modes

- · Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

### 16.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

## FIGURE 16-1: RTCC BLOCK DIAGRAM

### 16.2.4 RTCC CONTROL REGISTERS

## REGISTER 16-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                  | R-0, HSC                                                                                                                                                                         | R-0, HSC                                                                                                                              | R/W-0                                                                                     | R/W-0                                                                  | R/W-0                                               |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------|

| RTCEN <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                        | RTCWREN                                                                                                                                                                                                                                                                                                                                                | RTCSYNC                                                                                                                                                                          | HALFSEC <sup>(3)</sup>                                                                                                                | RTCOE                                                                                     | RTCPTR1                                                                | RTCPTR0                                             |

| bit 15               |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  | 1                                                                                                                                     |                                                                                           |                                                                        | bit 8                                               |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

| R/W-0                | R/W-0                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                            | R/W-0                                                                                                                                 | R/W-0                                                                                     | R/W-0                                                                  | R/W-0                                               |

| CAL7                 | CAL6                                                                                                                                                                                                                                                                                                                                   | CAL5                                                                                                                                                                                                                                                                                                                                                   | CAL4                                                                                                                                                                             | CAL3                                                                                                                                  | CAL1                                                                                      | CAL0                                                                   |                                                     |

| bit 7                |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        | bit (                                               |

| Legend:              |                                                                                                                                                                                                                                                                                                                                        | HSC = Hardw                                                                                                                                                                                                                                                                                                                                            | are Settable/C                                                                                                                                                                   | learable bit                                                                                                                          |                                                                                           |                                                                        |                                                     |

| R = Readable         | e bit                                                                                                                                                                                                                                                                                                                                  | W = Writable I                                                                                                                                                                                                                                                                                                                                         | oit                                                                                                                                                                              | U = Unimplem                                                                                                                          | ented bit, rea                                                                            | d as '0'                                                               |                                                     |

| -n = Value at        | POR                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  | '0' = Bit is clea                                                                                                                     |                                                                                           | x = Bit is unkr                                                        | iown                                                |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

| bit 15               | RTCEN: RT                                                                                                                                                                                                                                                                                                                              | CC Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                        | nodule is enable                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                                                |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                        | nodule is disable                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

| bit 14               | •                                                                                                                                                                                                                                                                                                                                      | nted: Read as '0                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

| bit 13               |                                                                                                                                                                                                                                                                                                                                        | RTCC Value Re                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                |                                                                                                                                       | u the upor                                                                                |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           |                                                                        |                                                     |

|                      |                                                                                                                                                                                                                                                                                                                                        | _H and RTCVAL<br>_H and RTCVAL                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |                                                                                                                                       |                                                                                           | n to by the user                                                       |                                                     |

| bit 12               | 0 = RTCVAL                                                                                                                                                                                                                                                                                                                             | H and RTCVAL                                                                                                                                                                                                                                                                                                                                           | L registers are                                                                                                                                                                  | locked out from                                                                                                                       | n being writter                                                                           | n to by the user                                                       |                                                     |

| bit 12               | 0 = RTCVAL<br>RTCSYNC:                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                        | L registers are<br>gisters Read S                                                                                                                                                | locked out from                                                                                                                       | h being writter<br>bit                                                                    |                                                                        | rollover ripple                                     |

| bit 12               | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting                                                                                                                                                                                                                                                                                      | ∟H and RTCVAL<br>RTCC Value Reo<br>∟H, RTCVALL ar<br>g in an invalid da                                                                                                                                                                                                                                                                                | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the                                                                                                              | locked out from<br>ynchronization<br>registers can c                                                                                  | n being writter<br>bit<br>hange while r                                                   | eading due to a                                                        |                                                     |

| bit 12               | 0 = RTCVAI<br>RTCSYNC:<br>1 = RTCVAI<br>resulting<br>can be a                                                                                                                                                                                                                                                                          | ₋H and RTCVAL<br>RTCC Value Reg<br>∟H, RTCVALL ar<br>g in an invalid da<br>assumed to be va                                                                                                                                                                                                                                                            | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the<br>alid.                                                                                                     | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

|                      | 0 = RTCVAL<br><b>RTCSYNC:</b><br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL                                                                                                                                                                                                                                                     | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or                                                                                                                                                                                                                                               | L registers are<br>gisters Read S<br>nd ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r                                                                                       | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

| bit 12<br>bit 11     | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H                                                                                                                                                                                                                                              | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or<br>Half Second Stat                                                                                                                                                                                                                           | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>tus bit <sup>(3)</sup>                                                             | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

|                      | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC:<br>1 = Second                                                                                                                                                                                                                                  | H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or                                                                                                                                                                                                                                               | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>sus bit <sup>(3)</sup><br>second                                                   | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

|                      | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal                                                                                                                                                                                                               | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a s                                                                                                                                                                                                | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>sus bit <sup>(3)</sup><br>second<br>ond                                            | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

| bit 11               | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: 1<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o                                                                                                                                                                                 | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled                                                                                                                                                        | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>tus bit <sup>(3)</sup><br>second<br>ond<br>le bit                                  | locked out from<br>ynchronization<br>registers can c<br>register is read t                                                            | h being writter<br>bit<br>hange while r<br>twice and rest                                 | eading due to a<br>ults in the same                                    | data, the data                                      |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC:<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o                                                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled                                                                                                                                 | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>second<br>ond<br>le bit                                                            | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be                                         | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without                 | eading due to a<br>ults in the same                                    | data, the data                                      |

| bit 11               | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:                                                                                                                                                      | -H and RTCVAL<br>RTCC Value Reg<br>H, RTCVALL ar<br>in an invalid da<br>assumed to be va<br>H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0-:</b> RTCC Value                                                                                                              | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind                  | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be                                         | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without                 | eading due to a<br>ults in the same<br>concern over a                  | data, the data                                      |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled                                                                                                                                 | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the                                                                                                                                     | -H and RTCVAL<br>RTCC Value Reg<br>LH, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>LH, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec                                                                | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT                                                                                  | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>: <u>8&gt;:</u><br>ES                                       | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT<br>01 = WEEKI                                                                    | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>output is enabled<br>output is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>: <u>8&gt;:</u><br>ES<br>DAY                              | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |

| bit 11<br>bit 10     | 0 = RTCVAL<br>RTCSYNC: 1<br>1 = RTCVAL<br>resulting<br>can be a<br>0 = RTCVAL<br>HALFSEC: H<br>1 = Second<br>0 = First hal<br>RTCOE: RTC<br>1 = RTCC o<br>0 = RTCC o<br>RTCPTR<1:<br>Points to the<br>The RTCPTF<br><u>RTCVAL&lt;15</u><br>00 = MINUT                                                                                  | -H and RTCVAL<br>RTCC Value Reg<br>-H, RTCVALL ar<br>g in an invalid da<br>assumed to be va<br>-H, RTCVALL or<br>Half Second Stat<br>half period of a sec<br>CC Output Enab<br>utput is enabled<br>utput is disabled<br><b>0&gt;:</b> RTCC Value<br>corresponding R<br>R<1:0> value dec<br>:8>:<br>ES<br>DAY<br>H                                      | L registers are<br>gisters Read S<br>ad ALCFGRPT<br>ta read. If the<br>alid.<br>ALCFGRPT r<br>us bit <sup>(3)</sup><br>second<br>ond<br>le bit<br>Register Wind<br>TCC Value reg | locked out from<br>ynchronization<br>registers can c<br>register is read t<br>egisters can be<br>dow Pointer bits<br>gisters when rea | h being writter<br>bit<br>hange while r<br>twice and rest<br>read without<br>ding the RTC | eading due to a<br>ults in the same<br>concern over a<br>VALH and RTC\ | data, the data<br>rollover ripple<br>/ALL registers |